Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 53                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                |                                                                       |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dv48clh |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Sec  | tion Number Title                                          | Page |

|------|------------------------------------------------------------|------|

|      | 12.3.15MSCAN Identifier Acceptance Registers (CANIDAR0-7)  | 237  |

|      | 12.3.16MSCAN Identifier Mask Registers (CANIDMR0–CANIDMR7) | 238  |

| 12.4 | Programmer's Model of Message Storage                      | 239  |

|      | 12.4.1 Identifier Registers (IDR0–IDR3)                    | 242  |

|      | 12.4.2 IDR0–IDR3 for Standard Identifier Mapping           | 244  |

|      | 12.4.3 Data Segment Registers (DSR0-7)                     | 245  |

|      | 12.4.4 Data Length Register (DLR)                          |      |

|      | 12.4.5 Transmit Buffer Priority Register (TBPR)            |      |

|      | 12.4.6 Time Stamp Register (TSRH–TSRL)                     | 247  |

| 12.5 | Functional Description                                     |      |

|      | 12.5.1 General                                             |      |

|      | 12.5.2 Message Storage                                     |      |

|      | 12.5.3 Identifier Acceptance Filter                        |      |

|      | 12.5.4 Modes of Operation                                  | 259  |

|      | 12.5.5 Low-Power Options                                   |      |

|      | 12.5.6 Reset Initialization                                |      |

|      | 12.5.7 Interrupts                                          |      |

| 12.6 | Initialization/Application Information                     |      |

|      | 12.6.1 MSCAN initialization                                |      |

|      | 12.6.2 Bus-Off Recovery                                    | 269  |

|      | Chapter 13                                                 |      |

|      | Serial Peripheral Interface (S08SPIV3)                     |      |

| 13.1 | Introduction                                               |      |

|      | 13.1.1 Features                                            |      |

|      | 13.1.2 Block Diagrams                                      |      |

| 100  | 13.1.3 SPI Baud Rate Generation                            |      |

| 13.2 | External Signal Description                                |      |

|      | 13.2.1 SPSCK — SPI Serial Clock                            |      |

|      | 13.2.2 MOSI — Master Data Out, Slave Data In               |      |

|      | 13.2.3 MISO — Master Data In, Slave Data Out               |      |

| 10.0 | 13.2.4 $\overline{SS}$ — Slave Select                      |      |

| 13.3 | Modes of Operation                                         |      |

| 10.4 | 13.3.1 SPI in Stop Modes                                   |      |

| 13.4 | Register Definition                                        |      |

|      | 13.4.1 SPI Control Register 1 (SPIC1)                      |      |

|      | 13.4.2 SPI Control Register 2 (SPIC2)                      |      |

|      | 13.4.3 SPI Baud Rate Register (SPIBR)                      |      |

|      | 13.4.4 SPI Status Register (SPIS)                          |      |

| 10.5 | 13.4.5 SPI Data Register (SPID)                            |      |

| 13.5 | Functional Description                                     |      |

|      | 13.5.1 SPI Clock Formats                                   | 282  |

MC9S08DV60 Series Data Sheet, Rev 3

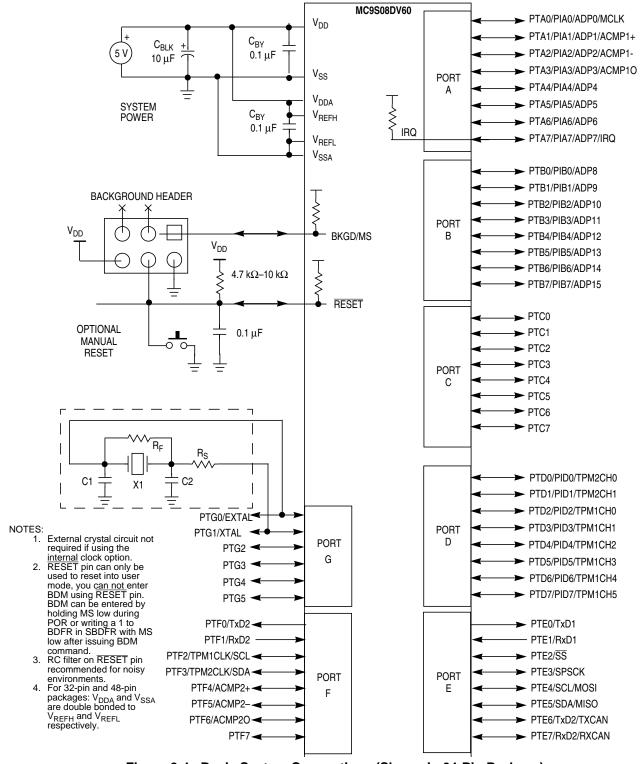

## 2.2 Recommended System Connections

Figure 2-4 shows pin connections that are common to MC9S08DV60 Series application systems.

Figure 2-4. Basic System Connections (Shown in 64-Pin Package)

MC9S08DV60 Series Data Sheet, Rev 3

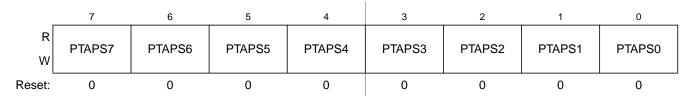

## 6.5.1.7 Port A Interrupt Pin Select Register (PTAPS)

Figure 6-9. Port A Interrupt Pin Select Register (PTAPS)

**Table 6-7. PTAPS Register Field Descriptions**

| Field | Description                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------|

| 7:0   | Port A Interrupt Pin Selects — Each of the PTAPSn bits enable the corresponding port A interrupt pin. |

|       | <ul><li>0 Pin not enabled as interrupt.</li><li>1 Pin enabled as interrupt.</li></ul>                 |

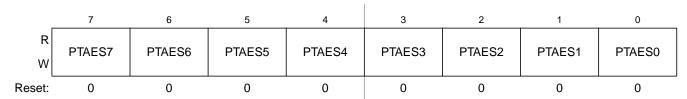

## 6.5.1.8 Port A Interrupt Edge Select Register (PTAES)

Figure 6-10. Port A Edge Select Register (PTAES)

Table 6-8. PTAES Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:0<br>PTAES[7:0] | Port A Edge Selects — Each of the PTAESn bits serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.  O A pull-up device is connected to the associated pin and detects falling edge/low level for interrupt generation.  A pull-down device is connected to the associated pin and detects rising edge/high level for interrupt generation. |  |

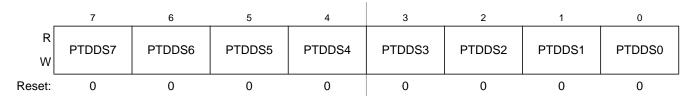

## 6.5.4.5 Port D Drive Strength Selection Register (PTDDS)

Figure 6-28. Drive Strength Selection for Port D Register (PTDDS)

Table 6-26. PTDDS Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Output Drive Strength Selection for Port D Bits — Each of these control bits selects between low and high output drive for the associated PTD pin. For port D pins that are configured as inputs, these bits have no effect.  1 Use the output drive strength selected for port D bit n.  2 District Distric |

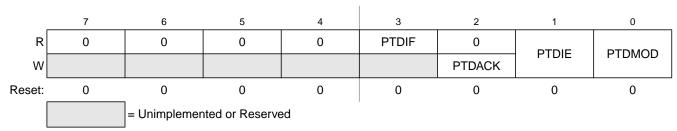

## 6.5.4.6 Port D Interrupt Status and Control Register (PTDSC)

Figure 6-29. Port D Interrupt Status and Control Register (PTDSC)

**Table 6-27. PTDSC Register Field Descriptions**

| Field       | Description                                                                                                                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>PTDIF  | Port D Interrupt Flag — PTDIF indicates when a port D interrupt is detected. Writes have no effect on PTDIF.  0 No port D interrupt detected.  1 Port D interrupt detected.                         |

| 2<br>PTDACK | Port D Interrupt Acknowledge — Writing a 1 to PTDACK is part of the flag clearing mechanism. PTDACK always reads as 0.                                                                              |

| 1<br>PTDIE  | Port D Interrupt Enable — PTDIE determines whether a port D interrupt is requested.  0 Port D interrupt request not enabled.  1 Port D interrupt request enabled.                                   |

| 0<br>PTDMOD | Port A Detection Mode — PTDMOD (along with the PTDES bits) controls the detection mode of the port D interrupt pins.  0 Port D pins detect edges only.  1 Port D pins detect both edges and levels. |

#### Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

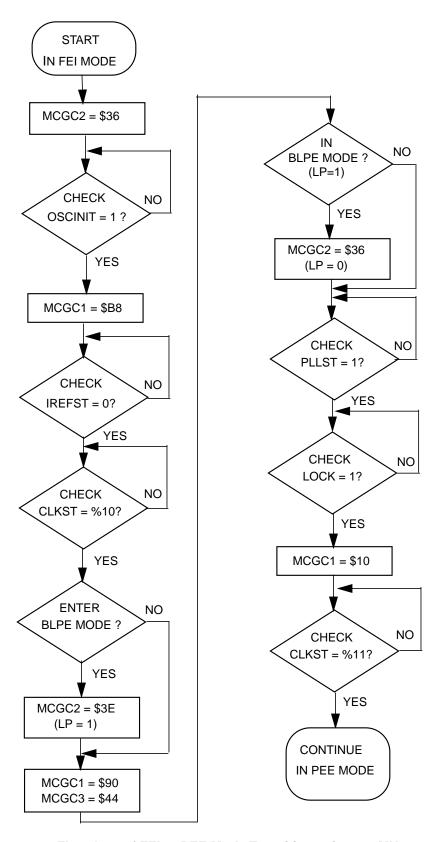

Figure 8-9. Flowchart of FEI to PEE Mode Transition using a 4 MHz crystal

## 8.5.2.2 Example # 2: Moving from PEE to BLPI Mode: External Crystal = 4 MHz, Bus Frequency =16 kHz

In this example, the MCG will move through the proper operational modes from PEE mode with a 4 MHz crystal configured for an 8 MHz bus frequency (see previous example) to BLPI mode with a 16 kHz bus frequency. First, the code sequence will be described. Then a flowchart will be included which illustrates the sequence.

- 1. First, PEE must transition to PBE mode:

- a) MCGC1 = 0x90 (%10010000)

- CLKS (bits 7 and 6) set to %10 in order to switch the system clock source to the external reference clock

- b) Loop until CLKST (bits 3 and 2) in MCGSC are %10, indicating that the external reference clock is selected to feed MCGOUT

- 2. Then, PBE must transition either directly to FBE mode or first through BLPE mode and then to FBE mode:

- a) BLPE: If a transition through BLPE mode is desired, first set LP (bit 3) in MCGC2 to 1

- b) BLPE/FBE: MCGC1 = 0xB8 (%10111000)

- RDIV (bits 5-3) set to %111, or divide-by-128 because 4 MHz / 128 = 31.25 kHz which is in the 31.25 kHz to 39.0625 kHz range required by the FLL. In BLPE mode, the configuration of the RDIV does not matter because both the FLL and PLL are disabled. Changing them only sets up the dividers for FLL usage in FBE mode

- c) BLPE/FBE: MCGC3 = 0x04 (%00000100)

- PLLS (bit 6) clear to 0 to select the FLL. In BLPE mode, changing this bit only prepares the MCG for FLL usage in FBE mode. With PLLS = 0, the VDIV value does not matter.

- d) BLPE: If transitioning through BLPE mode, clear LP (bit 3) in MCGC2 to 0 here to switch to FBE mode

- e) FBE: Loop until PLLST (bit 5) in MCGSC is clear, indicating that the current source for the PLLS clock is the FLL

- f) FBE: Optionally, loop until LOCK (bit 6) in the MCGSC is set, indicating that the FLL has acquired lock. Although the FLL is bypassed in FBE mode, it is still enabled and running.

- 3. Next, FBE mode transitions into FBI mode:

- a) MCGC1 = 0x44 (%01000100)

- CLKS (bits7 and 6) in MCGSC1 set to %01 in order to switch the system clock to the internal reference clock

- IREFS (bit 2) set to 1 to select the internal reference clock as the reference clock source

- RDIV (bits 5-3) set to %000, or divide-by-1 because the trimmed internal reference should be within the 31.25 kHz to 39.0625 kHz range required by the FLL

- b) Loop until IREFST (bit 4) in MCGSC is 1, indicating the internal reference clock has been selected as the reference clock source

- c) Loop until CLKST (bits 3 and 2) in MCGSC are %01, indicating that the internal reference clock is selected to feed MCGOUT

#### 9.1.2 Features

The ACMP has the following features:

- Full rail to rail supply operation.

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output.

- Option to compare to fixed internal bandgap reference voltage.

- Option to allow comparator output to be visible on a pin, ACMPxO.

## 9.1.3 Modes of Operation

This section defines the ACMP operation in wait, stop, and background debug modes.

#### 9.1.3.1 ACMP in Wait Mode

The ACMP continues to run in wait mode if enabled before executing the appropriate instruction. Therefore, the ACMP can be used to bring the MCU out of wait mode if the ACMP interrupt is enabled (ACIE is set). For lowest possible current consumption, the ACMP should be disabled by software if not required as an interrupt source during wait mode.

#### 9.1.3.2 ACMP in Stop Modes

The ACMP is disabled in all stop modes, regardless of the settings before executing the stop instruction. Therefore, the ACMP cannot be used as a wake up source from stop modes.

During stop2 mode, the ACMP module is fully powered down. Upon wake-up from stop2 mode, the ACMP module is in the reset state.

During stop3 mode, clocks to the ACMP module are halted. No registers are affected. In addition, the ACMP comparator circuit enters a low-power state. No compare operation occurs while in stop3.

If stop3 is exited with a reset, the ACMP is put into its reset state. If stop3 is exited with an interrupt, the ACMP continues from the state it was in when stop3 was entered.

## 9.1.3.3 ACMP in Active Background Mode

When the microcontroller is in active background mode, the ACMP continues to operate normally.

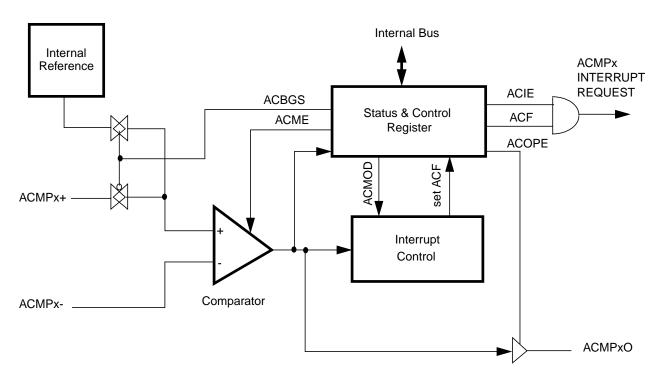

Chapter 9 Analog Comparator (S08ACMPV3)

## 9.1.4 Block Diagram

The block diagram for the analog comparator module is shown Figure 9-2.

Figure 9-2. Analog Comparator (ACMP) Block Diagram

## 9.2 External Signal Description

The ACMP has two analog input pins, ACMPx+ and ACMPx- and one digital output pin ACMPxO. Each of these pins can accept an input voltage that varies across the full operating voltage range of the MCU. As shown in Figure 9-2, the ACMPx- pin is connected to the inverting input of the comparator, and the ACMPx+ pin is connected to the comparator non-inverting input if ACBGS is a 0. As shown in Figure 9-2, the ACMPxO pin can be enabled to drive an external pin.

The signal properties of ACMP are shown in Table 9-1.

Signal Function I/O

ACMPx- Inverting analog input to the ACMP. (Minus input)

ACMPx+ Non-inverting analog input to the ACMP. (Positive input)

ACMPxO Digital output of the ACMP. O

**Table 9-1. Signal Properties**

MC9S08DV60 Series Data Sheet, Rev 3

## 10.3.2 Status and Control Register 2 (ADCSC2)

The ADCSC2 register controls the compare function, conversion trigger, and conversion active of the ADC module.

Figure 10-4. Status and Control Register 2 (ADCSC2)

Table 10-5. ADCSC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADACT | Conversion Active. Indicates that a conversion is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.  0 Conversion not in progress 1 Conversion in progress                                                                                                                                                                                                                                                |

| 6<br>ADTRG | Conversion Trigger Select. Selects the type of trigger used for initiating a conversion. Two types of triggers are selectable: software trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write to ADCSC1. When hardware trigger is selected, a conversion is initiated following the assertion of the ADHWT input.  O Software trigger selected  Hardware trigger selected                                        |

| 5<br>ACFE  | Compare Function Enable. Enables the compare function.  0 Compare function disabled  1 Compare function enabled                                                                                                                                                                                                                                                                                                                                                         |

| 4<br>ACFGT | Compare Function Greater Than Enable. Configures the compare function to trigger when the result of the conversion of the input being monitored is greater than or equal to the compare value. The compare function defaults to triggering when the result of the compare of the input being monitored is less than the compare value.  O Compare triggers when input is less than compare value  Compare triggers when input is greater than or equal to compare value |

## 10.3.3 Data Result High Register (ADCRH)

In 12-bit operation, ADCRH contains the upper four bits of the result of a 12-bit conversion. In 10-bit mode, ADCRH contains the upper two bits of the result of a 10-bit conversion. When configured for 10-bit mode, ADR[11:10] are cleared. When configured for 8-bit mode, ADR[11:8] are cleared.

In 12-bit and 10-bit mode, ADCRH is updated each time a conversion completes except when automatic compare is enabled and the compare condition is not met. When a compare event does occur, the value is the addition of the conversion result and the two's complement of the compare value. In 12-bit and 10-bit mode, reading ADCRH prevents the ADC from transferring subsequent conversion results into the result registers until ADCRL is read. If ADCRL is not read until after the next conversion is completed, the intermediate conversion result is lost. In 8-bit mode, there is no interlocking with ADCRL.

Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

#### 10.6.1.3 Analog Input Pins

The external analog inputs are typically shared with digital I/O pins on MCU devices. The pin I/O control is disabled by setting the appropriate control bit in one of the pin control registers. Conversions can be performed on inputs without the associated pin control register bit set. It is recommended that the pin control register bit always be set when using a pin as an analog input. This avoids problems with contention because the output buffer is in its high impedance state and the pullup is disabled. Also, the input buffer draws DC current when its input is not at  $V_{\rm DD}$  or  $V_{\rm SS}$ . Setting the pin control register bits for all pins used as analog inputs should be done to achieve lowest operating current.

Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. Use of  $0.01~\mu F$  capacitors with good high-frequency characteristics is sufficient. These capacitors are not necessary in all cases, but when used they must be placed as near as possible to the package pins and be referenced to  $V_{SSA}$ .

For proper conversion, the input voltage must fall between  $V_{REFH}$  and  $V_{REFL}$ . If the input is equal to or exceeds  $V_{REFH}$ , the converter circuit converts the signal to 0xFFF (full scale 12-bit representation), 0x3FF (full scale 10-bit representation) or 0xFF (full scale 8-bit representation). If the input is equal to or less than  $V_{REFL}$ , the converter circuit converts it to 0x000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are straight-line linear conversions. There is a brief current associated with  $V_{REFL}$  when the sampling capacitor is charging. The input is sampled for 3.5 cycles of the ADCK source when ADLSMP is low, or 23.5 cycles when ADLSMP is high.

For minimal loss of accuracy due to current injection, pins adjacent to the analog input pins should not be transitioning during conversions.

#### 10.6.2 Sources of Error

Several sources of error exist for A/D conversions. These are discussed in the following sections.

#### 10.6.2.1 Sampling Error

For proper conversions, the input must be sampled long enough to achieve the proper accuracy. Given the maximum input resistance of approximately  $7k\Omega$  and input capacitance of approximately 5.5 pF, sampling to within 1/4LSB (at 12-bit resolution) can be achieved within the minimum sample window (3.5 cycles @ 8 MHz maximum ADCK frequency) provided the resistance of the external analog source ( $R_{AS}$ ) is kept below  $2k\Omega$ .

Higher source resistances or higher-accuracy sampling is possible by setting ADLSMP (to increase the sample window to 23.5 cycles) or decreasing ADCK frequency to increase sample time.

## 10.6.2.2 Pin Leakage Error

Leakage on the I/O pins can cause conversion error if the external analog source resistance ( $R_{AS}$ ) is high. If this error cannot be tolerated by the application, keep  $R_{AS}$  lower than  $V_{DDAD}$  / ( $2^{N*}I_{LEAK}$ ) for less than 1/4LSB leakage error (N=8 in 8-bit, 10 in 10-bit or 12 in 12-bit mode).

#### Chapter 13 Serial Peripheral Interface (S08SPIV3)

**Table 13-1. SPIC1 Field Descriptions (continued)**

| Field      | Description                                                                                                                                                                                                                                                                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MSTR  | Master/Slave Mode Select 0 SPI module configured as a slave SPI device 1 SPI module configured as a master SPI device                                                                                                                                                                                                                                                     |

| 3<br>CPOL  | Clock Polarity — This bit effectively places an inverter in series with the clock signal from a master SPI or to a slave SPI device. Refer to Section 13.5.1, "SPI Clock Formats" for more details.  O Active-high SPI clock (idles low)  1 Active-low SPI clock (idles high)                                                                                             |

| 2<br>CPHA  | Clock Phase — This bit selects one of two clock formats for different kinds of synchronous serial peripheral devices. Refer to Section 13.5.1, "SPI Clock Formats" for more details.  0 First edge on SPSCK occurs at the middle of the first cycle of an 8-cycle data transfer  1 First edge on SPSCK occurs at the start of the first cycle of an 8-cycle data transfer |

| 1<br>SSOE  | Slave Select Output Enable — This bit is used in combination with the mode fault enable (MODFEN) bit in SPCR2 and the master/slave (MSTR) control bit to determine the function of the SS pin as shown in Table 13-2.                                                                                                                                                     |

| 0<br>LSBFE | USB First (Shifter Direction)  O SPI serial data transfers start with most significant bit  SPI serial data transfers start with least significant bit                                                                                                                                                                                                                    |

Table 13-2. SS Pin Function

| MODFEN | SSOE | Master Mode                   | Slave Mode         |

|--------|------|-------------------------------|--------------------|

| 0      | 0    | General-purpose I/O (not SPI) | Slave select input |

| 0      | 1    | General-purpose I/O (not SPI) | Slave select input |

| 1      | 0    | SS input for mode fault       | Slave select input |

| 1      | 1    | Automatic SS output           | Slave select input |

#### **NOTE**

Ensure that the SPI should not be disabled (SPE=0) at the same time as a bit change to the CPHA bit. These changes should be performed as separate operations or unexpected behavior may occur.

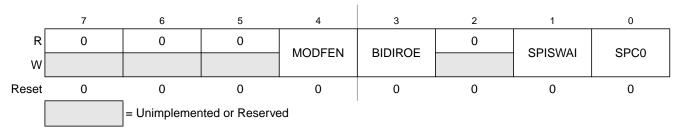

## 13.4.2 SPI Control Register 2 (SPIC2)

This read/write register is used to control optional features of the SPI system. Bits 7, 6, 5, and 2 are not implemented and always read 0.

Figure 13-6. SPI Control Register 2 (SPIC2)

MC9S08DV60 Series Data Sheet, Rev 3

Chapter 13 Serial Peripheral Interface (S08SPIV3)

## 13.5 Functional Description

An SPI transfer is initiated by checking for the SPI transmit buffer empty flag (SPTEF = 1) and then writing a byte of data to the SPI data register (SPID) in the master SPI device. When the SPI shift register is available, this byte of data is moved from the transmit data buffer to the shifter, SPTEF is set to indicate there is room in the buffer to queue another transmit character if desired, and the SPI serial transfer starts.

During the SPI transfer, data is sampled (read) on the MISO pin at one SPSCK edge and shifted, changing the bit value on the MOSI pin, one-half SPSCK cycle later. After eight SPSCK cycles, the data that was in the shift register of the master has been shifted out the MOSI pin to the slave while eight bits of data were shifted in the MISO pin into the master's shift register. At the end of this transfer, the received data byte is moved from the shifter into the receive data buffer and SPRF is set to indicate the data can be read by reading SPID. If another byte of data is waiting in the transmit buffer at the end of a transfer, it is moved into the shifter, SPTEF is set, and a new transfer is started.

Normally, SPI data is transferred most significant bit (MSB) first. If the least significant bit first enable (LSBFE) bit is set, SPI data is shifted LSB first.

When the SPI is configured as a slave, its  $\overline{SS}$  pin must be driven low before a transfer starts and  $\overline{SS}$  must stay low throughout the transfer. If a clock format where CPHA = 0 is selected,  $\overline{SS}$  must be driven to a logic 1 between successive transfers. If CPHA = 1,  $\overline{SS}$  may remain low between successive transfers. See Section 13.5.1, "SPI Clock Formats" for more details.

Because the transmitter and receiver are double buffered, a second byte, in addition to the byte currently being shifted out, can be queued into the transmit data buffer, and a previously received character can be in the receive data buffer while a new character is being shifted in. The SPTEF flag indicates when the transmit buffer has room for a new character. The SPRF flag indicates when a received character is available in the receive data buffer. The received character must be read out of the receive buffer (read SPID) before the next transfer is finished or a receive overrun error results.

In the case of a receive overrun, the new data is lost because the receive buffer still held the previous character and was not ready to accept the new data. There is no indication for such an overrun condition so the application system designer must ensure that previous data has been read from the receive buffer before a new transfer is initiated.

#### 13.5.1 SPI Clock Formats

To accommodate a wide variety of synchronous serial peripherals from different manufacturers, the SPI system has a clock polarity (CPOL) bit and a clock phase (CPHA) control bit to select one of four clock formats for data transfers. CPOL selectively inserts an inverter in series with the clock. CPHA chooses between two different clock phase relationships between the clock and data.

Figure 13-10 shows the clock formats when CPHA = 1. At the top of the figure, the eight bit times are shown for reference with bit 1 starting at the first SPSCK edge and bit 8 ending one-half SPSCK cycle after the sixteenth SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output

| Table 16-3. TPM-Clock-Source Selection |

|----------------------------------------|

|----------------------------------------|

| CLKSB:CLKSA | TPM Clock Source to Prescaler Input     |

|-------------|-----------------------------------------|

| 00          | No clock selected (TPM counter disable) |

| 01          | Bus rate clock                          |

| 10          | Fixed system clock                      |

| 11          | External source                         |

**Table 16-4. Prescale Factor Selection**

| PS2:PS1:PS0 | TPM Clock Source Divided-by |

|-------------|-----------------------------|

| 000         | 1                           |

| 001         | 2                           |

| 010         | 4                           |

| 011         | 8                           |

| 100         | 16                          |

| 101         | 32                          |

| 110         | 64                          |

| 111         | 128                         |

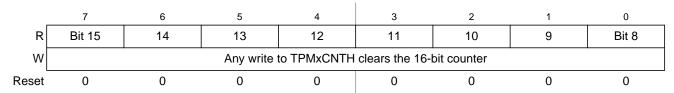

## 16.3.2 TPM-Counter Registers (TPMxCNTH:TPMxCNTL)

The two read-only TPM counter registers contain the high and low bytes of the value in the TPM counter. Reading either byte (TPMxCNTH or TPMxCNTL) latches the contents of both bytes into a buffer where they remain latched until the other half is read. This allows coherent 16-bit reads in either big-endian or little-endian order which makes this more friendly to various compiler implementations. The coherency mechanism is automatically restarted by an MCU reset or any write to the timer status/control register (TPMxSC).

Reset clears the TPM counter registers. Writing any value to TPMxCNTH or TPMxCNTL also clears the TPM counter (TPMxCNTH:TPMxCNTL) and resets the coherency mechanism, regardless of the data involved in the write.

Figure 16-8. TPM Counter Register High (TPMxCNTH)

| CLKSB:CLKSA TPM Clock Source to Prescaler Inpu |                                          |  |  |  |  |

|------------------------------------------------|------------------------------------------|--|--|--|--|

| 00                                             | No clock selected (TPM counter disabled) |  |  |  |  |

| 01                                             | Bus rate clock                           |  |  |  |  |

| 10                                             | Fixed system clock                       |  |  |  |  |

| 11                                             | External source                          |  |  |  |  |

Table 16-7, TPM Clock Source Selection

The bus rate clock is the main system bus clock for the MCU. This clock source requires no synchronization because it is the clock that is used for all internal MCU activities including operation of the CPU and buses.

In MCUs that have no PLL and FLL or the PLL and FLL are not engaged, the fixed system clock source is the same as the bus-rate-clock source, and it does not go through a synchronizer. When a PLL or FLL is present and engaged, a synchronizer is required between the crystal divided-by two clock source and the timer counter so counter transitions will be properly aligned to bus-clock transitions. A synchronizer will be used at chip level to synchronize the crystal-related source clock to the bus clock.

The external clock source may be connected to any TPM channel pin. This clock source always has to pass through a synchronizer to assure that counter transitions are properly aligned to bus clock transitions. The bus-rate clock drives the synchronizer; therefore, to meet Nyquist criteria even with jitter, the frequency of the external clock source must not be faster than the bus rate divided-by four. With ideal clocks the external clock can be as fast as bus clock divided by four.

When the external clock source shares the TPM channel pin, this pin should not be used for other channel timing functions. For example, it would be ambiguous to configure channel 0 for input capture when the TPM channel 0 pin was also being used as the timer external clock source. (It is the user's responsibility to avoid such settings.) The TPM channel could still be used in output compare mode for software timing functions (pin controls set not to affect the TPM channel pin).

#### 16.4.1.2 Counter Overflow and Modulo Reset

An interrupt flag and enable are associated with the 16-bit main counter. The flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE=0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE=1) where a static hardware interrupt is generated whenever the TOF flag is equal to one.

The conditions causing TOF to become set depend on whether the TPM is configured for center-aligned PWM (CPWMS=1). In the simplest mode, there is no modulus limit and the TPM is not in CPWMS=1 mode. In this case, the 16-bit timer counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the TPM is in center-aligned PWM mode (CPWMS=1), the TOF flag gets set as the counter changes direction at the end of the count value set in the modulus register (that is, at the transition from the value set in the modulus register to the next lower count value). This corresponds to the end of a PWM period (the 0x0000 count value corresponds to the center of a period).

# **Chapter 17 Development Support**

### 17.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC) and the on-chip debug module (DBG). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip Flash and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins (not even in test modes). Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

## 17.1.1 Forcing Active Background

The method for forcing active background mode depends on the specific HCS08 derivative. For the MC9S08DV60, you can force active background after a power-on reset by holding the BKGD pin low as the device exits the reset condition. You can also force active background by driving BKGD low immediately after a serial background command that writes a one to the BDFR bit in the SBDFR register. If no debug pod is connected to the BKGD pin, the MCU will always reset into normal operating mode.

#### **Chapter 17 Development Support**

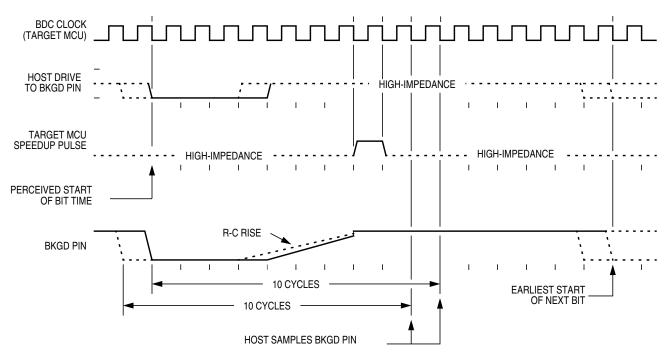

Figure 17-3 shows the host receiving a logic 1 from the target HCS08 MCU. Because the host is asynchronous to the target MCU, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the perceived start of the bit time in the target MCU. The host holds the BKGD pin low long enough for the target to recognize it (at least two target BDC cycles). The host must release the low drive before the target MCU drives a brief active-high speedup pulse seven cycles after the perceived start of the bit time. The host should sample the bit level about 10 cycles after it started the bit time.

Figure 17-3. BDC Target-to-Host Serial Bit Timing (Logic 1)

#### **Chapter 17 Development Support**

**A-Only** — Trigger when the address matches the value in comparator A

**A OR B** — Trigger when the address matches either the value in comparator A or the value in comparator B

**A Then B** — Trigger when the address matches the value in comparator B but only after the address for another cycle matched the value in comparator A. There can be any number of cycles after the A match and before the B match.

**A AND B Data (Full Mode)** — This is called a full mode because address, data, and R/W (optionally) must match within the same bus cycle to cause a trigger event. Comparator A checks address, the low byte of comparator B checks data, and R/W is checked against RWA if RWAEN = 1. The high-order half of comparator B is not used.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

**A AND NOT B Data (Full Mode)** — Address must match comparator A, data must not match the low half of comparator B, and R/W must match RWA if RWAEN = 1. All three conditions must be met within the same bus cycle to cause a trigger.

In full trigger modes it is not useful to specify a tag-type CPU breakpoint (BRKEN = TAG = 1), but if you do, the comparator B data match is ignored for the purpose of issuing the tag request to the CPU and the CPU breakpoint is issued when the comparator A address matches.

**Event-Only B** (Store Data) — Trigger events occur each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

A Then Event-Only B (Store Data) — After the address has matched the value in comparator A, a trigger event occurs each time the address matches the value in comparator B. Trigger events cause the data to be captured into the FIFO. The debug run ends when the FIFO becomes full.

**Inside Range** ( $A \le Address \le B$ ) — A trigger occurs when the address is greater than or equal to the value in comparator A and less than or equal to the value in comparator B at the same time.

Outside Range (Address < A or Address > B) — A trigger occurs when the address is either less than the value in comparator A or greater than the value in comparator B.

**Chapter 17 Development Support**

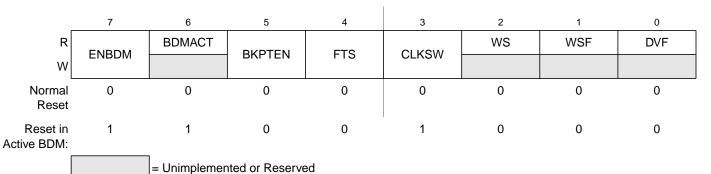

## 17.4.1.1 BDC Status and Control Register (BDCSCR)

This register can be read or written by serial BDC commands (READ\_STATUS and WRITE\_CONTROL) but is not accessible to user programs because it is not located in the normal memory map of the MCU.

Figure 17-5. BDC Status and Control Register (BDCSCR)

Table 17-2. BDCSCR Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ENBDM  | Enable BDM (Permit Active Background Mode) — Typically, this bit is written to 1 by the debug host shortly after the beginning of a debug session or whenever the debug host resets the target and remains 1 until a normal reset clears it.  0 BDM cannot be made active (non-intrusive commands still allowed)  1 BDM can be made active to allow active background mode commands                                                                                                                                                                                                                                              |

| 6<br>BDMACT | Background Mode Active Status — This is a read-only status bit.  0 BDM not active (user application program running)  1 BDM active and waiting for serial commands                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5<br>BKPTEN | BDC Breakpoint Enable — If this bit is clear, the BDC breakpoint is disabled and the FTS (force tag select) control bit and BDCBKPT match register are ignored.  0 BDC breakpoint disabled  1 BDC breakpoint enabled                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4<br>FTS    | Force/Tag Select — When FTS = 1, a breakpoint is requested whenever the CPU address bus matches the BDCBKPT match register. When FTS = 0, a match between the CPU address bus and the BDCBKPT register causes the fetched opcode to be tagged. If this tagged opcode ever reaches the end of the instruction queue, the CPU enters active background mode rather than executing the tagged opcode.  O Tag opcode at breakpoint address and enter active background mode if CPU attempts to execute that instruction  Breakpoint match forces active background mode at next instruction boundary (address need not be an opcode) |

| 3<br>CLKSW  | Select Source for BDC Communications Clock — CLKSW defaults to 0, which selects the alternate BDC clock source.  0 Alternate BDC clock source  1 MCU bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### **Appendix A Electrical Characteristics**

Table A-7. Supply Current Characteristics (continued)

| Num | С | Parameter                                                         | Symbol | V <sub>DD</sub> (V) | Typical <sup>1</sup> | Max <sup>2</sup> | Unit |

|-----|---|-------------------------------------------------------------------|--------|---------------------|----------------------|------------------|------|

| 6   | ( | RTC adder to stop2 or stop3 <sup>5</sup> , 25°C                   |        | 5                   | 300                  |                  | nA   |

| 6   | С |                                                                   |        | 3                   | 300                  | _                | nA   |

| _   |   | LVD adder to stop3 (LVDE = LVDSE = 1)                             |        | 5                   | 110                  | _                | μΑ   |

| 7 C |   |                                                                   |        | 3                   | 90                   | _                | μΑ   |

|     |   | Adder to stop3 for oscillator enabled <sup>6</sup>                |        | 5                   | 5                    | _                | μΑ   |

| 8 C |   | (IRCLKEN = 1 and IREFSTEN = 1 or<br>ERCLKEN = 1 and EREFSTEN = 1) |        | 3                   | 5                    | _                | μΑ   |

<sup>&</sup>lt;sup>1</sup> Typicals are measured at 25°C, unless otherwise noted.

## A.8 Analog Comparator (ACMP) Electricals

Table A-8. Analog Comparator Electrical Specifications

| Num | С | Rating                                 | Symbol             | Min                   | Typical | Max      | Unit |

|-----|---|----------------------------------------|--------------------|-----------------------|---------|----------|------|

| 1   | — | Supply voltage                         | $V_{DD}$           | 2.7                   | _       | 5.5      | V    |

| 2   | D | Supply current (active)                | I <sub>DDAC</sub>  | _                     | 20      | 35       | μΑ   |

| 3   | D | Analog input voltage                   | V <sub>AIN</sub>   | V <sub>SS</sub> - 0.3 | _       | $V_{DD}$ | V    |

| 4   | D | Analog input offset voltage            | V <sub>AIO</sub>   |                       | 20      | 40       | mV   |

| 5   | D | Analog Comparator hysteresis           | V <sub>H</sub>     | 3.0                   | 6.0     | 20.0     | mV   |

| 6   | D | Analog input leakage current           | I <sub>ALKG</sub>  |                       |         | 1.0      | μΑ   |

| 7   | D | Analog Comparator initialization delay | t <sub>AINIT</sub> | _                     | _       | 1.0      | μs   |

## A.9 ADC Characteristics

**Table A-9. 12-bit ADC Operating Conditions**

| Characteristic | Conditions                                                                  | Symb              | Min  | Typ <sup>1</sup> | Max  | Unit | Comment |

|----------------|-----------------------------------------------------------------------------|-------------------|------|------------------|------|------|---------|

| Supply voltage | Absolute                                                                    | V <sub>DDAD</sub> | 2.7  | _                | 5.5  | V    |         |

|                | Delta to V <sub>DD</sub> (V <sub>DD</sub> -V <sub>DDAD</sub> ) <sup>2</sup> | $\Delta V_{DDAD}$ | -100 | 0                | +100 | mV   |         |

| Ground voltage | Delta to V <sub>SS</sub> (V <sub>SS</sub> -V <sub>SSAD</sub> ) <sup>2</sup> | $\Delta V_{SSAD}$ | -100 | 0                | +100 | mV   |         |

#### MC9S08DV60 Series Data Sheet, Rev 3

<sup>&</sup>lt;sup>2</sup> Maximum values in this column apply for the full operating temperature range of the device unless otherwise noted.

<sup>&</sup>lt;sup>3</sup> All modules except ADC active, MCG configured for FBE, and does not include any dc loads on port pins

Stop currents are tested in production for 25°C on all parts. Tests at other temperatures depend upon the part number suffix and maturity of the product. Freescale may eliminate a test insertion at a particular temperature from the production test flow once sufficient data has been collected and is approved.

Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode.

Values given under the following conditions: low range operation (RANGE = 0), low power mode (HGO = 0).

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5-1994.

- $\sqrt{3}$ . Datums A, B, and D to be determined at datum plane H.

- 4. DIMENSIONS TO BE DETERMINED AT SEATING PLANE DATUM C.

- DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION: 0.07 MM.

- 6. DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS

0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING

MOLD MISMATCH.

- EXACT SHAPE OF EACH CORNER IS OPTIONAL.

- A. THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.1 MM AND 0.25 MM FROM THE LEAD TIP.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OUTLINE              |                 | PRINT VERSION NO | IT TO SCALE |

|------------------------------------------------------|---------------------------------|-----------------|------------------|-------------|

| TITLE:                                               | DOCUMENT NO                     | ]: 98ASH70029A  | REV: D           |             |

| LOW PROFILE QUAD FLAT PA                             | CASE NUMBER: 873A-03 19 MAY 200 |                 |                  |             |

| 32 LEAD, 0.8 PITCH (7 X                              | STANDARD: JE                    | IDEC MS-026 BBA |                  |             |