Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 53                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dv48mlh |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

| <b>5</b> e( | ction Number Title                                                | Page |

|-------------|-------------------------------------------------------------------|------|

|             | Chapter 1<br>Device Overview                                      |      |

| 1.1         | Devices in the MC9S08DV60 Series                                  | 21   |

| 1.2         | MCU Block Diagram                                                 | 22   |

| 1.3         | System Clock Distribution                                         |      |

|             | Chapter 2                                                         |      |

| 2.1         | Pins and Connection                                               |      |

| 2.1 2.2     | Device Pin Assignment                                             |      |

| 2.2         | 2.2.1 Power                                                       |      |

|             | 2.2.2 Oscillator                                                  |      |

|             | 2.2.3 RESET                                                       |      |

|             | 2.2.4 Background / Mode Select (BKGD/MS)                          |      |

|             | 2.2.5 ADC Reference Pins (V <sub>REFH</sub> , V <sub>REFL</sub> ) |      |

|             | 2.2.6 General-Purpose I/O and Peripheral Ports                    |      |

|             | Chapter 3                                                         |      |

|             | Modes of Operation                                                |      |

| 3.1         | Introduction                                                      |      |

| 3.2         | Features                                                          |      |

| 3.3         | Run Mode                                                          |      |

| 3.4         | Active Background Mode                                            |      |

| 3.5         | Wait Mode                                                         |      |

| 3.6         | Stop Modes                                                        |      |

|             | 3.6.1 Stop3 Mode                                                  |      |

|             | 3.6.2 Stop2 Mode                                                  |      |

|             |                                                                   |      |

|             | Chapter 4<br>Memory                                               |      |

| 4.1         | MC9S08DV60 Series Memory Map                                      | 41   |

| 4.2         | Reset and Interrupt Vector Assignments                            | 42   |

| 4.3         | Register Addresses and Bit Assignments                            |      |

| 4.4         | RAM                                                               |      |

| 4.5         | Flash                                                             |      |

|             | 4.5.1 Features                                                    | 52   |

MC9S08DV60 Series Data Sheet, Rev 3

Freescale Semiconductor

Subject to Change

#### **Chapter 1 Device Overview**

Table 1-2 provides the functional version of the on-chip modules.

Table 1-2. Module Versions

| Module                          |         | Version        |

|---------------------------------|---------|----------------|

| Central Processor Unit          | (CPU)   | 3              |

| Multi-Purpose Clock Generator   | (MCG)   | 1              |

| Analog Comparator               | (ACMP)  | 3              |

| Analog-to-Digital Converter     | (ADC)   | 1              |

| Inter-Integrated Circuit        | (IIC)   | 2              |

| Freescale's CAN                 | (MSCAN) | 1              |

| Serial Peripheral Interface     | (SPI)   | 3              |

| Serial Communications Interface | (SCI)   | 4              |

| Real-Time Counter               | (RTC)   | 1              |

| Timer Pulse Width Modulator     | (TPM)   | 3 <sup>1</sup> |

| Debug Module                    | (DBG)   | 2              |

<sup>1 3</sup>M05C and older masks have TPM version 2.

### 1.3 System Clock Distribution

Figure 1-2 shows a simplified clock connection diagram. Some modules in the MCU have selectable clock inputs as shown. The clock inputs to the modules indicate the clock(s) that are used to drive the module function.

The following are the clocks used in this MCU:

- BUSCLK The frequency of the bus is always half of MCGOUT.

- LPO Independent 1-kHz clock that can be selected as the source for the COP and RTC modules.

- MCGOUT Primary output of the MCG and is twice the bus frequency.

- MCGLCLK Development tools can select this clock source to speed up BDC communications in systems where BUSCLK is configured to run at a very slow frequency.

- MCGERCLK External reference clock can be selected as the RTC clock source. It can also be

used as the alternate clock for the ADC and MSCAN.

- MCGIRCLK Internal reference clock can be selected as the RTC clock source.

- MCGFFCLK Fixed frequency clock can be selected as clock source for the TPM1 and TPM2.

- TPM1CLK External input clock source for TPM1.

- TPM2CLK External input clock source for TPM2.

**Chapter 4 Memory**

Table 4-3. High-Page Register Summary (Sheet 1 of 3)

| Address            | Register Name | Bit 7   | 6      | 5        | 4                     | 3        | 2      | 1      | Bit 0  |

|--------------------|---------------|---------|--------|----------|-----------------------|----------|--------|--------|--------|

| 0x1800             | SRS           | POR     | PIN    | COP      | ILOP                  | ILAD     | LOCS   | LVD    | 0      |

| 0x1801             | SBDFR         | 0       | 0      | 0        | 0                     | 0        | 0      | 0      | BDFR   |

| 0x1802             | SOPT1         | СО      | PT     | STOPE    | SCI2PS                | IICPS    | 0      | 0      | 0      |

| 0x1803             | SOPT2         | COPCLKS | COPW   | 0        | ADHTS                 | 0        |        | MCSEL  |        |

| 0x1804 —<br>0x1805 | Reserved      | _       | _<br>_ | _<br>_   | _                     |          | _      | _<br>_ | _      |

| 0x1806             | SDIDH         | _       | _      | _        | _                     | ID11     | ID10   | ID9    | ID8    |

| 0x1807             | SDIDL         | ID7     | ID6    | ID5      | ID4                   | ID3      | ID2    | ID1    | ID0    |

| 0x1808             | Reserved      | _       | _      | _        | _                     | _        | _      | _      | _      |

| 0x1809             | SPMSC1        | LVWF    | LVWACK | LVWIE    | LVDRE                 | LVDSE    | LVDE   | 0      | BGBE   |

| 0x180A             | SPMSC2        | 0       | 0      | LVDV     | LVWV                  | PPDF     | PPDACK | 0      | PPDC   |

| 0x180B-<br>0x180F  | Reserved      | _       | _      | _        | _                     | _        | _      | _      | _      |

| 0x1810             | DBGCAH        | Bit 15  | 14     | 13       | 12                    | 11       | 10     | 9      | Bit 8  |

| 0x1811             | DBGCAL        | Bit 7   | 6      | 5        | 4                     | 3        | 2      | 1      | Bit 0  |

| 0x1812             | DBGCBH        | Bit 15  | 14     | 13       | 12                    | 11       | 10     | 9      | Bit 8  |

| 0x1813             | DBGCBL        | Bit 7   | 6      | 5        | 4                     | 3        | 2      | 1      | Bit 0  |

| 0x1814             | DBGFH         | Bit 15  | 14     | 13       | 12                    | 11       | 10     | 9      | Bit 8  |

| 0x1815             | DBGFL         | Bit 7   | 6      | 5        | 4                     | 3        | 2      | 1      | Bit 0  |

| 0x1816             | DBGC          | DBGEN   | ARM    | TAG      | BRKEN                 | RWA      | RWAEN  | RWB    | RWBEN  |

| 0x1817             | DBGT          | TRGSEL  | BEGIN  | 0        | 0                     | TRG3     | TRG2   | TRG1   | TRG0   |

| 0x1818             | DBGS          | AF      | BF     | ARMF     | 0                     | CNT3     | CNT2   | CNT1   | CNT0   |

| 0x1819–<br>0x181F  | Reserved      | _       |        | _<br>_   | _                     |          |        |        |        |

| 0x1820             | FCDIV         | DIVLD   | PRDIV8 |          |                       | D        | IV     |        |        |

| 0x1821             | FOPT          | KEYEN   | FNORED | Reserved | 0                     | 0        | 0      | SE     | C      |

| 0x1822             | Reserved      | _       | _      | _        | _                     | _        | _      | _      | _      |

| 0x1823             | FCNFG         | 0       | _      | KEYACC   | Reserved <sup>1</sup> | 0        | 0      | 0      | 1      |

| 0x1824             | FPROT         | Rese    | erved  |          |                       | FF       | PS     |        |        |

| 0x1825             | FSTAT         | FCBEF   | FCCF   | FPVIOL   | FACCERR               | 0        | FBLANK | 0      | 0      |

| 0x1826             | FCMD          |         |        | FCMD     |                       |          |        |        |        |

| 0x1827-<br>0x183F  | Reserved      | _       | _<br>_ | _<br>_   | _<br>_                | <u> </u> | _<br>_ | _<br>_ |        |

| 0x1840             | PTAPE         | PTAPE7  | PTAPE6 | PTAPE5   | PTAPE4                | PTAPE3   | PTAPE2 | PTAPE1 | PTAPE0 |

| 0x1841             | PTASE         | PTASE7  | PTASE6 | PTASE5   | PTASE4                | PTASE3   | PTASE2 | PTASE1 | PTASE0 |

| 0x1842             | PTADS         | PTADS7  | PTADS6 | PTADS5   | PTADS4                | PTADS3   | PTADS2 | PTADS1 | PTADS0 |

| 0x1843             | Reserved      | _       | _      | _        | _                     | _        | _      | _      | _      |

| 0x1844             | PTASC         | 0       | 0      | 0        | 0                     | PTAIF    | PTAACK | PTAIE  | PTAMOD |

| 0x1845             | PTAPS         | PTAPS7  | PTAPS6 | PTAPS5   | PTAPS4                | PTAPS3   | PTAPS2 | PTAPS1 | PTAPS0 |

| 0x1846             | PTAES         | PTAES7  | PTAES6 | PTAES5   | PTAES4                | PTAES3   | PTAES2 | PTAES1 | PTAES0 |

MC9S08DV60 Series Data Sheet, Rev 3

#### **Chapter 4 Memory**

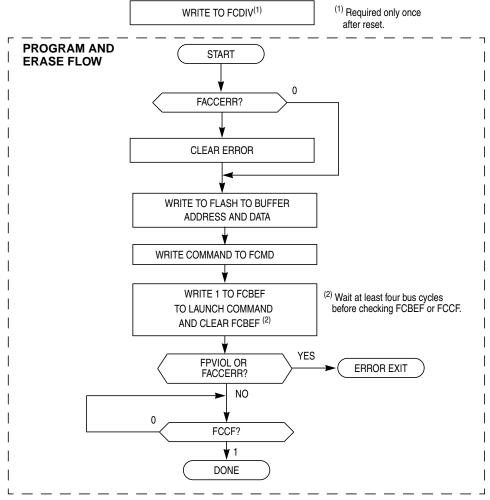

3. Write a 1 to the FCBEF bit in FSTAT to clear FCBEF and launch the command (including its address and data information).

A partial command sequence can be aborted manually by writing a 0 to FCBEF any time after the write to the memory array and before writing the 1 that clears FCBEF and launches the complete command. Aborting a command in this way sets the FACCERR access error flag which must be cleared before starting a new command.

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-2 is a flowchart for executing all of the commands except for burst programming and sector erase abort.

4. Wait until the FCCF bit in FSTAT is set. As soon as FCCF= 1, the operation has completed successfully.

Figure 4-2. Program and Erase Flowchart

### 4.5.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the Flash array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the Flash memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When a burst program command is issued, the charge pump is enabled and remains enabled after completion of the burst program operation if these two conditions are met:

- The next burst program command sequence has begun before the FCCF bit is set.

- The next sequential address selects a byte on the same burst block as the current byte being programmed. A burst block in this Flash memory consists of 32 bytes. A new burst block begins at each 32-byte address boundary.

The first byte of a series of sequential bytes being programmed in burst mode will take the same amount of time to program as a byte programmed in standard mode. Subsequent bytes will program in the burst program time provided that the conditions above are met. If the next sequential address is the beginning of a new row, the program time for that byte will be the standard time instead of the burst time. This is because the high voltage to the array must be disabled and then enabled again. If a new burst command has not been queued before the current command completes, then the charge pump will be disabled and high voltage removed from the array.

A flowchart to execute the burst program operation is shown in Figure 4-3.

#### **Chapter 4 Memory**

Reset

This register is loaded from nonvolatile location NVPROT during reset.

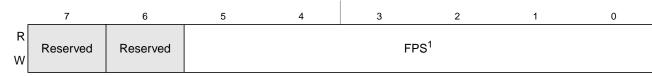

Figure 4-8. Flash Protection Register (FPROT)

**Table 4-12. FPROT Register Field Descriptions**

| Field      | Description                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 5:0<br>FPS | Flash Protect Select Bits — This 6-bit field determines the protected Flash locations that cannot be erased or programmed. See Table 4-13. |

**Table 4-13. Flash Block Protection**

| FPS  | Address Area Protected | Memory Size Protected (bytes) | Number of Sectors Protected |

|------|------------------------|-------------------------------|-----------------------------|

| 0x3F | N/A                    | 0                             | 0                           |

| 0x3E | 0xFA00-0xFFFF          | 1.5K                          | 2                           |

| 0x3D | 0xF400-0xFFFF          | 3К                            | 4                           |

| 0x3C | 0xEE00-0xFFFF          | 4.5K                          | 6                           |

| 0x3B | 0xE800-0xFFFF          | 6K                            | 8                           |

|      |                        |                               |                             |

| 0x37 | 0xD000-0xFFFF          | 12K                           | 16                          |

| 0x36 | 0xCA00-0xFFFF          | 13.5K                         | 18                          |

| 0x35 | 0xC400-0xFFFF          | 15K                           | 20                          |

| 0x34 | 0xBE00-0xFFFF          | 16.5K                         | 22                          |

|      |                        |                               |                             |

| 0x2C | 0x8E00-0xFFFF          | 28.5K                         | 38                          |

| 0x2B | 0x8800-0xFFFF          | 30K                           | 40                          |

| 0x2A | 0x8200-0xFFFF          | 31.5K                         | 42                          |

| 0x29 | 0x7C00-0xFFFF          | 33K                           | 44                          |

|      |                        |                               |                             |

| 0x22 | 0x5200-0xFFFF          | 43.5K                         | 58                          |

| 0x21 | 0x4C00-0xFFFF          | 45K                           | 60                          |

| 0x20 | 0x4600-0xFFFF          | 46.5K                         | 62                          |

| 0x1F | 0x4000-0xFFFF          | 48K                           | 64                          |

|      |                        |                               |                             |

MC9S08DV60 Series Data Sheet, Rev 3

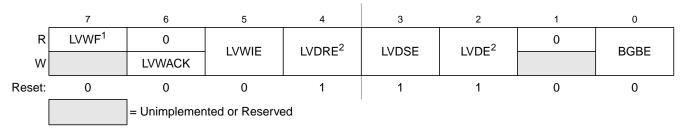

# 5.8.7 System Power Management Status and Control 1 Register (SPMSC1)

This high page register contains status and control bits to support the low-voltage detect function, and to enable the bandgap voltage reference for use by the ADC and ACMP modules. This register should be written during the user's reset initialization program to set the desired controls even if the desired settings are the same as the reset settings.

$<sup>^{1}</sup>$  LVWF will be set in the case when  $V_{Supply}$  transitions below the trip point or after reset and  $V_{Supply}$  is already below  $V_{LVW}$ .

Figure 5-9. System Power Management Status and Control 1 Register (SPMSC1)

| Field       | Description                                                                                                                                                                                                                                                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVWF   | Low-Voltage Warning Flag — The LVWF bit indicates the low-voltage warning status.  0 low-voltage warning is not present.  1 low-voltage warning is present or was present.                                                                                         |

| 6<br>LVWACK | <b>Low-Voltage Warning Acknowledge</b> — If LVWF = 1, a low-voltage condition has occurred. To acknowledge this low-voltage warning, write 1 to LVWACK, which will automatically clear LVWF to 0 if the low-voltage warning is no longer present.                  |

| 5<br>LVWIE  | Low-Voltage Warning Interrupt Enable — This bit enables hardware interrupt requests for LVWF.  0 Hardware interrupt disabled (use polling).  1 Request a hardware interrupt when LVWF = 1.                                                                         |

| 4<br>LVDRE  | Low-Voltage Detect Reset Enable — This write-once bit enables LVD events to generate a hardware reset (provided LVDE = 1).  0 LVD events do not generate hardware resets.  1 Force an MCU reset when an enabled low-voltage detect event occurs.                   |

| 3<br>LVDSE  | Low-Voltage Detect Stop Enable — Provided LVDE = 1, this read/write bit determines whether the low-voltage detect function operates when the MCU is in stop mode.  1 Low-voltage detect disabled during stop mode.  2 Low-voltage detect enabled during stop mode. |

| 2<br>LVDE   | Low-Voltage Detect Enable — This write-once bit enables low-voltage detect logic and qualifies the operation of other bits in this register.  0 LVD logic disabled.  1 LVD logic enabled.                                                                          |

| 0<br>BGBE   | Bandgap Buffer Enable — This bit enables an internal buffer for the bandgap voltage reference for use by the ADC and ACMP modules on one of its internal channels.  0 Bandgap buffer disabled.  1 Bandgap buffer enabled.                                          |

<sup>&</sup>lt;sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

**Chapter 6 Parallel Input/Output Control**

### 6.5.2 Port B Registers

Port B is controlled by the registers listed below.

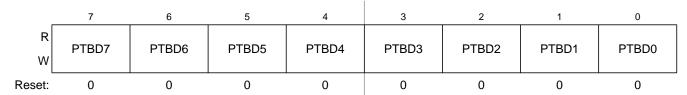

# 6.5.2.1 Port B Data Register (PTBD)

Figure 6-11. Port B Data Register (PTBD)

#### Table 6-9. PTBD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBD[7:0] | Port B Data Register Bits — For port B pins that are inputs, reads return the logic level on the pin. For port B pins that are configured as outputs, reads return the last value written to this register.  Writes are latched into all bits of this register. For port B pins that are configured as outputs, the logic level is driven out the corresponding MCU pin.  Reset forces PTBD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups/pull-downs disabled. |

## 6.5.2.2 Port B Data Direction Register (PTBDD)

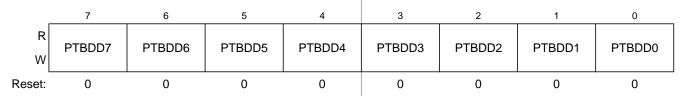

Figure 6-12. Port B Data Direction Register (PTBDD)

### Table 6-10. PTBDD Register Field Descriptions

| Field             | Description                                                                                                                                                                      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBDD[7:0] | <b>Data Direction for Port B Bits</b> — These read/write bits control the direction of port B pins and what is read for PTBD reads.                                              |

|                   | <ul><li>0 Input (output driver disabled) and reads return the pin value.</li><li>1 Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn.</li></ul> |

Chapter 11 Inter-Integrated Circuit (S08IICV2)

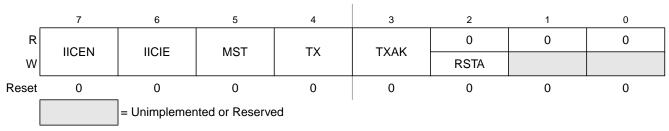

#### **IIC Control Register (IICC1)** 11.3.3

Figure 11-5. IIC Control Register (IICC1)

**Table 11-5. IICC1 Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                                                                                            |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IICEN | IIC Enable. The IICEN bit determines whether the IIC module is enabled.  0 IIC is not enabled 1 IIC is enabled                                                                                                                                                                                                                                                         |

| 6<br>IICIE | IIC Interrupt Enable. The IICIE bit determines whether an IIC interrupt is requested.  0 IIC interrupt request not enabled 1 IIC interrupt request enabled                                                                                                                                                                                                             |

| 5<br>MST   | Master Mode Select. The MST bit changes from a 0 to a 1 when a start signal is generated on the bus and master mode is selected. When this bit changes from a 1 to a 0 a stop signal is generated and the mode of operation changes from master to slave.  O Slave mode  Master mode                                                                                   |

| 4<br>TX    | Transmit Mode Select. The TX bit selects the direction of master and slave transfers. In master mode, this bit should be set according to the type of transfer required. Therefore, for address cycles, this bit is always high. When addressed as a slave, this bit should be set by software according to the SRW bit in the status register.  O Receive  1 Transmit |

| 3<br>TXAK  | Transmit Acknowledge Enable. This bit specifies the value driven onto the SDA during data acknowledge cycles for master and slave receivers.  O An acknowledge signal is sent out to the bus after receiving one data byte  No acknowledge signal response is sent                                                                                                     |

| 2<br>RSTA  | Repeat start. Writing a 1 to this bit generates a repeated start condition provided it is the current master. This bit is always read as cleared. Attempting a repeat at the wrong time results in loss of arbitration.                                                                                                                                                |

MC9S08DV60 Series Data Sheet, Rev 3 204 Freescale Semiconductor

| Table 12-9. CANRFLG Register Field Descriptions (continued) | ster Field Descriptions (continued) |

|-------------------------------------------------------------|-------------------------------------|

|-------------------------------------------------------------|-------------------------------------|

| Field                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>OVRIF            | Overrun Interrupt Flag — This flag is set when a data overrun condition occurs. If not masked, an error interrupt is pending while this flag is set.  O No data overrun condition  A data overrun detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0<br>RXF <sup>2</sup> | Receive Buffer Full Flag — RXF is set by the MSCAN when a new message is shifted in the receiver FIFO. This flag indicates whether the shifted buffer is loaded with a correctly received message (matching identifier, matching cyclic redundancy code (CRC) and no other errors detected). After the CPU has read that message from the RxFG buffer in the receiver FIFO, the RXF flag must be cleared to release the buffer. A set RXF flag prohibits the shifting of the next FIFO entry into the foreground buffer (RxFG). If not masked, a receive interrupt is pending while this flag is set.  No new message available within the RxFG  The receiver FIFO is not empty. A new message is available in the RxFG |

Redundant Information for the most critical CAN bus status which is "bus-off". This only occurs if the Tx error counter exceeds a number of 255 errors. Bus-off affects the receiver state. As soon as the transmitter leaves its bus-off state the receiver state skips to RxOK too. Refer also to TSTAT[1:0] coding in this register.

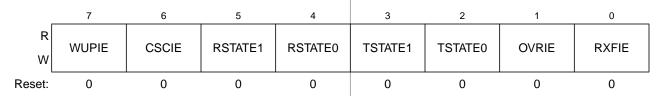

### 12.3.5 MSCAN Receiver Interrupt Enable Register (CANRIER)

This register contains the interrupt enable bits for the interrupt flags described in the CANRFLG register.

Figure 12-9. MSCAN Receiver Interrupt Enable Register (CANRIER)

#### NOTE

The CANRIER register is held in the reset state when the initialization mode is active (INITRQ=1 and INITAK=1). This register is writable when not in initialization mode (INITRQ=0 and INITAK=0).

The RSTATE[1:0], TSTATE[1:0] bits are not affected by initialization mode.

Read: Anytime

Write: Anytime when not in initialization mode

<sup>&</sup>lt;sup>2</sup> To ensure data integrity, do not read the receive buffer registers while the RXF flag is cleared. For MCUs with dual CPUs, reading the receive buffer registers while the RXF flag is cleared may result in a CPU fault condition.

#### Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

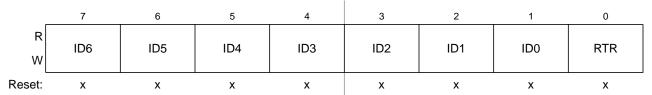

Figure 12-28. Identifier Register 3 (IDR3) — Extended Identifier Mapping

Table 12-28. IDR3 Register Field Descriptions — Extended

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1<br>ID[6:0] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbithation procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                               |

| 0<br>RTR       | Remote Transmission Request — This flag reflects the status of the remote transmission request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.  O Data frame Remote frame |

# 12.4.2 IDR0-IDR3 for Standard Identifier Mapping

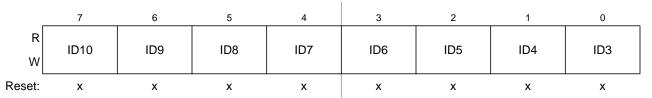

Figure 12-29. Identifier Register 0 — Standard Mapping

Table 12-29. IDR0 Register Field Descriptions — Standard

| Field    | Description                                                                                                       |

|----------|-------------------------------------------------------------------------------------------------------------------|

| 7:0      | Standard Format Identifier — The identifiers consist of 11 bits (ID[10:0]) for the standard format. ID10 is the   |

| ID[10:3] | most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an |

|          | identifier is defined to be highest for the smallest binary number. See also ID bits in Table 12-30.              |

= Unused; always read 'x'

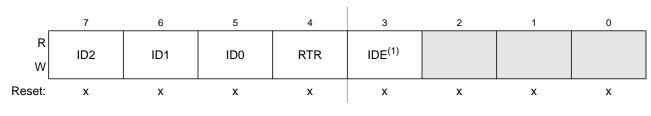

Figure 12-30. Identifier Register 1 — Standard Mapping

#### MC9S08DV60 Series Data Sheet, Rev 3

<sup>&</sup>lt;sup>1</sup> IDE is 0.

|      | Data Byte |      |      |       |  |

|------|-----------|------|------|-------|--|

| DLC3 | DLC2      | DLC1 | DLC0 | Count |  |

| 0    | 0         | 0    | 0    | 0     |  |

| 0    | 0         | 0    | 1    | 1     |  |

| 0    | 0         | 1    | 0    | 2     |  |

| 0    | 0         | 1    | 1    | 3     |  |

| 0    | 1         | 0    | 0    | 4     |  |

| 0    | 1         | 0    | 1    | 5     |  |

| 0    | 1         | 1    | 0    | 6     |  |

| 0    | 1         | 1    | 1    | 7     |  |

| 1    | 0         | 0    | 0    | 8     |  |

Table 12-33. Data Length Codes

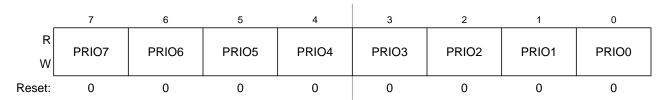

# 12.4.5 Transmit Buffer Priority Register (TBPR)

This register defines the local priority of the associated message transmit buffer. The local priority is used for the internal prioritization process of the MSCAN and is defined to be highest for the smallest binary number. The MSCAN implements the following internal prioritization mechanisms:

- All transmission buffers with a cleared TXEx flag participate in the prioritization immediately before the SOF (start of frame) is sent.

- The transmission buffer with the lowest local priority field wins the prioritization.

In cases of more than one buffer having the same lowest priority, the message buffer with the lower index number wins.

Figure 12-35. Transmit Buffer Priority Register (TBPR)

Read: Anytime when TXEx flag is set (see Section 12.3.6, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 12.3.10, "MSCAN Transmit Buffer Selection Register (CANTBSEL)").

Write: Anytime when TXEx flag is set (see Section 12.3.6, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 12.3.10, "MSCAN Transmit Buffer Selection Register (CANTBSEL)").

### 12.4.6 Time Stamp Register (TSRH-TSRL)

If the TIME bit is enabled, the MSCAN will write a time stamp to the respective registers in the active transmit or receive buffer as soon as a message has been acknowledged on the CAN bus (see

MC9S08DV60 Series Data Sheet, Rev 3

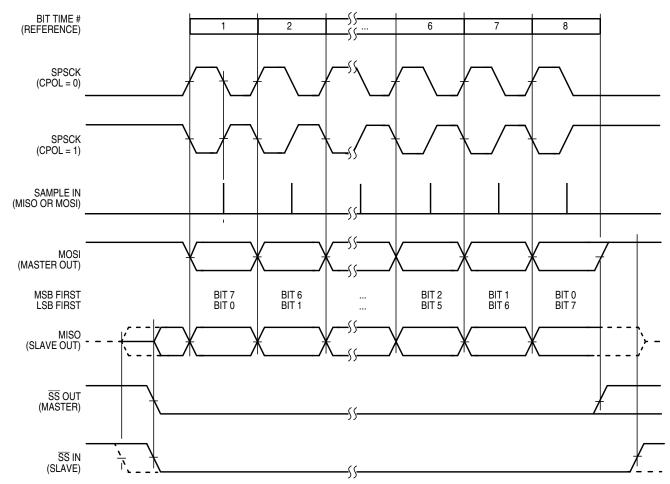

pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low one-half SPSCK cycle before the start of the transfer and goes back high at the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

Figure 13-10. SPI Clock Formats (CPHA = 1)

When CPHA = 1, the slave begins to drive its MISO output when  $\overline{SS}$  goes to active low, but the data is not defined until the first SPSCK edge. The first SPSCK edge shifts the first bit of data from the shifter onto the MOSI output of the master and the MISO output of the slave. The next SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the third SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled, and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CHPA = 1, the slave's  $\overline{SS}$  input is not required to go to its inactive high level between transfers.

Figure 13-11 shows the clock formats when CPHA = 0. At the top of the figure, the eight bit times are shown for reference with bit 1 starting as the slave is selected ( $\overline{SS}$  IN goes low), and bit 8 ends at the last SPSCK edge. The MSB first and LSB first lines show the order of SPI data bits depending on the setting

#### Chapter 14 Serial Communications Interface (S08SCIV4)

flag is set. If RDRF was already set indicating the receive data register (buffer) was already full, the overrun (OR) status flag is set and the new data is lost. Because the SCI receiver is double-buffered, the program has one full character time after RDRF is set before the data in the receive data buffer must be read to avoid a receiver overrun.

When a program detects that the receive data register is full (RDRF = 1), it gets the data from the receive data register by reading SCIxD. The RDRF flag is cleared automatically by a 2-step sequence which is normally satisfied in the course of the user's program that handles receive data. Refer to Section 14.3.4, "Interrupts and Status Flags" for more details about flag clearing.

### 14.3.3.1 Data Sampling Technique

The SCI receiver uses a 16× baud rate clock for sampling. The receiver starts by taking logic level samples at 16 times the baud rate to search for a falling edge on the RxD serial data input pin. A falling edge is defined as a logic 0 sample after three consecutive logic 1 samples. The 16× baud rate clock is used to divide the bit time into 16 segments labeled RT1 through RT16. When a falling edge is located, three more samples are taken at RT3, RT5, and RT7 to make sure this was a real start bit and not merely noise. If at least two of these three samples are 0, the receiver assumes it is synchronized to a receive character.

The receiver then samples each bit time, including the start and stop bits, at RT8, RT9, and RT10 to determine the logic level for that bit. The logic level is interpreted to be that of the majority of the samples taken during the bit time. In the case of the start bit, the bit is assumed to be 0 if at least two of the samples at RT3, RT5, and RT7 are 0 even if one or all of the samples taken at RT8, RT9, and RT10 are 1s. If any sample in any bit time (including the start and stop bits) in a character frame fails to agree with the logic level for that bit, the noise flag (NF) will be set when the received character is transferred to the receive data buffer.

The falling edge detection logic continuously looks for falling edges, and if an edge is detected, the sample clock is resynchronized to bit times. This improves the reliability of the receiver in the presence of noise or mismatched baud rates. It does not improve worst case analysis because some characters do not have any extra falling edges anywhere in the character frame.

In the case of a framing error, provided the received character was not a break character, the sampling logic that searches for a falling edge is filled with three logic 1 samples so that a new start bit can be detected almost immediately.

In the case of a framing error, the receiver is inhibited from receiving any new characters until the framing error flag is cleared. The receive shift register continues to function, but a complete character cannot transfer to the receive data buffer if FE is still set.

### 14.3.3.2 Receiver Wakeup Operation

Receiver wakeup is a hardware mechanism that allows an SCI receiver to ignore the characters in a message that is intended for a different SCI receiver. In such a system, all receivers evaluate the first character(s) of each message, and as soon as they determine the message is intended for a different receiver, they write logic 1 to the receiver wake up (RWU) control bit in SCIxC2. When RWU bit is set, the status flags associated with the receiver (with the exception of the idle bit, IDLE, when RWUID bit is set) are inhibited from setting, thus eliminating the software overhead for handling the unimportant

MC9S08DV60 Series Data Sheet, Rev 3

#### **Appendix A Electrical Characteristics**

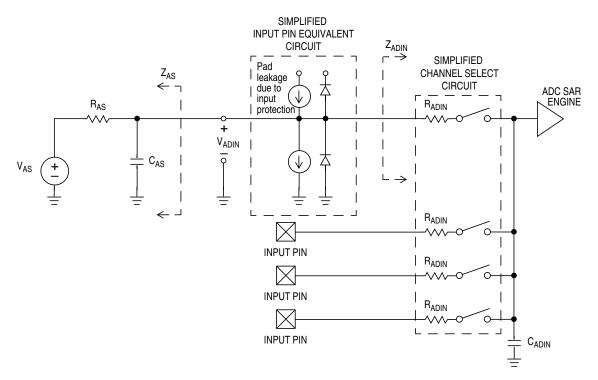

Figure A-1. ADC Input Impedance Equivalency Diagram

Table A-10. 12-bit ADC Characteristics (V<sub>REFH</sub> = V<sub>DDAD</sub>, V<sub>REFL</sub> = V<sub>SSAD</sub>)

| Characteristic               | Conditions                    | С | Symb                                   | Min  | Typ <sup>1</sup> | Max | Unit | Comment              |

|------------------------------|-------------------------------|---|----------------------------------------|------|------------------|-----|------|----------------------|

| Supply Current               | ADLPC=1<br>ADLSMP=1<br>ADCO=1 | Т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 133              | _   | μА   | ADC current only     |

| Supply Current               | ADLPC=1<br>ADLSMP=0<br>ADCO=1 | Т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 218              | _   | μА   | ADC current only     |

| Supply Current               | ADLPC=0<br>ADLSMP=1<br>ADCO=1 | Т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 327              | _   | μА   | ADC current only     |

| Supply Current               | ADLPC=0<br>ADLSMP=0<br>ADCO=1 | D | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 0.582            | 1   | mA   | ADC current only     |

| Supply Current               | Stop, Reset, Module Off       |   | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 0.011            | 1   | μА   | ADC current only     |

| ADC                          | High Speed (ADLPC=0)          | Р | f <sub>ADACK</sub>                     | 2    | 3.3              | 5   | MHz  | t <sub>ADACK</sub> = |

| Asynchronous<br>Clock Source | Low Power (ADLPC=1)           |   |                                        | 1.25 | 2                | 3.3 |      | 1/f <sub>ADACK</sub> |

#### **Appendix A Electrical Characteristics**

#### Table A-12. MCG Frequency Specifications (Temperature Range = -40 to 125°C Ambient) (continued)

| Num | С | Rating                                                                                  | Symbol                        | Min                       | Typical            | Max                                                        | Unit              |

|-----|---|-----------------------------------------------------------------------------------------|-------------------------------|---------------------------|--------------------|------------------------------------------------------------|-------------------|

| 18  | Т | RMS frequency variation of a single clock cycle measured 625 ns after reference edge. 6 | f <sub>pll_cycjit_625ns</sub> | _                         | 0.566 <sup>4</sup> | _                                                          | %f <sub>pll</sub> |

| 19  | Т | Maximum frequency variation averaged over 625 ns window.                                | f <sub>pll_maxjit_625ns</sub> | _                         | 0.113              | _                                                          | %f <sub>pll</sub> |

| 20  | D | Lock entry frequency tolerance <sup>7</sup>                                             | D <sub>lock</sub>             | ± 1.49                    | _                  | ± 2.98                                                     | %                 |

| 21  | D | Lock exit frequency tolerance <sup>8</sup>                                              | D <sub>unl</sub>              | ± 4.47                    | _                  | ± 5.97                                                     | %                 |

| 22  | D | Lock time - FLL                                                                         | t <sub>fil_lock</sub>         | _                         | _                  | t <sub>fll_acquire+</sub><br>1075(1/ <sup>f</sup> int_t)   | s                 |

| 23  | D | Lock time - PLL                                                                         | t <sub>pll_lock</sub>         | _                         | 1                  | t <sub>pll_acquire+</sub><br>1075(1/ <sup>f</sup> pll_ref) | S                 |

| 24  | D | Loss of external clock minimum frequency - RANGE = 0                                    | f <sub>loc_low</sub>          | (3/5) x f <sub>int</sub>  | _                  | _                                                          | kHz               |

| 25  | D | Loss of external clock minimum frequency - RANGE = 1                                    | f <sub>loc_high</sub>         | (16/5) x f <sub>int</sub> | _                  | _                                                          | kHz               |

<sup>&</sup>lt;sup>1</sup> TRIM register at default value (0x80) and FTRIM control bit at default value (0x0).

<sup>&</sup>lt;sup>2</sup> This specification applies to any time the FLL reference source or reference divider is changed, trim value changed or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>BUS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DD</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval. Jitter measurements are based upon a 40MHz MCGOUT clock frequency.

<sup>&</sup>lt;sup>5</sup> In some specifications, this value is described as "long term accuracy of PLL output clock (averaged over 2 ms)" with symbol "f<sub>pll iitter 2ms</sub>." The parameter is unchanged, but the description has been changed for clarification purposes.

In some specifications, this value is described as "Jitter of PLL output clock measured over 625 ns" with symbol "f<sub>pll iitter 625ns</sub>." The parameter is unchanged, but the description has been changed for clarification purposes.

Below D<sub>lock</sub> minimum, the MCG is guaranteed to enter lock. Above D<sub>lock</sub> maximum, the MCG will not enter lock. But if the MCG is already in lock, then the MCG may stay in lock.

<sup>8</sup> Below D<sub>unt</sub> minimum, the MCG will not exit lock if already in lock. Above D<sub>unt</sub> maximum, the MCG is guaranteed to exit lock.

#### **Appendix A Electrical Characteristics**

### A.12.4 SPI

Table A-16 and Figure A-7 through Figure A-10 describe the timing requirements for the SPI system.

**Table A-16. SPI Electrical Characteristic**

| Num <sup>1</sup> | С | Rating <sup>2</sup>                           | Symbol                                   | Min                          | Max                      | Unit             |

|------------------|---|-----------------------------------------------|------------------------------------------|------------------------------|--------------------------|------------------|

| 1                | D | Cycle time<br>Master<br>Slave                 | t <sub>SCK</sub>                         | 2<br>4                       | 2048<br>—                | t <sub>cyc</sub> |

| 2                | D | Enable lead time<br>Master<br>Slave           | t <sub>Lead</sub><br>t <sub>Lead</sub>   | <br>1/2                      | 1/2<br>—                 | t <sub>SCK</sub> |

| 3                | D | Enable lag time<br>Master<br>Slave            | t <sub>Lag</sub><br>t <sub>Lag</sub>     | <br>1/2                      | 1/2<br>—                 | t <sub>SCK</sub> |

| 4                | D | Clock (SPSCK) high time<br>Master and Slave   | t <sub>SCKH</sub>                        | (1/2 t <sub>SCK</sub> )– 25  | _                        | ns               |

| 5                | D | Clock (SPSCK) low time<br>Master and Slave    | t <sub>SCKL</sub>                        | (1/2 t <sub>SCK</sub> ) – 25 | _                        | ns               |

| 6                | D | Data setup time (inputs)  Master Slave        | t <sub>SI(M)</sub><br>t <sub>SI(S)</sub> | 30<br>30                     | _                        | ns<br>ns         |

| 7                | D | Data hold time (inputs)  Master Slave         | t <sub>HI(M)</sub><br>t <sub>HI(S)</sub> | 30<br>30                     |                          | ns<br>ns         |

| 8                | D | Access time, slave <sup>3</sup>               | t <sub>A</sub>                           | 0                            | 40                       | ns               |

| 9                | D | Disable time, slave <sup>4</sup>              | t <sub>dis</sub>                         | _                            | 40                       | ns               |

| 10               | D | Data setup time (outputs)  Master Slave       | t <sub>so</sub>                          | 25<br>25                     | _<br>_                   | ns<br>ns         |

| 11               | D | Data hold time (outputs)  Master Slave        | t <sub>HO</sub>                          | -10<br>-10                   | _<br>_                   | ns<br>ns         |

| 12               | D | Operating frequency <sup>5</sup> Master Slave | f <sub>op</sub><br>f <sub>op</sub>       | f <sub>Bus</sub> /2048<br>dc | 5<br>f <sub>Bus</sub> /4 | MHz              |

Refer to Figure A-7 through Figure A-10.

<sup>&</sup>lt;sup>2</sup> All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins. All timing assumes slew rate control disabled and high drive strength enabled for SPI output pins.

<sup>&</sup>lt;sup>3</sup> Time to data active from high-impedance state.

<sup>&</sup>lt;sup>4</sup> Hold time to high-impedance state.

<sup>&</sup>lt;sup>5</sup> Maximum baud rate must be limited to 5 MHz due to pad input characteristics.

### A.13 Flash

This section provides details about program/erase times and program-erase endurance for the Flash memory.

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see Chapter 4, "Memory."

| Num | С | Rating                                                                                                  | Symbol                  | Min    | Typical | Max  | Unit              |

|-----|---|---------------------------------------------------------------------------------------------------------|-------------------------|--------|---------|------|-------------------|

| 1   | _ | Supply voltage for program/erase                                                                        | V <sub>prog/erase</sub> | 2.7    |         | 5.5  | V                 |

| 2   | _ | Supply voltage for read operation $0 < f_{Bus} < 8 \text{ MHz}$ $0 < f_{Bus} < 20 \text{ MHz}$          | V <sub>Read</sub>       | 2.7    |         | 5.5  | V                 |

| 3   | _ | Internal FCLK frequency <sup>1</sup>                                                                    | f <sub>FCLK</sub>       | 150    |         | 200  | kHz               |

| 4   | _ | Internal FCLK period (1/FCLK)                                                                           | t <sub>Fcyc</sub>       | 5      |         | 6.67 | μs                |

| 5   | _ | Byte program time (random location) <sup>(2)</sup>                                                      | t <sub>prog</sub>       | 9      |         |      | t <sub>Fcyc</sub> |

| 6   | _ | Byte program time (burst mode) <sup>(2)</sup>                                                           | t <sub>Burst</sub>      |        | 4       |      |                   |

| 7   | _ | Page erase time <sup>2</sup>                                                                            | t <sub>Page</sub>       |        | 4000    |      |                   |

| 8   | _ | Mass erase time <sup>(2)</sup>                                                                          | t <sub>Mass</sub>       | 20,000 |         |      | t <sub>Fcyc</sub> |

| 9   | С | Flash Program/erase endurance <sup>3</sup> $T_L$ to $T_H = -40^{\circ}$ C to + 125°C $T = 25^{\circ}$ C | n <sub>FLPE</sub>       | 10,000 | 100,000 | _    | cycles            |

| 10  | С | Data retention <sup>4</sup>                                                                             | t <sub>D_ret</sub>      | 15     | 100     | _    | years             |

Table A-17. Flash Characteristics

### A.14 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

MC9S08DV60 Series Data Sheet, Rev 3

The frequency of this clock is controlled by a software setting.

These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

Typical endurance for Flash is based on the intrinsic bit cell performance. For additional information on how Freescale Semiconductor defines typical endurance, please refer to Engineering Bulletin EB619, Typical Endurance for Nonvolatile Memory.

Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines typical data retention, please refer to Engineering Bulletin EB618, Typical Data Retention for Nonvolatile Memory.

Because the HCS08 is a family of 8-bit MCUs, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers, TPMxMODH, TPMxMODL, TPMxCnVH, and TPMxCnVL, actually write to buffer registers. Values are transferred to the corresponding timer channel registers only after both 8-bit bytes of a 16-bit register have been written and the timer counter overflows (reverses direction from up-counting to down-counting at the end of the terminal count in the modulus register). This TPMxCNT overflow requirement only applies to PWM channels, not output compares.

Optionally, when TPMxCNTH:TPMxCNTL = TPMxMODH:TPMxMODL, the TPM can generate a TOF interrupt at the end of this count. The user can choose to reload any number of the PWM buffers, and they will all update simultaneously at the start of a new period.

Writing to TPMxSC cancels any values written to TPMxMODH and/or TPMxMODL and resets the coherency mechanism for the modulo registers. Writing to TPMxCnSC cancels any values written to the channel value registers and resets the coherency mechanism for TPMxCnVH:TPMxCnVL.

### **B.4** TPM Interrupts

The TPM generates an optional interrupt for the main counter overflow and an interrupt for each channel. The meaning of channel interrupts depends on the mode of operation for each channel. If the channel is configured for input capture, the interrupt flag is set each time the selected input capture edge is recognized. If the channel is configured for output compare or PWM modes, the interrupt flag is set each time the main timer counter matches the value in the 16-bit channel value register. See the Resets, Interrupts, and System Configuration chapter for absolute interrupt vector addresses, priority, and local interrupt mask control bits.

For each interrupt source in the TPM, a flag bit is set on recognition of the interrupt condition such as timer overflow, channel input capture, or output compare events. This flag may be read (polled) by software to verify that the action has occurred, or an associated enable bit (TOIE or CHnIE) can be set to enable hardware interrupt generation. While the interrupt enable bit is set, a static interrupt will be generated whenever the associated interrupt flag equals 1. It is the responsibility of user software to perform a sequence of steps to clear the interrupt flag before returning from the interrupt service routine.

# **B.4.1** Clearing Timer Interrupt Flags

TPM interrupt flags are cleared by a 2-step process that includes a read of the flag bit while it is set (1) followed by a write of 0 to the bit. If a new event is detected between these two steps, the sequence is reset and the interrupt flag remains set after the second step to avoid the possibility of missing the new event.

### **B.4.2** Timer Overflow Interrupt Description

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the 16-bit timer counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction

MC9S08DV60 Series Data Sheet, Rev 3

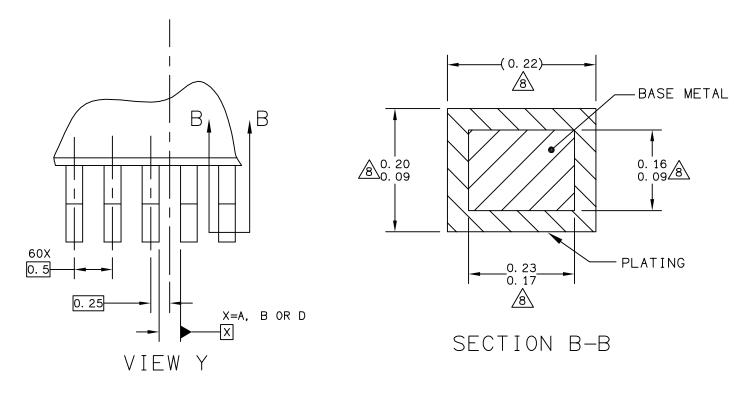

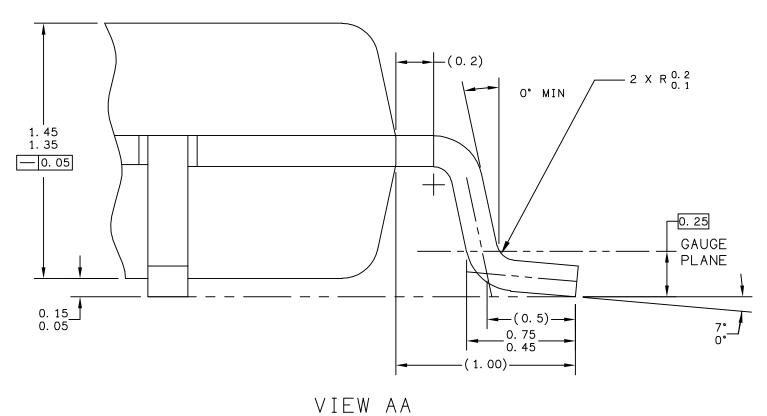

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | L OUTLINE    | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|--------------|------------------|-------------|

| TITLE: 64LD LQFP,                                    | DOCUMENT NO  | ): 98ASS23234W   | REV: E      |

| 10 X 10 X 1.4 P                                      | CASE NUMBER  | 2: 840F-02       | 11 AUG 2006 |

| 0.5 PITCH, CASE OU                                   | STANDARD: JE | DEC MS-026 BCD   |             |