Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 3K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dv60clc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Sec         | ction N | umber Title                                | Page      |

|-------------|---------|--------------------------------------------|-----------|

|             | 6.3.3   | Pull-up/Pull-down Resistors                | 86        |

|             | 6.3.4   | Pin Interrupt Initialization               |           |

| 6.4         |         | navior in Stop Modes                       |           |

| 6.5         |         | I/O and Pin Control Registers              |           |

|             | 6.5.1   | Port A Registers                           |           |

|             | 6.5.2   | Port B Registers                           |           |

|             | 6.5.3   | Port C Registers                           |           |

|             | 6.5.4   | Port D Registers                           |           |

|             | 6.5.5   | Port E Registers                           |           |

|             | 6.5.6   | Port F Registers                           |           |

|             | 6.5.7   | Port G Registers                           | 109       |

|             |         | Chapter 7 Central Processor Unit (S08C     | DI IV3)   |

| 7.1         | Introdu | ction                                      |           |

|             | 7.1.1   | Features                                   |           |

| 7.2         | Progran | nmer's Model and CPU Registers             | 114       |

|             | 7.2.1   | Accumulator (A)                            |           |

|             | 7.2.2   | Index Register (H:X)                       | 114       |

|             | 7.2.3   | Stack Pointer (SP)                         | 115       |

|             | 7.2.4   | Program Counter (PC)                       | 115       |

|             | 7.2.5   | Condition Code Register (CCR)              |           |

| 7.3         | Address | sing Modes                                 |           |

|             | 7.3.1   | Inherent Addressing Mode (INH)             | 117       |

|             | 7.3.2   | Relative Addressing Mode (REL)             |           |

|             | 7.3.3   | Immediate Addressing Mode (IMM)            |           |

|             | 7.3.4   | Direct Addressing Mode (DIR)               |           |

|             | 7.3.5   | Extended Addressing Mode (EXT)             |           |

|             | 7.3.6   | Indexed Addressing Mode                    |           |

| 7.4         |         | Operations                                 |           |

|             | 7.4.1   | Reset Sequence                             |           |

|             | 7.4.2   | Interrupt Sequence                         |           |

|             | 7.4.3   | Wait Mode Operation                        |           |

|             | 7.4.4   | Stop Mode Operation                        |           |

| <b>7.</b> - | 7.4.5   | BGND Instruction                           |           |

| 7.5         | HCS08   | Instruction Set Summary                    | 122       |

|             |         | Chapter 8 Multi-Purpose Clock Generator (S | .08MCGV1) |

| 8.1         | Introdu | ction                                      |           |

|             | 8.1.1   | Features                                   |           |

|             | 8.1.2   | Modes of Operation                         | 137       |

|             |         |                                            |           |

MC9S08DV60 Series Data Sheet, Rev 3

Freescale Semiconductor

Subject to Change

**Chapter 1 Device Overview**

## 4.5.10 Flash Registers and Control Bits

The Flash module has seven 8-bit registers in the high-page register space and three locations in the nonvolatile register space in Flash memory. Two of those locations are copied into two corresponding high-page control registers at reset. There is also an 8-byte comparison key in Flash memory. Refer to Table 4-3 and Table 4-5 for the absolute address assignments for all Flash registers. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

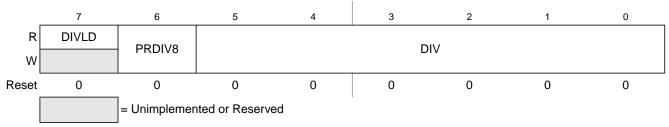

## 4.5.10.1 Flash Clock Divider Register (FCDIV)

Bit 7 of this register is a read-only flag. Bits 6:0 may be read at any time but can be written only one time. Before any erase or programming operations are possible, write to this register to set the frequency of the clock for the nonvolatile memory system within acceptable limits.

Figure 4-5. Flash Clock Divider Register (FCDIV)

Table 4-7. FCDIV Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>DIVLD  | Divisor Loaded Status Flag — When set, this read-only status flag indicates that the FCDIV register has been written since reset. Reset clears this bit and the first write to this register causes this bit to become set regardless of the data written.  0 FCDIV has not been written since reset; erase and program operations disabled for Flash.  1 FCDIV has been written since reset; erase and program operations enabled for Flash.                                                                                                                                                                                  |  |  |  |  |  |  |

| 6<br>PRDIV8 | Prescale (Divide) Flash Clock by 8 (This bit is write once.)  O Clock input to the Flash clock divider is the bus rate clock.  Clock input to the Flash clock divider is the bus rate clock divided by 8.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 5:0<br>DIV  | Divisor for Flash Clock Divider — These bits are write once. The Flash clock divider divides the bus rate clock (or the bus rate clock divided by 8 if PRDIV8 = 1) by the value in the 6-bit DIV field plus one. The resulting frequency of the internal Flash clock must fall within the range of 200 kHz to 150 kHz for proper Flash operations. Program/Erase timing pulses are one cycle of this internal Flash clock which corresponds to a range of 5 μs to 6.7 μs. The automated programming logic uses an integer number of these pulses to complete an erase or program operation. See Equation 4-1 and Equation 4-2. |  |  |  |  |  |  |

if PRDIV8 =

$$0 - f_{FCLK} = f_{Bus} \div (DIV + 1)$$

Eqn. 4-1

if PRDIV8 =  $1 - f_{FCLK} = f_{Bus} \div (8 \times (DIV + 1))$  Eqn. 4-2

Table 4-8 shows the appropriate values for PRDIV8 and DIV for selected bus frequencies.

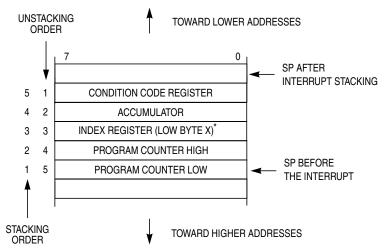

## 5.5 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it left off before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on the IRQ pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

If an event occurs in an enabled interrupt source, an associated read-only status flag will become set. The CPU will not respond unless the local interrupt enable is a 1 to enable the interrupt and the I bit in the CCR is 0 to allow interrupts. The global interrupt mask (I bit) in the CCR is initially set after reset which prevents all maskable interrupt sources. The user program initializes the stack pointer and performs other system setup before clearing the I bit to allow the CPU to respond to interrupts.

When the CPU receives a qualified interrupt request, it completes the current instruction before responding to the interrupt. The interrupt sequence obeys the same cycle-by-cycle sequence as the SWI instruction and consists of:

- Saving the CPU registers on the stack

- Setting the I bit in the CCR to mask further interrupts

- Fetching the interrupt vector for the highest-priority interrupt that is currently pending

- Filling the instruction queue with the first three bytes of program information starting from the address fetched from the interrupt vector locations

While the CPU is responding to the interrupt, the I bit is automatically set to avoid the possibility of another interrupt interrupting the ISR itself (this is called nesting of interrupts). Normally, the I bit is restored to 0 when the CCR is restored from the value stacked on entry to the ISR. In rare cases, the I bit can be cleared inside an ISR (after clearing the status flag that generated the interrupt) so that other interrupts can be serviced without waiting for the first service routine to finish. This practice is not recommended for anyone other than the most experienced programmers because it can lead to subtle program errors that are difficult to debug.

The interrupt service routine ends with a return-from-interrupt (RTI) instruction which restores the CCR, A, X, and PC registers to their pre-interrupt values by reading the previously saved information from the stack.

### **NOTE**

For compatibility with M68HC08 devices, the H register is not automatically saved and restored. It is good programming practice to push H onto the stack at the start of the interrupt service routine (ISR) and restore it immediately before the RTI that is used to return from the ISR.

If more than one interrupt is pending when the I bit is cleared, the highest priority source is serviced first (see Table 5-1).

Chapter 5 Resets, Interrupts, and General System Control

## 5.5.1 Interrupt Stack Frame

Figure 5-1 shows the contents and organization of a stack frame. Before the interrupt, the stack pointer (SP) points at the next available byte location on the stack. The current values of CPU registers are stored on the stack starting with the low-order byte of the program counter (PCL) and ending with the CCR. After stacking, the SP points at the next available location on the stack which is the address that is one less than the address where the CCR was saved. The PC value that is stacked is the address of the instruction in the main program that would have executed next if the interrupt had not occurred.

<sup>\*</sup> High byte (H) of index register is not automatically stacked

Figure 5-1. Interrupt Stack Frame

When an RTI instruction is executed, these values are recovered from the stack in reverse order. As part of the RTI sequence, the CPU fills the instruction pipeline by reading three bytes of program information, starting from the PC address recovered from the stack.

The status flag corresponding to the interrupt source must be acknowledged (cleared) before returning from the ISR. Typically, the flag is cleared at the beginning of the ISR so that if another interrupt is generated by this same source, it will be registered so it can be serviced after completion of the current ISR.

# 5.5.2 External Interrupt Request (IRQ) Pin

External interrupts are managed by the IRQ status and control register, IRQSC. When the IRQ function is enabled, synchronous logic monitors the pin for edge-only or edge-and-level events. When the MCU is in stop mode and system clocks are shut down, a separate asynchronous path is used so the IRQ (if enabled) can wake the MCU.

# 5.5.2.1 Pin Configuration Options

The IRQ pin enable (IRQPE) control bit in IRQSC must be 1 in order for the IRQ pin to act as the interrupt request (IRQ) input. As an IRQ input, the user can choose the polarity of edges or levels detected (IRQEDG), whether the pin detects edges-only or edges and levels (IRQMOD), and whether an event causes an interrupt or only sets the IRQF flag which can be polled by software.

**Chapter 6 Parallel Input/Output Control**

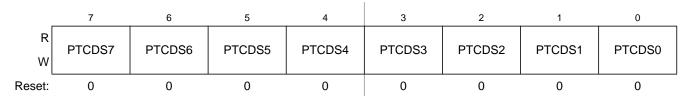

## 6.5.3.5 Port C Drive Strength Selection Register (PTCDS)

Figure 6-23. Drive Strength Selection for Port C Register (PTCDS)

**Table 6-21. PTCDS Register Field Descriptions**

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Output Drive Strength Selection for Port C Bits — Each of these control bits selects between low and high output drive for the associated PTC pin. For port C pins that are configured as inputs, these bits have no effect.  1 Use the control bits selects between low and high output drive strength selected for port C bit n.  2 Use the control bits selects between low and high output drive strength selected for port C bit n. |

### Chapter 7 Central Processor Unit (S08CPUV3)

Table 7-2. Instruction Set Summary (Sheet 7 of 9)

| Source                                                                                                          | Operation                                                                                                                                                                                                                                | Address                                      | Object Code                                                             | Cycles                          | Cyc-by-Cyc                           | Affect on CCR |                |  |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------|---------------------------------|--------------------------------------|---------------|----------------|--|

| Form                                                                                                            |                                                                                                                                                                                                                                          | Adc                                          |                                                                         | င်                              | Details                              | V 1 1 H       | INZC           |  |

| RSP                                                                                                             | Reset Stack Pointer (Low Byte) SPL ← \$FF (High Byte Not Affected)                                                                                                                                                                       | INH                                          | 9C                                                                      | 1                               | р                                    | - 1 1 -       |                |  |

| RTI                                                                                                             | Return from Interrupt $SP \leftarrow (SP) + \$0001$ ; Pull (CCR) $SP \leftarrow (SP) + \$0001$ ; Pull (A) $SP \leftarrow (SP) + \$0001$ ; Pull (X) $SP \leftarrow (SP) + \$0001$ ; Pull (PCH) $SP \leftarrow (SP) + \$0001$ ; Pull (PCL) | INH                                          | 80                                                                      | 9                               | uuuuufppp                            | \$ 1 1 \$     | <b>‡</b> ‡ ‡ ‡ |  |

| RTS                                                                                                             | Return from Subroutine<br>SP ← SP + \$0001; Pull (PCH)<br>SP ← SP + \$0001; Pull (PCL)                                                                                                                                                   | INH                                          | 81                                                                      | 5                               | ufppp                                | - 1 1 -       |                |  |

| SBC #opr8i<br>SBC opr8a<br>SBC opr16a<br>SBC oprx16,X<br>SBC oprx8,X<br>SBC ,X<br>SBC oprx16,SP<br>SBC oprx8,SP | Subtract with Carry $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                       | IMM DIR EXT IX2 IX1 IX SP2 SP1               | A2 ii B2 dd C2 hh ll D2 ee ff E2 ff F2 9E D2 ee ff 9E E2 ff             | 2<br>3<br>4<br>4<br>3<br>5<br>4 | pp rpp prpp rfp pprpp prpp           | ↑ 1 1 -       | - 1 1          |  |

| SEC                                                                                                             | Set Carry Bit (C ← 1)                                                                                                                                                                                                                    | INH                                          | 99                                                                      | 1                               | р                                    | - 1 1 -       | 1              |  |

| SEI                                                                                                             | Set Interrupt Mask Bit (I ← 1)                                                                                                                                                                                                           | INH                                          | 9В                                                                      | 1                               | р                                    | - 1 1 -       | 1 – – –        |  |

| STA opr8a<br>STA opr16a<br>STA oprx16,X<br>STA oprx8,X<br>STA ,X<br>STA oprx16,SP<br>STA oprx8,SP               | Store Accumulator in Memory $M \leftarrow (A)$                                                                                                                                                                                           | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | B7 dd<br>C7 hh ll<br>D7 ee ff<br>E7 ff<br>F7<br>9E D7 ee ff<br>9E E7 ff | 3<br>4<br>4<br>3<br>2<br>5<br>4 | bwbb<br>bbwbb<br>wbb<br>bwbb<br>bwbb | 0 1 1 –       | - \$ \$ -      |  |

| STHX opr8a<br>STHX opr16a<br>STHX oprx8,SP                                                                      | Store H:X (Index Reg.)<br>(M:M + \$0001) ← (H:X)                                                                                                                                                                                         | DIR<br>EXT<br>SP1                            | 35 dd<br>96 hh 11<br>9E FF ff                                           | 4<br>5<br>5                     | pwwpp<br>pwwpp                       | 0 1 1 -       | - \$ \$ -      |  |

| STOP                                                                                                            | Enable Interrupts: Stop Processing Refer to MCU Documentation I bit ← 0; Stop Processing                                                                                                                                                 | INH                                          | 8E                                                                      | 2                               | fp                                   | - 1 1 -       | 0              |  |

| STX opr8a<br>STX opr16a<br>STX oprx16,X<br>STX oprx8,X<br>STX ,X<br>STX oprx16,SP<br>STX oprx8,SP               | Store X (Low 8 Bits of Index Register) in Memory $\mathbf{M} \leftarrow (\mathbf{X})$                                                                                                                                                    | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | BF dd<br>CF hh ll<br>DF ee ff<br>EF ff<br>FF<br>9E DF ee ff<br>9E EF ff | 3<br>4<br>4<br>3<br>2<br>5<br>4 | bwbb<br>bbwbb<br>wbb<br>bwbb<br>bwbb | 0 1 1 -       | - \$ \$ -      |  |

### 10.1.6 Features

Features of the ADC module include:

- Linear successive approximation algorithm with 12-bit resolution

- Up to 28 analog inputs

- Output formatted in 12-, 10-, or 8-bit right-justified unsigned format

- Single or continuous conversion (automatic return to idle after single conversion)

- Configurable sample time and conversion speed/power

- Conversion complete flag and interrupt

- Input clock selectable from up to four sources

- Operation in wait or stop3 modes for lower noise operation

- Asynchronous clock source for lower noise operation

- Selectable asynchronous hardware conversion trigger

- Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value

- Temperature sensor

## 10.1.7 ADC Module Block Diagram

Figure 10-2 provides a block diagram of the ADC module.

#### Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

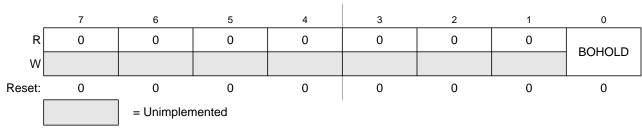

Figure 12-16. MSCAN Miscellaneous Register (CANMISC)

Read: Anytime

Write: Anytime; write of '1' clears flag; write of '0' ignored

**Table 12-19. CANMISC Register Field Descriptions**

| Field  | Description                                                                                                    |  |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0      | Bus-off State Hold Until User Request — If BORM is set in Section 12.3.2, "MSCAN Control Register 1            |  |  |  |  |  |

| BOHOLD | (CANCTL1), this bit indicates whether the module has entered the bus-off state. Clearing this bit requests the |  |  |  |  |  |

|        | recovery from bus-off. Refer to Section 12.6.2, "Bus-Off Recovery," for details.                               |  |  |  |  |  |

|        | 0 Module is not bus-off or recovery has been requested by user in bus-off state                                |  |  |  |  |  |

|        | 1 Module is bus-off and holds this state until user request                                                    |  |  |  |  |  |

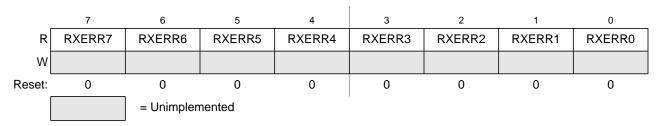

## 12.3.13 MSCAN Receive Error Counter (CANRXERR)

This register reflects the status of the MSCAN receive error counter.

Figure 12-17. MSCAN Receive Error Counter (CANRXERR)

Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1)

Write: Unimplemented

### **NOTE**

Reading this register when in any other mode other than sleep or initialization mode may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

Writing to this register when in special modes can alter the MSCAN functionality.

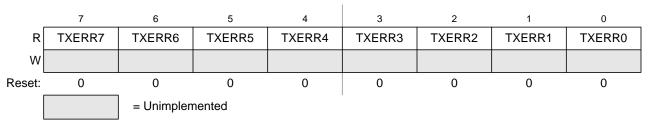

## 12.3.14 MSCAN Transmit Error Counter (CANTXERR)

This register reflects the status of the MSCAN transmit error counter.

Figure 12-18. MSCAN Transmit Error Counter (CANTXERR)

Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1)

Write: Unimplemented

### **NOTE**

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

Writing to this register when in special modes can alter the MSCAN functionality.

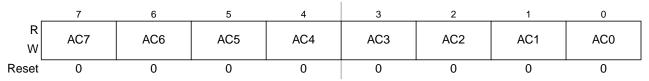

# 12.3.15 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0–IDR3 registers (see Section 12.4.1, "Identifier Registers (IDR0–IDR3)") of incoming messages in a bit by bit manner (see Section 12.5.3, "Identifier Acceptance Filter").

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

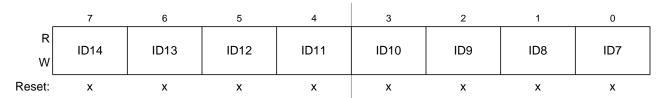

Figure 12-19. MSCAN Identifier Acceptance Registers (First Bank) — CANIDAR0-CANIDAR3

Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

### Table 12-25. IDR0 Register Field Descriptions — Extended

| Field            | Description                                                                                                                                                                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>ID[28:21] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. |

| _      | 7    | 6    | 5    | 4                  | 3                  | 2    | 1    | 0    |

|--------|------|------|------|--------------------|--------------------|------|------|------|

| R<br>W | ID20 | ID19 | ID18 | SRR <sup>(1)</sup> | IDE <sup>(1)</sup> | ID17 | ID16 | ID15 |

| Reset: | Х    | Х    | Х    | Х                  | Х                  | Х    | Х    | x    |

Figure 12-26. Identifier Register 1 (IDR1) — Extended Identifier Mapping

### Table 12-26. IDR1 Register Field Descriptions — Extended

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5<br>ID[20:18] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                                                   |

| 4<br>SRR         | Substitute Remote Request — This fixed recessive bit is used only in extended format. It must be set to 1 by the user for transmission buffers and is stored as received on the CAN bus for receive buffers.                                                                                                                                                                                                   |

| 3<br>IDE         | ID Extended — This flag indicates whether the extended or standard identifier format is applied in this buffer. In the case of a receive buffer, the flag is set as received and indicates to the CPU how to process the buffer identifier registers. In the case of a transmit buffer, the flag indicates to the MSCAN what type of identifier to send.  O Standard format (11 bit)  Extended format (29 bit) |

| 2:0<br>ID[17:15] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                                                   |

Figure 12-27. Identifier Register 2 (IDR2) — Extended Identifier Mapping

### Table 12-27. IDR2 Register Field Descriptions — Extended

| Field           | Description                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>ID[14:7] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. |

### MC9S08DV60 Series Data Sheet, Rev 3

<sup>&</sup>lt;sup>1</sup> SRR and IDE are both 1s.

### 12.5.5.5 MSCAN Initialization Mode

In initialization mode, any on-going transmission or reception is immediately aborted and synchronization to the CAN bus is lost, potentially causing CAN protocol violations. To protect the CAN bus system from fatal consequences of violations, the MSCAN immediately drives the TXCAN pin into a recessive state.

#### NOTE

The user is responsible for ensuring that the MSCAN is not active when initialization mode is entered. The recommended procedure is to bring the MSCAN into sleep mode (SLPRQ = 1 and SLPAK = 1) before setting the INITRQ bit in the CANCTL0 register. Otherwise, the abort of an on-going message can cause an error condition and can impact other CAN bus devices.

In initialization mode, the MSCAN is stopped. However, interface registers remain accessible. This mode is used to reset the CANCTL0, CANRFLG, CANRIER, CANTFLG, CANTIER, CANTARQ, CANTAAK, and CANTBSEL registers to their default values. In addition, the MSCAN enables the configuration of the CANBTR0, CANBTR1 bit timing registers; CANIDAC; and the CANIDAR, CANIDMR message filters. See Section 12.3.1, "MSCAN Control Register 0 (CANCTL0)," for a detailed description of the initialization mode.

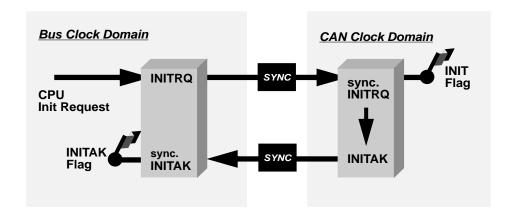

Figure 12-46. Initialization Request/Acknowledge Cycle

Due to independent clock domains within the MSCAN, INITRQ must be synchronized to all domains by using a special handshake mechanism. This handshake causes additional synchronization delay (see Section Figure 12-46., "Initialization Request/Acknowledge Cycle").

If there is no message transfer ongoing on the CAN bus, the minimum delay will be two additional bus clocks and three additional CAN clocks. When all parts of the MSCAN are in initialization mode, the INITAK flag is set. The application software must use INITAK as a handshake indication for the request (INITRQ) to go into initialization mode.

#### NOTE

The CPU cannot clear INITRQ before initialization mode (INITRQ = 1 and INITAK = 1) is active.

MC9S08DV60 Series Data Sheet, Rev 3

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

Section 12.3.4.1, "MSCAN Receiver Flag Register (CANRFLG)" and Section 12.3.5, "MSCAN Receiver Interrupt Enable Register (CANRIER)").

## 12.5.7.6 Interrupt Acknowledge

Interrupts are directly associated with one or more status flags in either the Section 12.3.4.1, "MSCAN Receiver Flag Register (CANRFLG)" or the Section 12.3.6, "MSCAN Transmitter Flag Register (CANTFLG)." Interrupts are pending as long as one of the corresponding flags is set. The flags in CANRFLG and CANTFLG must be reset within the interrupt handler to handshake the interrupt. The flags are reset by writing a 1 to the corresponding bit position. A flag cannot be cleared if the respective condition prevails.

#### NOTE

It must be guaranteed that the CPU clears only the bit causing the current interrupt. For this reason, bit manipulation instructions (BSET) must not be used to clear interrupt flags. These instructions may cause accidental clearing of interrupt flags which are set after entering the current interrupt service routine.

## 12.5.7.7 Recovery from Stop or Wait

The MSCAN can recover from stop or wait via the wake-up interrupt. This interrupt can only occur if the MSCAN was in sleep mode (SLPRQ = 1 and SLPAK = 1) before entering power down mode, the wake-up option is enabled (WUPE = 1), and the wake-up interrupt is enabled (WUPE = 1).

# 12.6 Initialization/Application Information

### 12.6.1 MSCAN initialization

The procedure to initially start up the MSCAN module out of reset is as follows:

- Assert CANE

- 2. Write to the configuration registers in initialization mode

- 3. Clear INITRQ to leave initialization mode and enter normal mode

If the configuration of registers which are writable in initialization mode needs to be changed only when the MSCAN module is in normal mode:

- 1. Bring the module into sleep mode by setting SLPRQ and awaiting SLPAK to assert after the CAN bus becomes idle.

- 2. Enter initialization mode: assert INITRQ and await INITAK

- 3. Write to the configuration registers in initialization mode

- 4. Clear INITRQ to leave initialization mode and continue in normal mode

#### 13.5.2 **SPI Interrupts**

There are three flag bits, two interrupt mask bits, and one interrupt vector associated with the SPI system. The SPI interrupt enable mask (SPIE) enables interrupts from the SPI receiver full flag (SPRF) and mode fault flag (MODF). The SPI transmit interrupt enable mask (SPTIE) enables interrupts from the SPI transmit buffer empty flag (SPTEF). When one of the flag bits is set, and the associated interrupt mask bit is set, a hardware interrupt request is sent to the CPU. If the interrupt mask bits are cleared, software can poll the associated flag bits instead of using interrupts. The SPI interrupt service routine (ISR) should check the flag bits to determine what event caused the interrupt. The service routine should also clear the flag bit(s) before returning from the ISR (usually near the beginning of the ISR).

#### 13.5.3 Mode Fault Detection

A mode fault occurs and the mode fault flag (MODF) becomes set when a master SPI device detects an error on the  $\overline{SS}$  pin (provided the  $\overline{SS}$  pin is configured as the mode fault input signal). The  $\overline{SS}$  pin is configured to be the mode fault input signal when MSTR = 1, mode fault enable is set (MODFEN = 1), and slave select output enable is clear (SSOE = 0).

The mode fault detection feature can be used in a system where more than one SPI device might become a master at the same time. The error is detected when a master's  $\overline{SS}$  pin is low, indicating that some other SPI device is trying to address this master as if it were a slave. This could indicate a harmful output driver conflict, so the mode fault logic is designed to disable all SPI output drivers when such an error is detected.

When a mode fault is detected, MODF is set and MSTR is cleared to change the SPI configuration back to slave mode. The output drivers on the SPSCK, MOSI, and MISO (if not bidirectional mode) are disabled.

MODF is cleared by reading it while it is set, then writing to the SPI control register 1 (SPIC1). User software should verify the error condition has been corrected before changing the SPI back to master mode.

### Chapter 15 Real-Time Counter (S08RTCV1)

```

#pragma TRAP_PROC

void RTC_ISR(void)

/* Clear the interrupt flag */

RTCSC.byte = RTCSC.byte | 0x80;

/* RTC interrupts every 1 Second */

Seconds++;

/* 60 seconds in a minute */

if (Seconds > 59){

Minutes++;

Seconds = 0;

/* 60 minutes in an hour */

if (Minutes > 59){

Hours++;

Minutes = 0;

/* 24 hours in a day */

if (Hours > 23){

Days ++;

Hours = 0;

}

```

MC9S08DV60 Series Data Sheet, Rev 3

Freescale Semiconductor 315

Chapter 16 Timer/PWM Module (S08TPMV3)

## 16.4.1.3 Counting Modes

The main timer counter has two counting modes. When center-aligned PWM is selected (CPWMS=1), the counter operates in up/down counting mode. Otherwise, the counter operates as a simple up counter. As an up counter, the timer counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

When center-aligned PWM operation is specified, the counter counts up from 0x0000 through its terminal count and then down to 0x0000 where it changes back to up counting. Both 0x0000 and the terminal count value are normal length counts (one timer clock period long). In this mode, the timer overflow flag (TOF) becomes set at the end of the terminal-count period (as the count changes to the next lower count value).

### 16.4.1.4 Manual Counter Reset

The main timer counter can be manually reset at any time by writing any value to either half of TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only half of the counter was read before resetting the count.

### 16.4.2 Channel Mode Selection

Provided CPWMS=0, the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and edge-aligned PWM.

## 16.4.2.1 Input Capture Mode

With the input-capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input-capture channel, the TPM latches the contents of the TPM counter into the channel-value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

In input capture mode, the TPMxCnVH and TPMxCnVL registers are read only.

When either half of the 16-bit capture register is read, the other half is latched into a buffer to support coherent 16-bit accesses in big-endian or little-endian order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An input capture event sets a flag bit (CHnF) which may optionally generate a CPU interrupt request.

While in BDM, the input capture function works as configured by the user. When an external event occurs, the TPM latches the contents of the TPM counter (which is frozen because of the BDM mode) into the channel value registers and sets the flag bit.

# 16.4.2.2 Output Compare Mode

With the output-compare function, the TPM can generate timed pulses with programmable position, polarity, duration, and frequency. When the counter reaches the value in the channel-value registers of an output-compare channel, the TPM can set, clear, or toggle the channel pin.

MC9S08DV60 Series Data Sheet, Rev 3

TPM counter changes from (TPMxMODH:L - 1) to (TPMxMODH:L). If the TPM counter is a free-running counter, then this update is made when the TPM counter changes from \$FFFE to \$FFFF. Instead, the TPM v2 makes this update after that the both bytes were written and when the TPM counter changes from TPMxMODH:L to \$0000.

- Center-Aligned PWM (Section 16.4.2.4, "Center-Aligned PWM Mode) In this mode and if (CLKSB:CLKSA not = 00), the TPM v3 updates the TPMxCnVH:L registers with the value of their write buffer after that the both bytes were written and when the TPM counter changes from (TPMxMODH:L - 1) to (TPMxMODH:L). If the TPM counter is a free-running counter, then this update is made when the TPM counter changes from \$FFFE to \$FFFF. Instead, the TPM v2 makes this update after that the both bytes were written and when the TPM counter changes from TPMxMODH:L to (TPMxMODH:L - 1).

- 5. Center-Aligned PWM (Section 16.4.2.4, "Center-Aligned PWM Mode)

- TPMxCnVH:L = TPMxMODH:L [SE110-TPM case 1] In this case, the TPM v3 produces 100% duty cycle. Instead, the TPM v2 produces 0% duty cycle.

- TPMxCnVH:L = (TPMxMODH:L 1) [SE110-TPM case 2] In this case, the TPM v3 produces almost 100% duty cycle. Instead, the TPM v2 produces 0% duty cycle.

- TPMxCnVH:L is changed from 0x0000 to a non-zero value [SE110-TPM case 3 and 5] In this case, the TPM v3 waits for the start of a new PWM period to begin using the new duty cycle setting. Instead, the TPM v2 changes the channel output at the middle of the current PWM period (when the count reaches 0x0000).

- TPMxCnVH:L is changed from a non-zero value to 0x0000 [SE110-TPM case 4] In this case, the TPM v3 finishes the current PWM period using the old duty cycle setting. Instead, the TPM v2 finishes the current PWM period using the new duty cycle setting.

- 6. Write to TPMxMODH:L registers in BDM mode (Section 16.3.3, "TPM Counter Modulo Registers (TPMxMODH:TPMxMODL))

- In the TPM v3 a write to TPMxSC register in BDM mode clears the write coherency mechanism of TPMxMODH:L registers. Instead, in the TPM v2 this coherency mechanism is not cleared when there is a write to TPMxSC register.

- 7. Update of EPWM signal when CLKSB:CLKSA = 00

- In the TPM v3 if CLKSB:CLKSA = 00, then the EPWM signal in the channel output is not update (it is frozen while CLKSB:CLKSA = 00). Instead, in the TPM v2 the EPWM signal is updated at the next rising edge of bus clock after a write to TPMxCnSC register.

- The Figure 0-1 and Figure 0-2 show when the EPWM signals generated by TPM v2 and TPM v3 after the reset (CLKSB:CLKSA = 00) and if there is a write to TPMxCnSC register.

#### **Appendix A Electrical Characteristics**

- <sup>3</sup> Monotonicity and No-Missing-Codes guaranteed in 10 bit and 8 bit modes

- <sup>4</sup> Based on input pad leakage current. Refer to pad electricals.

# A.10 External Oscillator (XOSC) Characteristics

Table A-11. Oscillator Electrical Specifications (Temperature Range = -40 to 125°C Ambient)

| Num | С | Rating                                                     | Symbol              | Min                                                | Typ <sup>1</sup> | Max       | Unit    |   |  |

|-----|---|------------------------------------------------------------|---------------------|----------------------------------------------------|------------------|-----------|---------|---|--|

|     |   | Oscillator crystal or resonator (EREFS = 1, ERCLKEN = 1    | •                   |                                                    |                  |           | •       |   |  |

|     |   | Low range (RANGE = 0)                                      | f <sub>lo</sub>     | 32                                                 | _                | 38.4      | kHz     |   |  |

|     | С | High range (RANGE = 1) FEE or FBE mode <sup>2</sup>        | f <sub>hi-fil</sub> | 1                                                  | _                | 5         | MHz     |   |  |

| 1   |   | High range (RANGE = 1) PEE or PBE mode <sup>3</sup>        | f <sub>hi-pll</sub> | 1                                                  | _                | 16        | MHz     |   |  |

|     |   | High range (RANGE = 1, HGO = 1) BLPE mode                  | f <sub>hi-hgo</sub> | 1                                                  | _                | 16        | MHz     |   |  |

|     |   | High range (RANGE = 1, HGO = 0) BLPE mode                  | f <sub>hi-lp</sub>  | 1                                                  | _                | 8         | MHz     |   |  |

| 2   |   | I and compaiters                                           | C <sub>1</sub>      | See                                                | crystal c        | r resonat | or      |   |  |

|     |   | Load capacitors                                            | C <sub>2</sub>      | manufact                                           | urer's re        | commen    | dation. |   |  |

|     |   | Feedback resistor                                          |                     |                                                    |                  |           |         |   |  |

| 3   | _ | Low range (32 kHz to 100 kHz)                              | R <sub>F</sub>      | _                                                  | 10               | _         | MΩ      |   |  |

|     |   | High range (1 MHz to 16 MHz)                               |                     |                                                    | 1                |           | МΩ      |   |  |

|     |   | Series resistor                                            |                     |                                                    |                  |           |         |   |  |

|     | _ | Low range, low gain (RANGE = 0, HGO = 0)                   |                     | _                                                  | 0                |           |         |   |  |

|     |   | Low range, high gain (RANGE = 0, HGO = 1)                  |                     | _                                                  | 100              | _         |         |   |  |

| 4   |   | High range, low gain (RANGE = 1, HGO = 0)                  | R <sub>S</sub>      | _                                                  | 0                | _         | kΩ      |   |  |

|     |   |                                                            |                     | High range, high gain (RANGE = 1, HGO = 1) ≥ 8 MHz |                  |           | 0       | 0 |  |

|     |   | 4 MHz                                                      |                     | -                                                  | 0                | 10        |         |   |  |

|     |   | 1 MHz                                                      |                     | _                                                  | 0                | 20        |         |   |  |

|     |   | Crystal start-up time <sup>4</sup>                         |                     |                                                    |                  |           |         |   |  |

|     |   | Low range, low gain (RANGE = 0, HGO = 0)                   | t<br>CSTL-LP        | _                                                  | 200              | _         |         |   |  |

| 5   | Т | Low range, high gain (RANGE = 0, HGO = 1)                  | t<br>CSTL-HGO       | _                                                  | 400              |           |         |   |  |

|     |   | High range, low gain (RANGE = 1, HGO = 0) <sup>5</sup>     | t<br>CSTH-LP        | _                                                  | 5                |           | ms      |   |  |

|     |   | High range, high gain (RANGE = 1, HGO = 1) <sup>4</sup>    | t<br>CSTH-HGO       | _                                                  | 15               | _         |         |   |  |

|     |   | Square wave input clock frequency (EREFS = 0, ERCLKEN = 1) |                     |                                                    |                  |           |         |   |  |

| 6   | Т | FEE or FBE mode <sup>2</sup>                               |                     | 0.03125                                            |                  | 5         |         |   |  |

|     |   | PEE or PBE mode <sup>3</sup>                               | f <sub>extal</sub>  | 1                                                  | _                | 16        | MHz     |   |  |

|     |   | BLPE mode                                                  |                     | 0                                                  | _                | 40        |         |   |  |

<sup>&</sup>lt;sup>1</sup> Typical data was characterized at 3.0 V, 25°C or is recommended value.

When MCG is configured for FEE or FBE mode, the input clock source must be divisible using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

When MCG is configured for PEE or PBE mode, input clock source must be divisible using RDIV to within the range of 1 MHz to 2 MHz.

This parameter is characterized and not tested on each device. Proper PC board layout procedures must be followed to achieve specifications. This data will vary based upon the crystal manufacturer and board design. The crystal should be characterized by the crystal manufacturer.

<sup>&</sup>lt;sup>5</sup> 4 MHz crystal.

### **Appendix A Electrical Characteristics**

1. Not defined but normally MSB of character just received

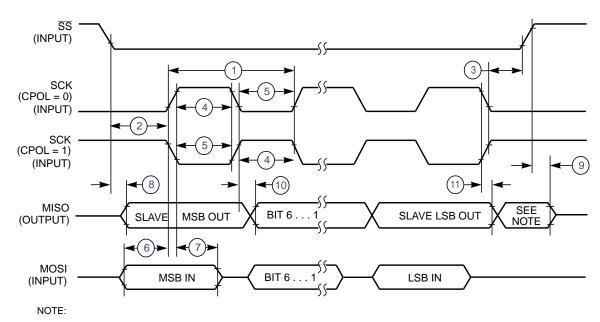

Figure A-9. SPI Slave Timing (CPHA = 0)

1. Not defined but normally LSB of character just received

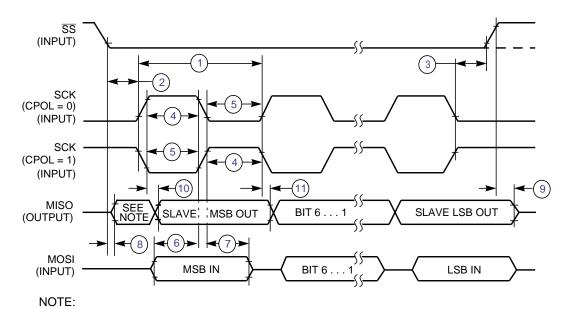

Figure A-10. SPI Slave Timing (CPHA = 1)

### **Appendix C Ordering Information and Mechanical Drawings**

## **Table C-2. Package Descriptions**

| Pin Count | Туре                  | Abbreviation | Designator | Document No. |

|-----------|-----------------------|--------------|------------|--------------|

| 64        | Low Quad Flat Package | LQFP         | LH         | 98ASS23234W  |

| 48        | Low Quad Flat Package | LQFP         | LF         | 98ASH00962A  |

| 32        | Low Quad Flat Package | LQFP         | LC         | 98ASH70029A  |