### NXP USA Inc. - S9S08DV32F2MLC Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 25                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 10x12b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08dv32f2mlc |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

The following revision history table summarizes changes contained in this document.

| Revision<br>Number | Revision<br>Date | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | 6/2006           | Advance Information version for alpha samples customers                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2                  | 9/2007           | Product Launch. Removed the 64-pin QFN package. Changed from standard to extended mode for MSCAN registers in register summary. Corrected Block diagrams for SCI. Updated the latest Temp Sensor information. Made FTSTMOD reserved. Updated device to use the ADC 12-bit module. Revised the MCG module. Updated the TPM block module to version 3. Added the TPM block module version 2 as an appendix for devices using 3M05C (or earlier) mask sets. Heavily revised the Electricals appendix. |

| 3                  | 6/2008           | Sustaining Update. Incorporated PS Issues # 2765, 3177, 3236, 3292, 3301, 3311, 3312, 3326, 3335, 3345, 3382, 2795, 3382 and 3386 PLL Jitter Spec update. Also, added internal reference clock trim adjustment statement to Features page. Updated the TPM module to the latest version. Adjusted values in Table A-13 Control Timing row 2 and in Table A-6 DC Characteristics row 24 so that it references 5.0 V instead of 3.0 V.                                                               |

© Freescale Semiconductor, Inc., 2007-2008. All rights reserved.

This product incorporates  $\mathsf{SuperFlash}^{\texttt{®}}$  Technology licensed from SST.

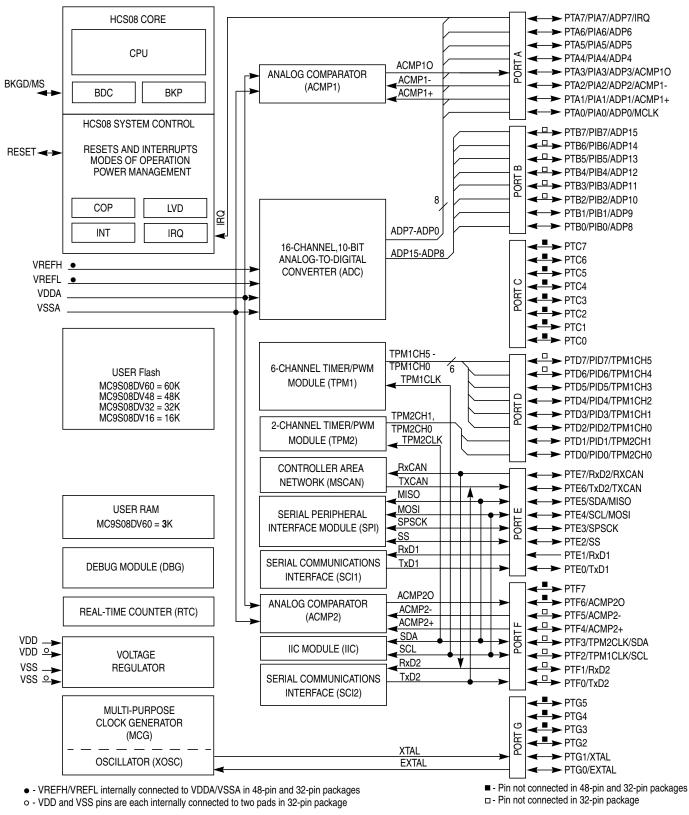

**Chapter 1 Device Overview**

MC9S08DV60 Series Data Sheet, Rev 3

**Chapter 2 Pins and Connections**

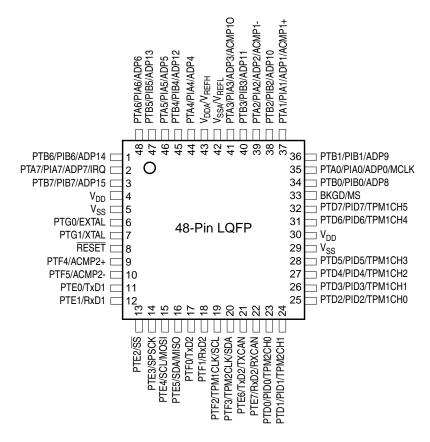

Figure 2-2. 48-Pin LQFP

## NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pull-up devices or change the direction of unused or non-bonded pins to outputs so they do not float.

**Chapter 4 Memory**

### Table 4-2. Direct-Page Register Summary (Sheet 3 of 3)

| 0x0051         SPIC2         0         0         0         MODFEN         BIDIROE         0         SPISAL         SPC0           0x0052         SPIBR         0         SPPR2         SPPR1         SPPR0         0         SPR2         SPR1         SPR0           0x0053         SPIS         SPRF         0         SPTEF         MODF         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                      | Address        | Register<br>Name | Bit 7  | 6     | 5     | 4      | 3       | 2     | 1       | Bit 0 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|--------|-------|-------|--------|---------|-------|---------|-------|

| 0x0052         SPIBR         0         SPPR2         SPPR1         SPPR0         0         SPR2         SPR1         SPR1           0x0053         SPIS         SPRF         0         SPTEF         MODF         0         0         0         0           0x0054         Reserved         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                            | 0x00 <b>50</b> | SPIC1            | SPIE   | SPE   | SPTIE | MSTR   | CPOL    | CPHA  | SSOE    | LSBFE |

| 0x0053         SPIS         SPRF         0         SPTEF         MODF         0         0         0         0           0x0054         Reserved         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <t< td=""><td>0x00<b>51</b></td><td>SPIC2</td><td>0</td><td>0</td><td>0</td><td>MODFEN</td><td>BIDIROE</td><td>0</td><td>SPISWAI</td><td>SPC0</td></t<>                                | 0x00 <b>51</b> | SPIC2            | 0      | 0     | 0     | MODFEN | BIDIROE | 0     | SPISWAI | SPC0  |

| 0x0054         Reserved         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         <                                                                                                                                                                              | 0x00 <b>52</b> | SPIBR            | 0      | SPPR2 | SPPR1 | SPPR0  | 0       | SPR2  | SPR1    | SPR0  |

| DX0055         SPID         Bit 7         6         5         4         3         2         1         Bit 0           DX0057         Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x00 <b>53</b> | SPIS             | SPRF   | 0     | SPTEF | MODF   | 0       | 0     | 0       | 0     |

| 0x0056-<br>0x0057         Reserved         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                             | 0x00 <b>54</b> | Reserved         | 0      | 0     | 0     | 0      | 0       | 0     | 0       | 0     |

| 0x0057         Reserved                                                                             0x0055         IICC         IICC         IICCA         ADEXT         0         0         0         AD10         AD9         AD8         0x0055         IICS         IICC         IICCA         IICCA         IICCA         IICCA         IICCA         IICCA         IICCA         IICCA <t< td=""><td>0x00<b>55</b></td><td>SPID</td><td>Bit 7</td><td>6</td><td>5</td><td>4</td><td>3</td><td>2</td><td>1</td><td>Bit 0</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00 <b>55</b> | SPID             | Bit 7  | 6     | 5     | 4      | 3       | 2     | 1       | Bit 0 |

| 0x0059         IICF         MULT         ICR           0x005A         IICC1         IICEN         IICE         MST         TX         TXAK         RSTA         0         0           0x005B         IICS         TCF         IAAS         BUSY         ARBL         0         SRW         IICIF         RXAK           0x005C         IICD         TCF         IAAS         BUSY         ARBL         0         SRW         IICIF         RXAK           0x005D         IICC2         GCAEN         ADEXT         0         0         0         AD10         AD9         AD8           0x005F         Reserved </td <td></td> <td>Reserved</td> <td>_</td> <td>_</td> <td></td> <td></td> <td>_</td> <td>_</td> <td></td> <td>_</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                | Reserved         | _      | _     |       |        | _       | _     |         | _     |

| DX005A         IICC1         IICEN         IICE         MST         TX         TXAK         RSTA         0         0           DX005B         IICS         TCF         IAAS         BUSY         ARBL         0         SRW         IICIF         RXAH           DX005C         IICD         GCAEN         ADEXT         0         0         0         AD10         AD9         AD8           DX005F         Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x00 <b>58</b> | IICA             | AD7    | AD6   | AD5   | AD4    | AD3     | AD2   | AD1     | 0     |

| 0x005B         IICS         TCF         IAAS         BUSY         ARBL         0         SRW         IICIF         RXAR           0x005C         IICD         DATA         DA                                                            | 0x00 <b>59</b> | IICF             | MU     | JLT   |       | 1      | IC      | R     | 1       |       |

| 0x005C         IICD         GCAEN         ADEXT         0         0         0         AD10         AD9         AD8           0x005F         Reserved         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …                                                                                                                                                                                   | 0x00 <b>5A</b> | IICC1            | IICEN  | IICIE | MST   | ТХ     | TXAK    | RSTA  | 0       | 0     |

| 0x005D         IICC2         GCAEN         ADEXT         0         0         AD10         AD9         AD8           0x005F         Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00 <b>5B</b> | IICS             | TCF    | IAAS  | BUSY  | ARBL   | 0       | SRW   | IICIF   | RXAK  |

| 0x005E-<br>0x005F         Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x00 <b>5C</b> | IICD             |        |       |       | DA     | ΤA      |       |         |       |

| 0x005F         Heserved         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         <                                                                                                                                                                              | 0x00 <b>5D</b> | IICC2            | GCAEN  | ADEXT | 0     | 0      | 0       | AD10  | AD9     | AD8   |

| 0x0061         TPM2CNTH         Bit 15         14         13         12         11         10         9         Bit 8           0x0062         TPM2CNTL         Bit 7         6         5         4         3         2         1         Bit 0           0x0063         TPM2MODH         Bit 15         14         13         12         11         10         9         Bit 8           0x0064         TPM2MODL         Bit 15         14         13         12         11         10         9         Bit 8           0x0064         TPM2MODL         Bit 7         6         5         4         3         2         1         Bit 0           0x0065         TPM2COSC         CHOF         CHOIE         MS0B         MS0A         ELS0B         ELS0A         0         0           0x0066         TPM2COVL         Bit 7         6         5         4         3         2         1         Bit 0           0x0067         TPM2COVL         Bit 7         6         5         4         3         2         1         Bit 0           0x0068         TPM2C1VH         Bit 15         14         13         12         11         10 <td></td> <td>Reserved</td> <td></td> <td></td> <td>_</td> <td>_</td> <td>_</td> <td>—</td> <td>_</td> <td>_</td>                                 |                | Reserved         |        |       | _     | _      | _       | —     | _       | _     |

| 0x0062         TPM2CNTL         Bit 7         6         5         4         3         2         1         Bit 0           0x0063         TPM2MODH         Bit 15         14         13         12         11         10         9         Bit 8           0x0064         TPM2MODL         Bit 7         6         5         4         3         2         1         Bit 0           0x0065         TPM2COSC         CH0F         CH0IE         MS0B         MS0A         ELS0B         ELS0A         0         0           0x0066         TPM2COVH         Bit 15         14         13         12         11         10         9         Bit 8           0x0066         TPM2COVH         Bit 7         6         5         4         3         2         1         Bit 0           0x0067         TPM2COVL         Bit 7         6         5         4         3         2         1         Bit 0           0x0068         TPM2C1VL         Bit 7         6         5         4         3         2         1         Bit 0           0x006A         TPM2C1VL         Bit 7         6         5         4         3         2 <t< td=""><td>0x00<b>60</b></td><td>TPM2SC</td><td>TOF</td><td>TOIE</td><td>CPWMS</td><td>CLKSB</td><td>CLKSA</td><td>PS2</td><td>PS1</td><td>PS0</td></t<>   | 0x00 <b>60</b> | TPM2SC           | TOF    | TOIE  | CPWMS | CLKSB  | CLKSA   | PS2   | PS1     | PS0   |

| 0x0063         TPM2MODH         Bit 15         14         13         12         11         10         9         Bit 8           0x0064         TPM2MODL         Bit 7         6         5         4         3         2         1         Bit 0           0x0065         TPM2COSC         CHOF         CHOIE         MS0B         MS0A         ELS0B         ELS0A         0         0           0x0066         TPM2COVH         Bit 15         14         13         12         11         10         9         Bit 8           0x0066         TPM2COVH         Bit 15         14         13         12         11         10         9         Bit 8           0x0067         TPM2COVL         Bit 7         6         5         4         3         2         1         Bit 0           0x0068         TPM2C1SC         CH1F         CH1IE         MS1B         MS1A         ELS1B         ELS1A         0         0           0x006A         TPM2C1VH         Bit 7         6         5         4         3         2         1         Bit 0           0x006A         TPM2C1VL         Bit 7         6         5         4         3 <t< td=""><td>0x00<b>61</b></td><td>TPM2CNTH</td><td>Bit 15</td><td>14</td><td>13</td><td>12</td><td>11</td><td>10</td><td>9</td><td>Bit 8</td></t<> | 0x00 <b>61</b> | TPM2CNTH         | Bit 15 | 14    | 13    | 12     | 11      | 10    | 9       | Bit 8 |

| 0x0064         TPM2MODL         Bit 7         6         5         4         3         2         1         Bit 0           0x0065         TPM2COSC         CH0F         CH0IE         MS0B         MS0A         ELS0B         ELS0A         0         0           0x0066         TPM2C0VH         Bit 15         14         13         12         11         10         9         Bit 8           0x0067         TPM2C0VL         Bit 7         6         5         4         3         2         1         Bit 0           0x0067         TPM2C0VL         Bit 7         6         5         4         3         2         1         Bit 0           0x0068         TPM2C1VH         Bit 15         14         13         12         11         10         9         Bit 8           0x0069         TPM2C1VH         Bit 7         6         5         4         3         2         1         Bit 0           0x0068         Reserved         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - </td <td>0x00<b>62</b></td> <td>TPM2CNTL</td> <td>Bit 7</td> <td>6</td> <td>5</td> <td>4</td> <td>3</td> <td>2</td> <td>1</td> <td>Bit 0</td>             | 0x00 <b>62</b> | TPM2CNTL         | Bit 7  | 6     | 5     | 4      | 3       | 2     | 1       | Bit 0 |

| 0x0065         TPM2C0SC         CH0F         CH0IE         MS0B         MS0A         ELS0B         ELS0A         0         0           0x0066         TPM2C0VH         Bit 15         14         13         12         11         10         9         Bit 8           0x0067         TPM2C0VL         Bit 7         6         5         4         3         2         1         Bit 0           0x0068         TPM2C1SC         CH1F         CH1IE         MS1B         MS1A         ELS1B         ELS1A         0         0           0x0069         TPM2C1VH         Bit 15         14         13         12         11         10         9         Bit 8           0x0064         TPM2C1VH         Bit 7         6         5         4         3         2         1         Bit 9           0x006A         TPM2C1VL         Bit 7         6         5         4         3         2         1         Bit 9           0x006B         Reserved         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                        | 0x00 <b>63</b> | TPM2MODH         | Bit 15 | 14    | 13    | 12     | 11      | 10    | 9       | Bit 8 |

| 0x0066         TPM2C0VH         Bit 15         14         13         12         11         10         9         Bit 8           0x0067         TPM2C0VL         Bit 7         6         5         4         3         2         1         Bit 0           0x0068         TPM2C1SC         CH1F         CH1IE         MS1B         MS1A         ELS1B         ELS1A         0         0           0x0069         TPM2C1VH         Bit 15         14         13         12         11         10         9         Bit 8           0x006A         TPM2C1VL         Bit 7         6         5         4         3         2         1         Bit 0           0x006B         Reserved         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <td>0x00<b>64</b></td> <td>TPM2MODL</td> <td>Bit 7</td> <td>6</td> <td>5</td> <td>4</td> <td>3</td> <td>2</td> <td>1</td> <td>Bit 0</td>                      | 0x00 <b>64</b> | TPM2MODL         | Bit 7  | 6     | 5     | 4      | 3       | 2     | 1       | Bit 0 |

| 0x0067         TPM2C0VL         Bit 7         6         5         4         3         2         1         Bit 0           0x0068         TPM2C1SC         CH1F         CH1IE         MS1B         MS1A         ELS1B         ELS1A         0         0           0x0069         TPM2C1VH         Bit 15         14         13         12         11         10         9         Bit 8           0x006A         TPM2C1VL         Bit 7         6         5         4         3         2         1         Bit 9           0x006A         TPM2C1VL         Bit 7         6         5         4         3         2         1         Bit 9           0x006B         Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 <b>65</b> | TPM2C0SC         | CH0F   | CH0IE | MS0B  | MS0A   | ELS0B   | ELS0A | 0       | 0     |

| 0x0068         TPM2C1SC         CH1F         CH1IE         MS1B         MS1A         ELS1B         ELS1A         0         0           0x0069         TPM2C1VH         Bit 15         14         13         12         11         10         9         Bit 8           0x006A         TPM2C1VL         Bit 7         6         5         4         3         2         1         Bit 0           0x006B         Reserved         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                         | 0x00 <b>66</b> | TPM2C0VH         | Bit 15 | 14    | 13    | 12     | 11      | 10    | 9       | Bit 8 |

| 0x0069         TPM2C1VH         Bit 15         14         13         12         11         10         9         Bit 8           0x006A         TPM2C1VL         Bit 7         6         5         4         3         2         1         Bit 0           0x006B         Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x00 <b>67</b> | TPM2C0VL         | Bit 7  | 6     | 5     | 4      | 3       | 2     | 1       | Bit 0 |

| 0x006A         TPM2C1VL         Bit 7         6         5         4         3         2         1         Bit 0           0x006B         Reserved         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                      | 0x00 <b>68</b> | TPM2C1SC         | CH1F   | CH1IE | MS1B  | MS1A   | ELS1B   | ELS1A | 0       | 0     |

| 0x006B         Reserved         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         …         <                                                                                                                                                                              | 0x00 <b>69</b> | TPM2C1VH         | Bit 15 | 14    | 13    | 12     | 11      | 10    | 9       | Bit 8 |

| 0x006C     RTCSC     RTIF     RTCLKS     RTIE     RTCPS       0x006D     RTCCNT     RTCCNT     RTCMOD       0x006E     RTCMOD     RTCMOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00 <b>6A</b> | TPM2C1VL         | Bit 7  | 6     | 5     | 4      | 3       | 2     | 1       | Bit 0 |

| 0x006D     RTCCNT     RTCCNT       0x006E     RTCMOD     RTCMOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00 <b>6B</b> | Reserved         |        |       | —     | —      | —       | _     | —       | —     |

| 0x006E RTCMOD RTCMOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x00 <b>6C</b> | RTCSC            | RTIF   | RTC   | LKS   | RTIE   |         | RTC   | CPS     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00 <b>6D</b> | RTCCNT           | RTCCNT |       |       |        |         |       |         |       |

| 0x006F Beserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00 <b>6E</b> | RTCMOD           |        |       |       | RTC    | MOD     |       |         |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00 <b>6F</b> | Reserved         | —      | —     | —     | —      | —       | —     | —       | —     |

| 0x00 <b>70</b> -<br>0x00 <b>7F</b> Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                | Reserved         | _      | _     | _     | _      | _       | _     | _       | _     |

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at 0x1800.

| SEC[1:0] | Description |

|----------|-------------|

| 0:0      | secure      |

| 0:1      | secure      |

| 1:0      | unsecured   |

| 1:1      | secure      |

Table 4-10. Security States<sup>1</sup>

<sup>1</sup> SEC changes to 1:0 after successful backdoor key entry or a successful blank check of Flash.

## 4.5.10.3 Flash Configuration Register (FCNFG)

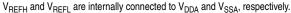

### Figure 4-7. Flash Configuration Register (FCNFG)

<sup>1</sup> User must write a 1 to this bit. Failing to do so may result in unexpected behavior.

#### Table 4-11. FCNFG Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>KEYACC | <ul> <li>Enable Writing of Access Key — This bit enables writing of the backdoor comparison key. For more detailed information about the backdoor key mechanism, refer to Section 4.5.9, "Security."</li> <li>Writes to 0xFFB0–0xFFB7 are interpreted as the start of a Flash programming or erase command.</li> <li>Writes to NVBACKKEY (0xFFB0–0xFFB7) are interpreted as comparison key writes.</li> </ul> |

## 4.5.10.4 Flash Protection Register (FPROT and NVPROT)

The FPROT register defines which Flash and EEPROM sectors are protected against program and erase operations.

During the reset sequence, the FPROT register is loaded from the nonvolatile location NVPROT. To change the protection that will be loaded during the reset sequence, the sector containing NVPROT must be unprotected and erased, then NVPROT can be reprogrammed.

FPROT bits are readable at any time and writable as long as the size of the protected region is being increased. Any write to FPROT that attempts to decrease the size of the protected memory will be ignored.

Trying to alter data in any protected area will result in a protection violation error and the FPVIOL flag will be set in the FSTAT register. Mass erase is not possible if any one of the sectors is protected.

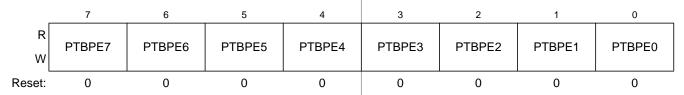

# 6.5.2.3 Port B Pull Enable Register (PTBPE)

Figure 6-13. Internal Pull Enable for Port B Register (PTBPE)

### Table 6-11. PTBPE Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0   | Internal Pull Enable for Port B Bits — Each of these control bits determines if the internal pull-up or pull-down                                                                                                                                                                                                                      |

|       | <ul> <li>device is enabled for the associated PTB pin. For port B pins that are configured as outputs, these bits have no effect and the internal pull devices are disabled.</li> <li>0 Internal pull-up/pull-down device disabled for port B bit n.</li> <li>1 Internal pull-up/pull-down device enabled for port B bit n.</li> </ul> |

### NOTE

Pull-down devices only apply when using pin interrupt functions, when corresponding edge select and pin select functions are configured.

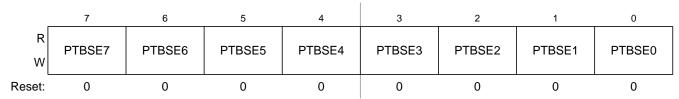

## 6.5.2.4 Port B Slew Rate Enable Register (PTBSE)

### Figure 6-14. Slew Rate Enable for Port B Register (PTBSE)

### Table 6-12. PTBSE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBSE[7:0] | <ul> <li>Output Slew Rate Enable for Port B Bits — Each of these control bits determines if the output slew rate control is enabled for the associated PTB pin. For port B pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port B bit n.</li> <li>Output slew rate control enabled for port B bit n.</li> </ul> |

**Note:** Slew rate reset default values may differ between engineering samples and final production parts. Always initialize slew rate control to the desired value to ensure correct operation.

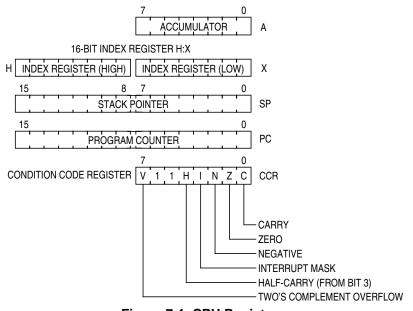

Chapter 7 Central Processor Unit (S08CPUV3)

# 7.2 Programmer's Model and CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 7-1. CPU Registers

# 7.2.1 Accumulator (A)

The A accumulator is a general-purpose 8-bit register. One operand input to the arithmetic logic unit (ALU) is connected to the accumulator and the ALU results are often stored into the A accumulator after arithmetic and logical operations. The accumulator can be loaded from memory using various addressing modes to specify the address where the loaded data comes from, or the contents of A can be stored to memory using various addressing modes to specify the addressing modes to specify the addressing modes to specify the address where data from A will be stored.

Reset has no effect on the contents of the A accumulator.

# 7.2.2 Index Register (H:X)

This 16-bit register is actually two separate 8-bit registers (H and X), which often work together as a 16-bit address pointer where H holds the upper byte of an address and X holds the lower byte of the address. All indexed addressing mode instructions use the full 16-bit value in H:X as an index reference pointer; however, for compatibility with the earlier M68HC05 Family, some instructions operate only on the low-order 8-bit half (X).

Many instructions treat X as a second general-purpose 8-bit register that can be used to hold 8-bit data values. X can be cleared, incremented, decremented, complemented, negated, shifted, or rotated. Transfer instructions allow data to be transferred from A or transferred to A where arithmetic and logical operations can then be performed.

For compatibility with the earlier M68HC05 Family, H is forced to 0x00 during reset. Reset has no effect on the contents of X.

#### Chapter 7 Central Processor Unit (S08CPUV3)

interrupt service routine, this would allow nesting of interrupts (which is not recommended because it leads to programs that are difficult to debug and maintain).

For compatibility with the earlier M68HC05 MCUs, the high-order half of the H:X index register pair (H) is not saved on the stack as part of the interrupt sequence. The user must use a PSHH instruction at the beginning of the service routine to save H and then use a PULH instruction just before the RTI that ends the interrupt service routine. It is not necessary to save H if you are certain that the interrupt service routine does not use any instructions or auto-increment addressing modes that might change the value of H.

The software interrupt (SWI) instruction is like a hardware interrupt except that it is not masked by the global I bit in the CCR and it is associated with an instruction opcode within the program so it is not asynchronous to program execution.

# 7.4.3 Wait Mode Operation

The WAIT instruction enables interrupts by clearing the I bit in the CCR. It then halts the clocks to the CPU to reduce overall power consumption while the CPU is waiting for the interrupt or reset event that will wake the CPU from wait mode. When an interrupt or reset event occurs, the CPU clocks will resume and the interrupt or reset event will be processed normally.

If a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in wait mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in wait mode.

# 7.4.4 Stop Mode Operation

Usually, all system clocks, including the crystal oscillator (when used), are halted during stop mode to minimize power consumption. In such systems, external circuitry is needed to control the time spent in stop mode and to issue a signal to wake up the target MCU when it is time to resume processing. Unlike the earlier M68HC05 and M68HC08 MCUs, the HCS08 can be configured to keep a minimum set of clocks running in stop mode. This optionally allows an internal periodic signal to wake the target MCU from stop mode.

When a host debug system is connected to the background debug pin (BKGD) and the ENBDM control bit has been set by a serial command through the background interface (or because the MCU was reset into active background mode), the oscillator is forced to remain active when the MCU enters stop mode. In this case, if a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in stop mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in stop mode.

Recovery from stop mode depends on the particular HCS08 and whether the oscillator was stopped in stop mode. Refer to the Modes of Operation chapter for more details.

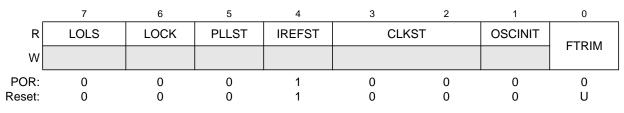

# 8.3.4 MCG Status and Control Register (MCGSC)

Figure 8-6. MCG Status and Control Register (MCGSC)

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOLS    | <ul> <li>Loss of Lock Status — This bit is a sticky indication of lock status for the FLL or PLL. LOLS is set when lock detection is enabled and after acquiring lock, the FLL or PLL output frequency has fallen outside the lock exit frequency tolerance, D<sub>unl</sub>. LOLIE determines whether an interrupt request is made when set. LOLS is cleared by reset or by writing a logic 1 to LOLS when LOLS is set. Writing a logic 0 to LOLS has no effect.</li> <li>0 FLL or PLL has not lost lock since LOLS was last cleared.</li> <li>1 FLL or PLL has lost lock since LOLS was last cleared.</li> </ul>                                                                                                                                                                                                                                                                                                                                           |

| 6<br>LOCK    | Lock Status — Indicates whether the FLL or PLL has acquired lock. Lock detection is disabled when both the FLL and PLL are disabled. If the lock status bit is set then changing the value of any of the following bits IREFS, PLLS, RDIV[2:0], TRIM[7:0] (if in FEI or FBI modes), or VDIV[3:0] (if in PBE or PEE modes), will cause the lock status bit to clear and stay cleared until the FLL or PLL has reacquired lock. Stop mode entry will also cause the lock status bit to clear and stay cleared until the FLL or PLL has reacquired lock. Entry into BLPI or BLPE mode will also cause the lock status bit to clear and stay cleared until the FLL or PLL has reacquired lock. Entry into BLPI or BLPE mode will also cause the lock status bit to clear and stay cleared until the FLL or PLL has reacquired lock. Entry into BLPI or BLPE mode will also cause the lock. 0 FLL or PLL is currently unlocked. 1 FLL or PLL is currently locked. |

| 5<br>PLLST   | <ul> <li>PLL Select Status — The PLLST bit indicates the current source for the PLLS clock. The PLLST bit does not update immediately after a write to the PLLS bit due to internal synchronization between clock domains.</li> <li>0 Source of PLLS clock is FLL clock.</li> <li>1 Source of PLLS clock is PLL clock.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4<br>IREFST  | <ul> <li>Internal Reference Status — The IREFST bit indicates the current source for the reference clock. The IREFST bit does not update immediately after a write to the IREFS bit due to internal synchronization between clock domains.</li> <li>0 Source of reference clock is external reference clock (oscillator or external clock source as determined by the EREFS bit in the MCGC2 register).</li> <li>1 Source of reference clock is internal reference clock.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3:2<br>CLKST | <ul> <li>Clock Mode Status — The CLKST bits indicate the current clock mode. The CLKST bits do not update immediately after a write to the CLKS bits due to internal synchronization between clock domains.</li> <li>00 Encoding 0 — Output of FLL is selected.</li> <li>01 Encoding 1 — Internal reference clock is selected.</li> <li>10 Encoding 2 — External reference clock is selected.</li> <li>11 Encoding 3 — Output of PLL is selected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

MC9S08DV60 Series Data Sheet, Rev 3

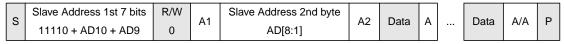

# 11.4.2 10-bit Address

For 10-bit addressing, 0x11110 is used for the first 5 bits of the first address byte. Various combinations of read/write formats are possible within a transfer that includes 10-bit addressing.

## 11.4.2.1 Master-Transmitter Addresses a Slave-Receiver

The transfer direction is not changed (see Table 11-9). When a 10-bit address follows a start condition, each slave compares the first seven bits of the first byte of the slave address (11110XX) with its own address and tests whether the eighth bit (R/W direction bit) is 0. More than one device can find a match and generate an acknowledge (A1). Then, each slave that finds a match compares the eight bits of the second byte of the slave address with its own address. Only one slave finds a match and generates an acknowledge (A2). The matching slave remains addressed by the master until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

Table 11-9. Master-Transmitter Addresses Slave-Receiver with a 10-bit Address

After the master-transmitter has sent the first byte of the 10-bit address, the slave-receiver sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

## 11.4.2.2 Master-Receiver Addresses a Slave-Transmitter

The transfer direction is changed after the second  $R/\overline{W}$  bit (see Table 11-10). Up to and including acknowledge bit A2, the procedure is the same as that described for a master-transmitter addressing a slave-receiver. After the repeated start condition (Sr), a matching slave remembers that it was addressed before. This slave then checks whether the first seven bits of the first byte of the slave address following Sr are the same as they were after the start condition (S) and tests whether the eighth ( $R/\overline{W}$ ) bit is 1. If there is a match, the slave considers that it has been addressed as a transmitter and generates acknowledge A3. The slave-transmitter remains addressed until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

After a repeated start condition (Sr), all other slave devices also compare the first seven bits of the first byte of the slave address with their own addresses and test the eighth  $(R/\overline{W})$  bit. However, none of them are addressed because  $R/\overline{W} = 1$  (for 10-bit devices) or the 11110XX slave address (for 7-bit devices) does not match.

| s | Slave Address<br>1st 7 bits | R/W | A1 | Slave Address<br>2nd byte | A2 | Sr | Slave Address<br>1st 7 bits | R/W | A3 | Data | A | <br>Data | A | Р |

|---|-----------------------------|-----|----|---------------------------|----|----|-----------------------------|-----|----|------|---|----------|---|---|

|   | 11110 + AD10 + AD9          | 0   |    | AD[8:1]                   |    |    | 11110 + AD10 + AD9          | 1   |    |      |   |          |   |   |

Table 11-10. Master-Receiver Addresses a Slave-Transmitter with a 10-bit Address

After the master-receiver has sent the first byte of the 10-bit address, the slave-transmitter sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

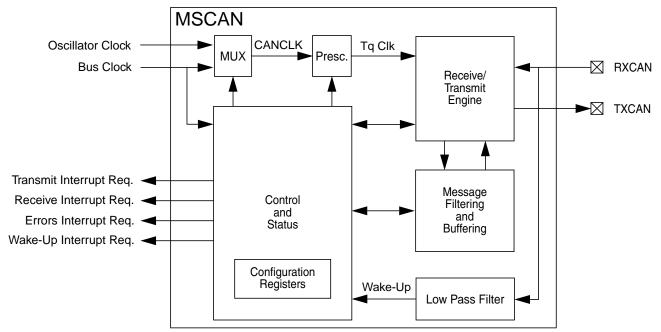

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

# 12.1.3 Block Diagram

Figure 12-2. MSCAN Block Diagram

# 12.2 External Signal Description

The MSCAN uses two external pins:

# 12.2.1 RXCAN — CAN Receiver Input Pin

RXCAN is the MSCAN receiver input pin.

# 12.2.2 TXCAN — CAN Transmitter Output Pin

TXCAN is the MSCAN transmitter output pin. The TXCAN output pin represents the logic level on the CAN bus:

0 = Dominant state 1 = Recessive state

# 12.2.3 CAN System

A typical CAN system with MSCAN is shown in Figure 12-3. Each CAN node is connected physically to the CAN bus lines through a transceiver device. The transceiver is capable of driving the large current needed for the CAN bus and has current protection against defective CAN or defective nodes.

| Register<br>Name |        | Bit 7 | 6    | 5             | 4                                                    | 3    | 2    | 1    | Bit0             |

|------------------|--------|-------|------|---------------|------------------------------------------------------|------|------|------|------------------|

| IDR0             | R<br>W | ID28  | ID27 | ID26          | ID25                                                 | ID24 | ID23 | ID22 | ID21             |

| IDR1             | R<br>W | ID20  | ID19 | ID18          | ID18 SRR <sup>(1)</sup> IDE <sup>(1)</sup> ID17 ID16 |      | ID16 | ID15 |                  |

| IDR2             | R<br>W | ID14  | ID13 | ID12          | ID11                                                 | ID10 | ID9  | ID8  | ID7              |

| IDR3             | R<br>W | ID6   | ID5  | ID4           | ID3                                                  | ID2  | ID1  | ID0  | RTR <sup>2</sup> |

| DSR0             | R<br>W | DB7   | DB6  | DB5           | DB4                                                  | DB3  | DB2  | DB1  | DB0              |

| DSR1             | R<br>W | DB7   | DB6  | DB5           | DB4                                                  | DB3  | DB2  | DB1  | DB0              |

| DSR2             | R<br>W | DB7   | DB6  | DB5           | DB4                                                  | DB3  | DB2  | DB1  | DB0              |

| DSR3             | R<br>W | DB7   | DB6  | DB5           | DB4                                                  | DB3  | DB2  | DB1  | DB0              |

| DSR4             | R<br>W | DB7   | DB6  | DB5           | DB4                                                  | DB3  | DB2  | DB1  | DB0              |

| DSR5             | R<br>W | DB7   | DB6  | DB5           | DB4                                                  | DB3  | DB2  | DB1  | DB0              |

| DSR6             | R<br>W | DB7   | DB6  | DB5           | DB4                                                  | DB3  | DB2  | DB1  | DB0              |

| DSR7             | R<br>W | DB7   | DB6  | DB5           | DB4                                                  | DB3  | DB2  | DB1  | DB0              |

| DLR              | R<br>W |       |      |               |                                                      | DLC3 | DLC2 | DLC1 | DLC0             |

|                  | Г      |       |      | wave road 'y' |                                                      |      |      |      |                  |

= Unused, always read 'x'

### Figure 12-23. Receive/Transmit Message Buffer — Extended Identifier Mapping

<sup>1</sup> SRR and IDE are both 1s.

$^2$  The position of RTR differs between extended and standard indentifier mapping.

Read: For transmit buffers, anytime when TXEx flag is set (see Section 12.3.6, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see

MC9S08DV60 Series Data Sheet, Rev 3

Chapter 13 Serial Peripheral Interface (S08SPIV3)

The most common uses of the SPI system include connecting simple shift registers for adding input or output ports or connecting small peripheral devices such as serial A/D or D/A converters. Although Figure 13-2 shows a system where data is exchanged between two MCUs, many practical systems involve simpler connections where data is unidirectionally transferred from the master MCU to a slave or from a slave to the master MCU.

## 13.1.2.2 SPI Module Block Diagram

Figure 13-3 is a block diagram of the SPI module. The central element of the SPI is the SPI shift register. Data is written to the double-buffered transmitter (write to SPID) and gets transferred to the SPI shift register at the start of a data transfer. After shifting in a byte of data, the data is transferred into the double-buffered receiver where it can be read (read from SPID). Pin multiplexing logic controls connections between MCU pins and the SPI module.

When the SPI is configured as a master, the clock output is routed to the SPSCK pin, the shifter output is routed to MOSI, and the shifter input is routed from the MISO pin.

When the SPI is configured as a slave, the SPSCK pin is routed to the clock input of the SPI, the shifter output is routed to MISO, and the shifter input is routed from the MOSI pin.

In the external SPI system, simply connect all SPSCK pins to each other, all MISO pins together, and all MOSI pins together. Peripheral devices often use slightly different names for these pins.

Writing 0 to TE does not immediately release the pin to be a general-purpose I/O pin. Any transmit activity that is in progress must first be completed. This includes data characters in progress, queued idle characters, and queued break characters.

## 14.3.2.1 Send Break and Queued Idle

The SBK control bit in SCIxC2 is used to send break characters which were originally used to gain the attention of old teletype receivers. Break characters are a full character time of logic 0 (10 bit times including the start and stop bits). A longer break of 13 bit times can be enabled by setting BRK13 = 1. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 1 and then write 0 to the SBK bit. This action queues a break character to be sent as soon as the shifter is available. If SBK is still 1 when the queued break moves into the shifter (synchronized to the baud rate clock), an additional break character is queued. If the receiving device is another Freescale Semiconductor SCI, the break characters will be received as 0s in all eight data bits and a framing error (FE = 1) occurs.

When idle-line wakeup is used, a full character time of idle (logic 1) is needed between messages to wake up any sleeping receivers. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 0 and then write 1 to the TE bit. This action queues an idle character to be sent as soon as the shifter is available. As long as the character in the shifter does not finish while TE = 0, the SCI transmitter never actually releases control of the TxD pin. If there is a possibility of the shifter finishing while TE = 0, set the general-purpose I/O controls so the pin that is shared with TxD is an output driving a logic 1. This ensures that the TxD line will look like a normal idle line even if the SCI loses control of the port pin between writing 0 and then 1 to TE.

The length of the break character is affected by the BRK13 and M bits as shown below.

| BRK13 | М | Break Character Length |