Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 39                                                                     |

| Program Memory Size        | 60KB (60K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 3K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08dv60f2mlf |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Section Number**

Title

## Page

| 10.2 | External Signal Description                        | 176 |

|------|----------------------------------------------------|-----|

|      | 10.2.1 Analog Power (V <sub>DDAD</sub> )           | 177 |

|      | 10.2.2 Analog Ground (V <sub>SSAD</sub> )          | 177 |

|      | 10.2.3 Voltage Reference High (V <sub>REFH</sub> ) |     |

|      | 10.2.4 Voltage Reference Low (V <sub>REFL</sub> )  | 177 |

|      | 10.2.5 Analog Channel Inputs (ADx)                 | 177 |

| 10.3 | Register Definition                                |     |

|      | 10.3.1 Status and Control Register 1 (ADCSC1)      |     |

|      | 10.3.2 Status and Control Register 2 (ADCSC2)      | 179 |

|      | 10.3.3 Data Result High Register (ADCRH)           |     |

|      | 10.3.4 Data Result Low Register (ADCRL)            |     |

|      | 10.3.5 Compare Value High Register (ADCCVH)        | 180 |

|      | 10.3.6 Compare Value Low Register (ADCCVL)         |     |

|      | 10.3.7 Configuration Register (ADCCFG)             | 181 |

|      | 10.3.8 Pin Control 1 Register (APCTL1)             | 182 |

|      | 10.3.9 Pin Control 2 Register (APCTL2)             | 183 |

|      | 10.3.10Pin Control 3 Register (APCTL3)             | 184 |

| 10.4 | Functional Description                             | 185 |

|      | 10.4.1 Clock Select and Divide Control             | 186 |

|      | 10.4.2 Input Select and Pin Control                | 186 |

|      | 10.4.3 Hardware Trigger                            |     |

|      | 10.4.4 Conversion Control                          | 186 |

|      | 10.4.5 Automatic Compare Function                  |     |

|      | 10.4.6 MCU Wait Mode Operation                     | 189 |

|      | 10.4.7 MCU Stop3 Mode Operation                    |     |

|      | 10.4.8 MCU Stop2 Mode Operation                    | 190 |

| 10.5 | Initialization Information                         | 191 |

|      | 10.5.1 ADC Module Initialization Example           | 191 |

| 10.6 | Application Information                            |     |

|      | 10.6.1 External Pins and Routing                   | 193 |

|      | 10.6.2 Sources of Error                            | 194 |

# Chapter 11 Inter-Integrated Circuit (S08IICV2)

| 11.1 | I Introduction                |  |

|------|-------------------------------|--|

|      | 11.1.1 Features               |  |

|      | 11.1.2 Modes of Operation     |  |

|      |                               |  |

| 11.2 | 2 External Signal Description |  |

|      |                               |  |

|      | 11.2.2 SDA — Serial Data Line |  |

| 11.3 | 3 Register Definition         |  |

|      | -                             |  |

## **Section Number**

Title

## Page

| 17.4 | Register Definition                                         | 359 |

|------|-------------------------------------------------------------|-----|

|      | 17.4.1 BDC Registers and Control Bits                       |     |

|      | 17.4.2 System Background Debug Force Reset Register (SBDFR) | 361 |

|      | 17.4.3 DBG Registers and Control Bits                       | 362 |

## Appendix A Electrical Characteristics

| A.1  | Introduction                               | 367 |

|------|--------------------------------------------|-----|

| A.2  | Parameter Classification                   | 367 |

| A.3  | Absolute Maximum Ratings                   | 367 |

| A.4  | Thermal Characteristics                    | 368 |

| A.5  | ESD Protection and Latch-Up Immunity       | 370 |

| A.6  | DC Characteristics                         | 371 |

| A.7  | Supply Current Characteristics             | 373 |

| A.8  | Analog Comparator (ACMP) Electricals       | 374 |

| A.9  | ADC Characteristics                        | 374 |

| A.10 | External Oscillator (XOSC) Characteristics | 378 |

| A.11 | MCG Specifications                         | 379 |

| A.12 | AC Characteristics                         | 381 |

|      | A.12.1 Control Timing                      | 381 |

|      | A.12.2 Timer/PWM                           |     |

|      | A.12.3 MSCAN                               | 383 |

|      | A.12.4 SPI                                 | 384 |

| A.13 | Flash                                      | 387 |

| A.14 | EMC Performance                            | 387 |

|      | A.14.1 Radiated Emissions                  | 388 |

## Appendix B Timer Pulse-Width Modulator (TPMV2)

|             | <b>B.0.1</b>  | Features                                               | 389 |

|-------------|---------------|--------------------------------------------------------|-----|

|             | B.0.2         | Block Diagram                                          | 389 |

| <b>B</b> .1 | Externa       | l Signal Description                                   | 391 |

|             | <b>B</b> .1.1 | External TPM Clock Sources                             | 391 |

|             | B.1.2         | TPMxCHn — TPMx Channel n I/O Pins                      | 391 |

| B.2         | Register      | Definition                                             | 391 |

|             |               | Timer Status and Control Register (TPMxSC)             |     |

|             | B.2.2         | Timer Counter Registers (TPMxCNTH:TPMxCNTL)            | 393 |

|             | B.2.3         | Timer Counter Modulo Registers (TPMxMODH:TPMxMODL)     | 394 |

|             | B.2.4         | Timer Channel n Status and Control Register (TPMxCnSC) | 395 |

|             | B.2.5         | Timer Channel Value Registers (TPMxCnVH:TPMxCnVL)      | 396 |

| B.3         | Function      | nal Description                                        | 397 |

|             | <b>B.3.1</b>  | Counter                                                | 397 |

|             |               |                                                        |     |

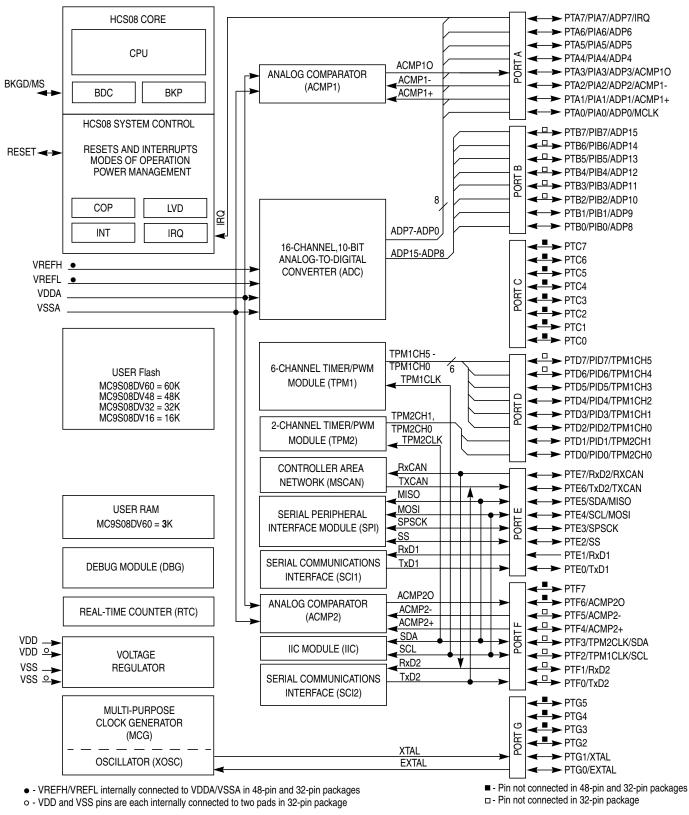

**Chapter 1 Device Overview**

#### **Chapter 3 Modes of Operation**

Background commands are of two types:

- Non-intrusive commands, defined as commands that can be issued while the user program is running. Non-intrusive commands can be issued through the BKGD/MS pin while the MCU is in run mode; non-intrusive commands can also be executed when the MCU is in the active background mode. Non-intrusive commands include:

- Memory access commands

- Memory-access-with-status commands

- BDC register access commands

- The BACKGROUND command

- Active background commands, which can only be executed while the MCU is in active background mode. Active background commands include commands to:

- Read or write CPU registers

- Trace one user program instruction at a time

- Leave active background mode to return to the user application program (GO)

The active background mode is used to program a bootloader or user application program into the Flash program memory before the MCU is operated in run mode for the first time. When the MC9S08DV60 Series is shipped from the Freescale Semiconductor factory, the Flash program memory is erased by default unless specifically noted so there is no program that could be executed in run mode until the Flash memory is initially programmed. The active background mode can also be used to erase and reprogram the Flash memory after it has been previously programmed.

For additional information about the active background mode, refer to the Development Support chapter.

# 3.5 Wait Mode

Wait mode is entered by executing a WAIT instruction. Upon execution of the WAIT instruction, the CPU enters a low-power state in which it is not clocked. The I bit in CCR is cleared when the CPU enters the wait mode, enabling interrupts. When an interrupt request occurs, the CPU exits the wait mode and resumes processing, beginning with the stacking operations leading to the interrupt service routine.

While the MCU is in wait mode, there are some restrictions on which background debug commands can be used. Only the BACKGROUND command and memory-access-with-status commands are available when the MCU is in wait mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from wait mode and enter active background mode.

Chapter 4 Memory

Table 4-2. Direct-Page Register Summary (Sheet 2 of 3)

| Address                            | Register<br>Name | Bit 7  | 6       | 5     | 4      | 3     | 2     | 1       | Bit 0    |

|------------------------------------|------------------|--------|---------|-------|--------|-------|-------|---------|----------|

| 0x00 <b>28</b>                     | TPM1C1SC         | CH1F   | CH1IE   | MS1B  | MS1A   | ELS1B | ELS1A | 0       | 0        |

| 0x00 <b>29</b>                     | TPM1C1VH         | Bit 15 | 14      | 13    | 12     | 11    | 10    | 9       | Bit 8    |

| 0x00 <b>2A</b>                     | TPM1C1VL         | Bit 7  | 6       | 5     | 4      | 3     | 2     | 1       | Bit 0    |

| 0x00 <b>2B</b>                     | TPM1C2SC         | CH2F   | CH2IE   | MS2B  | MS2A   | ELS2B | ELS2A | 0       | 0        |

| 0x00 <b>2C</b>                     | TPM1C2VH         | Bit 15 | 14      | 13    | 12     | 11    | 10    | 9       | Bit 8    |

| 0x00 <b>2D</b>                     | TPM1C2VL         | Bit 7  | 6       | 5     | 4      | 3     | 2     | 1       | Bit 0    |

| 0x00 <b>2E</b>                     | TPM1C3SC         | CH3F   | CH3IE   | MS3B  | MS3A   | ELS3B | ELS3A | 0       | 0        |

| 0x00 <b>2F</b>                     | TPM1C3VH         | Bit 15 | 14      | 13    | 12     | 11    | 10    | 9       | Bit 8    |

| 0x00 <b>30</b>                     | TPM1C3VL         | Bit 7  | 6       | 5     | 4      | 3     | 2     | 1       | Bit 0    |

| 0x00 <b>31</b>                     | TPM1C4SC         | CH4F   | CH4IE   | MS4B  | MS4A   | ELS4B | ELS4A | 0       | 0        |

| 0x00 <b>32</b>                     | TPM1C4VH         | Bit 15 | 14      | 13    | 12     | 11    | 10    | 9       | Bit 8    |

| 0x00 <b>33</b>                     | TPM1C4VL         | Bit 7  | 6       | 5     | 4      | 3     | 2     | 1       | Bit 0    |

| 0x00 <b>34</b>                     | TPM1C5SC         | CH5F   | CH5IE   | MS5B  | MS5A   | ELS5B | ELS5A | 0       | 0        |

| 0x00 <b>35</b>                     | TPM1C5VH         | Bit 15 | 14      | 13    | 12     | 11    | 10    | 9       | Bit 8    |

| 0x00 <b>36</b>                     | TPM1C5VL         | Bit 7  | 6       | 5     | 4      | 3     | 2     | 1       | Bit 0    |

| 0x00 <b>37</b>                     | Reserved         | —      | —       | _     | —      | —     | —     | —       | —        |

| 0x00 <b>38</b>                     | SCI1BDH          | LBKDIE | RXEDGIE | 0     | SBR12  | SBR11 | SBR10 | SBR9    | SBR8     |

| 0x00 <b>39</b>                     | SCI1BDL          | SBR7   | SBR6    | SBR5  | SBR4   | SBR3  | SBR2  | SBR1    | SBR0     |

| 0x00 <b>3A</b>                     | SCI1C1           | LOOPS  | SCISWAI | RSRC  | М      | WAKE  | ILT   | PE      | PT       |

| 0x00 <b>3B</b>                     | SCI1C2           | TIE    | TCIE    | RIE   | ILIE   | TE    | RE    | RWU     | SBK      |

| 0x00 <b>3C</b>                     | SCI1S1           | TDRE   | TC      | RDRF  | IDLE   | OR    | NF    | FE      | PF       |

| 0x00 <b>3D</b>                     | SCI1S2           | LBKDIF | RXEDGIF | 0     | RXINV  | RWUID | BRK13 | LBKDE   | RAF      |

| 0x00 <b>3E</b>                     | SCI1C3           | R8     | Т8      | TXDIR | TXINV  | ORIE  | NEIE  | FEIE    | PEIE     |

| 0x00 <b>3F</b>                     | SCI1D            | Bit 7  | 6       | 5     | 4      | 3     | 2     | 1       | Bit 0    |

| 0x00 <b>40</b>                     | SCI2BDH          | LBKDIE | RXEDGIE | 0     | SBR12  | SBR11 | SBR10 | SBR9    | SBR8     |

| 0x00 <b>41</b>                     | SCI2BDL          | SBR7   | SBR6    | SBR5  | SBR4   | SBR3  | SBR2  | SBR1    | SBR0     |

| 0x00 <b>42</b>                     | SCI2C1           | LOOPS  | SCISWAI | RSRC  | М      | WAKE  | ILT   | PE      | PT       |

| 0x00 <b>43</b>                     | SCI2C2           | TIE    | TCIE    | RIE   | ILIE   | TE    | RE    | RWU     | SBK      |

| 0x00 <b>44</b>                     | SCI2S1           | TDRE   | TC      | RDRF  | IDLE   | OR    | NF    | FE      | PF       |

| 0x00 <b>45</b>                     | SCI2S2           | LBKDIF | RXEDGIF | 0     | RXINV  | RWUID | BRK13 | LBKDE   | RAF      |

| 0x00 <b>46</b>                     | SCI2C3           | R8     | T8      | TXDIR | TXINV  | ORIE  | NEIE  | FEIE    | PEIE     |

| 0x00 <b>47</b>                     | SCI2D            | Bit 7  | 6       | 5     | 4      | 3     | 2     | 1       | Bit 0    |

| 0x00 <b>48</b>                     | MCGC1            | CL     | KS      |       | RDIV   |       | IREFS | IRCLKEN | IREFSTEN |

| 0x00 <b>49</b>                     | MCGC2            | BE     | DIV     | RANGE | HGO    | LP    | EREFS | ERCLKEN | EREFSTEN |

| 0x00 <b>4A</b>                     | MCGTRM           |        |         |       | TR     | IM    |       |         |          |

| 0x00 <b>4B</b>                     | MCGSC            | LOLS   | LOCK    | PLLST | IREFST | CLI   | KST   | OSCINIT | FTRIM    |

| 0x00 <b>4C</b>                     | MCGC3            | LOLIE  | PLLS    | CME   | 0      |       | VI    | DIV     |          |

| 0x00 <b>4D</b> –<br>0x00 <b>4F</b> | Reserved         |        |         |       |        |       |       |         | -        |

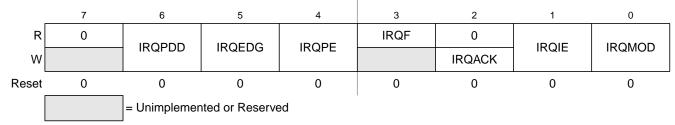

## 5.8.1 Interrupt Pin Request Status and Control Register (IRQSC)

This direct page register includes status and control bits which are used to configure the IRQ function, report status, and acknowledge IRQ events.

#### Figure 5-2. Interrupt Request Status and Control Register (IRQSC)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>IRQPDD | Interrupt Request (IRQ) Pull Device Disable— This read/write control bit is used to disable the internal pull-up/pull-down device when the IRQ pin is enabled (IRQPE = 1) allowing for an external device to be used.<br>0 IRQ pull device enabled if IRQPE = 1.<br>1 IRQ pull device disabled if IRQPE = 1.                                                                                                                                                                                                                                                                                                             |

| 5<br>IRQEDG | Interrupt Request (IRQ) Edge Select — This read/write control bit is used to select the polarity of edges or levels on the IRQ pin that cause IRQF to be set. The IRQMOD control bit determines whether the IRQ pin is sensitive to both edges and levels or only edges. When the IRQ pin is enabled as the IRQ input and is configured to detect rising edges, it has a pull-down. When the IRQ pin is enabled as the IRQ input and is configured to detect falling edges, it has a pull-up.<br>0 IRQ is falling edge or falling edge/low-level sensitive.<br>1 IRQ is rising edge or rising edge/high-level sensitive. |

| 4<br>IRQPE  | <ul> <li>IRQ Pin Enable — This read/write control bit enables the IRQ pin function. When this bit is set the IRQ pin can be used as an interrupt request.</li> <li>IRQ pin function is disabled.</li> <li>IRQ pin function is enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

| 3<br>IRQF   | <ul> <li>IRQ Flag — This read-only status bit indicates when an interrupt request event has occurred.</li> <li>0 No IRQ request.</li> <li>1 IRQ event detected.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2<br>IRQACK | <b>IRQ Acknowledge</b> — This write-only bit is used to acknowledge interrupt request events (write 1 to clear IRQF). Writing 0 has no meaning or effect. Reads always return 0. If edge-and-level detection is selected (IRQMOD = 1), IRQF cannot be cleared while the IRQ pin remains at its asserted level.                                                                                                                                                                                                                                                                                                           |

| 1<br>IRQIE  | <ul> <li>IRQ Interrupt Enable — This read/write control bit determines whether IRQ events generate an interrupt request.</li> <li>0 Interrupt request when IRQF set is disabled (use polling).</li> <li>1 Interrupt requested whenever IRQF = 1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                              |

| 0<br>IRQMOD | <ul> <li>IRQ Detection Mode — This read/write control bit selects either edge-only detection or edge-and-level detection. The IRQEDG control bit determines the polarity of edges and levels that are detected as interrupt request events. See Section 5.5.2.2, "Edge and Level Sensitivity" for more details.</li> <li>IRQ event on falling edges or rising edges only.</li> <li>IRQ event on falling edges and low levels or on rising edges and high levels.</li> </ul>                                                                                                                                              |

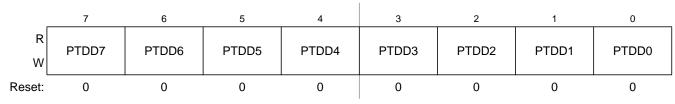

## 6.5.4 Port D Registers

Port D is controlled by the registers listed below.

### 6.5.4.1 Port D Data Register (PTDD)

#### Figure 6-24. Port D Data Register (PTDD)

#### Table 6-22. PTDD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTDD[7:0] | Port D Data Register Bits — For port D pins that are inputs, reads return the logic level on the pin. For port D pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port D pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTDD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups/pull-downs disabled. |

### 6.5.4.2 Port D Data Direction Register (PTDDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTDDD7 | PTDDD6 | PTDDD5 | PTDDD4 | PTDDD3 | PTDDD2 | PTDDD1 | PTDDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-25. Port D Data Direction Register (PTDDD)

#### Table 6-23. PTDDD Register Field Descriptions

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data Direction for Port D Bits</b> — These read/write bits control the direction of port D pins and what is read for PTDD reads.                                             |

|       | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port D bit n and PTDD reads return the contents of PTDDn.</li> </ol> |

### 8.1.1 Features

Key features of the MCG module are:

- Frequency-locked loop (FLL)

- 0.2% resolution using internal 32-kHz reference

- 2% deviation over voltage and temperature using internal 32-kHz reference

- Internal or external reference can be used to control the FLL

- Phase-locked loop (PLL)

- Voltage-controlled oscillator (VCO)

- Modulo VCO frequency divider

- Phase/Frequency detector

- Integrated loop filter

- Lock detector with interrupt capability

- Internal reference clock

- Nine trim bits for accuracy

- Can be selected as the clock source for the MCU

- External reference clock

- Control for external oscillator

- Clock monitor with reset capability

- Can be selected as the clock source for the MCU

- Reference divider is provided

- Clock source selected can be divided down by 1, 2, 4, or 8

- BDC clock (MCGLCLK) is provided as a constant divide by 2 of the DCO output whether in an FLL or PLL mode.

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

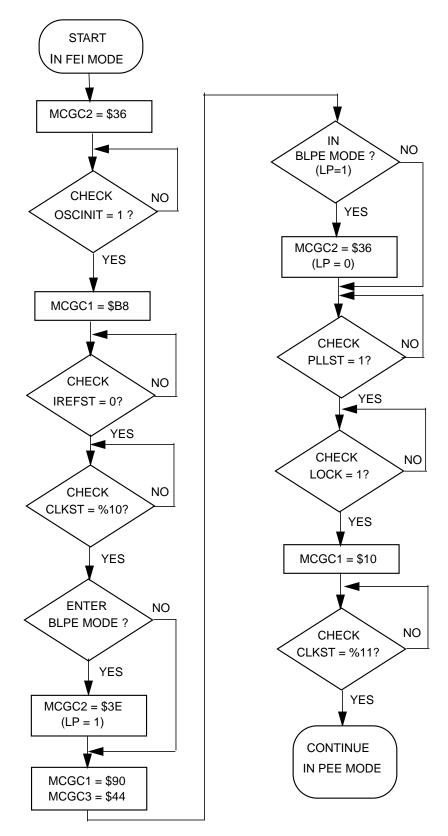

Figure 8-9. Flowchart of FEI to PEE Mode Transition using a 4 MHz crystal

### 9.1.2 Features

The ACMP has the following features:

- Full rail to rail supply operation.

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output.

- Option to compare to fixed internal bandgap reference voltage.

- Option to allow comparator output to be visible on a pin, ACMPxO.

### 9.1.3 Modes of Operation

This section defines the ACMP operation in wait, stop, and background debug modes.

#### 9.1.3.1 ACMP in Wait Mode

The ACMP continues to run in wait mode if enabled before executing the appropriate instruction. Therefore, the ACMP can be used to bring the MCU out of wait mode if the ACMP interrupt is enabled (ACIE is set). For lowest possible current consumption, the ACMP should be disabled by software if not required as an interrupt source during wait mode.

### 9.1.3.2 ACMP in Stop Modes

The ACMP is disabled in all stop modes, regardless of the settings before executing the stop instruction. Therefore, the ACMP cannot be used as a wake up source from stop modes.

During stop2 mode, the ACMP module is fully powered down. Upon wake-up from stop2 mode, the ACMP module is in the reset state.

During stop3 mode, clocks to the ACMP module are halted. No registers are affected. In addition, the ACMP comparator circuit enters a low-power state. No compare operation occurs while in stop3.

If stop3 is exited with a reset, the ACMP is put into its reset state. If stop3 is exited with an interrupt, the ACMP continues from the state it was in when stop3 was entered.

### 9.1.3.3 ACMP in Active Background Mode

When the microcontroller is in active background mode, the ACMP continues to operate normally.

# Chapter 11 Inter-Integrated Circuit (S08IICV2)

# 11.1 Introduction

The inter-integrated circuit (IIC) provides a method of communication between a number of devices. The interface is designed to operate up to 100 kbps with maximum bus loading and timing. The device is capable of operating at higher baud rates, up to a maximum of clock/20, with reduced bus loading. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400 pF.

All MC9S08DV60 Series MCUs feature the IIC, as shown in the following block diagram.

#### NOTE

Drive strength must be disabled (DSE=0) for the IIC pins when using the IIC module for correct operation.

Chapter 11 Inter-Integrated Circuit (S08IICV2)

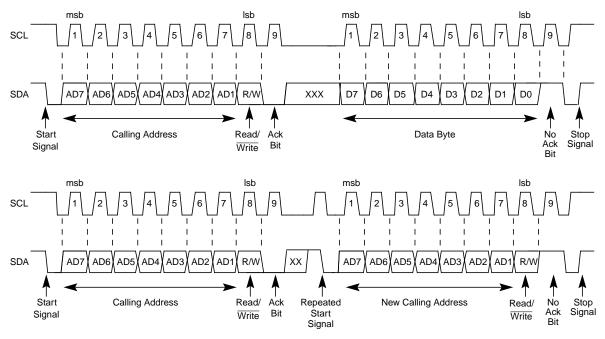

Figure 11-9. IIC Bus Transmission Signals

### 11.4.1.1 Start Signal

When the bus is free, no master device is engaging the bus (SCL and SDA lines are at logical high), a master may initiate communication by sending a start signal. As shown in Figure 11-9, a start signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

### 11.4.1.2 Slave Address Transmission

The first byte of data transferred immediately after the start signal is the slave address transmitted by the master. This is a seven-bit calling address followed by a  $R/\overline{W}$  bit. The  $R/\overline{W}$  bit tells the slave the desired direction of data transfer.

- 1 =Read transfer, the slave transmits data to the master.

- 0 = Write transfer, the master transmits data to the slave.

Only the slave with a calling address that matches the one transmitted by the master responds by sending back an acknowledge bit. This is done by pulling the SDA low at the ninth clock (see Figure 11-9).

No two slaves in the system may have the same address. If the IIC module is the master, it must not transmit an address equal to its own slave address. The IIC cannot be master and slave at the same time. However, if arbitration is lost during an address cycle, the IIC reverts to slave mode and operates correctly even if it is being addressed by another master.

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

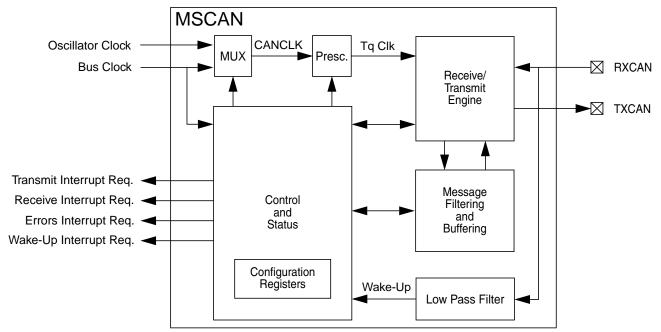

# 12.1.3 Block Diagram

Figure 12-2. MSCAN Block Diagram

# 12.2 External Signal Description

The MSCAN uses two external pins:

# 12.2.1 RXCAN — CAN Receiver Input Pin

RXCAN is the MSCAN receiver input pin.

# 12.2.2 TXCAN — CAN Transmitter Output Pin

TXCAN is the MSCAN transmitter output pin. The TXCAN output pin represents the logic level on the CAN bus:

0 = Dominant state 1 = Recessive state

## 12.2.3 CAN System

A typical CAN system with MSCAN is shown in Figure 12-3. Each CAN node is connected physically to the CAN bus lines through a transceiver device. The transceiver is capable of driving the large current needed for the CAN bus and has current protection against defective CAN or defective nodes.

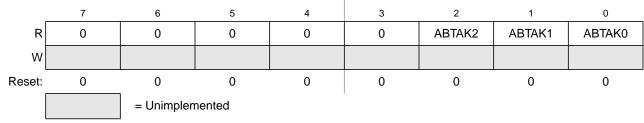

## 12.3.9 MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

The CANTAAK register indicates the successful abort of messages queued for transmission, if requested by the appropriate bits in the CANTARQ register.

Figure 12-13. MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK)

NOTE

The CANTAAK register is held in the reset state when the initialization mode is active (INITRQ = 1 and INITAK = 1).

Read: Anytime Write: Unimplemented for ABTAKx flags

#### Table 12-14. CANTAAK Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0<br>ABTAK[2:0] | <ul> <li>Abort Acknowledge — This flag acknowledges that a message was aborted due to a pending transmission abort request from the CPU. After a particular message buffer is flagged empty, this flag can be used by the application software to identify whether the message was aborted successfully or was sent anyway. The ABTAKx flag is cleared whenever the corresponding TXE flag is cleared.</li> <li>0 The message was not aborted.</li> <li>1 The message was aborted.</li> </ul> |

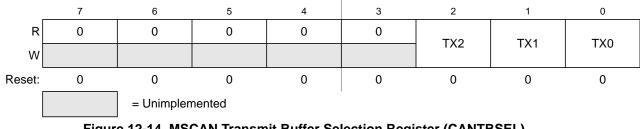

## 12.3.10 MSCAN Transmit Buffer Selection Register (CANTBSEL)

The CANTBSEL selections of the actual transmit message buffer, which is accessible in the CANTXFG register space.

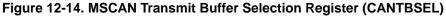

Figure 12-33. Data Segment Registers (DSR0–DSR7) — Extended Identifier Mapping

#### Table 12-31. DSR0–DSR7 Register Field Descriptions

| Field          | Description   |

|----------------|---------------|

| 7:0<br>DB[7:0] | Data bits 7:0 |

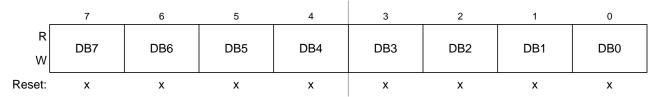

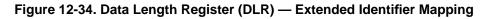

#### 12.4.4 Data Length Register (DLR)

This register keeps the data length field of the CAN frame.

= Unused; always read "x"

| Table 12-32. | <b>DLR Register Field</b> | Descriptions |

|--------------|---------------------------|--------------|

|--------------|---------------------------|--------------|

| Field | Description                                                                                                                                                                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0   | Data Length Code Bits — The data length code contains the number of bytes (data byte count) of the respective                                                                                                                                                                |

|       | message. During the transmission of a remote frame, the data length code is transmitted as programmed while the number of transmitted data bytes is always 0. The data byte count ranges from 0 to 8 for a data frame. Table 12-33 shows the effect of setting the DLC bits. |

#### Chapter 13 Serial Peripheral Interface (S08SPIV3)

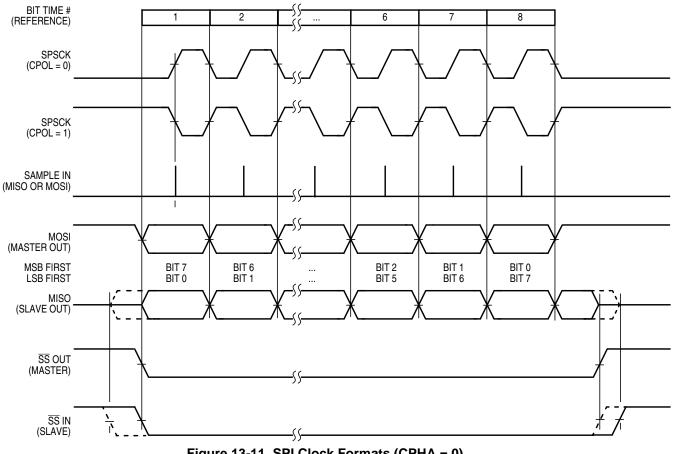

in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low at the start of the first bit time of the transfer and goes back high one-half SPSCK cycle after the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

When CPHA = 0, the slave begins to drive its MISO output with the first data bit value (MSB or LSB depending on LSBFE) when  $\overline{SS}$  goes to active low. The first SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the second SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CPHA = 0, the slave's  $\overline{SS}$  input must go to its inactive high level between transfers.

Chapter 14 Serial Communications Interface (S08SCIV4)

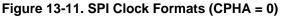

# 14.1.4 Block Diagram

Figure 14-2 shows the transmitter portion of the SCI.

Figure 14-2. SCI Transmitter Block Diagram

Chapter 15 Real-Time Counter (S08RTCV1)

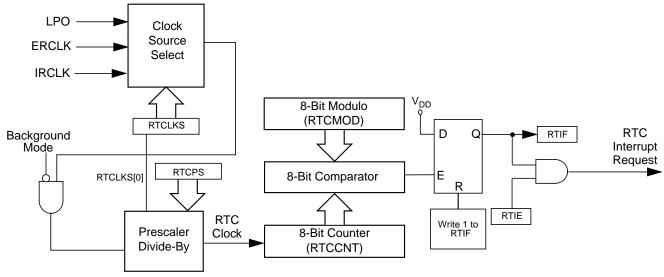

## 15.1.4 Block Diagram

The block diagram for the RTC module is shown in Figure 15-2.

Figure 15-2. Real-Time Counter (RTC) Block Diagram

# 15.2 External Signal Description

The RTC does not include any off-chip signals.

# **15.3 Register Definition**

The RTC includes a status and control register, an 8-bit counter register, and an 8-bit modulo register.

Refer to the direct-page register summary in the memory section of this document for the absolute address assignments for all RTC registers. This section refers to registers and control bits only by their names and relative address offsets.

Table 15-1 is a summary of RTC registers.

| Name    | 7 | 6      | 5      | 4 | 3    | 2     | 1 | 0 |  |  |

|---------|---|--------|--------|---|------|-------|---|---|--|--|

| RTCSC   | R | RTIF   | RTCLKS |   | RTIE | RTCPS |   |   |  |  |

| KTCSC   | W | 1X111  |        |   |      |       |   |   |  |  |

| RTCCNT  | R | RTCCNT |        |   |      |       |   |   |  |  |

| KICCINI | W |        |        |   |      |       |   |   |  |  |

| RTCMOD  | R | RTCMOD |        |   |      |       |   |   |  |  |

|         | W |        |        |   |      |       |   |   |  |  |

# Chapter 17 Development Support

# 17.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC) and the on-chip debug module (DBG). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip Flash and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins (not even in test modes). Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

# 17.1.1 Forcing Active Background

The method for forcing active background mode depends on the specific HCS08 derivative. For the MC9S08DV60, you can force active background after a power-on reset by holding the BKGD pin low as the device exits the reset condition. You can also force active background by driving BKGD low immediately after a serial background command that writes a one to the BDFR bit in the SBDFR register. If no debug pod is connected to the BKGD pin, the MCU will always reset into normal operating mode.

# A.6 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

| Num | С | Characteristic                                                     | Symbol                               | Condition                            | Min                    | Typ <sup>1</sup> | Max                    | Unit |

|-----|---|--------------------------------------------------------------------|--------------------------------------|--------------------------------------|------------------------|------------------|------------------------|------|

| 1   | _ | Operating Voltage                                                  | V <sub>DD</sub>                      |                                      | 2.7                    | _                | 5.5                    | V    |

|     | Ρ | All I/O pins, low-drive strength                                   |                                      | 5 V, I <sub>Load</sub> = -2 mA       | V <sub>DD</sub> – 1.5  | _                | —                      |      |

|     | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = -0.6 mA     | V <sub>DD</sub> – 1.5  | _                | —                      |      |

|     | С | Output high                                                        |                                      | 5 V, I <sub>Load</sub> = -0.4 mA     | V <sub>DD</sub> – 0.8  | _                | _                      |      |

| 2   | С | voltage                                                            | V <sub>OH</sub>                      | 3 V, I <sub>Load</sub> = -0.24 mA    | V <sub>DD</sub> – 0.8  | _                | _                      | V    |

|     | Ρ | All I/O pins, high-drive strength                                  |                                      | 5 V, I <sub>Load</sub> = -10 mA      | V <sub>DD</sub> – 1.5  | _                | —                      |      |

|     | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = -3 mA       | V <sub>DD</sub> – 1.5  | _                | —                      |      |

|     | С |                                                                    |                                      | 5 V, I <sub>Load</sub> = -2 mA       | V <sub>DD</sub> – 0.8  | _                | —                      |      |

|     | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = -0.4 mA     | V <sub>DD</sub> – 0.8  | —                | —                      |      |

| 3   | С | Output Max total I <sub>OH</sub> for all ports                     | I <sub>OHT</sub>                     | 5 V                                  | 0                      | —                | -100                   | mA   |

|     |   | high current                                                       |                                      | 3 V                                  | 0                      | _                | -60                    |      |

|     | Р | All I/O pins, low-drive strength                                   |                                      | 5 V, I <sub>Load</sub> = 2 mA        | —                      | _                | 1.5                    |      |

|     | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = 0.6 mA      | —                      | _                | 1.5                    |      |

|     | С | Output low                                                         |                                      | 5 V, I <sub>Load</sub> = 0.4 mA      |                        | _                | 0.8                    |      |

| 4   | С | voltage                                                            | V <sub>OL</sub>                      | 3 V, I <sub>Load</sub> = 0.24 mA     | —                      | —                | 0.8                    | V    |

|     | Ρ | All I/O pins, high-drive strength                                  |                                      | 5 V, I <sub>Load</sub> = 10 mA       | —                      | —                | 1.5                    |      |

|     | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = 3 mA        | —                      | _                | 1.5                    |      |

|     | С |                                                                    |                                      | 5 V, I <sub>Load</sub> = 2 mA        | —                      | —                | 0.8                    |      |

|     | С |                                                                    |                                      | 3 V, I <sub>Load</sub> = 0.4 mA      | —                      | _                | 0.8                    |      |

| 5   | С | Output Max total I <sub>OL</sub> for all ports                     | I <sub>OLT</sub>                     | 5 V                                  | 0                      | —                | 100                    | mA   |

|     |   | low current                                                        |                                      | 3 V                                  | 0                      |                  | 60                     |      |

| 6   | С | Input high voltage; all digital inputs                             | V <sub>IH</sub>                      | 5V                                   | 0.65 x V <sub>DD</sub> | _                | —                      |      |

| 7   | С | Input low voltage; all digital inputs                              | V <sub>IL</sub>                      | 5V                                   | —                      | _                | 0.35 x V <sub>DD</sub> | V    |

| 8   | С | Input hysteresis                                                   | V <sub>hys</sub>                     |                                      | 0.06 x V <sub>DD</sub> |                  |                        | mV   |

| 9   | Ρ | Input leakage<br>current (Per pin)<br>all input only pins          | I <sub>In</sub>                      | $V_{ln} = V_{DD} \text{ or } V_{SS}$ | —                      | 0.1              | 1                      | μA   |

| 10  | Ρ | Hi-Z (off-state) leakage<br>current (per pin)<br>all input/output  | I <sub>OZ</sub>                      | $V_{In} = V_{DD} \text{ or } V_{SS}$ | —                      | 0.1              | 1                      | μΑ   |

| 11  | P | Pullup resistors (or Pulldown <sup>2</sup> resistors when enabled) | R <sub>PU</sub> ,<br>R <sub>PD</sub> | 5 V                                  | 20                     | 45               | 65                     | kΩ   |

|     | С |                                                                    |                                      | 3 V                                  | 20                     | 45               | 65                     |      |

| 12  | Т | Input Capacitance, all pins                                        | C <sub>In</sub>                      |                                      | _                      | _                | 8                      | pF   |

| 13  | D | RAM retention voltage                                              | V <sub>RAM</sub>                     |                                      | —                      | 0.6              | 1.0                    | V    |

#### **Table A-6. DC Characteristics**