# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.25GHz                                                                |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR2, DDR3                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | SATA 3Gbps (1)                                                         |

| USB                             | USB 2.0 (2)                                                            |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8535bvjatha |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

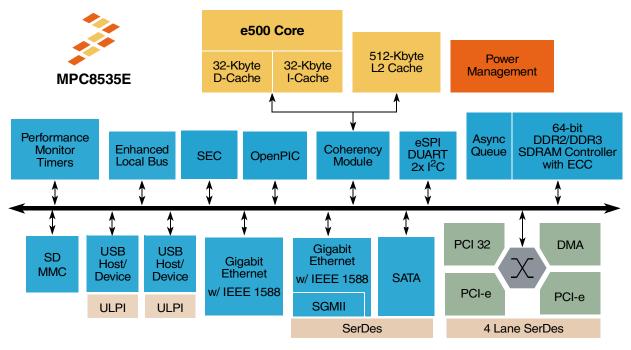

This figure shows the major functional units within the chip.

Figure 1. Chip Block Diagram

# 1 Pin Assignments and Reset States

#### NOTE

The naming convention of TSEC1 and TSEC3 is used to allow the splitting voltage rails for the eTSEC blocks and to ease the port of existing PowerQUICC III software

#### NOTE

The UART\_SOUT[0:1] and TEST\_SEL pins must be set to a proper state during POR configuration. See Table 1 for more details.

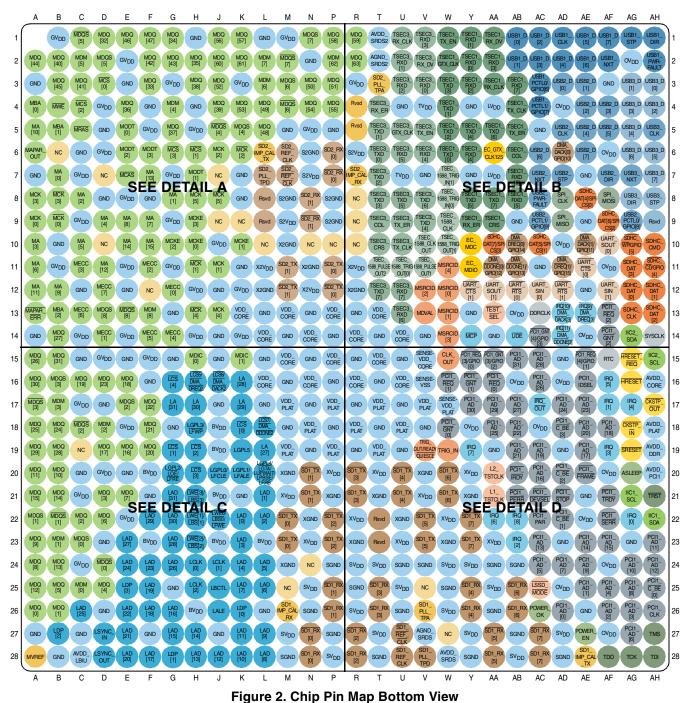

### 1.1 Pin Map

See Table 1 for the MPC8535E pinout, which is a subset of the MPC8536E.

| DETAIL D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----|

| (SNL) = (SNL) (NDD) (SNL) (S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C2_<br>SCL         | 15 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | /DD_<br>ORE        | 16 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | STP_<br>DUT        | 17 |

| PLAT GND PLAT GND GNT OVDD AD AD OVDD C_BE AD AD AD [0] [25] [22] [3] [20] [18] IN P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | /DD_<br>PLAT       | 18 |

| $(ANI) = (ANI) \cup (ANI$ | /DD_<br>DDR        | 19 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | /DD_<br>PCI1       | 20 |

| SD1_TX     XGND     SD1_TX     XVDD     SD1_TX     XGND     L1_     PCI1_     PCI1_     PCI1_     GND     PCI1_     IIC1_       [3]     XGND     [4]     XVDD     [6]     XGND     L1_     PERR     PEI1_     DEVSEL     PCI1_     GND     PCI1_     IIC1_     TI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RST                | 21 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | C1_<br>SDA         | 22 |

| XGND Rsvd XV <sub>DD</sub> 301-11 XGND 301-11 XV <sub>DD</sub> 101 AD GND AD AD GND AD GND .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CI1_<br>AD<br>[11] | 23 |

| SVD SGND SGND SGND SVDD SGND SGND AD AD AD OVDD AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | CI1_<br>AD<br>[12] | 24 |

| SGND SD1_RX SVDD NC SGND SD1_RX SVDD SD1_RX LSSD_ OVDD AD AD AD AD C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CI1_<br>_BE<br>[0] | 25 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CI1_<br>CLK        | 26 |

| SD1_RX     SVDD     SD1_<br>REF_<br>CLK     AGND_<br>SRDS     NC     SVDD     SD1_RX<br>[5]     SGND     SD1_RX<br>[7]     SVDD     POWER_<br>EN     OVDD     PCI1_<br>AD<br>[6]     T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TMS                | 27 |

| [2] CLK TPD SRUS [5] [7] TX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TDI                | 28 |

| R T U V W Y AA AB AC AD AE AF AG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AH                 |    |

Figure 6. Chip Pin Map Detail D

| Signal    | Signal Name                | Signal Name Package Pin Number                                                                                                                  |                                  | Power<br>Supply  | Notes   |

|-----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|---------|

| тск       | Test clock                 | AG28                                                                                                                                            | I                                | OV <sub>DD</sub> |         |

| TDI       | Test data in               | AH28                                                                                                                                            | I                                | OV <sub>DD</sub> | 12      |

| TDO       | Test data out              | AF28                                                                                                                                            | 0                                | OV <sub>DD</sub> | 11      |

| TMS       | Test mode select           | AH27                                                                                                                                            | I                                | OV <sub>DD</sub> | 12      |

| TRST      | Test reset                 | AH21                                                                                                                                            | I                                | OV <sub>DD</sub> | 12      |

|           |                            | DFT                                                                                                                                             |                                  |                  |         |

| L1_TSTCLK | L1 test clock              | AA21                                                                                                                                            | I                                | OV <sub>DD</sub> | 19      |

| L2_TSTCLK | L2 test clock              | AA20                                                                                                                                            | I                                | OV <sub>DD</sub> | 19      |

| LSSD_MODE | LSSD Mode                  | AC25                                                                                                                                            | I                                | OV <sub>DD</sub> | 19      |

| TEST_SEL  | Test select                | AA13                                                                                                                                            | I                                | OV <sub>DD</sub> | 19      |

|           | Power                      | Management                                                                                                                                      | ĮI                               |                  | 4       |

| ASLEEP    | Asleep                     | AG20                                                                                                                                            | 0                                | OV <sub>DD</sub> | 9,16,22 |

| POWER_OK  | Power OK                   | AC26                                                                                                                                            | I                                | OV <sub>DD</sub> | _       |

| POWER_EN  | Power enable               | AE27                                                                                                                                            | 0                                | OV <sub>DD</sub> | _       |

|           | Power and                  | Ground Signals                                                                                                                                  | <u> </u>                         |                  |         |

| OVDD      | General I/O supply         | Y18,AG2,AD4,AB16,<br>AF6,AC18,AB13,AD10,<br>AE14,AD16,AD25,<br>AF27,AE22,AF11,<br>AF20,AF24                                                     | _                                | OV <sub>DD</sub> | _       |

| LVDD      | GMAC 1 I/O supply          | AA7, AA4                                                                                                                                        | Power for<br>TSEC1<br>interfaces | LV <sub>DD</sub> | —       |

| TVDD      | GMAC 3 I/O supply          | V4,U7                                                                                                                                           | Power for<br>TSEC3<br>interfaces | TV <sub>DD</sub> | _       |

| GVDD      | SSTL2 DDR supply           | B1,B11,C7,C9,C14,<br>C17,D4,D6,R3,D15,E2,<br>E8,C24,E18,F5,E14,<br>C21,G3,G7,G9,G11,<br>H5,H12,E22,F15,J10,<br>K3,K12,K14,H14,D20,<br>E11,M1,N5 | Power for<br>DDR<br>DRAM I/O     | GV <sub>DD</sub> | _       |

| BVDD      | Local bus I/O supply       | L23,J18,J23,J19,F20,<br>F23,H26,J21                                                                                                             | Power for<br>Local Bus           | BV <sub>DD</sub> | _       |

| SVDD      | SerDes 1 core logic supply | M27,N25,P28,R24,<br>R26,T24,T27,U25,<br>W24,W26,Y24,Y27,<br>AA25,AB28,AD27                                                                      | —                                | SV <sub>DD</sub> | _       |

#### Table 1. Pinout Listing (continued)

| Signal        | Signal Name                              | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                    | Pin Type | Power<br>Supply       | Notes |

|---------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------------|-------|

| XVDD          | SerDes 1 transceiver supply              | M21,N23,P20,R22,T20,<br>U23,V21,W22,Y20,<br>AA23                                                                                                                                                                                                                                                                                                                                                                                      | _        | xv <sub>dd</sub>      | _     |

| S2VDD         | SerDes 2 core logic supply               | R6,N7,M9                                                                                                                                                                                                                                                                                                                                                                                                                              | —        | S2V <sub>DD</sub>     | _     |

| X2VDD         | SerDes 2 transceiver supply              | R11,N12,L11                                                                                                                                                                                                                                                                                                                                                                                                                           | —        | X2V <sub>DD</sub>     | _     |

| VDD_CORE      | Core, L2 logic supply                    | P13,U16,L16,M15,N14,<br>R14,P15,N16,M13,<br>U14,T13,L14,T15,R16,<br>K13                                                                                                                                                                                                                                                                                                                                                               | _        | V <sub>DD_CORE</sub>  |       |

| VDD_PLAT      | Platform logic supply                    | T19,T17,V17,U18,R18,<br>N18,M19,P19,P17,M17                                                                                                                                                                                                                                                                                                                                                                                           | —        | V <sub>DD_PLAT</sub>  | _     |

| AVDD_CORE     | CPU PLL supply                           | AH16                                                                                                                                                                                                                                                                                                                                                                                                                                  | —        | $AV_{DD\_CORE}$       | 20,28 |

| AVDD_PLAT     | Platform PLL supply                      | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                  | —        | AV <sub>DD_PLAT</sub> | 20    |

| AVDD_DDR      | DDR PLL supply                           | AH19                                                                                                                                                                                                                                                                                                                                                                                                                                  | —        | AV <sub>DD_DDR</sub>  | 20    |

| AVDD_LBIU     | Local Bus PLL supply                     | C28                                                                                                                                                                                                                                                                                                                                                                                                                                   | —        | AV <sub>DD_LBIU</sub> | 20    |

| AVDD_PCI1     | PCI PLL supply                           | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                  | —        | AV <sub>DD_PCI1</sub> | 20    |

| AVDD_SRDS     | SerDes 1 PLL supply                      | W28                                                                                                                                                                                                                                                                                                                                                                                                                                   | —        | $AV_{DD\_SRDS}$       | 20    |

| AVDD_SRDS2    | SerDes 2 PLL supply                      | T1                                                                                                                                                                                                                                                                                                                                                                                                                                    | —        | $AV_{DD\_SRDS2}$      | 20    |

| SENSEVDD_CORE | —                                        | V15                                                                                                                                                                                                                                                                                                                                                                                                                                   | —        | V <sub>DD_CORE</sub>  | 13    |

| SENSEVDD_PLAT | _                                        | W17                                                                                                                                                                                                                                                                                                                                                                                                                                   | —        | V <sub>DD_PLAT</sub>  | 13    |

| GND           | Ground                                   | D5,AE7,F4,D26,D23,<br>C12,C15,E20,D8,B10,<br>AF3,E3,J14,K21,F8,A3,<br>F16,E12,E15,D17,L1,<br>F21,H1,G13,G15,G18,<br>C6,A14,A7,G25,H4,<br>C20,J12,J15,J17,F27,<br>M5,J27,K11,L26,K7,<br>K8,T14,V14,M16,M18,<br>P14,N15,N17,N19,N2,<br>P5,P16,P18,M14,R15,<br>R17,R19,T16,T18,L17,<br>U15,U17,U19,V18,C27,<br>Y13,AE26,AA19,AE21,<br>B28,AC11,AD19,AD23,<br>L15,AD15,AG23,AE9,<br>A27,V7,Y7,AC5,U4,Y4,<br>AE12,AB9,AA14,N13,<br>R13,L13 |          |                       |       |

| XGND          | SerDes 1Transceiver pad<br>GND (xpadvss) | M20,M24,N22,P21,<br>R23,T21,U22,V20,<br>W23, Y21                                                                                                                                                                                                                                                                                                                                                                                      | —        | —                     | _     |

#### Table 1. Pinout Listing (continued)

#### Table 1. Pinout Listing (continued)

| Signal | Signal Name | Package Pin Number | Pin Type | Power<br>Supply | Notes |  |

|--------|-------------|--------------------|----------|-----------------|-------|--|

|--------|-------------|--------------------|----------|-----------------|-------|--|

#### Notes:

- 1. All multiplexed signals may be listed only once and may not re-occur.

- 2. Recommend a weak pull-up resistor (2–10 K $\Omega$ ) be placed on this pin to OV<sub>DD</sub>.

- 3. This pin must always be pulled-high.

- 4. This pin is an open drain signal.

- 5. This pin is a reset configuration pin. It has a weak internal pull-up P-FET which is enabled only when the processor is in the reset state. This pull-up is designed such that it can be overpowered by an external 4.7-kΩ pull-down resistor. However, if the signal is intended to be high after reset, and if there is any device on the net which might pull down the value of the net at reset, then a pullup or active driver is needed.

- 6. Treat these pins as no connects (NC) unless using debug address functionality.

- 7. The value of LA[28:31] during reset sets the CCB clock to SYSCLK PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See Section 22.2, "CCB/SYSCLK PLL Ratio."

- 8. The value of LALE, LGPL2 and LBCTL at reset set the e500 core clock to CCB Clock PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See the Section 22.3, "e500 Core PLL Ratio."

- 9. Functionally, this pin is an output, but structurally it is an I/O because it either samples configuration input during reset or because it has other manufacturing test functions. This pin will therefore be described as an I/O for boundary scan.

- 10.For proper state of these signals during reset, UART\_SOUT[1] must be pulled down to GND through a resistor. UART\_SOUT[0] can be pulled up or left without a resistor. However, if there is any device on the net which might pull down the value of the net at reset, then a pullup is needed on UART\_SOUT[0].

- 11. This output is actively driven during reset rather than being three-stated during reset.

- 12. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 13. These pins are connected to the V<sub>DD\_CORE</sub>/V<sub>DD\_PLAT</sub>/GND planes internally and may be used by the core power supply to improve tracking and regulation.

- 15. These pins have other manufacturing or debug test functions. It's recommended to add both pull-up resistor pads to OVDD and pull-down resistor pads to GND on board to support future debug testing when needed.

- 16. If this pin is connected to a device that pulls down during reset, an external pull-up is required to drive this pin to a safe state during reset.

- 17. This pin is only an output in FIFO mode when used as Rx Flow Control.

- 18. Do not connect.

- 19.These must be pulled up (100  $\Omega$  1 k $\Omega$ ) to OVDD.

- 20. Independent supplies derived from board VDD.

- 21. Recommend a pull-up resistor (1 K $\Omega$ ) be placed on this pin to OV<sub>DD</sub>.

- 22. The following pins must NOT be pulled down during power-on reset: MDVAL, UART\_SOUT[0], EC\_MDC, TSEC1\_TXD[3], TSEC3\_TXD[7], HRESET\_REQ, TRIG\_OUT/READY/QUIESCE, MSRCID[2:4], ASLEEP.

- 23. This pin requires an external 4.7-kΩ pull-down resistor to prevent PHY from seeing a valid Transmit Enable before it is actively driven.

- 24. General-Purpose POR configuration of user system.

### 2.4.4 eTSEC Gigabit Reference Clock Timing

This table provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications for the chip.

| Parameter/Condition                                                                     | Symbol                                 | Min      | Typical | Max         | Unit | Notes |

|-----------------------------------------------------------------------------------------|----------------------------------------|----------|---------|-------------|------|-------|

| EC_GTX_CLK125 frequency                                                                 | f <sub>G125</sub>                      | _        | 125     | _           | MHz  | —     |

| EC_GTX_CLK125 cycle time                                                                | t <sub>G125</sub>                      | —        | 8       | _           | ns   | —     |

| EC_GTX_CLK rise and fall time $LV_{DD}$ , $TV_{DD} = 2.5V$ $LV_{DD}$ , $TV_{DD} = 3.3V$ | t <sub>G125R</sub> /t <sub>G125F</sub> | _        | _       | 0.75<br>1.0 | ns   | 1     |

| EC_GTX_CLK125 duty cycle<br>GMII, TBI<br>1000Base-T for RGMII, RTBI                     | t <sub>G125H</sub> /t <sub>G125</sub>  | 45<br>47 | _       | 55<br>53    | %    | 2     |

#### Table 8. EC\_GTX\_CLK125 AC Timing Specifications

Notes:

1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5V and 2.0V for L/TVDD=2.5V, and from 0.6 and 2.7V for L/TVDD=3.3V at 0.6 V and 2.7 V.

2. EC\_GTX\_CLK125 is used to generate the GTX clock for the eTSEC transmitter with 2% degradation. EC\_GTX\_CLK125 duty cycle can be loosened from 47/53% as long as the PHY device can tolerate the duty cycle generated by the eTSEC GTX\_CLK. See Section 2.9.2.6, "RGMII and RTBI AC Timing Specifications," for duty cycle for 10Base-T and 100Base-T reference clock.

### 2.4.5 DDR Clock Timing

This table provides the DDR clock (DDRCLK) AC timing specifications for the chip.

#### Table 9. DDRCLK AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  of 3.3V ± 5%.

| Parameter/Condition       | Symbol                                | Min | Typical | Max     | Unit | Notes |

|---------------------------|---------------------------------------|-----|---------|---------|------|-------|

| DDRCLK frequency          | f <sub>DDRCLK</sub>                   | 66  | _       | 166     | MHz  | 1     |

| DDRCLK cycle time         | t <sub>DDRCLK</sub>                   | 6.0 | —       | 15.15   | ns   | _     |

| DDRCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0     | 1.2     | ns   | 2     |

| DDRCLK duty cycle         | t <sub>KHK</sub> /t <sub>DDRCLK</sub> | 40  | —       | 60      | %    | —     |

| DDRCLK jitter             | —                                     | _   | —       | +/- 150 | ps   | 3, 4  |

Notes:

1. **Caution:** The DDR complex clock to DDRCLK ratio settings must be chosen such that the resulting DDR complex clock frequency does not exceed the maximum or minimum operating frequencies. See Section 2.23.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

2. Rise and fall times for DDRCLK are measured at 0.6 V and 2.7 V.

- 3. The DDRCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track DDRCLK drivers with the specified jitter.

- 4. For spread spectrum clocking, guidelines are +0% to −1% down spread at a modulation rate between 20 kHz and 60 kHz on DDRCLK.

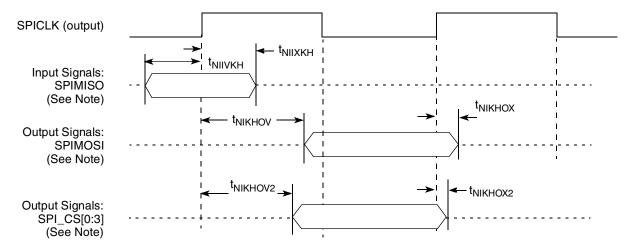

| Characteristic                          | Symbol <sup>2</sup>  | Min | Max | Unit | Note |

|-----------------------------------------|----------------------|-----|-----|------|------|

| SPI_CS outputs—Master data delay        | t <sub>NIKHOV2</sub> | _   | 6.0 | ns   | _    |

| SPI inputs—Master data input setup time | t <sub>NIIVKH</sub>  | 5   |     | ns   |      |

| SPI inputs—Master data input hold time  | t <sub>NIIXKH</sub>  | 0   | _   | ns   | _    |

Table 21. SPI AC Timing Specifications<sup>1</sup> (continued)

Notes:

1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).

3. SPCOM[RxDelay] is set to 0.

4. SPCOM[RxDelay] is set to 1.

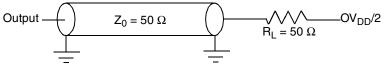

This figure provides the AC test load for the SPI.

This figure represents the AC timing from Table 21. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Note: The clock edge is selectable on SPI.

Figure 13. SPI AC Timing in Master mode (Internal Clock) Diagram

### 2.9.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps) — FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics

The electrical characteristics specified here apply to all FIFO mode, gigabit media independent interface (GMII), media independent interface (MII), ten-bit interface (TBI), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), and reduced media independent interface (RMII) signals except management data input/output (MDIO) and management data clock (MDC), and serial gigabit media independent interface (SGMII). The RGMII, RTBI and FIFO mode interfaces are defined for 2.5 V, while the GMII, MII, RMII, and TBI interfaces can operate at 3.3V.

The GMII, MII, or TBI interface timing is compliant with IEEE 802.3. The RGMII and RTBI interfaces follow the Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3 (12/10/2000). The RMII interface follows the RMII Consortium RMII Specification Version 1.2 (3/20/1998).

The electrical characteristics for MDIO and MDC are specified in Section 2.10, "Ethernet Management Interface Electrical Characteristics."

The electrical characteristics for SGMII is specified in Section 2.9.3, "SGMII Interface Electrical Characteristics." The SGMII interface conforms (with exceptions) to the Serial-GMII Specification Version 1.8.

### 2.9.1.1 GMII, MII, TBI, RGMII, RMII and RTBI DC Electrical Characteristics

All GMII, MII, TBI, RGMII, RMII and RTBI drivers and receivers comply with the DC parametric attributes specified in the following tables. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter                                                                                        | Symbol                               | Min  | Мах                                      | Unit | Notes  |

|--------------------------------------------------------------------------------------------------|--------------------------------------|------|------------------------------------------|------|--------|

| Supply voltage 3.3 V                                                                             | LV <sub>DD</sub><br>TV <sub>DD</sub> | 3.13 | 3.47                                     | V    | 1, 2   |

| Output high voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, IOH = -4.0 mA)                 | VOH                                  | 2.40 | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | —      |

| Output low voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, IOL = 4.0 mA)                   | VOL                                  | GND  | 0.50                                     | V    | —      |

| Input high voltage                                                                               | V <sub>IH</sub>                      | 1.90 | $LV_{DD}/TV_{DD} + 0.3$                  | V    | —      |

| Input low voltage                                                                                | V <sub>IL</sub>                      | -0.3 | 0.90                                     | V    | —      |

| Input high current<br>(V <sub>IN</sub> = LV <sub>DD</sub> , V <sub>IN</sub> = TV <sub>DD</sub> ) | IIH                                  | _    | 40                                       | μΑ   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                                                     | IIL                                  | -600 | —                                        | μA   | 3      |

Table 24. GMII, MII, RMII, and TBI DC Electrical Characteristics

#### Notes:

<sup>1</sup> LV<sub>DD</sub> supports eTSECs 1.

<sup>2</sup> TV<sub>DD</sub> supports eTSECs 3.

$^{3}$  The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

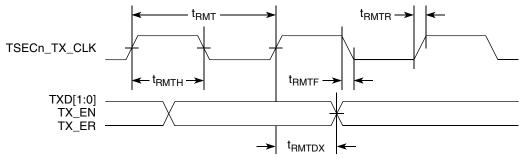

#### Table 36. RMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup> | Min | Тур | Мах  | Unit |

|-------------------------------------------------|---------------------|-----|-----|------|------|

| Rise time TSECn_TX_CLK (20%–80%)                | t <sub>RMTR</sub>   | 1.0 | —   | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%-20%)                | t <sub>RMTF</sub>   | 1.0 | —   | 2.0  | ns   |

| TSECn_TX_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>  | 2.0 | —   | 10.0 | ns   |

#### Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

This figure shows the RMII transmit AC timing diagram.

Figure 26. RMII Transmit AC Timing Diagram

#### 2.9.2.7.2 RMII Receive AC Timing Specifications

#### Table 37. RMII Receive AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition              | Symbol <sup>1</sup> | Min  | Тур  | Мах  | Unit |

|----------------------------------|---------------------|------|------|------|------|

| TSECn_RX_CLK clock period        | t <sub>RMR</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_RX_CLK duty cycle          | t <sub>RMRH</sub>   | 35   | 50   | 65   | %    |

| TSECn_RX_CLK peak-to-peak jitter | t <sub>RMRJ</sub>   |      |      | 250  | ps   |

| Rise time TSECn_RX_CLK (20%–80%) | t <sub>RMRR</sub>   | 1.0  | _    | 2.0  | ns   |

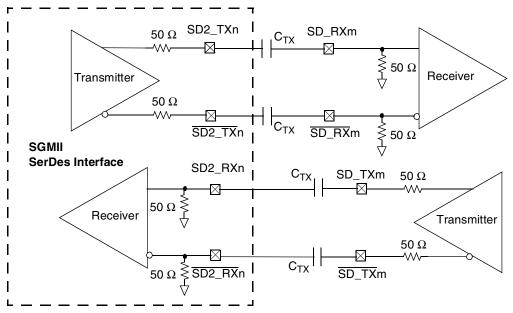

Figure 29. 4-Wire AC-Coupled SGMII Serial Link Connection Example

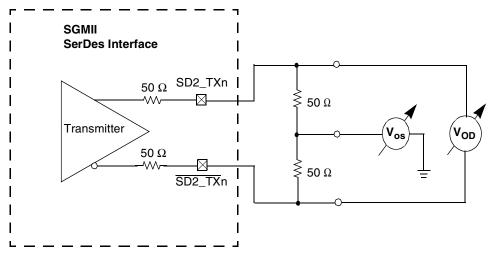

Figure 30. SGMII Transmitter DC Measurement Circuit

Table 40. SGMII DC Receiver Electrical Characteristics

| Parameter                  |          | Symbol                  | Min  | Тур | Мах  | Unit | Notes |

|----------------------------|----------|-------------------------|------|-----|------|------|-------|

| Supply Voltage             |          | X2V <sub>DD</sub>       | 0.95 | 1.0 | 1.05 | V    | —     |

| DC Input voltage range     |          | —                       |      | N/A |      | _    | 1     |

| Input differential voltage | LSTS = 0 | V <sub>RX_DIFFp-p</sub> | 100  | —   | 1200 | mV   | 2, 4  |

|                            | LSTS = 1 |                         | 175  | —   |      |      |       |

| Loss of signal threshold   | LSTS = 0 | VLOS                    | 30   | —   | 100  | mV   | 3, 4  |

|                            | LSTS = 1 |                         | 65   | —   | 175  |      |       |

| Input AC common mode v     | oltage   | V <sub>CM_ACp-p</sub>   |      |     | 100  | mV   | 5     |

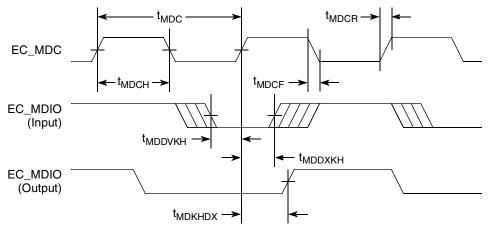

### 2.10.1 MII Management DC Electrical Characteristics

The EC\_MDC and EC\_MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for EC\_MDIO and EC\_MDC are provided in the following table.

| Parameter                                                                            | Symbol           | Min  | Мах                    | Unit |

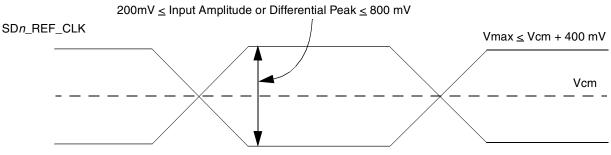

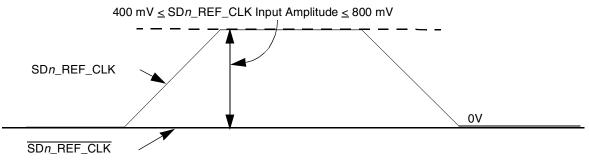

|--------------------------------------------------------------------------------------|------------------|------|------------------------|------|