#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.25GHz                                                                |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR2, DDR3                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | SATA 3Gbps (1)                                                         |

| USB                             | USB 2.0 (2)                                                            |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8535bvjatla |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

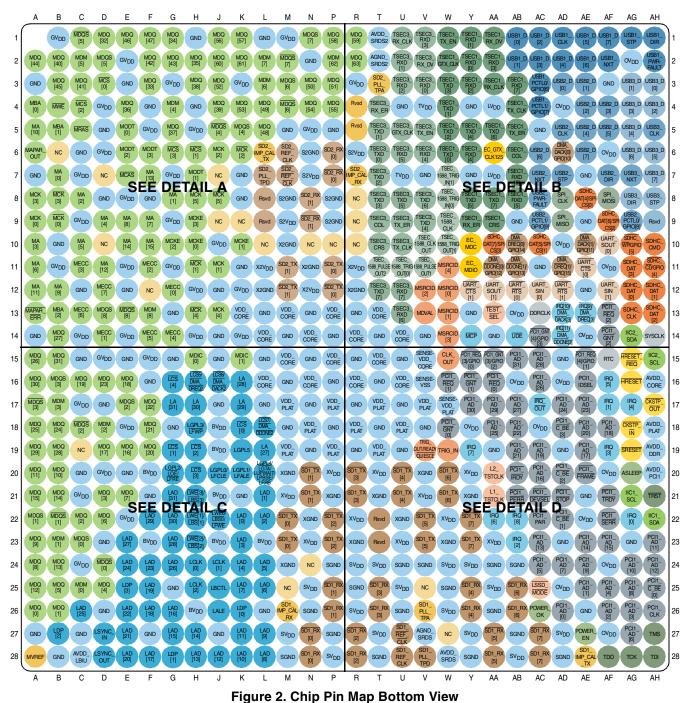

**Pin Assignments and Reset States**

## 1.1 Pin Map

See Table 1 for the MPC8535E pinout, which is a subset of the MPC8536E.

## **Pin Assignments and Reset States**

| Signal                         | Signal Name                 | Package Pin Number | Pin Type | Power<br>Supply  | Notes  |

|--------------------------------|-----------------------------|--------------------|----------|------------------|--------|

|                                | General-Purpo               | ose Input/Output   | <u> </u> |                  |        |

| GPIO[0:1]/PCI1_REQ[3:4]        | GPIO/PCI request            | Y15,AE15           | I/O      | OV <sub>DD</sub> | _      |

| GPIO[2:3]/PCI1_GNT[3:4]        | GPIO/PCI grant              | AA15,AC14          | I/O      | OV <sub>DD</sub> | —      |

| GPIO[4]/SDHC_CD                | GPIO/SDHC card detection    | AH11               | I/O      | OV <sub>DD</sub> | —      |

| GPIO[5]/SDHC_WP                | GPIO/SDHC write protection  | AG10               | I/O      | OV <sub>DD</sub> | 32     |

| GPIO[6]/USB1_PCTL0             | GPIO/USB1 PCTL0             | AC3                | I/O      | OV <sub>DD</sub> | —      |

| GPIO[7]/USB1_PCTL1             | GPIO/USB1 PCTL1             | AC4                | I/O      | $OV_{DD}$        | —      |

| GPIO[8]/USB2_PCTL0             | GPIO/USB2 PCTL0             | AG9                | I/O      | OV <sub>DD</sub> | —      |

| GPIO[9]/USB2_PCTL1             | GPIO/USB2 PCTL1             | AC9                | I/O      | OV <sub>DD</sub> | —      |

| GPIO[10:11]<br>/DMA_DACK[0:1]  | GPIO/DMA Ack                | AD6,AE10           | I/O      | $OV_{DD}$        | —      |

| GPIO[12:13]<br>/DMA_DDONE[0:1] | GPIO/DMA done               | AA11,AB11          | I/O      | OV <sub>DD</sub> |        |

| GPIO[14:15]<br>/DMA_DREQ[0:1]  | GPIO/DMA request            | AB10,AD11          | I/O      | $OV_{DD}$        | —      |

|                                | Systen                      | n Control          | 1        |                  |        |

| HRESET                         | Hard reset                  | AG16               | I        | OV <sub>DD</sub> | _      |

| HRESET_REQ                     | Hard reset - request        | AG15               | 0        | OV <sub>DD</sub> | 22     |

| SRESET                         | Soft reset                  | AG19               | I        | OV <sub>DD</sub> | —      |

| CKSTP_IN                       | CheckStop in                | AG18               | I        | OV <sub>DD</sub> | —      |

| CKSTP_OUT                      | CheckStop Output            | AH17               | 0        | $OV_{DD}$        | 2,4    |

|                                | De                          | ebug               |          |                  |        |

| TRIG_IN                        | Trigger in                  | W19                | I        | OV <sub>DD</sub> | _      |

| TRIG_OUT/READY<br>/QUIESCE     | Trigger out/Ready/Quiesce   | V19                | 0        | $OV_{DD}$        | 22     |

| MSRCID[0:1]                    | Memory debug source port ID | W12,W13            | 0        | OV <sub>DD</sub> | 6,9    |

| MSRCID[2:4]                    | Memory debug source port ID | V12, W14,W11       | 0        | OV <sub>DD</sub> | 6,9,22 |

| MDVAL                          | Memory debug data valid     | V13                | 0        | OV <sub>DD</sub> | 6,22   |

| CLK_OUT                        | Clock Out                   | W15                | 0        | OV <sub>DD</sub> | 11     |

|                                | C                           | lock               | · ·      |                  |        |

| RTC                            | Real time clock             | AF15               | Ι        | OV <sub>DD</sub> |        |

| SYSCLK                         | System clock / PCI clock    | AH14               | I        | OV <sub>DD</sub> | —      |

| DDRCLK                         | DDR clock                   | AC13               | I        | OV <sub>DD</sub> | 30     |

|                                | J.                          | TAG                | ·        |                  | •      |

# 2.1.3 Output Driver Characteristics

This table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                                                | Notes |  |

|---------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------|--|

| Local bus interface utilities signals | 25<br>35                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V                             | 1     |  |

|                                       | 45(default)<br>45(default)<br>125       | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V<br>BV <sub>DD</sub> = 1.8 V |       |  |

| PCI signals                           | 25                                      | OV <sub>DD</sub> = 3.3 V                                                         | 2     |  |

|                                       | 42 (default)                            |                                                                                  |       |  |

| DDR2 signal                           | 16<br>32 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                                                         | 3     |  |

| DDR3 signal                           | 20<br>40 (half strength mode)           | GV <sub>DD</sub> = 1.5 V                                                         | 2     |  |

| TSEC signals                          | 42                                      | LV <sub>DD</sub> = 2.5/3.3 V                                                     | —     |  |

| DUART, system control, JTAG           | 42                                      | OV <sub>DD</sub> = 3.3 V                                                         | —     |  |

| I <sup>2</sup> C                      | 150                                     | OV <sub>DD</sub> = 3.3 V                                                         | —     |  |

## Table 4. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI1\_GNT1 signal at reset.

3. The drive strength of the DDR2 or DDR3 interface in half-strength mode is at T<sub>i</sub> = 105°C and at GV<sub>DD</sub> (min)

# 2.2 Power Sequencing

The chip requires its power rails to be applied in a specific sequence in order to ensure proper chip operation. These requirements are as follows for power up:

- 1. V<sub>DD\_PLAT</sub>, V<sub>DD\_CORE</sub> (if POWER\_EN is not used to control V<sub>DD\_CORE</sub>), AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, SV<sub>DD</sub>, SV<sub>DD</sub>, TV<sub>DD</sub>, XV<sub>DD</sub> and X2V<sub>DD</sub>

- 2. [Wait for POWER\_EN to assert], then V<sub>DD CORE</sub> (if POWER\_EN is used to control V<sub>DD CORE</sub>)

- 3. GV<sub>DD</sub>

All supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-up, then the sequencing for  $GV_{DD}$  is not required.

From a system standpoint, if any of the I/O power supplies ramp prior to the VDD platform supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-up, and extra current may be drawn by the chip.

During the Deep Sleep state, the VDD core supply is removed. But all other power supplies remain applied. Therefore, there is no requirement to apply the VDD core supply before any other power rails when the silicon waking from Deep Sleep.

# 2.4.6 Platform to FIFO Restrictions

Please note the following FIFO maximum speed restrictions based on platform speed. The "platform clock (CCB) frequency" in the following formula refers to the maximum platform (CCB) frequency of the speed bins the part belongs to, which is defined in Table 73.

For FIFO GMII mode:

FIFO TX/RX clock frequency <= platform clock frequency/3.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz

For FIFO encoded mode:

FIFO TX/RX clock frequency <= platform clock frequency/3.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz

## 2.4.7 Other Input Clocks

For information on the input clocks of other functional blocks of the platform such as SerDes, and eTSEC, see the specific section of this document.

# 2.5 **RESET** Initialization

This section describes the AC electrical specifications for the RESET initialization timing requirements of the chip. This table provides the RESET initialization AC timing specifications for the DDR SDRAM component(s).

| Parameter/Condition                                                                                            | Min | Max | Unit    | Notes |

|----------------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HREST                                                                               | 100 |     | μs      | —     |

| Minimum assertion time for SRESET                                                                              | 3   |     | Sysclk  | 1     |

| PLL input setup time with stable SYSCLK before HRESET negation                                                 | 100 | —   | μs      | —     |

| Input setup time for POR configurations (other than PLL config) with respect to negation of HRESET             | 4   | —   | SYSCLKs | 1     |

| Input hold time for all POR configurations (including PLL config) with respect to negation of HRESET           | 2   | —   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively driven POR configurations with respect to negation of HRESET | _   | 5   | SYSCLKs | 1     |

| HRESET rise time                                                                                               | _   | 1   | SYSCLK  | -     |

Table 10. RESET Initialization Timing Specifications

Notes:

1. SYSCLK is the primary clock input for the chip.

This table provides the PLL lock times.

Table 11. PLL Lock Times

| Parameter/Condition | Min | Max | Unit | Notes |

|---------------------|-----|-----|------|-------|

| PLL lock times      | —   | 100 | μs   | —     |

| Local bus PLL       | —   | 50  | μs   | —     |

| PCI bus lock time   | —   | 50  | μs   | —     |

### Table 17. DDR3 SDRAM Input AC Timing Specifications for 1.5-V Interface

At recommended operating conditions with GVDD of 1.5 V ± 5%. DDR3 data rate is between 606MHz and 667MHz.

| Parameter             | Symbol          | Min                       | Мах                       | Unit | Notes |

|-----------------------|-----------------|---------------------------|---------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | —                         | MV <sub>REF</sub> – 0.175 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.175 | —                         | V    | —     |

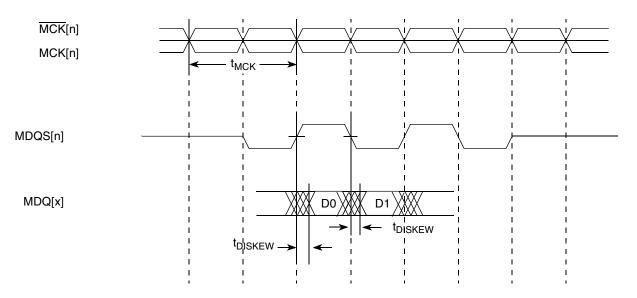

#### Table 18. DDR2 and DDR3 SDRAM Interface Input AC Timing Specifications

At recommended operating conditions with GVDD of 1.8 V  $\pm$  5% for DDR2 or 1.5 V  $\pm$  5% for DDR3.

| Parameter                         | Symbol              | Min  | Max | Unit | Notes |

|-----------------------------------|---------------------|------|-----|------|-------|

| Controller Skew for MDQS—MDQ/MECC | t <sub>CISKEW</sub> | —    | —   | ps   | 1, 2  |

| 667 MHz                           | —                   | -240 | 240 | —    | 3     |

| 533 MHz                           | _                   | -300 | 300 | —    | _     |

| 400 MHz                           | _                   | -365 | 365 | —    | _     |

#### Note:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that will be captured with MDQS[n]. This should be subtracted from the total timing budget.

- 2. The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> =+/-(T/4 abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

- 3. Maximum DDR2 and DDR3 frequency is 667MHz.

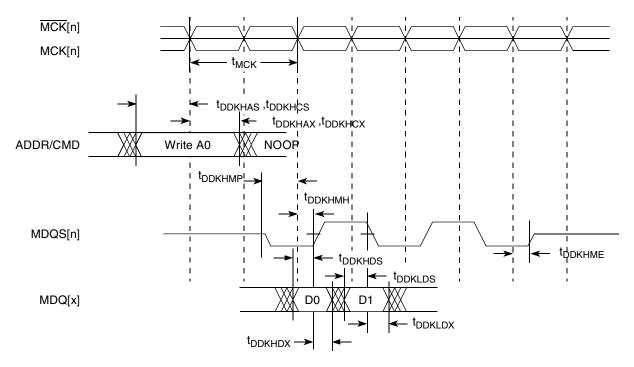

This figure shows the DDR2 and DDR3 SDRAM interface input timing diagram.

Figure 8. DDR SDRAM Input Timing Diagram

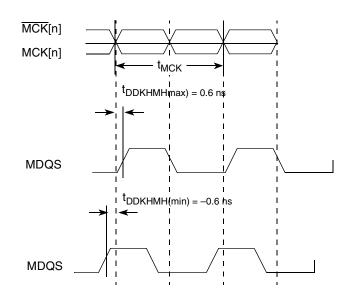

This figure shows the DDR SDRAM output timing for the MCK to MDQS skew measurement ( $t_{DDKHMH}$ ).

Figure 9. Timing Diagram for tDDKHMH

This figure shows the DDR SDRAM output timing diagram.

Figure 10. DDR SDRAM Output Timing Diagram

When operating in SGMII mode, the eTSEC EC\_GTX\_CLK125 clock is not required for this port. Instead, SerDes reference clock is required on SD2\_REF\_CLK and SD2\_REF\_CLK pins.

## 2.9.3.1 DC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 2.20, "High-Speed Serial Interfaces."

# 2.9.3.2 AC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

This table lists the SGMII SerDes reference clock AC requirements. Please note that SD2\_REF\_CLK and SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

| Symbol             | Parameter Description                                                                    |     | Typical | Max | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 10 (8)  | —   | ns    | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles |     | _       | 100 | ps    | —     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _       | 50  | ps    | 2,3   |

## Table 38. SD2\_REF\_CLK and SD2\_REF\_CLK AC Requirements

Notes:

1.8 ns applies only when 125 MHz SerDes2 reference clock frequency is selected via cfg\_srds\_sgmii\_refclk during POR.

2. In a frequency band from 150 kHz to 15 MHz, at BER of 10E-12.

3. Total peak-to-peak deterministic jitter "Dj" should be less than or equal to 50 ps.

# 2.12 enhanced Local Bus Controller (eLBC)

This section describes the DC and AC electrical specifications for the local bus interface of the chip.

## 2.12.1 Local Bus DC Electrical Characteristics

This table provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 3.3 \text{ V DC}$ .

| Parameter                                                                                      | Symbol           | Min  | Мах                    | Unit |

|------------------------------------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage 3.3V                                                                            | BV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| High-level input voltage                                                                       | V <sub>IH</sub>  | 1.9  | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                        | V <sub>IL</sub>  | -0.3 | 0.8                    | V    |

| Input current<br>(BV <sub>IN</sub> <sup>1</sup> = 0 V or BV <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IN</sub>  |      | ±5                     | μA   |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA)                 | V <sub>OH</sub>  | 2.4  | -                      | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)                   | V <sub>OL</sub>  | _    | 0.4                    | V    |

## Table 48. Local Bus DC Electrical Characteristics (3.3 V DC)

#### Note:

1. The symbol  $\mathsf{BV}_{\mathsf{IN}}$  in this case, represents the  $\mathsf{BV}_{\mathsf{IN}}$  symbol referenced in Table 1.

This table provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 2.5 \text{ V DC}$ .

## Table 49. Local Bus DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                      | Symbol           | Min       | Мах                    | Unit |

|--------------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5V                                                            | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level input voltage                                                       | V <sub>IH</sub>  | 1.70      | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                        | V <sub>IL</sub>  | -0.3      | 0.7                    | V    |

| Input current                                                                  | I <sub>IH</sub>  | —         | 10                     | μA   |

| $(BV_{IN}^{1} = 0 V \text{ or } BV_{IN} = BV_{DD})$                            | I <sub>IL</sub>  |           | -15                    |      |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -1 mA) | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 1 mA)   | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

#### Note:

1. Note that the symbol  $\mathsf{BV}_{\mathsf{IN}}$ , in this case, represents the  $\mathsf{BV}_{\mathsf{IN}}$  symbol referenced in Table 1.

This table provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 1.8 \text{ V DC}$ .

| Parameter                                                                                      | Symbol           | Condition                 | Min                     | Мах                   | Unit |

|------------------------------------------------------------------------------------------------|------------------|---------------------------|-------------------------|-----------------------|------|

| Supply voltage 1.8V                                                                            | BV <sub>DD</sub> | —                         | 1.71                    | 1.89                  | V    |

| High-level input voltage                                                                       | V <sub>IH</sub>  | _                         | 0.65*BV <sub>DD</sub>   | 0.3+BV <sub>DD</sub>  | V    |

| Low-level input voltage                                                                        | V <sub>IL</sub>  | —                         | -0.3                    | 0.35*BV <sub>DD</sub> | V    |

| Input current<br>(BV <sub>IN</sub> <sup>1</sup> = 0 V or BV <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IN</sub>  | —                         | -15                     | 10                    | μA   |

| High-level output voltage                                                                      | V <sub>OH</sub>  | I <sub>OH</sub> = -100 μA | BV <sub>DD</sub> – 0.2  | —                     | V    |

|                                                                                                |                  | I <sub>OH</sub> = -2 mA   | BV <sub>DD</sub> – 0.45 | —                     |      |

| Low-level output voltage                                                                       | V <sub>OL</sub>  | I <sub>OH</sub> = 100 μA  | —                       | 0.2                   | V    |

|                                                                                                |                  | I <sub>OH</sub> = 2 mA    | —                       | 0.45                  |      |

Note:

1. Note that the symbol  $BV_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1.

## 2.12.2 Local Bus AC Electrical Specifications

This table describes the general timing parameters of the local bus interface at  $BV_{DD} = 3.3 \text{ V DC}$ . For information about the frequency range of local bus see Section 2.23.1, "Clock Ranges."

| Parameter                                                                       | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|---------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | <b>tlbkskew</b>                     |     | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | t <sub>LBIVKH1</sub>                | 1.8 | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | t <sub>LBIVKH2</sub>                | 1.7 |     | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | t <sub>LBIXKH1</sub>                | 1.0 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | t <sub>LBIXKH2</sub>                | 1.0 |     | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | t <sub>LBOTOT</sub>                 | 1.5 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | t <sub>LBKHOV1</sub>                | _   | 2.3 | ns   | _     |

| Local bus clock to data valid for LAD/LDP                                       | t <sub>LBKHOV2</sub>                |     | 2.4 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | t <sub>LBKHOV3</sub>                |     | 2.3 | ns   | 3     |

| Local bus clock to LALE assertion                                               | t <sub>LBKHOV4</sub>                |     | 2.3 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | t <sub>LBKHOX1</sub>                | 0.7 | —   | ns   | 3     |

## Table 51. Local Bus General Timing Parameters (BV<sub>DD</sub> = 3.3 V DC)

| Parameter                                                          | Configuration | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|---------------|----------------------|-----|-----|------|-------|

| Output hold from local bus clock for LAD/LDP                       | —             | t <sub>LBKHOX2</sub> | 0.8 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) |               | t <sub>LBKHOZ1</sub> | _   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP               | —             | t <sub>LBKHOZ2</sub> |     | 2.6 | ns   | 5     |

## Table 52. Local Bus General Timing Parameters (BV<sub>DD</sub> = 2.5 V DC) (continued)

Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 2.5-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. tLBOTOT is guaranteed with LBCR[AHD] = 0.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BVDD/2.

This table describes the general timing parameters of the local bus interface at  $BV_{DD} = 1.8 \text{ V DC}$ .

| Parameter                                                                       | Configuration | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|---------------------------------------------------------------------------------|---------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | —             | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | —             | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    |       |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | —             | <b>t</b> LBKSKEW                    |     | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | —             | t <sub>LBIVKH1</sub>                | 2.4 | _   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | —             | t <sub>LBIVKH2</sub>                | 1.9 | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | —             | t <sub>LBIXKH1</sub>                | 1.1 | _   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | —             | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | —             | t <sub>LBOTOT</sub>                 | 1.2 | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | —             | t <sub>LBKHOV1</sub>                |     | 3.2 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                                       | —             | t <sub>LBKHOV2</sub>                |     | 3.2 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | —             | t <sub>LBKHOV3</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to LALE assertion                                               | —             | t <sub>LBKHOV4</sub>                |     | 3.2 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | —             | t <sub>LBKHOX1</sub>                | 0.9 | —   | ns   | 3     |

Table 53. Local Bus General Timing Parameters (BV<sub>DD</sub> = 1.8 V DC)

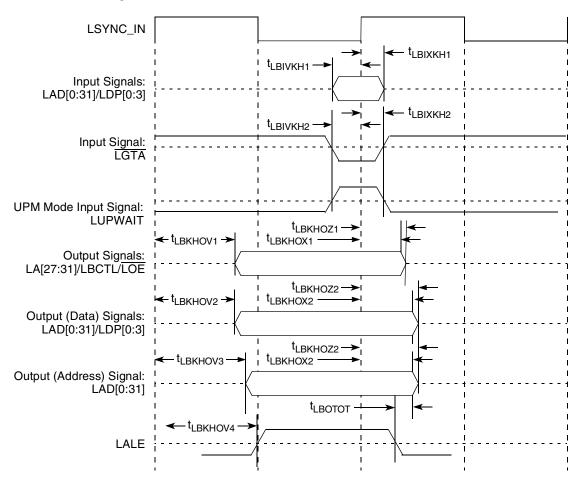

This figures show the local bus signals.

Figure 39. Local Bus Signals, Non-Special Signals Only (PLL Enabled)

## NOTE

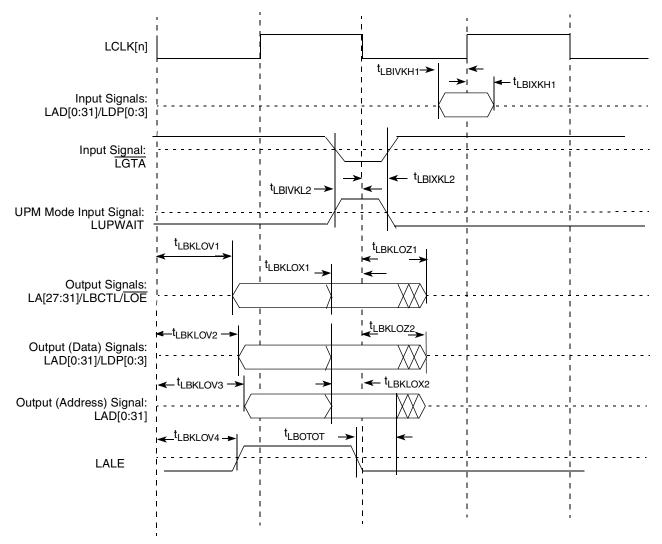

In PLL bypass mode, some signals are launched and captured on the opposite edge of LCLK[n] to that used in PLL Enable Mode. In this mode, output signals are launched at the falling edge of the LCLK[n] and inputs signals are captured at the rising edge of LCLK[n] with the exception of LGTA/LUPWAIT (which is captured at the falling edge of the LCLK[n]).

Figure 40. Local Bus Signals (PLL Bypass Mode)

This table describes the general timing parameters of the local bus interface at  $V_{DD} = 3.3$  V DC with PLL disabled.

Table 54. Local Bus General Timing Parameters—PLL Bypassed

| Parameter                                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 12   | —   | ns   | 2     |

| Local bus duty cycle                                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | —     |

| Input setup to local bus clock (except LUPWAIT)                       | t <sub>LBIVKH1</sub>                | 5.1  | —   | ns   | 4, 5  |

| LUPWAIT input setup to local bus clock                                | t <sub>LBIVKL2</sub>                | 4.2  | —   | ns   | 4, 5  |

| Input hold from local bus clock (except LUPWAIT)                      | t <sub>LBIXKH1</sub>                | -1.4 | —   | ns   | 4, 5  |

| LUPWAIT input hold from local bus clock                               | t <sub>LBIXKL2</sub>                | -2.0 | —   | ns   | 4, 5  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.4  |     | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKLOV1</sub>                | —    | 0.5 | ns   | 4     |

| Parameter                                                          | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to data valid for LAD/LDP                          | t <sub>LBKLOV2</sub> | —   | 0.5 | ns   | 4     |

| Local bus clock to address valid for LAD, and LALE                 | t <sub>LBKLOV3</sub> | _   | 0.5 | ns   | 4     |

| Local bus clock to LALE assertion                                  | t <sub>LBKLOV4</sub> | —   | 0.5 | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)         | t <sub>LBKLOX1</sub> | _   | 2.2 | ns   | 4,8   |

| Output hold from local bus clock for LAD/LDP                       | t <sub>LBKLOX2</sub> | —   | 2.2 | ns   | 4,8   |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) | t <sub>LBKLOZ1</sub> | —   | 0.1 | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP               | t <sub>LBKLOZ2</sub> |     | 0.1 | ns   | 7     |

## Table 54. Local Bus General Timing Parameters—PLL Bypassed (continued)

#### Notes:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to local bus clock for PLL bypass mode.

- 3. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 4. All signals are measured from BVDD/2 of the rising edge of local bus clock for PLL bypass mode to 0.4 x BVDD of the signal in question for 3.3-V signaling levels.

- 5. Input timings are measured at the pin.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. tLBOTOT is guaranteed with LBCR[AHD] = 0.

- 7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 8. These timing parameters for PLL bypass mode are defined in the opposite direction of the PLL enabled output hold timing parameters.

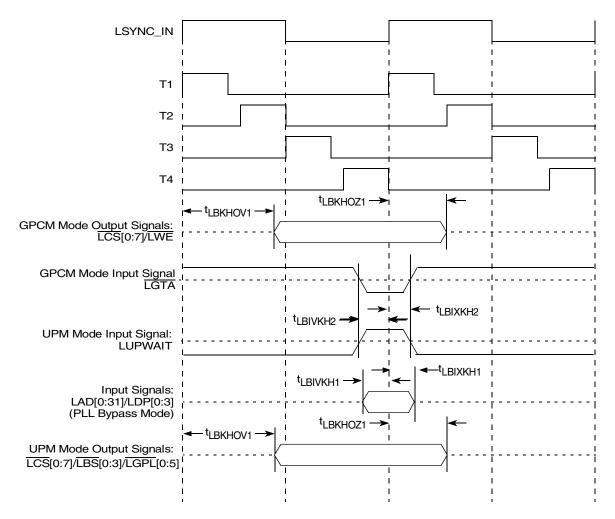

Figure 42. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 8 or 16(PLL Enabled)

# 2.13 Enhanced Secure Digital Host Controller (eSDHC)

This section describes the DC and AC electrical specifications for the eSDHC interface of the chip.

# 2.13.1 eSDHC DC Electrical Characteristics

This table provides the DC electrical characteristics for the eSDHC interface of the chip.

## Table 55. eSDHC interface DC Electrical Characteristics

At recommended operating conditions (see Table 3)

| Characteristic               | Symbol                           | Condition                          | Min          | Max         | Unit | Notes |

|------------------------------|----------------------------------|------------------------------------|--------------|-------------|------|-------|

| Input high voltage           | V <sub>IH</sub>                  | —                                  | 0.625 * OVDD | OVDD+0.3    | V    | _     |

| Input low voltage            | V <sub>IL</sub>                  | —                                  | -0.3         | 0.25 * OVDD | V    | _     |

| Input/Output leakage current | I <sub>IN</sub> /I <sub>OZ</sub> | —                                  | -10          | 10          | uA   | _     |

| Output high voltage          | V <sub>OH</sub>                  | I <sub>OH</sub> = -100 uA @OVDDmin | 0.75 * OVDD  | _           | V    | _     |

| Parameter                                                                      | Symbol <sup>1</sup> | Min | Мах | Unit |

|--------------------------------------------------------------------------------|---------------------|-----|-----|------|

| Input current<br>$(V_{IN}^{1} = 0 V \text{ or } V_{IN} = V_{DD})$              | I <sub>IN</sub>     | _   | ±5  | μA   |

| High-level output voltage<br>(OV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA) | V <sub>OH</sub>     | 2.4 | _   | V    |

| Low-level output voltage $(OV_{DD} = min, I_{OL} = 2 mA)$                      | V <sub>OL</sub>     | _   | 0.4 | V    |

Table 57. JTAG DC Electrical Characteristics (continued)

#### Notes:

1. Note that the symbol V<sub>IN</sub>, in this case, represents the OV<sub>IN</sub>,

## 2.15.2 JTAG AC Electrical Specifications

This section describes the AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the chip.

This table provides the JTAG AC timing specifications as defined in the following figures.

#### Table 58. JTAG AC Timing Specifications (Independent of SYSCLK)

At recommended operating conditions (see Table 3).

| Parameter                                         | Symbol <sup>1</sup>                   | Min | Мах  | Unit | Notes |

|---------------------------------------------------|---------------------------------------|-----|------|------|-------|

| JTAG external clock frequency of operation        | f <sub>JTG</sub>                      | 0   | 33.3 | MHz  | _     |

| JTAG external clock cycle time                    | t <sub>JTG</sub>                      | 30  | —    | ns   | —     |

| JTAG external clock pulse width measured at 1.4 V | t <sub>JTKHKL</sub>                   | 15  | —    | ns   | —     |

| JTAG external clock rise and fall times           | t <sub>JTGR</sub> & t <sub>JTGF</sub> | 0   | 2    | ns   | —     |

| TRST assert time                                  | t <sub>TRST</sub>                     | 25  | —    | ns   | 2     |

| Input setup times:                                | t <sub>JTDVKH</sub>                   | 4   | —    | ns   |       |

| Input hold times:                                 | t <sub>JTDXKH</sub>                   | 10  | —    | ns   |       |

| Output Valid times:                               | t <sub>JTKLDV</sub>                   | —   | 10   | ns   | 3     |

| Output hold times:                                | t <sub>JTKLDX</sub>                   | 0   | —    | ns   | 3     |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

3.) The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load. Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

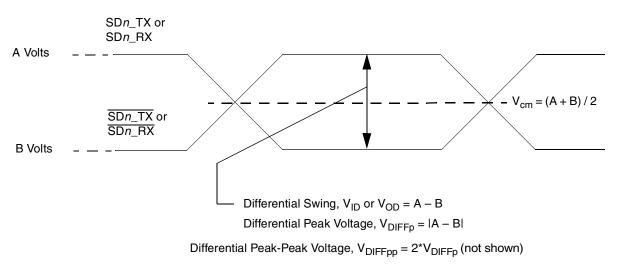

peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2*|V_{OD}|$ .

#### 6. Common Mode Voltage, V<sub>cm</sub>

The Common Mode Voltage is equal to one half of the sum of the voltages between each conductor of a balanced interchange circuit and ground. In this example, for SerDes output,  $V_{cm_out} = V_{SDn_TX} + V_{\overline{SDn_TX}} = (A + B)$ / 2, which is the arithmetic mean of the two complimentary output voltages within a differential pair. In a system, the common mode voltage may often differ from one component's output to the other's input. Sometimes, it may be even different between the receiver input and driver output circuits within the same component. It is also referred as the DC offset in some occasion.

#### Figure 57. Differential Voltage Definitions for Transmitter or Receiver

To illustrate these definitions using real values, consider the case of a CML (Current Mode Logic) transmitter that has a common mode voltage of 2.25 V and each of its outputs, TD and TD, has a swing that goes between 2.5V and 2.0V. Using these values, the peak-to-peak voltage swing of each signal (TD or TD) is 500 mV p-p, which is referred as the single-ended swing for each signal. In this example, since the differential signaling environment is fully symmetrical, the transmitter output's differential swing (V<sub>OD</sub>) has the same amplitude as each signal's single-ended swing. The differential output signal ranges between 500 mV and -500 mV, in other words, V<sub>OD</sub> is 500 mV in one phase and -500 mV in the other phase. The peak differential voltage (V<sub>DIFFp</sub>) is 500 mV. The peak-to-peak differential voltage (V<sub>DIFFp-p</sub>) is 1000 mV p-p.

## 2.20.2 SerDes Reference Clocks

The SerDes reference clock inputs are applied to an internal PLL whose output creates the clock used by the corresponding SerDes lanes. The SerDes reference clocks for PCI Express are SD1\_REF\_CLK and, SD1\_REF\_CLK. The SerDes reference clocks for the SATA and SGMII interfaces are SD2\_REF\_CLK and, SD2\_REF\_CLK.

The following sections describe the SerDes reference clock requirements and some application information.

## 2.20.2.1 SerDes Reference Clock Receiver Characteristics

Figure 58 shows a receiver reference diagram of the SerDes reference clocks.

- The supply voltage requirements for X2V<sub>DD</sub> are specified in Table 2 and Table 3.

- SerDes Reference Clock Receiver Reference Circuit Structure

- The SDn\_REF\_CLK and SDn\_REF\_CLK are internally AC-coupled differential inputs as shown in Figure 58.

Each differential clock input (SDn\_REF\_CLK or SDn\_REF\_CLK) has a 50-Ω termination to SGND (xcorevss) followed by on-chip AC-coupling.

# 2.21 PCI Express

This section describes the DC and AC electrical specifications for the PCI Express bus of the chip.

# 2.21.1 DC Requirements for PCI Express SD1\_REF\_CLK and SD1\_REF\_CLK

For more information, see Section 2.20.2, "SerDes Reference Clocks."

# 2.21.2 AC Requirements for PCI Express SerDes Clocks

This table lists AC requirements.

| Symbol             | Parameter Description                                                                    | Min | Typical | Мах | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 10      | _   | ns    | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | —   | —       | 100 | ps    | —     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _       | 50  | ps    | 1,2,3 |

Notes:

1. Tj at BER of 10E-6 86 ps Max.

2. Total peak-to-peak deterministic jitter "Dj" should be less than or equal to 42 ps.

3. Limits from "PCI Express CEM Rev 2.0" and measured per "PCI Express Rj, D, and Bit Error Rates".

## 2.21.3 Clocking Dependencies

The ports on the two ends of a link must transmit data at a rate that is within 600 parts per million 15 (ppm) of each other at all times. This is specified to allow bit rate clock sources with a +/-300 ppm tolerance.

# 2.21.4 Physical Layer Specifications

The following is a summary of the specifications for the physical layer of PCI Express on this chip. For further details as well as the specifications of the transport and data link layer, please use the PCI Express Base Specification. REV. 1.0a document.

## 2.21.4.1 Differential Transmitter (TX) Output

This table defines the specifications for the differential output at all transmitters (TXs). The parameters are specified at the component pins.

| Symbol                  | Parameter                                      | Min    | Nom | Max    | Units | Comments                                                                                                        |

|-------------------------|------------------------------------------------|--------|-----|--------|-------|-----------------------------------------------------------------------------------------------------------------|

| UI                      | Unit Interval                                  | 399.88 | 400 | 400.12 |       | Each UI is 400 ps $\pm$ 300 ppm. UI does not account for Spread Spectrum Clock dictated variations. See Note 1. |

| V <sub>TX-DIFFp-p</sub> | Differential<br>Peak-to-Peak<br>Output Voltage | 0.8    |     | 1.2    | V     | $V_{TX-DIFFp-p} = 2^*  V_{TX-D+} - V_{TX-D-} $ See Note 2.                                                      |

Table 71. Differential Transmitter (TX) Output Specifications

| Characteristic                    | JEDEC Board             | Symbol                | Value | Unit | Notes |

|-----------------------------------|-------------------------|-----------------------|-------|------|-------|

| Junction-to-ambient (@200 ft/min) | Four layer board (2s2p) | $R_{	extsf{	heta}JA}$ | 14    | °C/W | 1, 2  |

| Junction-to-board thermal         | —                       | $R_{\theta JB}$       | 10    | °C/W | 3     |

| Junction-to-case thermal          | —                       | $R_{	extsf{	heta}JC}$ | < 0.1 | °C/W | 4     |

#### Table 79. Package Thermal Characteristics (continued)

Notes

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 and JESD51-6 with the board (JESD51-9) horizontal.

- 3. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 4. Thermal resistance between the active surface of the die and the case top surface determined by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature. Actual thermal resistance is less than 0.1 •C/W

Simulations with heat sinks were done with the package mounted on the 2s2p thermal test board. The thermal interface material was a typical thermal grease such as Dow Corning 340 or Wakefield 120 grease. For system thermal modeling, the chip's thermal model without a lid is shown in Figure 72 The substrate is modeled as a block 29 x 29 x 1.2 mm with an in-plane conductivity of 19.8 W/m•K and a through-plane conductivity of 1.13 W/m•K. The solder balls and air are modeled as a single block 29 x 29 x 0.5 mm with an in-plane conductivity of 0.034 W/m•K and a through plane conductivity of 12.1 W/m•K. The die is modeled as 9.6 x 9.57 mm with a thickness of 0.75 mm. The bump/underfill layer is modeled as a collapsed thermal resistance between the die and substrate assuming a conductivity of 7.5 W/m•K in the thickness dimension of 0.07 mm. The die is centered on the substrate. The thermal model uses approximate dimensions to reduce grid. Please refer to the case outline for actual dimensions.

## 2.24.2 Recommended Thermal Model

This table shows the chip's thermal model.

| Conductivity                 | Value                                   | Units                   |  |  |  |  |

|------------------------------|-----------------------------------------|-------------------------|--|--|--|--|

| Die (9.6x9.6 × 0.85 mm)      |                                         |                         |  |  |  |  |

| Silicon                      | Temperature dependent                   | —                       |  |  |  |  |

| Bump/Underfil                | l (9.6 x 9.6 × 0.07 mm) Colla           | psed Thermal Resistance |  |  |  |  |

| Kz                           | 7.5                                     | W/m•K                   |  |  |  |  |

| Substrate (29 × 29 × 1.2 mm) |                                         |                         |  |  |  |  |

| Kx                           | 19.8                                    | W/m•K                   |  |  |  |  |

| Ку                           | 19.8                                    |                         |  |  |  |  |

| Kz                           | 1.13                                    |                         |  |  |  |  |

|                              | Solder and Air (29 $\times$ 29 $\times$ | 0.5 mm)                 |  |  |  |  |

| Kx                           | 0.034                                   | W/m∙K                   |  |  |  |  |

| Ку                           | 0.034                                   |                         |  |  |  |  |

| Kz                           | 12.1                                    |                         |  |  |  |  |

#### Table 80. Thermal Model

#### Hardware Design Considerations

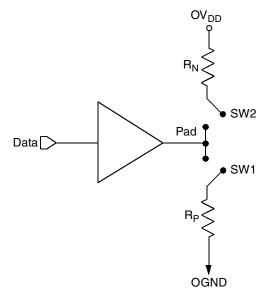

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 77). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_p$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_p$  then becomes the resistance of the pull-up devices.  $R_p$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_p + R_N)/2$ .

Figure 77. Driver Impedance Measurement

This table summarizes the signal impedance targets. The driver impedances are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet, DUART,<br>Control, Configuration, Power<br>Management | PCI                                                      | DDR DRAM                                                         | Symbol         | Unit |

|----------------|----------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------|----------------|------|

| R <sub>N</sub> | 45 Target                                                                  | 45 Target (cfg_pci_impd=1)<br>25 Target (cfg_pci_impd=0) | 18 Target (full strength mode)<br>36 Target (full strength mode) | Z <sub>0</sub> | Ω    |

| R <sub>P</sub> | 45 Target                                                                  | 45 Target (cfg_pci_impd=1)<br>25 Target (cfg_pci_impd=0) | 18 Target (full strength mode)<br>36 Target (full strength mode) | Z <sub>0</sub> | Ω    |

**Table 81. Impedance Characteristics**

Note: Nominal supply voltages. See Table 1.

# 3.9 Configuration Pin Muxing

The chip provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 k $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While  $\overline{\text{HRESET}}$  is asserted however, these pins are treated as inputs. The value presented on these pins while  $\overline{\text{HRESET}}$  is asserted, is latched when  $\overline{\text{HRESET}}$  deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Most of these sampled configuration pins are equipped with an on-chip gated resistor of approximately 20 k $\Omega$ . This value should permit the 4.7-k $\Omega$  resistor to pull the configuration pin to a valid logic low level. The pull-up resistor is enabled only during  $\overline{\text{HRESET}}$  (and for platform /system clocks after  $\overline{\text{HRESET}}$  deassertion to ensure capture of the reset value). When the input receiver is disabled the pull-up is also, thus allowing functional operation of the pin as an output with minimal signal quality or delay disruption. The default value for all configuration bits treated this way has been encoded such that a high voltage level puts the chip into the default state and external resistors are needed only when non-default settings are required by the user.

#### **Ordering Information**

The following pins must be connected to XGND if not used:

- SD1\_RX[7:4]

- SD1\_RX[7:4]

- SD1\_REF\_CLK

- SD1\_REF\_CLK

# 3.11.3 SerDes 2 Interface Entirely Unused

If the high-speed SerDes 2 interface (SGMII/SATA) is not used at all, the unused pin should be terminated as described in this section. There are several Reserved pins that need to be either left floating or connected to X2GND. See SerDes2 in Table 1 Table 1 for details.

The following pins must be left unconnected (float):

- SD2\_TX[0]

- <u>SD2\_TX[0]</u>

- Reserved pins L8, L9

The following pins must be connected to X2GND:

- SD2\_RX[0]

- SD2\_RX[0]

- SD2\_REF\_CLK

- SD2\_REF\_CLK

The POR configuration pin cfg\_srds2\_prtcl[0:2] on TSEC1\_TXD[2], TSEC3\_TXD[2], TSEC\_1588\_PUSLE\_OUT1 can be used to power down SerDes 2 block for power saving. Note that both S2VDD and X2VDD must remain powered.

# 4 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 4.1, "Part Numbers Fully Addressed by this Document."