Welcome to **E-XFL.COM**

## **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                               |

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 600MHz                                                                 |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | DDR2, DDR3                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | SATA 3Gbps (1)                                                         |

| USB                             | USB 2.0 (2)                                                            |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8535bvtakga |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

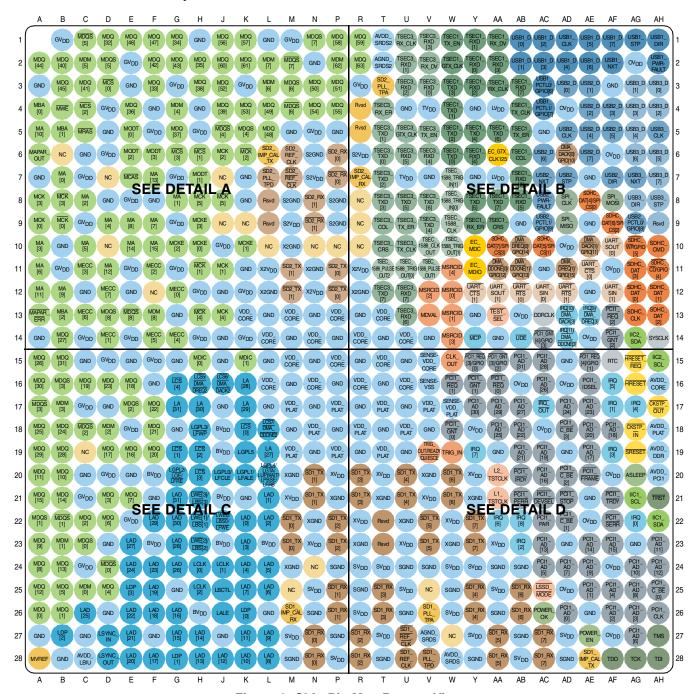

## Pin Assignments and Reset States

## 1.1 Pin Map

See Table 1 for the MPC8535E pinout, which is a subset of the MPC8536E.

Figure 2. Chip Pin Map Bottom View

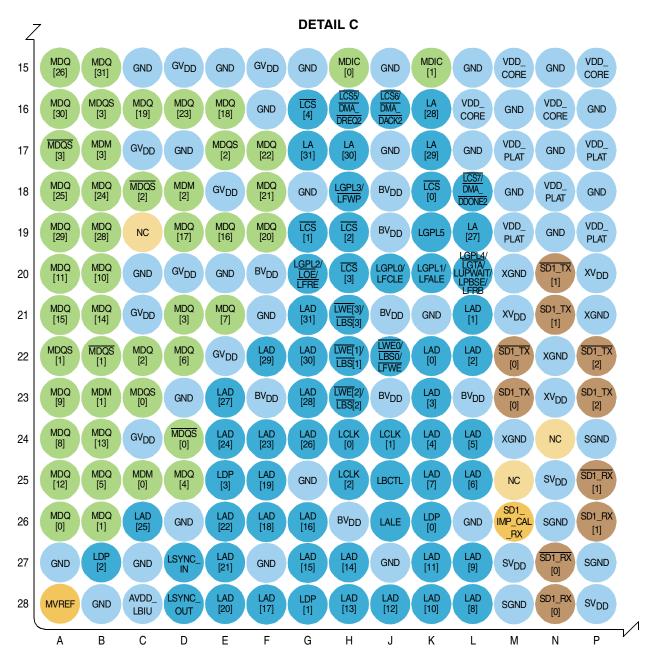

Figure 5. Chip Pin Map Detail C

**Table 1. Pinout Listing (continued)**

| Signal               | Signal Name                    | Package Pin Number                                  | Pin Type | Power<br>Supply  | Notes  |

|----------------------|--------------------------------|-----------------------------------------------------|----------|------------------|--------|

|                      | Programmable I                 | nterrupt Controller                                 |          |                  |        |

| MCP                  | Machine check processor        | Y14                                                 | I        | OV <sub>DD</sub> | _      |

| UDE                  | Unconditional debug event      | AB14                                                | I        | OV <sub>DD</sub> | _      |

| IRQ[0:8]             | External interrupts            | AG22,AF17,AB23,<br>AF19,AG17,AF16,<br>AA22,Y19,AB22 | I        | OV <sub>DD</sub> | _      |

| IRQ[9]/DMA_DREQ[3]   | External interrupt/DMA request | AE13                                                | I        | $OV_{DD}$        | 1      |

| IRQ[10]/DMA_DACK[3]  | External interrupt/DMA Ack     | AD13                                                | I/O      | OV <sub>DD</sub> | 1      |

| IRQ[11]/DMA_DDONE[3] | External interrupt/DMA done    | AD14                                                | I/O      | OV <sub>DD</sub> | 1      |

| IRQ_OUT              | Interrupt output               | AC17                                                | 0        | OV <sub>DD</sub> | 2,4    |

|                      | Ethernet Mana                  | gement Interface                                    |          |                  |        |

| EC_MDC               | Management data clock          | Y10                                                 | 0        | OV <sub>DD</sub> | 5,9,22 |

| EC_MDIO              | Management data In/Out         | Y11                                                 | I/O      | OV <sub>DD</sub> | _      |

|                      | Gigabit Re                     | ference Clock                                       | -        |                  | •      |

| EC_GTX_CLK125        | Reference clock                | AA6                                                 | I        | LV <sub>DD</sub> | 31     |

|                      | Three-Speed Ethernet Co        | entroller (Gigabit Etherne                          | et 1)    |                  | 1      |

| TSEC1_TXD[7:0]       | Transmit data                  | AA8,AA5,Y8,Y5,W3,<br>W5,W4,W6                       | 0        | LV <sub>DD</sub> | 5,9,22 |

| TSEC1_TX_EN          | Transmit Enable                | W1                                                  | 0        | LV <sub>DD</sub> | 23     |

| TSEC1_TX_ER          | Transmit Error                 | AB5                                                 | 0        | LV <sub>DD</sub> | 5,9    |

| TSEC1_TX_CLK         | Transmit clock In              | AB4                                                 | I        | LV <sub>DD</sub> | _      |

| TSEC1_GTX_CLK        | Transmit clock Out             | W2                                                  | 0        | LV <sub>DD</sub> | _      |

| TSEC1_CRS            | Carrier sense                  | AA9                                                 | I/O      | $LV_DD$          | 17     |

| TSEC1_COL            | Collision detect               | AB6                                                 | I        | $LV_DD$          | _      |

| TSEC1_RXD[7:0]       | Receive data                   | AB3,AB7,AB8,Y6,AA2,<br>Y3,Y1,Y2                     | I        | LV <sub>DD</sub> | _      |

| TSEC1_RX_DV          | Receive data valid             | AA1                                                 | I        | LV <sub>DD</sub> | _      |

| TSEC1_RX_ER          | Receive data error             | Y9                                                  | I        | LV <sub>DD</sub> | _      |

| TSEC1_RX_CLK         | Receive clock                  | AA3                                                 | I        | LV <sub>DD</sub> | _      |

|                      | Three-Speed Ethernet Co        | ontroller (Gigabit Etherne                          | et 3)    |                  |        |

| TSEC3_TXD[7:0]       | Transmit data                  | T12,V8,U8,V9,T8,T7,<br>T5,T6                        | 0        | TV <sub>DD</sub> | 5,9,22 |

| TSEC3_TX_EN          | Transmit Enable                | V5                                                  | 0        | $TV_DD$          | 23     |

| TSEC3_TX_ER          | Transmit Error                 | U9                                                  | 0        | TV <sub>DD</sub> | 5,9    |

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

## Pin Assignments and Reset States

**Table 1. Pinout Listing (continued)**

| Signal                         | Signal Name                 | Package Pin Number | Pin Type | Power<br>Supply  | Notes  |

|--------------------------------|-----------------------------|--------------------|----------|------------------|--------|

|                                | General-Purpo               | ose Input/Output   |          |                  | ı      |

| GPIO[0:1]/PCI1_REQ[3:4]        | GPIO/PCI request            | Y15,AE15           | I/O      | OV <sub>DD</sub> | _      |

| GPIO[2:3]/PCI1_GNT[3:4]        | GPIO/PCI grant              | AA15,AC14          | I/O      | OV <sub>DD</sub> | _      |

| GPIO[4]/SDHC_CD                | GPIO/SDHC card detection    | AH11               | I/O      | OV <sub>DD</sub> | _      |

| GPIO[5]/SDHC_WP                | GPIO/SDHC write protection  | AG10               | I/O      | OV <sub>DD</sub> | 32     |

| GPIO[6]/USB1_PCTL0             | GPIO/USB1 PCTL0             | AC3                | I/O      | OV <sub>DD</sub> | _      |

| GPIO[7]/USB1_PCTL1             | GPIO/USB1 PCTL1             | AC4                | I/O      | OV <sub>DD</sub> | _      |

| GPIO[8]/USB2_PCTL0             | GPIO/USB2 PCTL0             | AG9                | I/O      | OV <sub>DD</sub> | _      |

| GPIO[9]/USB2_PCTL1             | GPIO/USB2 PCTL1             | AC9                | I/O      | OV <sub>DD</sub> | _      |

| GPIO[10:11]<br>/DMA_DACK[0:1]  | GPIO/DMA Ack                | AD6,AE10           | I/O      | OV <sub>DD</sub> | _      |

| GPIO[12:13]<br>/DMA_DDONE[0:1] | GPIO/DMA done               | AA11,AB11          | I/O      | $OV_{DD}$        | _      |

| GPIO[14:15]<br>/DMA_DREQ[0:1]  | GPIO/DMA request            | AB10,AD11          | I/O      | $OV_{DD}$        | _      |

|                                | Systen                      | n Control          | 1        |                  |        |

| HRESET                         | Hard reset                  | AG16               | I        | OV <sub>DD</sub> | _      |

| HRESET_REQ                     | Hard reset - request        | AG15               | 0        | OV <sub>DD</sub> | 22     |

| SRESET                         | Soft reset                  | AG19               | Ţ        | $OV_{DD}$        | _      |

| CKSTP_IN                       | CheckStop in                | AG18               | Ţ        | OV <sub>DD</sub> | _      |

| CKSTP_OUT                      | CheckStop Output            | AH17               | 0        | OV <sub>DD</sub> | 2,4    |

|                                | De                          | ebug               |          |                  |        |

| TRIG_IN                        | Trigger in                  | W19                | I        | $OV_{DD}$        | _      |

| TRIG_OUT/READY<br>/QUIESCE     | Trigger out/Ready/Quiesce   | V19                | 0        | $OV_DD$          | 22     |

| MSRCID[0:1]                    | Memory debug source port ID | W12,W13            | 0        | $OV_{DD}$        | 6,9    |

| MSRCID[2:4]                    | Memory debug source port ID | V12, W14,W11       | 0        | $OV_{DD}$        | 6,9,22 |

| MDVAL                          | Memory debug data valid     | V13                | 0        | OV <sub>DD</sub> | 6,22   |

| CLK_OUT                        | Clock Out                   | W15                | 0        | $OV_{DD}$        | 11     |

|                                | C                           | lock               |          |                  | ı      |

| RTC                            | Real time clock             | AF15               | I        | OV <sub>DD</sub> | _      |

| SYSCLK                         | System clock / PCI clock    | AH14               | ı        | OV <sub>DD</sub> | _      |

| DDRCLK                         | DDR clock                   | AC13               | I        | OV <sub>DD</sub> | 30     |

|                                | J                           | TAG                |          |                  |        |

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

**Table 1. Pinout Listing (continued)**

| Signal Name    |                                                | Package Pin Number                                                               | Pin Type                        | Power<br>Supply       | Notes |

|----------------|------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|-----------------------|-------|

| SGND           | SerDes 1 Transceiver core logic GND (xcorevss) | M28,N26,P24,P27,<br>R25,T28,U24,U26,V24,<br>W25,Y28,AA24,AA26,<br>AB24,AB27,AD28 | _                               | _                     | _     |

| X2GND          | SerDes 2 Transceiver pad<br>GND (xpadvss)      | R12,M10,N11,L12                                                                  | _                               | _                     | _     |

| S2GND          | SerDes 2 Transceiver core logic GND (xcorevss) | P8,P9,N6,M8                                                                      | _                               | _                     | _     |

| AGND_SRDS      | SerDes 1 PLL GND                               | V27                                                                              | _                               | _                     | _     |

| AGND_SRDS2     | SerDes 2 PLL GND                               | T2                                                                               | _                               | _                     | _     |

| SENSEVSS       | GND Sensing                                    | V16                                                                              | _                               | _                     | 13    |

|                | Analo                                          | og Signals                                                                       |                                 |                       |       |

| MVREF          | SSTL2 reference voltage                        |                                                                                  | Reference<br>voltage for<br>DDR | GVDD/2                | _     |

| SD1_IMP_CAL_RX | Rx impedance calibration                       | M26                                                                              | _                               | 200Ω (±1%)<br>to GND  | _     |

| SD1_IMP_CAL_TX | Tx impedance calibration                       | AE28                                                                             | _                               | 100Ω (±1%)<br>to GND  | _     |

| SD1_PLL_TPA    | PLL test point analog                          | V26                                                                              | _                               | AVDD_SRD<br>S analog  | 18    |

| SD2_IMP_CAL_RX | Rx impedance calibration                       | R7                                                                               | _                               | 200Ω (±1%)<br>to GND  | _     |

| SD2_IMP_CAL_TX | Tx impedance calibration                       | L6                                                                               | _                               | 100Ω (±1%)<br>to GND  | _     |

| SD2_PLL_TPA    | PLL test point analog                          | Т3                                                                               | _                               | AVDD_SRD<br>S2 analog | 18    |

| Reserved       | _                                              | R4                                                                               | _                               | _                     | _     |

| Reserved       | _                                              | R5                                                                               | _                               | _                     | _     |

|                | No Co                                          | nnect Pins                                                                       |                                 |                       |       |

| NC             | _                                              | C19,D7,D10,L10,R10,<br>B6,F12,J7,P10,M25,<br>W27,N24,N10,R8,J9,<br>K9,V25,R9     | _                               | _                     | _     |

# 2.1.1 Absolute Maximum Ratings

This table provides the absolute maximum ratings.

Table 2. Absolute Maximum Ratings<sup>1</sup>

|                                                                                             | Characteristic                                                                                         | Symbol                               | Max Value                                                            | Unit | Notes |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------|------|-------|

| Core supply volta                                                                           | ge                                                                                                     | V <sub>DD_CORE</sub>                 | -0.3 to 1.21                                                         | ٧    | _     |

| Platform supply v                                                                           | oltage                                                                                                 | V <sub>DD_PLAT</sub>                 | -0.3 to 1.1                                                          | V    | _     |

| PLL core supply                                                                             | voltage                                                                                                | AV <sub>DD_CORE</sub>                | -0.3 to 1.21                                                         | V    | _     |

| PLL other supply                                                                            | voltage                                                                                                | AV <sub>DD</sub>                     | -0.3 to 1.1                                                          | V    | _     |

| Core power supp                                                                             | y for SerDes transceivers                                                                              | SV <sub>DD</sub> , S2V <sub>DD</sub> | -0.3 to 1.1                                                          | V    | _     |

| Pad power supply                                                                            | for SerDes transceivers and PCI Express                                                                | XV <sub>DD,</sub> X2V <sub>DD</sub>  | -0.3 to 1.1                                                          | V    |       |

| DDR SDRAM                                                                                   | DDR2 SDRAM Interface                                                                                   | GV <sub>DD</sub>                     | -0.3 to 1.98                                                         | V    |       |

| Controller I/O supply voltage                                                               | DDR3 SDRAM Interface                                                                                   | _                                    | -0.3 to 1.65                                                         | 1    |       |

| Three-speed Ethe                                                                            | ernet I/O                                                                                              | LV <sub>DD</sub> (eTSEC1)            | -0.3 to 3.63<br>-0.3 to 2.75                                         | ٧    | 2     |

|                                                                                             |                                                                                                        | TV <sub>DD</sub> (eTSEC3)            | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | 2     |

|                                                                                             | tem control and power management, I <sup>2</sup> C, USB,<br>d JTAG I/O voltage, MII management voltage | OV <sub>DD</sub>                     | -0.3 to 3.63                                                         | V    | _     |

| Local bus I/O volt                                                                          | age                                                                                                    | BV <sub>DD</sub>                     | -0.3 to 3.63<br>-0.3 to 2.75<br>-0.3 to 1.98                         | V    | _     |

| Input voltage                                                                               | DDR2/DDR3 DRAM signals                                                                                 | MV <sub>IN</sub>                     | -0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 3     |

|                                                                                             | DDR2/DDR3 DRAM reference                                                                               | MV <sub>REF</sub>                    | -0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | _     |

|                                                                                             | Three-speed Ethernet signals                                                                           | LV <sub>IN</sub><br>TV <sub>IN</sub> | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 3     |

|                                                                                             | Local bus signals                                                                                      | BV <sub>IN</sub>                     | -0.3 to (BV <sub>DD</sub> + 0.3)                                     | _    | _     |

| PCI, DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals |                                                                                                        | OV <sub>IN</sub>                     | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 3     |

| Storage temperat                                                                            | ure range                                                                                              | T <sub>STG</sub>                     | -55 to 150                                                           | 0C   | _     |

## Notes:

- 1. Functional and tested operating conditions are given in Table 3. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect chip reliability or cause permanent damage to the chip.

- 2. The 3.63-V maximum is only supported when the port is configured in GMII, MII, RMII or TBI modes; otherwise the 2.75V maximum applies. See Section 2.9.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

- 3. (M,L,O)V<sub>IN</sub> and MV<sub>REF</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 7.

# 2.1.2 Recommended Operating Conditions

This table provides the recommended operating conditions for this chip. Note that the values in this table are the recommended and tested operating conditions. Proper chip operation outside these conditions is not guaranteed.

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

Table 5. Power Dissipation (continued)<sup>5</sup>

| Power Mode        | Core<br>Frequen<br>cy | CCB<br>Frequen<br>cy | DDR<br>Frequen<br>cy | V <sub>DD</sub><br>Platfor<br>m | V <sub>DD</sub><br>Core | Junction<br>Tempera<br>ture | Core              | Power   | Platform          | ı Power <sup>9</sup> | Notes   |

|-------------------|-----------------------|----------------------|----------------------|---------------------------------|-------------------------|-----------------------------|-------------------|---------|-------------------|----------------------|---------|

|                   | (MHz)                 | (MHz)                | (MHz)                | (V)                             | (V)                     | (°C)                        | mean <sup>7</sup> | Max     | mean <sup>7</sup> | Max                  |         |

| Maximum (A)       |                       |                      |                      |                                 |                         | 105                         |                   | 5.3/4.4 |                   | 5.0/4.0              | 1, 3, 8 |

| Thermal (W)       | 1250                  | 500                  | 500                  | 1.0                             | 1.0                     | / 90                        |                   | 4.4/3.6 |                   | 5.0/4.0              | 1, 4, 8 |

| Typical (W)       |                       |                      |                      |                                 |                         | 65                          | 2.2               |         | 1.7               |                      | 1       |

| Doze (W)          |                       |                      |                      |                                 |                         |                             | 1.6               | 2.4     | 1.5               | 2.1                  | 1       |

| Nap (W)           |                       |                      |                      |                                 |                         |                             | 0.8               | 1.6     | 1.5               | 2.1                  | 1       |

| Sleep (W)         |                       |                      |                      |                                 |                         |                             | 0.8               | 1.6     | 1.1               | 1.7                  | 1       |

| Deep Sleep<br>(W) |                       |                      |                      |                                 |                         | 35                          | 0                 | 0       | 0.6               | 1.2                  | 1, 6    |

#### Notes:

- 1. These values specify the power consumption at nominal voltage and apply to all valid processor bus frequencies and configurations. The values do not include power dissipation for I/O supplies.

- 2. Typical power is an average value measured at the nominal recommended core voltage (V<sub>DD</sub>) and 65°C junction temperature (see Table 3) while running the Dhrystone benchmark.

- 3. Maximum power is the maximum power measured with the worst process and recommended core and platform voltage (V<sub>DD</sub>) at maximum operating junction temperature (see Table 3) while running a smoke test which includes an entirely L1-cache-resident, contrived sequence of instructions which keep the execution unit maximally busy.

- 4. Thermal power is the maximum power measured with worst case process and recommended core and platform voltage (V<sub>DD</sub>) at maximum operating junction temperature (see Table 3) while running the Dhrystone benchmark.

- 6. Maximum power is the maximum number measured with USB1, eTSEC1, and DDR blocks enabled. The Mean power is the mean power measured with only external interrupts enabled and DDR in self refresh.

- Mean power is provided for information purposes only and is the mean power consumed by a statistically significant range of devices.

- 8. Maximum operating junction temperature (see Table 3) for Commercial Tier is 90 <sup>0</sup>C, for Industrial Tier is 105 <sup>0</sup>C.

- 9. Platform power is the power supplied to all the  $V_{DD\ PLAT}$  pins.

See Section 2.23.6.1, "SYSCLK to Platform Frequency Options," for the full range of CCB frequencies that the chip supports.

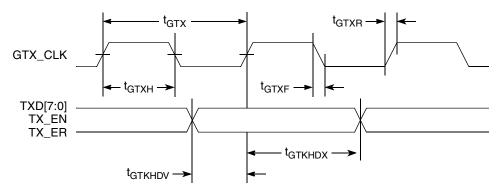

This figure shows the GMII transmit AC timing diagram.

Figure 16. GMII Transmit AC Timing Diagram

## 2.9.2.2.2 GMII Receive AC Timing Specifications

This table provides the GMII receive AC timing specifications.

## **Table 29. GMII Receive AC Timing Specifications**

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | _   | 8.0 | _   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 35  | _   | 65  | %    |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | _   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0   | _   | _   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>GRXR</sub>                   | _   | _   | 1.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>GRXF</sub>                   | _   | _   | 1.0 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)</sub>(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

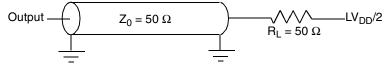

This figure provides the AC test load for eTSEC.

Figure 17. eTSEC AC Test Load

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

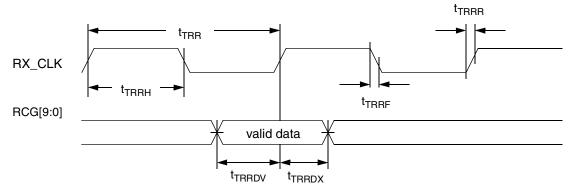

A timing diagram for TBI receive appears in the following figure.

Figure 24. TBI Single-Clock Mode Receive AC Timing Diagram

## 2.9.2.6 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

## Table 35. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 2.5 V  $\pm$  5%.

| Parameter/Condition                                    | Symbol <sup>1</sup>                 | Min  | Тур | Max  | Unit |

|--------------------------------------------------------|-------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)             | t <sub>SKRGT_TX</sub>               | -500 | 0   | 500  | ps   |

| Data to clock input skew (at receiver) <sup>2</sup>    | tskrgt_rx                           | 1.0  | _   | 2.8  | ns   |

| Clock period duration <sup>3</sup>                     | t <sub>RGT</sub>                    | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 1000BASE-T <sup>4</sup>                 | t <sub>RGTH</sub> /t <sub>RGT</sub> | 45   | _   | 55   | %    |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 4</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub> | 40   | 50  | 60   | %    |

| Rise time (20%–80%)                                    | t <sub>RGTR</sub>                   | _    | _   | 0.75 | ns   |

| Fall time (20%-80%)                                    | t <sub>RGTF</sub>                   | _    | _   | 0.75 | ns   |

### Notes:

- 1. Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design will require clocks to be routed such that an additional trace delay of greater than 1.5 ns will be added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns  $\pm$  40 ns and 40 ns  $\pm$  4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transition to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

87

## 2.18 **GPIO**

This section describes the DC and AC electrical specifications for the GPIO interface of the chip.

## 2.18.1 GPIO DC Electrical Characteristics

This table provides the DC electrical characteristics for the GPIO interface.

**Table 65. GPIO DC Electrical Characteristics**

| Parameter                                                                               | Symbol          | Min   | Max                    | Unit |

|-----------------------------------------------------------------------------------------|-----------------|-------|------------------------|------|

| High-level input voltage                                                                | V <sub>IH</sub> | 2     | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                 | V <sub>IL</sub> | - 0.3 | 0.8                    | V    |

| Input current (V <sub>IN</sub> <sup>1</sup> = 0 V or V <sub>IN</sub> = V <sub>DD)</sub> | I <sub>IN</sub> | _     | ±5                     | μΑ   |

| High-level output voltage<br>(OV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA)          | V <sub>OH</sub> | 2.4   | _                      | V    |

| Low-level output voltage<br>(OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)            | V <sub>OL</sub> | _     | 0.4                    | V    |

#### Note:

## 2.18.2 GPIO AC Electrical Specifications

This table provides the GPIO input and output AC timing specifications.

Table 66. GPIO Input and Output AC Timing Specifications<sup>1</sup>

| Characteristic                   | Symbol <sup>2</sup> | Min | Unit | Notes |

|----------------------------------|---------------------|-----|------|-------|

| GPIO inputs—minimum pulse width  | t <sub>PIWID</sub>  | 7.5 | ns   | 3     |

| GPIO outputs—minimum pulse width | t <sub>GTOWID</sub> | 12  | ns   | _     |

#### Notes:

- 1. Input specifications are measured from the 50% level of the signal to the 50% level of the rising edge of CLKIN. Timings are measured at the pin.

- 2. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

- 3. The minimum pulse width is a function of the MPX/Platform clock. The minimum pulse width must be greater than or equal to 4 times the MPX/Platform clock period.

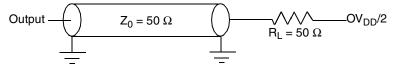

This figure provides the AC test load for the GPIO.

Figure 53. GPIO AC Test Load

<sup>1.</sup> The symbol V<sub>IN</sub>, in this case, represents the OV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

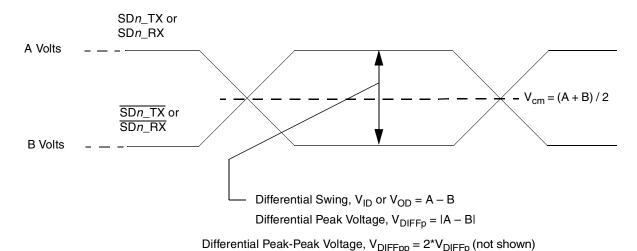

peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX\text{-DIFFp-p}} = 2*|V_{OD}|$ .

### 6. Common Mode Voltage, V<sub>cm</sub>

The Common Mode Voltage is equal to one half of the sum of the voltages between each conductor of a balanced interchange circuit and ground. In this example, for SerDes output,  $V_{cm\_out} = V_{SDn\_TX} + V_{\overline{SDn\_TX}} = (A+B)/2$ , which is the arithmetic mean of the two complimentary output voltages within a differential pair. In a system, the common mode voltage may often differ from one component's output to the other's input. Sometimes, it may be even different between the receiver input and driver output circuits within the same component. It is also referred as the DC offset in some occasion.

Figure 57. Differential Voltage Definitions for Transmitter or Receiver

To illustrate these definitions using real values, consider the case of a CML (Current Mode Logic) transmitter that has a common mode voltage of 2.25 V and each of its outputs, TD and  $\overline{\text{TD}}$ , has a swing that goes between 2.5V and 2.0V. Using these values, the peak-to-peak voltage swing of each signal (TD or  $\overline{\text{TD}}$ ) is 500 mV p-p, which is referred as the single-ended swing for each signal. In this example, since the differential signaling environment is fully symmetrical, the transmitter output's differential swing (V<sub>OD</sub>) has the same amplitude as each signal's single-ended swing. The differential output signal ranges between 500 mV and –500 mV, in other words, V<sub>OD</sub> is 500 mV in one phase and –500 mV in the other phase. The peak differential voltage (V<sub>DIFFp</sub>-p) is 500 mV. The peak-to-peak differential voltage (V<sub>DIFFp</sub>-p) is 1000 mV p-p.

## 2.20.2 SerDes Reference Clocks

The SerDes reference clock inputs are applied to an internal PLL whose output creates the clock used by the corresponding SerDes lanes. The SerDes reference clocks for PCI Express are SD1\_REF\_CLK and, SD1\_REF\_CLK. The SerDes reference clocks for the SATA and SGMII interfaces are SD2\_REF\_CLK and, SD2\_REF\_CLK.

The following sections describe the SerDes reference clock requirements and some application information.

## 2.20.2.1 SerDes Reference Clock Receiver Characteristics

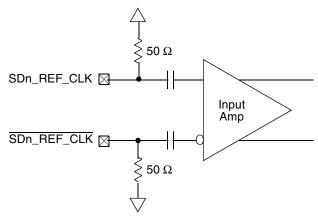

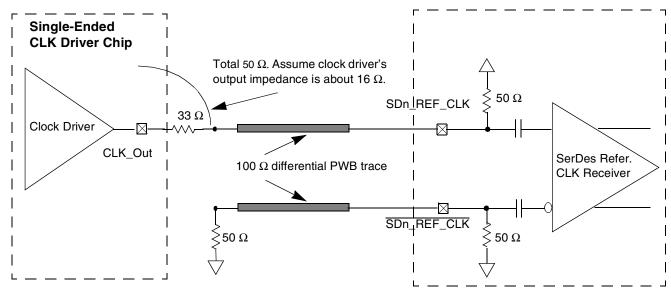

Figure 58 shows a receiver reference diagram of the SerDes reference clocks.

- The supply voltage requirements for X2V<sub>DD</sub> are specified in Table 2 and Table 3.

- SerDes Reference Clock Receiver Reference Circuit Structure

- The SDn\_REF\_CLK and  $\overline{\text{SD}n_REF_CLK}$  are internally AC-coupled differential inputs as shown in Figure 58. Each differential clock input (SDn\_REF\_CLK or  $\overline{\text{SD}n_REF_CLK}$ ) has a 50-Ω termination to SGND (xcorevss) followed by on-chip AC-coupling.

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. See the Differential Mode and Single-ended Mode description below for further detailed requirements.

- · The maximum average current requirement that also determines the common mode voltage range

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA (refer to the following bullet for more detail), since the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V/50 = 8 mA) while the minimum common mode input level is 0.1V above SnGND (xcorevss). For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0mA to 16mA (0–0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800mV with the common mode voltage at 400mV.

- If the device driving the SDn\_REF\_CLK and  $\overline{\text{SDn}_{REF}_{CLK}}$  inputs cannot drive 50  $\Omega$  to SnGND (xcorevss) DC, or it exceeds the maximum input current limitations, then it must be AC-coupled off-chip.

- The input amplitude requirement

- This requirement is described in detail in the following sections.

Figure 58. Receiver of SerDes Reference Clocks

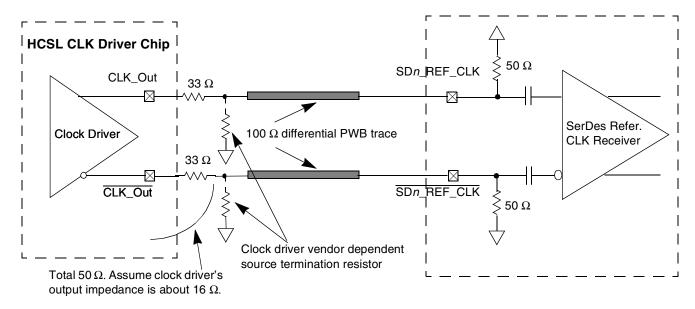

This figure shows the SerDes reference clock connection reference circuits for HCSL type clock driver. It assumes that the DC levels of the clock driver chip is compatible with chip's SerDes reference clock input's DC requirement.

Figure 62. DC-Coupled Differential Connection with HCSL Clock Driver (Reference Only)

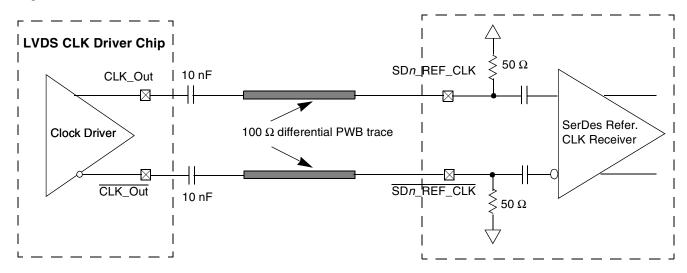

This figure shows the SerDes reference clock connection reference circuits for LVDS type clock driver. Since LVDS clock driver's common mode voltage is higher than the chip's SerDes reference clock input's allowed range (100 to 400mV), AC-coupled connection scheme must be used. It assumes the LVDS output driver features  $50-\Omega$  termination resistor. It also assumes that the LVDS transmitter establishes its own common mode level without relying on the receiver or other external component.

Figure 63. AC-Coupled Differential Connection with LVDS Clock Driver (Reference Only)

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

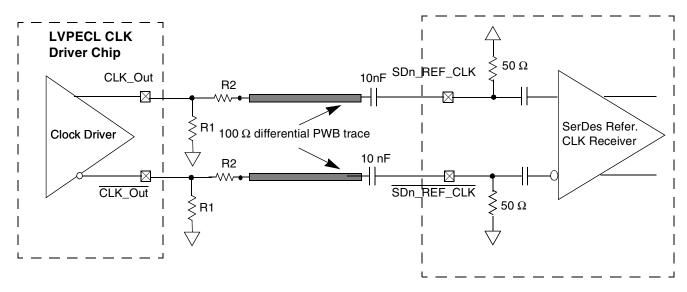

This figure shows the SerDes reference clock connection reference circuits for LVPECL type clock driver. Since LVPECL driver's DC levels (both common mode voltages and output swing) are incompatible with chip's SerDes reference clock input's DC requirement, AC-coupling has to be used. This figure assumes that the LVPECL clock driver's output impedance is  $50\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from  $140\Omega$  to  $240\Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's  $50-\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the chip's SerDes reference clock's differential input amplitude requirement (between 200mV and 800mV differential peak). For example, if the LVPECL output's differential peak is 900mV and the desired SerDes reference clock input amplitude is selected as 600mV, the attenuation factor is 0.67, which requires  $R2 = 25\Omega$ . Please consult clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 64. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

This figure shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with chip's SerDes reference clock input's DC requirement.

Figure 65. Single-Ended Connection (Reference Only)

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

| <b>Table 71. Differential Transmitter</b> | (TX) | Output S | pecifications | (continued) | ) |

|-------------------------------------------|------|----------|---------------|-------------|---|

|-------------------------------------------|------|----------|---------------|-------------|---|

| Symbol                            | Parameter                                                                                                         | Min | Nom | Max           | Units | Comments                                                                                                                                                                                                                                 |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>TX-IDLE-SET-TO-IDLE</sub>  | Maximum time to<br>transition to a valid<br>electrical idle after<br>sending an<br>electrical Idle<br>ordered set | _   | _   | 20            | UI    | After sending an Electrical Idle ordered set, the Transmitter must meet all Electrical Idle Specifications within this time. This is considered a debounce time for the Transmitter to meet Electrical Idle after transitioning from L0. |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Maximum time to transition to valid TX specifications after leaving an electrical idle condition                  | _   | _   | 20            | UI    | Maximum time to meet all TX specifications when transitioning from Electrical Idle to sending differential data. This is considered a debounce time for the TX to meet all TX specifications after leaving Electrical Idle               |

| RL <sub>TX-DIFF</sub>             | Differential Return<br>Loss                                                                                       | 12  | _   | _             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                             |

| RL <sub>TX-CM</sub>               | Common Mode<br>Return Loss                                                                                        | 6   | _   | _             | dB    | Measured over 50 MHz to 1.25 GHz. See Note 4                                                                                                                                                                                             |

| Z <sub>TX-DIFF-DC</sub>           | DC Differential TX Impedance                                                                                      | 80  | 100 | 120           | Ω     | TX DC Differential mode Low Impedance                                                                                                                                                                                                    |

| Z <sub>TX-DC</sub>                | Transmitter DC<br>Impedance                                                                                       | 40  | _   | _             | Ω     | Required TX D+ as well as D- DC Impedance during all states                                                                                                                                                                              |

| L <sub>TX-SKEW</sub>              | Lane-to-Lane<br>Output Skew                                                                                       | _   | _   | 500 +<br>2 UI | ps    | Static skew between any two Transmitter Lanes within a single Link                                                                                                                                                                       |

| Стх                               | AC Coupling<br>Capacitor                                                                                          | 75  | _   | 200           | nF    | All Transmitters shall be AC coupled. The AC coupling is required either within the media or within the transmitting component itself. See Note 8.                                                                                       |

| T <sub>crosslink</sub>            | Crosslink Random<br>Timeout                                                                                       | 0   | _   | 1             | ms    | This random timeout helps resolve conflicts in crosslink configuration by eventually resulting in only one Downstream and one Upstream Port. See Note 7.                                                                                 |

### Notes:

- 1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 52 and measured over any 250 consecutive TX UIs. (Also refer to the transmitter compliance eye diagram shown in Figure 50)

- 3. A T<sub>TX-EYE</sub> = 0.70 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.30 UI for the Transmitter collected over any 250 consecutive TX UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

- 4. The Transmitter input impedance shall result in a differential return loss greater than or equal to 12 dB and a common mode return loss greater than or equal to 6 dB over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements is 50 ohms to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50 ohm probes—see Figure 52). Note that the series capacitors C<sub>TX</sub> is optional for the return loss measurement.

- 5. Measured between 20-80% at transmitter package pins into a test load as shown in Figure 52 for both V<sub>TX-D+</sub> and V<sub>TX-D-</sub>.

- 6. See Section 4.3.1.8 of the PCI Express Base Specifications Rev 1.0a

- 7. See Section 4.2.6.3 of the PCI Express Base Specifications Rev 1.0a

- 8. SerDes transmitter does not have CTX built-in. An external AC Coupling capacitor is required.

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

## 2.23.1 Clock Ranges

This table provides the clocking specifications for the processor cores and Table 74 provides the clocking specifications for the memory bus.

|                               | Maximum Processor Core Frequency |     |         |     |          |      |          |      |      |       |

|-------------------------------|----------------------------------|-----|---------|-----|----------|------|----------|------|------|-------|

| Characteristic                | 600 MHz                          |     | 800 MHz |     | 1000 MHz |      | 1250 MHz |      | Unit | Notes |

|                               | Min                              | Max | Min     | Max | Min      | Max  | Min      | Max  |      |       |

| e500 core processor frequency | 600                              | 600 | 600     | 800 | 600      | 1000 | 600      | 1250 | MHz  | 1, 2  |

| CCB frequency                 | 400                              | 400 | 400     | 400 | 333      | 400  | 333      | 500  |      |       |

| DDR Data Rate                 | 400                              | 400 | 400     | 400 | 400      | 400  | 400      | 500  |      |       |

**Table 73. Processor Core Clocking Specifications**

### Notes:

- Caution: The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 2.23.2, "CCB/SYSCLK PLL Ratio," Section 2.23.3, "e500 Core PLL Ratio," and Section 2.23.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

- 2. The processor core frequency speed bins listed also reflect the maximum platform (CCB) and DDR data rate frequency supported by production test. Running CCB and/or DDR data rate higher than the limit shown above, although logically possible via valid clock ratio setting in some condition, is not supported.

The DDR memory controller can run in either synchronous or asynchronous mode. When running in synchronous mode, the memory bus is clocked relative to the platform clock frequency. When running in asynchronous mode, the memory bus is clocked with its own dedicated PLL. This table provides the clocking specifications for the memory bus.

|                            | Maximum Process | or Core Frequency |      | Notes      |  |

|----------------------------|-----------------|-------------------|------|------------|--|

| Characteristic             | 600, 800, 1     | 000, 1250         | Unit |            |  |

|                            | Min             | Max               |      |            |  |

| DDR Memory bus clock speed | 200             | 250               | MHz  | 1, 2, 3, 4 |  |

**Table 74. Memory Bus Clocking Specifications**

### Notes:

- Caution: The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 2.23.2, "CCB/SYSCLK PLL Ratio," Section 2.23.3, "e500 Core PLL Ratio," and Section 2.23.4, "DDR/DDRCLK PLL Ratio," for ratio settings.

- 2. The Memory bus clock refers to the chip's memory controllers' MCK[0:5] and MCK[0:5] output clocks, running at half of the DDR data rate.

- 3. In synchronous mode, the memory bus clock speed is half the platform clock frequency. In other words, the DDR data rate is the same as the platform (CCB) frequency. If the desired DDR data rate is higher than the platform (CCB) frequency, asynchronous mode must be used.

- 4. In asynchronous mode, the memory bus clock speed is dictated by its own PLL. See Section 2.23.4, "DDR/DDRCLK PLL Ratio." The memory bus clock speed must be less than or equal to the CCB clock rate which in turn must be less than the DDR data rate.

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

**Table 79. Package Thermal Characteristics (continued)**

| Characteristic                    | JEDEC Board             | Symbol          | Value | Unit | Notes |

|-----------------------------------|-------------------------|-----------------|-------|------|-------|

| Junction-to-ambient (@200 ft/min) | Four layer board (2s2p) | $R_{\theta JA}$ | 14    | °C/W | 1, 2  |

| Junction-to-board thermal         | _                       | $R_{\theta JB}$ | 10    | °C/W | 3     |

| Junction-to-case thermal          | _                       | $R_{\theta JC}$ | < 0.1 | °C/W | 4     |

#### **Notes**

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 and JESD51-6 with the board (JESD51-9) horizontal.

- 3. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 4. Thermal resistance between the active surface of the die and the case top surface determined by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature. Actual thermal resistance is less than 0.1 •C/W

Simulations with heat sinks were done with the package mounted on the 2s2p thermal test board. The thermal interface material was a typical thermal grease such as Dow Corning 340 or Wakefield 120 grease. For system thermal modeling, the chip's thermal model without a lid is shown in Figure 72 The substrate is modeled as a block 29 x 29 x 1.2 mm with an in-plane conductivity of 19.8 W/m•K and a through-plane conductivity of 1.13 W/m•K. The solder balls and air are modeled as a single block 29 x 29 x 0.5 mm with an in-plane conductivity of 0.034 W/m•K and a through plane conductivity of 12.1 W/m•K. The die is modeled as 9.6 x 9.57 mm with a thickness of 0.75 mm. The bump/underfill layer is modeled as a collapsed thermal resistance between the die and substrate assuming a conductivity of 7.5 W/m•K in the thickness dimension of 0.07 mm. The die is centered on the substrate. The thermal model uses approximate dimensions to reduce grid. Please refer to the case outline for actual dimensions.

## 2.24.2 Recommended Thermal Model

This table shows the chip's thermal model.

**Table 80. Thermal Model**

| Conductivity  | Value                          | Units                  |

|---------------|--------------------------------|------------------------|

|               | Die (9.6x9.6 × 0.85 m          | m)                     |

| Silicon       | Temperature dependent          | _                      |

| Bump/Underfil | l (9.6 x 9.6 × 0.07 mm) Collap | sed Thermal Resistance |

| Kz            | 7.5                            | W/m•K                  |

|               | Substrate (29 × 29 × 1.2       | mm)                    |

| Kx            | 19.8                           | W/m•K                  |

| Ку            | 19.8                           |                        |

| Kz            | 1.13                           |                        |

|               | Solder and Air (29 × 29 × 0    | ).5 mm)                |

| Kx            | 0.034                          | W/m•K                  |

| Ку            | 0.034                          |                        |

| Kz            | 12.1                           |                        |

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

#### **Hardware Design Considerations**

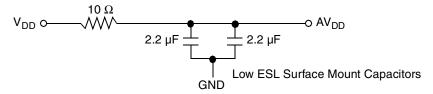

This figure shows the PLL power supply filter circuit.

Figure 75. Chip PLL Power Supply Filter Circuit

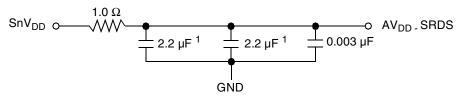

The AV<sub>DD</sub>\_SRDSn signals provides power for the analog portions of the SerDes PLL. To ensure stability of the internal clock, the power supplied to the PLL is filtered using a circuit similar to the one shown in following Figure 76. For maximum effectiveness, the filter circuit is placed as closely as possible to the AV<sub>DD</sub>\_SRDSn balls to ensure it filters out as much noise as possible. The ground connection should be near the AV<sub>DD</sub>\_SRDSn balls. The 0.003- $\mu$ F capacitor is closest to the balls, followed by the 1- $\mu$ F capacitor, and finally the 1 ohm resistor to the board supply plane. The capacitors are connected from AV<sub>DD</sub>\_SRDSn to the ground plane. Use ceramic chip capacitors with the highest possible self-resonant frequency. All traces should be kept short, wide and direct.

1. An 0805 sized capacitor is recommended for system initial bring-up

Figure 76. SerDes PLL Power Supply Filter Circuit

Note the following:

- AV<sub>DD</sub> should be a filtered version of SV<sub>DD</sub>.

- Signals on the SerDes interface are fed from the XV<sub>DD</sub> power plane.

# 3.3 Pin States in Deep Sleep State

In all low power mode by default, all input and output pads remain driven as per normal functional operation. The inputs remain enabled.

The exception is that in Deep Sleep mode, GCR[DEEPSLEEP\_Z] can be used to tristate a subset of output pads, and disable the receivers of input pads as defined in Table 1. See the MPC8536E PowerQUICC III Integrated Processor Reference Manual for details.

# 3.4 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, this chip can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the chip system, and the chip itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pin of the chip. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $OV_{DD}$ ,  $OV_{DD}$ , and  $OV_{DD$

MPC8535E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 5

117

Careful board layout with stubless connections to these pull-down resistors coupled with the large value of the pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

The platform PLL ratio and e500 PLL ratio configuration pins are not equipped with these default pull-up devices.

# 3.10 JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 78. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion will give unpredicatable results.

Boundary-scan testing is enabled through the JTAG interface signals. The  $\overline{TRST}$  signal is optional in the IEEE 1149.1 specification, but it is provided on all processors built on Power Architecture technology. The chip requires  $\overline{TRST}$  to be asserted during power-on reset flow to ensure that the JTAG boundary logic does not interfere with normal chip operation. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, generally systems assert  $\overline{TRST}$  during the power-on reset flow. Simply tying  $\overline{TRST}$  to  $\overline{HRESET}$  is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP), which implements the debug interface to the chip.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST in order to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 78 allows the COP port to independently assert  $\overline{\text{HRESET}}$  or  $\overline{\text{TRST}}$ , while ensuring that the target can drive  $\overline{\text{HRESET}}$  as well.

The COP interface has a standard header, shown in Figure 79, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; consequently, many different pin numbers have been observed from emulator vendors. Some are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom, while still others number the pins counter clockwise from pin 1 (as with an IC). Regardless of the numbering, the signal placement recommended in Figure 79 is common to all known emulators.

# 3.10.1 Termination of Unused Signals

If the JTAG interface and COP header will not be used, Freescale recommends the following connections:

- $\overline{TRST}$  should be tied to  $\overline{HRESET}$  through a 0 k $\Omega$  isolation resistor so that it is asserted when the system reset signal ( $\overline{HRESET}$ ) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 78. If this is not possible, the isolation resistor will allow future access to  $\overline{TRST}$  in case a JTAG interface may need to be wired onto the system in future debug situations.

- No pull-up/pull-down is required for TDI, TMS, or TDO.

### How to Reach Us:

**Home Page:**

www.freescale.com

Web Support:

http://www.freescale.com/support

**USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or +303-675-2140 Fax: +303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, and PowerQUICC are trademarks of Freescale Semiconductor, Inc. Reg., U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2011 Freescale Semiconductor, Inc.

Document Number: MPC8535EEC

Rev. 5 09/2011