#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

-XF

| Product Status                  | Obsolete                                                     |

|---------------------------------|--------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                               |

| Speed                           | 600MHz                                                       |

| Co-Processors/DSP               | Security; SEC                                                |

| RAM Controllers                 | DDR2, DDR3                                                   |

| Graphics Acceleration           | No                                                           |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | 10/100/1000Mbps (2)                                          |

| SATA                            | SATA 3Gbps (1)                                               |

| USB                             | USB 2.0 (2)                                                  |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                             |

| Operating Temperature           | -40°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography                                                 |

| Package / Case                  | 783-BBGA, FCBGA                                              |

| Supplier Device Package         | 783-FCPBGA (29x29)                                           |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8535ecvtakga |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Pin Assignments and Reset States**

|    | A             | В                | С                | D                | E                | F                | G                | Н                 | J                | К                | L                      | М                   | N                 | Ρ             | _/_ |

|----|---------------|------------------|------------------|------------------|------------------|------------------|------------------|-------------------|------------------|------------------|------------------------|---------------------|-------------------|---------------|-----|

| 1  |               | GV <sub>DD</sub> | MDQS<br>[5]      | MDQ<br>[32]      | MDQ<br>[46]      | MDQ<br>[47]      | MDQ<br>[34]      | GND               | MDQ<br>[56]      | MDQ<br>[57]      | GND                    | GV <sub>DD</sub>    | MDQS<br>[7]       | MDQ<br>[58]   | N   |

| 2  | MDQ<br>[44]   | MDQ<br>[40]      | MDM<br>[5]       | MDQS<br>[5]      | GV <sub>DD</sub> | MDQ<br>[42]      | MDQ<br>[43]      | MDQ<br>[35]       | MDQ<br>[60]      | MDQ<br>[61]      | MDM<br>[7]             | MDQS<br>[7]         | GND               | MDM<br>[62]   |     |

| 3  | GND           | MDQ<br>[45]      | MDQ<br>[41]      | MCS<br>[0]       | GND              | MDQ<br>[33]      | GV <sub>DD</sub> | MDQ<br>[38]       | MDQ<br>[52]      | GV <sub>DD</sub> | MDM<br>[6]             | MDQS<br>[6]         | MDQ<br>[50]       | MDQ<br>[51]   |     |

| 4  | MBA<br>[0]    | MWE              | MCS<br>[2]       | GV <sub>DD</sub> | MDQ<br>[36]      | GND              | MDM<br>[4]       | GND               | MDQ<br>[39]      | MDQ<br>[53]      | MDQ<br>[49]            | MDQS<br>[6]         | MDQ<br>[54]       | MDQ<br>[55]   |     |

| 5  | MA<br>[10]    | MBA<br>[1]       | MRAS             | GND              | MODT<br>[0]      | GV <sub>DD</sub> | MDQ<br>[37]      | GV <sub>DD</sub>  | MDQS<br>[4]      | MDQS<br>[4]      | MDQ<br>[48]            | GND                 | GV <sub>DD</sub>  | GND           |     |

| 6  | MAPAR_<br>OUT | NC               | GND              | GV <sub>DD</sub> | MODT<br>[2]      | MODT<br>[3]      | MCS<br>[3]       | MCS<br>[1]        | МСК<br>[2]       | MCK<br>[2]       | SD2_<br>IMP_CAL<br>_TX | SD2_<br>REF_<br>CLK | S2GND             | SD2_RX<br>[0] |     |

| 7  | GND           | MA<br>[0]        | GV <sub>DD</sub> | NC               | MCAS             | MA<br>[13]       | GV <sub>DD</sub> | MODT<br>[1]       | NC               | GND              | SD2_<br>PLL_<br>TPD    | SD2_<br>REF_<br>CLK | S2V <sub>DD</sub> | SD2_RX<br>[0] |     |

| 8  | МСК<br>[3]    | MCK<br>[3]       | MA<br>[2]        | GND              | GV <sub>DD</sub> | GND              | MA<br>[1]        | MCK<br>[5]        | MCK<br>[5]       | GND              | Rsvd                   | S2GND               | SD2_RX<br>[1]     | S2GND         |     |

| 9  | МСК<br>[0]    | MCK<br>[0]       | GV <sub>DD</sub> | MA<br>[4]        | MA<br>[8]        | MA<br>[7]        | GV <sub>DD</sub> | MCKE<br>[3]       | NC               | NC               | Rsvd                   | S2V <sub>DD</sub>   | SD2_RX<br>[1]     | S2GND         |     |

| 10 | MA<br>[3]     | GND              | MA<br>[5]        | NC               | MA<br>[14]       | MA<br>[15]       | MCKE<br>[2]      | МСКЕ<br>[0]       | GV <sub>DD</sub> | MCKE<br>[1]      | NC                     | X2GND               | NC                | NC            |     |

| 11 | MA<br>[6]     | GV <sub>DD</sub> | MECC<br>[3]      | MA<br>[12]       | GV <sub>DD</sub> | MECC<br>[2]      | GV <sub>DD</sub> | <u>МСК</u><br>[1] | МСК<br>[1]       | GND              | x2V <sub>DD</sub>      | SD2_TX<br>[1]       | X2GND             | SD2_TX<br>[0] |     |

| 12 | MA<br>[11]    | MA<br>[9]        | GND              | MECC<br>[7]      | GND              | NC               | MECC<br>[0]      | GV <sub>DD</sub>  | GND              | GV <sub>DD</sub> | X2GND                  | SD2_TX<br>[1]       | x2V <sub>DD</sub> | SD2_TX<br>[0] |     |

| 13 | MAPAR_<br>ERR | MBA<br>[2]       | MECC<br>[6]      | MDQS<br>[8]      | MDQS<br>[8]      | MDM<br>[8]       | GND              | MCK<br>[4]        | МСК<br>[4]       | VDD_<br>CORE     | GND                    | VDD_<br>CORE        | GND               | VDD_<br>CORE  |     |

| 14 | GND           | MDQ<br>[27]      | GV <sub>DD</sub> | MECC<br>[1]      | GV <sub>DD</sub> | MECC<br>[5]      | MECC<br>[4]      | GV <sub>DD</sub>  | GND              | GV <sub>DD</sub> | VDD_<br>CORE           | GND                 | VDD_<br>CORE      | GND           |     |

| <  | 2             |                  |                  |                  |                  |                  | DET              |                   |                  |                  |                        |                     |                   |               |     |

Figure 3. Chip Pin Map Detail A

## **Pin Assignments and Reset States**

| Signal    | Signal Name                          | Package Pin Number                                                                                                                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes |

|-----------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

|           | DDR SDRAM                            | Memory Interface                                                                                                                                                                                                                                                        |          |                  |       |

| MDQ[0:63] | Data                                 | A26,B26,C22,D21,D25,<br>B25,D22,E21,A24,A23,<br>B20,A20,A25,B24,B21,<br>A21,E19,D19,E16,C16,<br>F19,F18,F17,D16,B18,<br>A18,A15,B14,B19,A19,<br>A16,B15,D1,F3,G1,H2,<br>E4,G5,H3,J4,B2,C3,F2,<br>G2,A2,B3,E1,F1,L5,L4,<br>N3,P3,J3,K4,N4,P4,J1,<br>K1,P1,R1,J2,K2,P2,R2 | I/O      | GV <sub>DD</sub> | _     |

| MECC[0:7] | Error Correcting Code                | G12,D14,F11,C11,<br>G14,F14,C13,D12                                                                                                                                                                                                                                     | I/O      | GV <sub>DD</sub> | _     |

| MAPAR_ERR | Address Parity Error                 | A13                                                                                                                                                                                                                                                                     | I        | GV <sub>DD</sub> | _     |

| MAPAR_OUT | Address Parity Out                   | A6                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

| MDM[0:8]  | Data Mask                            | C25,B23,D18,B17,G4,<br>C2,L3,L2,F13                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _     |

| MDQS[0:8] | Data Strobe                          | D24,B22,C18,A17,J5,<br>C1,M4,M2,E13                                                                                                                                                                                                                                     | I/O      | GV <sub>DD</sub> | —     |

| MDQS[0:8] | Data Strobe                          | C23,A22,E17,B16,K5,<br>D2,M3,N1,D13                                                                                                                                                                                                                                     | I/O      | GV <sub>DD</sub> | —     |

| MA[0:15]  | Address                              | B7,G8,C8,A10,D9,C10,<br>A11,F9,E9,B12,A5,<br>A12,D11,F7,E10,F10                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | _     |

| MBA[0:2]  | Bank Select                          | A4,B5,B13                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | —     |

| MWE       | Write Enable                         | B4                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

| MRAS      | Row Address Strobe                   | C5                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

| MCAS      | Column Address Strobe                | E7                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

| MCS[0:3]  | Chip Select                          | D3,H6,C4,G6                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | —     |

| MCKE[0:3] | Clock Enable                         | H10,K10,G10,H9                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | 11    |

| MCK[0:5]  | Differential Clock 3 Pairs /<br>DIMM | A9,J11,J6,A8,J13,H8                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | —     |

| MCK[0:5]  | Differential Clock 3 Pairs /<br>DIMM | B9,H11,K6,B8,H13,J8                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _     |

| MODT[0:3] | On Die Termination                   | E5,H7,E6,F6                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | -     |

| MDIC[0:1] | Calibration                          | H15,K15                                                                                                                                                                                                                                                                 | I/O      | GV <sub>DD</sub> | 26    |

|           | Local Bus C                          | ontroller Interface                                                                                                                                                                                                                                                     |          |                  |       |

## Table 1. Pinout Listing (continued)

## **Pin Assignments and Reset States**

| Table 1. Pinout Li | sting (continued) |

|--------------------|-------------------|

|--------------------|-------------------|

| Signal                                           | Signal Name                                                                                     | Package Pin Number                                                                                                                                      | Pin Type | Power<br>Supply  | Notes    |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| LAD[0:31]                                        | Muxed data / address                                                                            | K22,L21,L22,K23,K24,<br>L24,L25,K25,L28,L27,<br>K28,K27,J28,H28,H27,<br>G27,G26,F28,F26,F25,<br>E28,E27,E26,F24,E24,<br>C26,G24,E23,G23,F22,<br>G22,G21 | I/O      | BV <sub>DD</sub> | 5,9,29   |

| LDP[0:3]                                         | Data parity                                                                                     | K26,G28,B27,E25                                                                                                                                         | I/O      | BV <sub>DD</sub> | 29       |

| LA[27]                                           | Burst address                                                                                   | L19                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5,9,29   |

| LA[28:31]                                        | Port address                                                                                    | K16,K17,H17,G17                                                                                                                                         | 0        | BV <sub>DD</sub> | 5,7,9,29 |

| LCS[0:4]                                         | Chip selects                                                                                    | K18,G19,H19,H20,G16                                                                                                                                     | 0        | BV <sub>DD</sub> | 29       |

| LCS5/DMA_DREQ2                                   | Chips selects / DMA Request                                                                     | H16                                                                                                                                                     | I/O      | BV <sub>DD</sub> | 1,29     |

| LCS6/DMA_DACK2                                   | Chips selects / DMA Ack                                                                         | J16                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1,29     |

| LCS7/DMA_DDONE2                                  | Chips selects / DMA Done                                                                        | L18                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1,29     |

| LWE0/LBS0/LFWE                                   | Write enable / Byte select                                                                      | J22                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5,9,29   |

| LWE[1:3]/LBS[1:3]                                | Write enable / Byte select                                                                      | H22,H23,H21                                                                                                                                             | 0        | BV <sub>DD</sub> | 5,9,29   |

| LBCTL                                            | Buffer control                                                                                  | J25                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5,8,9,29 |

| LALE                                             | Address latch enable                                                                            | J26                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5,8,9,29 |

| LGPL0/LFCLE                                      | UPM general purpose line 0 /<br>FLash command latch enable                                      |                                                                                                                                                         | 0        | BV <sub>DD</sub> | 5,9,29   |

| LGPL1/LFALE                                      | UPM general purpose line 1 /<br>Flash address latch enable                                      | K20                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5,9,29   |

| LGPL2/LOE/LFRE                                   | UPM general purpose line 2 /<br>Output enable/Flash read<br>enable                              | G20                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5,8,9,29 |

| LGPL3/LFWP                                       | UPM general purpose line 3 /<br>Flash write protect                                             | H18                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5,9,29   |

| LGPL4/ <mark>LGTA</mark> /LUPWAIT<br>/LPBSE/LFRB | UPM general purpose line 4 /<br>Target Ack/Wait/SDRAM<br>parity byte select/Flash<br>Ready-busy | L20                                                                                                                                                     | I/O      | BV <sub>DD</sub> | 29, 35   |

| LGPL5                                            | UPM general purpose line 5 /<br>Amux                                                            | К19                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5,9,29   |

| LCLK[0:2]                                        | Local bus clock                                                                                 | H24,J24,H25                                                                                                                                             | 0        | BV <sub>DD</sub> | 29       |

| LSYNC_IN                                         | Synchronization                                                                                 | D27                                                                                                                                                     | I        | BV <sub>DD</sub> | 29       |

| LSYNC_OUT                                        | Local bus DLL                                                                                   | D28                                                                                                                                                     | 0        | BV <sub>DD</sub> | 29       |

|                                                  | D                                                                                               | MA                                                                                                                                                      | 1        |                  | 1        |

| DMA_DACK[0:1]<br>/GPIO[10:11]                    | DMA Acknowledge                                                                                 | AD6,AE10                                                                                                                                                | 0        | OV <sub>DD</sub> | -        |

| Table | 1.  | Pinout | Listina | (continued) |

|-------|-----|--------|---------|-------------|

| labio | ••• | . moat | Lioung  | (oonaba)    |

| Signal               | Signal Name                    | Package Pin Number                                  | Pin Type | Power<br>Supply  | Notes  |

|----------------------|--------------------------------|-----------------------------------------------------|----------|------------------|--------|

|                      | Programmable I                 | nterrupt Controller                                 |          |                  |        |

| MCP                  | Machine check processor        | Y14                                                 | I        | OV <sub>DD</sub> |        |

| UDE                  | Unconditional debug event      | AB14                                                | I        | OV <sub>DD</sub> | —      |

| IRQ[0:8]             | External interrupts            | AG22,AF17,AB23,<br>AF19,AG17,AF16,<br>AA22,Y19,AB22 | I        | OV <sub>DD</sub> | _      |

| IRQ[9]/DMA_DREQ[3]   | External interrupt/DMA request | AE13                                                | I        | $OV_{DD}$        | 1      |

| IRQ[10]/DMA_DACK[3]  | External interrupt/DMA Ack     | AD13                                                | I/O      | $OV_{DD}$        | 1      |

| IRQ[11]/DMA_DDONE[3] | External interrupt/DMA done    | AD14                                                | I/O      | OV <sub>DD</sub> | 1      |

| IRQ_OUT              | Interrupt output               | AC17                                                | 0        | OV <sub>DD</sub> | 2,4    |

|                      | Ethernet Mana                  | gement Interface                                    |          |                  |        |

| EC_MDC               | Management data clock          | Y10                                                 | 0        | OV <sub>DD</sub> | 5,9,22 |

| EC_MDIO              | Management data In/Out         | Y11                                                 | I/O      | OV <sub>DD</sub> |        |

|                      | Gigabit Re                     | ference Clock                                       | ••       |                  | •      |

| EC_GTX_CLK125        | Reference clock                | AA6                                                 | I        | LV <sub>DD</sub> | 31     |

|                      | Three-Speed Ethernet Co        | ntroller (Gigabit Etherne                           | et 1)    |                  |        |

| TSEC1_TXD[7:0]       | Transmit data                  | AA8,AA5,Y8,Y5,W3,<br>W5,W4,W6                       | 0        | LV <sub>DD</sub> | 5,9,22 |

| TSEC1_TX_EN          | Transmit Enable                | W1                                                  | 0        | LV <sub>DD</sub> | 23     |

| TSEC1_TX_ER          | Transmit Error                 | AB5                                                 | 0        | LV <sub>DD</sub> | 5,9    |

| TSEC1_TX_CLK         | Transmit clock In              | AB4                                                 | I        | LV <sub>DD</sub> |        |

| TSEC1_GTX_CLK        | Transmit clock Out             | W2                                                  | 0        | LV <sub>DD</sub> | —      |

| TSEC1_CRS            | Carrier sense                  | AA9                                                 | I/O      | LV <sub>DD</sub> | 17     |

| TSEC1_COL            | Collision detect               | AB6                                                 | I        | LV <sub>DD</sub> | —      |

| TSEC1_RXD[7:0]       | Receive data                   | AB3,AB7,AB8,Y6,AA2,<br>Y3,Y1,Y2                     | I        | LV <sub>DD</sub> | _      |

| TSEC1_RX_DV          | Receive data valid             | AA1                                                 | I        | LV <sub>DD</sub> |        |

| TSEC1_RX_ER          | Receive data error             | Y9                                                  | I        | LV <sub>DD</sub> | —      |

| TSEC1_RX_CLK         | Receive clock                  | AA3                                                 | I        | LV <sub>DD</sub> | —      |

|                      | Three-Speed Ethernet Co        | ntroller (Gigabit Etherne                           | et 3)    |                  |        |

| TSEC3_TXD[7:0]       | Transmit data                  | T12,V8,U8,V9,T8,T7,<br>T5,T6                        | 0        | TV <sub>DD</sub> | 5,9,22 |

| TSEC3_TX_EN          | Transmit Enable                | V5                                                  | 0        | TV <sub>DD</sub> | 23     |

| TSEC3_TX_ER          | Transmit Error                 | U9                                                  | 0        | TV <sub>DD</sub> | 5,9    |

## **Pin Assignments and Reset States**

| Table 1. Pinout | Listing | (continued) |

|-----------------|---------|-------------|

|-----------------|---------|-------------|

| Signal         | Signal Name                    | Package Pin Number                  | Pin Type | Power<br>Supply   | Notes            |

|----------------|--------------------------------|-------------------------------------|----------|-------------------|------------------|

| UART_SOUT[0:1] | Transmit data                  | AF10,AA12                           | 0        | $OV_{DD}$         | 5,9,22,<br>10,29 |

|                | l <sup>2</sup>                 | C interface                         |          |                   |                  |

| IIC1_SCL       | Serial clock                   | AG21                                | I/O      | OV <sub>DD</sub>  | 4,21,29          |

| IIC1_SDA       | Serial data                    | AH22                                | I/O      | OV <sub>DD</sub>  | 4,21,29          |

| IIC2_SCL       | Serial clock                   | AH15                                | I/O      | OV <sub>DD</sub>  | 4,21,29          |

| IIC2_SDA       | Serial data                    | AG14                                | I/O      | $OV_{DD}$         | 4,21,29          |

|                | S                              | erDes1(x4)                          |          |                   | •                |

| SD1_TX[7:4]    | Transmit Data (+)              | Y23,W21,V23,U21                     | 0        | XV <sub>DD</sub>  | _                |

| SD1_TX[7:4]    | Transmit Data(-)               | Y22,W20,V22,U20                     | 0        | XV <sub>DD</sub>  |                  |

| SD1_RX[7:4]    | Receive Data(+)                | AC28,AB26,AA28,Y26                  | I        | XV <sub>DD</sub>  |                  |

| SD1_RX[7:4]    | Receive Data(-)                | AC27,AB25,AA27,Y25                  | I        | XV <sub>DD</sub>  | _                |

| Reserved       | -                              | R21,P23,N21,M23,<br>R20,P22,N20,M22 | -        | _                 | 18               |

| Reserved       | -                              | T26,R28,P26,N28,<br>T25,R27,P25,N27 | —        | _                 | 33               |

| SD1_PLL_TPD    | PLL test point Digital         | V28                                 | 0        | XV <sub>DD</sub>  | 18               |

| SD1_REF_CLK    | PLL Reference clock            | U28                                 | I        | XV <sub>DD</sub>  | —                |

| SD1_REF_CLK    | PLL Reference clock complement | U27                                 | I        | $XV_{DD}$         | —                |

| Reserved       | _                              | T22                                 | —        | _                 | 18               |

| Reserved       | —                              | T23                                 | —        | _                 | 18               |

|                | S                              | erDes2(x1)                          |          |                   |                  |

| SD2_TX[0]      | Transmit data(+)               | P11                                 | 0        | X2V <sub>DD</sub> | _                |

| SD2_TX[0]      | Transmit data(-)               | P12                                 | 0        | X2V <sub>DD</sub> | _                |

| SD2_RX[0]      | Receive data(+)                | P6                                  | I        | X2V <sub>DD</sub> |                  |

| SD2_RX[0]      | Receive data(-)                | P7                                  | I        | X2V <sub>DD</sub> |                  |

| Reserved       | _                              | M11,M12                             |          | _                 | 18               |

| Reserved       | _                              | N8, N9                              | _        | _                 | 34               |

| SD2_PLL_TPD    | PLL test point Digital         | L7                                  | 0        | X2V <sub>DD</sub> | 18               |

| SD2_REF_CLK    | PLL Reference clock            | M6                                  | I        | X2V <sub>DD</sub> |                  |

| SD2_REF_CLK    | PLL Reference clock complement | M7                                  | I        | X2V <sub>DD</sub> | -                |

| Reserved       | —                              | L8                                  | —        | X2V <sub>DD</sub> | 18               |

| Reserved       | _                              | L9                                  | _        | X2V <sub>DD</sub> | 18               |

## **Pin Assignments and Reset States**

| Signal                         | Signal Name                 | Package Pin Number | Pin Type | Power<br>Supply  | Notes  |

|--------------------------------|-----------------------------|--------------------|----------|------------------|--------|

|                                | General-Purpo               | ose Input/Output   | <u> </u> |                  |        |

| GPIO[0:1]/PCI1_REQ[3:4]        | GPIO/PCI request            | Y15,AE15           | I/O      | OV <sub>DD</sub> | _      |

| GPIO[2:3]/PCI1_GNT[3:4]        | GPIO/PCI grant              | AA15,AC14          | I/O      | OV <sub>DD</sub> | —      |

| GPIO[4]/SDHC_CD                | GPIO/SDHC card detection    | AH11               | I/O      | OV <sub>DD</sub> | —      |

| GPIO[5]/SDHC_WP                | GPIO/SDHC write protection  | AG10               | I/O      | OV <sub>DD</sub> | 32     |

| GPIO[6]/USB1_PCTL0             | GPIO/USB1 PCTL0             | AC3                | I/O      | OV <sub>DD</sub> | —      |

| GPIO[7]/USB1_PCTL1             | GPIO/USB1 PCTL1             | AC4                | I/O      | $OV_{DD}$        | —      |

| GPIO[8]/USB2_PCTL0             | GPIO/USB2 PCTL0             | AG9                | I/O      | OV <sub>DD</sub> | —      |

| GPIO[9]/USB2_PCTL1             | GPIO/USB2 PCTL1             | AC9                | I/O      | OV <sub>DD</sub> | —      |

| GPIO[10:11]<br>/DMA_DACK[0:1]  | GPIO/DMA Ack                | AD6,AE10           | I/O      | $OV_{DD}$        | —      |

| GPIO[12:13]<br>/DMA_DDONE[0:1] | GPIO/DMA done               | AA11,AB11          | I/O      | OV <sub>DD</sub> |        |

| GPIO[14:15]<br>/DMA_DREQ[0:1]  | GPIO/DMA request            | AB10,AD11          | I/O      | $OV_{DD}$        | —      |

|                                | Systen                      | n Control          | 1        |                  |        |

| HRESET                         | Hard reset                  | AG16               | I        | OV <sub>DD</sub> | _      |

| HRESET_REQ                     | Hard reset - request        | AG15               | 0        | OV <sub>DD</sub> | 22     |

| SRESET                         | Soft reset                  | AG19               | I        | OV <sub>DD</sub> | —      |

| CKSTP_IN                       | CheckStop in                | AG18               | I        | OV <sub>DD</sub> | —      |

| CKSTP_OUT                      | CheckStop Output            | AH17               | 0        | $OV_{DD}$        | 2,4    |

|                                | De                          | ebug               |          |                  |        |

| TRIG_IN                        | Trigger in                  | W19                | I        | OV <sub>DD</sub> | _      |

| TRIG_OUT/READY<br>/QUIESCE     | Trigger out/Ready/Quiesce   | V19                | 0        | $OV_{DD}$        | 22     |

| MSRCID[0:1]                    | Memory debug source port ID | W12,W13            | 0        | OV <sub>DD</sub> | 6,9    |

| MSRCID[2:4]                    | Memory debug source port ID | V12, W14,W11       | 0        | OV <sub>DD</sub> | 6,9,22 |

| MDVAL                          | Memory debug data valid     | V13                | 0        | OV <sub>DD</sub> | 6,22   |

| CLK_OUT                        | Clock Out                   | W15                | 0        | OV <sub>DD</sub> | 11     |

|                                | C                           | lock               | · ·      |                  |        |

| RTC                            | Real time clock             | AF15               | Ι        | OV <sub>DD</sub> |        |

| SYSCLK                         | System clock / PCI clock    | AH14               | I        | OV <sub>DD</sub> | —      |

| DDRCLK                         | DDR clock                   | AC13               | I        | OV <sub>DD</sub> | 30     |

|                                | J.                          | TAG                | ·        |                  | •      |

|                                  | Characteristic                                                                                         | Symbol                               | Recommended Value                                           | Unit | Notes |

|----------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------|------|-------|

| Core supply voltage              |                                                                                                        | V <sub>DD_CORE</sub>                 | 1.0 ± 50 mV                                                 | V    | —     |

| Platform supply voltag           | ge                                                                                                     | V <sub>DD_PLAT</sub>                 | 1.0 ± 50 mV                                                 | V    | —     |

| PLL core supply volta            | ge                                                                                                     | AV <sub>DD_CORE</sub>                | 1.0 ± 50 mV                                                 | V    | 2     |

| PLL other supply volta           | age                                                                                                    | AV <sub>DD</sub>                     | 1.0 ± 50 mV                                                 | V    | 2     |

| Core power supply for            | or SerDes transceivers $SV_{DD}$ $1.0 \pm 50 \text{ mV}$ V -                                           |                                      |                                                             |      | —     |

| Pad power supply for             | SerDes transceivers and PCI Express                                                                    | XV <sub>DD</sub>                     | 1.0 ± 50 mV                                                 | V    | —     |

| DDR SDRAM                        | DDR2 SDRAM Interface                                                                                   | GV <sub>DD</sub>                     | 1.8 V ± 90 mV                                               | nV V |       |

| Controller I/O supply voltage    | DDR3 SDRAM Interface                                                                                   |                                      | 1.5 V ± 75 mV                                               |      |       |

| Three-speed Ethernet I/O voltage |                                                                                                        | LV <sub>DD</sub><br>(eTSEC1)         | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                            | V    | 5     |

|                                  |                                                                                                        | TV <sub>DD</sub><br>(eTSEC3)         | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                            |      |       |

|                                  | control and power management, I <sup>2</sup> C, USB, eSDHC, oltage, MII management voltage             | OV <sub>DD</sub>                     | 3.3 V ± 165 mV                                              | V    | 4     |

| Local bus I/O voltage            | al bus I/O voltage                                                                                     |                                      | 3.3 V ± 165 mV<br>2.5 V ± 125 mV<br>1.8 V ± 90 mV           | V    | —     |

| Input voltage                    | DDR2 and DDR3 SDRAM Interface signals                                                                  | MV <sub>IN</sub>                     | GND to GV <sub>DD</sub>                                     | V    | 3     |

|                                  | DDR2 and DDR3 SDRAM Interface reference                                                                | MV <sub>REF</sub>                    | GV <sub>DD</sub> /2 ± 1%                                    | V    | —     |

|                                  | Three-speed Ethernet signals                                                                           | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub>          | V    | 5     |

|                                  | Local bus signals BV <sub>IN</sub> GND to                                                              |                                      | GND to BV <sub>DD</sub>                                     | V    | —     |

|                                  | PCI, Local bus, DUART, SYSCLK, system control and power management, I <sup>2</sup> C, and JTAG signals | OV <sub>IN</sub>                     | GND to OV <sub>DD</sub>                                     | V    | 4     |

| Operating<br>Temperature range   | Commercial                                                                                             |                                      | T <sub>A</sub> = 0 (min) to<br>T <sub>J</sub> = 90(max)     |      |       |

|                                  | Industrial standard temperature range                                                                  | 5                                    | $T_A = 0$ (min) to<br>$T_J = 105$ (max)                     | °C   | 6     |

|                                  | Extended temperature range                                                                             |                                      | T <sub>A</sub> = -40 (min) to<br>T <sub>J</sub> = 105 (max) |      |       |

## **Table 3. Recommended Operating Conditions**

## Notes:

- 2. This voltage is the input to the filter discussed in Section 3.2.1, "PLL Power Supply Filtering," and not necessarily the voltage at the AVDD pin, which may be reduced from VDD by the filter.

- 3. Caution: MVIN must not exceed GVDD by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. Caution: OVIN must not exceed OVDD by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 5. Caution: L/TVIN must not exceed L/TVDD by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 6. Minimum temperature is specified with T<sub>A</sub>; maximum temperature is specified with T<sub>J</sub>.

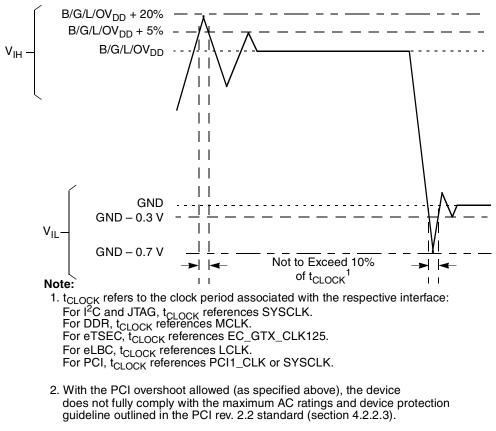

This figure shows the undershoot and overshoot voltages at the interfaces of the chip.

### Figure 7. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>/LV<sub>DD</sub>

The core voltage must always be provided at nominal 1.0 V. (See Table 3 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 3. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR2 and DDR3 SDRAM interface uses differential receivers referenced by the externally supplied MVREF*n* signal (nominally set to GVDD/2) as is appropriate for the SSTL\_1.8 electrical signaling standard for DDR2 or 1.5-V electrical signaling for DDR3. The DDR DQS receivers cannot be operated in single-ended fashion. The complement signal must be properly driven and cannot be grounded.

| Power Mode        | Core<br>Frequen<br>cy | CCB<br>Frequen<br>cy | DDR<br>Frequen<br>cy | V <sub>DD</sub><br>Platfor<br>m | V <sub>DD</sub><br>Core | Junction<br>Tempera<br>ture | Core Power        |         | Platform          | ı Power <sup>9</sup> | Notes   |

|-------------------|-----------------------|----------------------|----------------------|---------------------------------|-------------------------|-----------------------------|-------------------|---------|-------------------|----------------------|---------|

|                   | (MHz)                 | (MHz)                | (MHz)                | (V)                             | (V)                     | (°C)                        | mean <sup>7</sup> | Мах     | mean <sup>7</sup> | Max                  |         |

| Maximum (A)       |                       |                      |                      |                                 |                         | 105                         |                   | 5.3/4.4 | _                 | 5.0/4.0              | 1, 3, 8 |

| Thermal (W)       | 1250                  | 500                  | 500                  | 1.0                             | 1.0                     | / 90                        |                   | 4.4/3.6 | _                 | 5.0/4.0              | 1, 4, 8 |

| Typical (W)       |                       |                      |                      |                                 |                         | 65                          | 2.2               |         | 1.7               |                      | 1       |

| Doze (W)          |                       |                      |                      |                                 |                         |                             | 1.6               | 2.4     | 1.5               | 2.1                  | 1       |

| Nap (W)           |                       |                      |                      |                                 |                         |                             | 0.8               | 1.6     | 1.5               | 2.1                  | 1       |

| Sleep (W)         |                       |                      |                      |                                 |                         |                             | 0.8               | 1.6     | 1.1               | 1.7                  | 1       |

| Deep Sleep<br>(W) |                       |                      |                      |                                 |                         | 35                          | 0                 | 0       | 0.6               | 1.2                  | 1, 6    |

### Table 5. Power Dissipation (continued)<sup>5</sup>

#### Notes:

1. These values specify the power consumption at nominal voltage and apply to all valid processor bus frequencies and configurations. The values do not include power dissipation for I/O supplies.

- Typical power is an average value measured at the nominal recommended core voltage (V<sub>DD</sub>) and 65°C junction temperature (see Table 3) while running the Dhrystone benchmark.

- 3. Maximum power is the maximum power measured with the worst process and recommended core and platform voltage (V<sub>DD</sub>) at maximum operating junction temperature (see Table 3) while running a smoke test which includes an entirely L1-cache-resident, contrived sequence of instructions which keep the execution unit maximally busy.

- 4. Thermal power is the maximum power measured with worst case process and recommended core and platform voltage (V<sub>DD</sub>) at maximum operating junction temperature (see Table 3) while running the Dhrystone benchmark.

- 6. Maximum power is the maximum number measured with USB1, eTSEC1, and DDR blocks enabled. The Mean power is the mean power measured with only external interrupts enabled and DDR in self refresh.

- 7. Mean power is provided for information purposes only and is the mean power consumed by a statistically significant range of devices.

- 8. Maximum operating junction temperature (see Table 3) for Commercial Tier is 90 <sup>0</sup>C, for Industrial Tier is 105 <sup>0</sup>C.

- 9. Platform power is the power supplied to all the  $V_{DD}\ _{PLAT}$  pins.

See Section 2.23.6.1, "SYSCLK to Platform Frequency Options," for the full range of CCB frequencies that the chip supports.

| Characteristic                          | Symbol <sup>2</sup>  | Min | Max | Unit | Note |

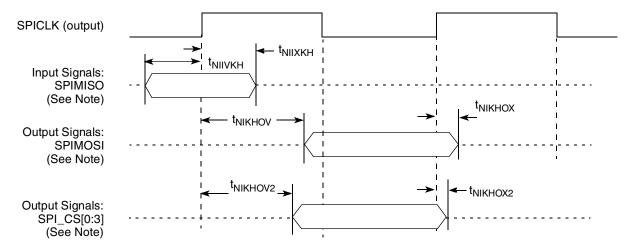

|-----------------------------------------|----------------------|-----|-----|------|------|

| SPI_CS outputs—Master data delay        | t <sub>NIKHOV2</sub> | _   | 6.0 | ns   | _    |

| SPI inputs—Master data input setup time | t <sub>NIIVKH</sub>  | 5   |     | ns   |      |

| SPI inputs—Master data input hold time  | t <sub>NIIXKH</sub>  | 0   | _   | ns   | _    |

Table 21. SPI AC Timing Specifications<sup>1</sup> (continued)

Notes:

1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).

3. SPCOM[RxDelay] is set to 0.

4. SPCOM[RxDelay] is set to 1.

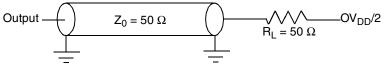

This figure provides the AC test load for the SPI.

This figure represents the AC timing from Table 21. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Note: The clock edge is selectable on SPI.

Figure 13. SPI AC Timing in Master mode (Internal Clock) Diagram

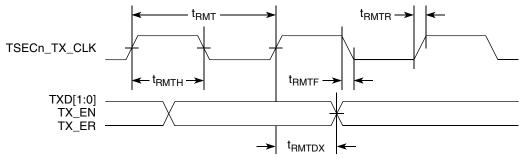

## Table 36. RMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup> | Min | Тур | Мах  | Unit |

|-------------------------------------------------|---------------------|-----|-----|------|------|

| Rise time TSECn_TX_CLK (20%–80%)                | t <sub>RMTR</sub>   | 1.0 | —   | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%-20%)                | t <sub>RMTF</sub>   | 1.0 | —   | 2.0  | ns   |

| TSECn_TX_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>  | 2.0 | —   | 10.0 | ns   |

#### Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

This figure shows the RMII transmit AC timing diagram.

Figure 26. RMII Transmit AC Timing Diagram

#### 2.9.2.7.2 RMII Receive AC Timing Specifications

### Table 37. RMII Receive AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition              | Symbol <sup>1</sup> | Min  | Тур  | Мах  | Unit |

|----------------------------------|---------------------|------|------|------|------|

| TSECn_RX_CLK clock period        | t <sub>RMR</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_RX_CLK duty cycle          | t <sub>RMRH</sub>   | 35   | 50   | 65   | %    |

| TSECn_RX_CLK peak-to-peak jitter | t <sub>RMRJ</sub>   |      |      | 250  | ps   |

| Rise time TSECn_RX_CLK (20%–80%) | t <sub>RMRR</sub>   | 1.0  | _    | 2.0  | ns   |

The IEEE 1588 AC timing specifications are in the following table.

## Table 43. eTSEC IEEE 1588 AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                | Symbol                                                | Min                         | Тур | Мах                    | Unit | Note |

|------------------------------------|-------------------------------------------------------|-----------------------------|-----|------------------------|------|------|

| TSEC_1588_CLK clock period         | t <sub>T1588CLK</sub>                                 | 3.8                         | _   | T <sub>TX_CLK</sub> *7 | ns   | 1    |

| TSEC_1588_CLK duty cycle           | t <sub>T1588</sub> CLKH<br>/t <sub>T1588</sub> CLK    | 40                          | 50  | 60                     | %    | —    |

| TSEC_1588_CLK peak-to-peak jitter  | t <sub>T1588CLKINJ</sub>                              | —                           | -   | 250                    | ps   | —    |

| Rise time eTSEC_1588_CLK (20%-80%) | t <sub>T1588CLKINR</sub>                              | 1.0                         | _   | 2.0                    | ns   | —    |

| Fall time eTSEC_1588_CLK (80%–20%) | t <sub>T1588CLKINF</sub>                              | 1.0                         | _   | 2.0                    | ns   | —    |

| TSEC_1588_CLK_OUT clock period     | t <sub>T1588</sub> CLKOUT                             | 2*t <sub>T1588CLK</sub>     | _   | —                      | ns   | —    |

| TSEC_1588_CLK_OUT duty cycle       | t <sub>T1588CLKOTH</sub><br>/t <sub>T1588CLKOUT</sub> | 30                          | 50  | 70                     | %    | —    |

| TSEC_1588_PULSE_OUT                | t <sub>T1588OV</sub>                                  | 0.5                         | _   | 3.0                    | ns   | —    |

| TSEC_1588_TRIG_IN pulse width      | t <sub>T1588</sub> TRIGH                              | 2*t <sub>T1588CLK_MAX</sub> | _   | —                      | ns   | 2    |

Note:

1. When TMR\_CTRL[CKSEL]=00, the external TSEC\_1588\_CLK input is selected as the 1588 timer reference clock source, with the timing defined in the Table above. The maximum value of t<sub>T1588CLK</sub> is defined in terms of T<sub>TX\_CLK</sub>, which is the maximum clock cycle period of the equivalent interface speed that the eTSEC1 port is running.

When eTSEC1 is configured to operate in the parallel mode, the  $T_{TX\_CLK}$  is the maximum clock period of the TSEC1\_TX\_CLK. When eTSEC1 operates in SGMII mode, the maximum value of  $t_{T1588CLK}$  is defined in terms of the recovered clock from SGMII SerDes. For example, for 10/100/1000 Mbps modes, the maximum value of  $t_{T1588CLK}$  will be 2800, 280, and 56 ns respectively.

See the MPC8536E PowerQUICC III Integrated Communications Processor Reference Manual for a description of TMR\_CTRL registers.

2. It need to be at least two times of clock period of clock selected by TMR\_CTRL[CKSEL]. See the *MPC8536E PowerQUICC III Integrated Processor Reference Manual* for a description of TMR\_CTRL registers.

# 2.10 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals EC\_MDIO (management data input/output) and EC\_MDC (management data clock). The electrical characteristics for GMII, SGMII, RGMII, RMII, TBI and RTBI are specified in Section 2.9, "Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management"

| Parameter                                                          | Configuration | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|---------------|----------------------|-----|-----|------|-------|

| Output hold from local bus clock for LAD/LDP                       | —             | t <sub>LBKHOX2</sub> | 0.8 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) |               | t <sub>LBKHOZ1</sub> | _   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP               | —             | t <sub>LBKHOZ2</sub> |     | 2.6 | ns   | 5     |

## Table 52. Local Bus General Timing Parameters (BV<sub>DD</sub> = 2.5 V DC) (continued)

Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 2.5-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. tLBOTOT is guaranteed with LBCR[AHD] = 0.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BVDD/2.

This table describes the general timing parameters of the local bus interface at  $BV_{DD} = 1.8 \text{ V DC}$ .

| Parameter                                                                       | Configuration | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|---------------------------------------------------------------------------------|---------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | —             | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | —             | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    |       |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | —             | <b>t</b> LBKSKEW                    |     | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | —             | t <sub>LBIVKH1</sub>                | 2.4 | _   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | —             | t <sub>LBIVKH2</sub>                | 1.9 | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | —             | t <sub>LBIXKH1</sub>                | 1.1 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | —             | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | —             | t <sub>LBOTOT</sub>                 | 1.2 | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | —             | t <sub>LBKHOV1</sub>                |     | 3.2 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                                       | —             | t <sub>LBKHOV2</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | —             | t <sub>LBKHOV3</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to LALE assertion                                               | —             | t <sub>LBKHOV4</sub>                |     | 3.2 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | —             | t <sub>LBKHOX1</sub>                | 0.9 | —   | ns   | 3     |

Table 53. Local Bus General Timing Parameters (BV<sub>DD</sub> = 1.8 V DC)

| Parameter                                                          | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to data valid for LAD/LDP                          | t <sub>LBKLOV2</sub> | —   | 0.5 | ns   | 4     |

| Local bus clock to address valid for LAD, and LALE                 | t <sub>LBKLOV3</sub> | _   | 0.5 | ns   | 4     |

| Local bus clock to LALE assertion                                  | t <sub>LBKLOV4</sub> | —   | 0.5 | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)         | t <sub>LBKLOX1</sub> | _   | 2.2 | ns   | 4,8   |

| Output hold from local bus clock for LAD/LDP                       | t <sub>LBKLOX2</sub> | —   | 2.2 | ns   | 4,8   |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) | t <sub>LBKLOZ1</sub> | —   | 0.1 | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP               | t <sub>LBKLOZ2</sub> |     | 0.1 | ns   | 7     |

## Table 54. Local Bus General Timing Parameters—PLL Bypassed (continued)

#### Notes:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to local bus clock for PLL bypass mode.

- 3. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 4. All signals are measured from BVDD/2 of the rising edge of local bus clock for PLL bypass mode to 0.4 x BVDD of the signal in question for 3.3-V signaling levels.

- 5. Input timings are measured at the pin.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. tLBOTOT is guaranteed with LBCR[AHD] = 0.

- 7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 8. These timing parameters for PLL bypass mode are defined in the opposite direction of the PLL enabled output hold timing parameters.

| Parameter                            | Symbol <sup>1</sup> | Min | Max | Unit   | Notes |

|--------------------------------------|---------------------|-----|-----|--------|-------|

| HRESET high to first FRAME assertion | t <sub>PCRHFV</sub> | 10  | _   | clocks | 8     |

| Rise time (20%–80%)                  | <b>t</b> PCICLK     | 0.6 | 2.1 | ns     | _     |

| Failing time (20%–80%)               | <b>t</b> PCICLK     | 0.6 | 2.1 | ns     | _     |

#### Table 68. PCI AC Timing Specifications at 66 MHz (continued)

#### Notes:

- The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>PCIVKH</sub> symbolizes PCI timing (PC) with respect to the time the input signals (I) reach the valid state (V) relative to the SYSCLK clock, t<sub>SYS</sub>, reference (K) going to the high (H) state or setup time. Also, t<sub>PCRHFV</sub> symbolizes PCI timing (PC) with respect to the time hard reset (R) went high (H) relative to the frame signal (F) going to the valid (V) state.

</sub>

- 2. See the timing measurement conditions in the PCI 2.2 Local Bus Specifications.

- 3. All PCI signals are measured from  $OV_{DD}/2$  of the rising edge of PCI\_SYNC\_IN to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V PCI signaling levels.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Input timings are measured at the pin.

- The timing parameter t<sub>SYS</sub> indicates the minimum and maximum CLK cycle times for the various specified frequencies. The system clock period must be kept within the minimum and maximum defined ranges. For values see Section 22, "Clocking."

- 7. The setup and hold time is with respect to the rising edge of HRESET.

- 8. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the *PCI 2.2 Local Bus Specifications*.

- 9. The reset assertion timing requirement for HRESET is 100  $\mu$ s.

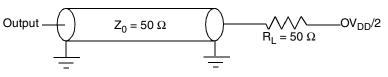

This figure provides the AC test load for PCI.

Figure 54. PCI AC Test Load

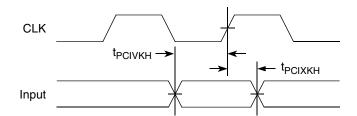

This figure shows the PCI input AC timing conditions.

Figure 55. PCI Input AC Timing Measurement Conditions

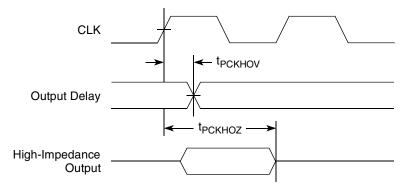

This figure shows the PCI output AC timing conditions.

Figure 56. PCI Output AC Timing Measurement Condition

## 2.20 High-Speed Serial Interfaces

This chip features two Serializer/Deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. The SerDes1 interface is dedicated for PCI Express data transfers. The SerDes2 can be used for SGMII or SATA.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

## 2.20.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 57 shows how the signals are defined. For illustration purposes, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SDn\_TX and  $\overline{SDn_TX}$ ) or a receiver input (SDn\_RX and  $\overline{SDn_RX}$ ). Each signal swings between A Volts and B Volts where A > B.

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

## 1. Single-Ended Swing

The transmitter output signals and the receiver input signals SDn\_TX, SDn\_TX, SDn\_RX and SDn\_RX each have a peak-to-peak swing of A - B Volts. This is also referred as each signal wire's Single-Ended Swing.

## 2. Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The Differential Output Voltage (or Swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SDn TX}$  -  $V_{\overline{SDn TX}}$ . The  $V_{OD}$  value can be either positive or negative.

## 3. Differential Input Voltage, V<sub>ID</sub> (or Differential Input Swing):

The Differential Input Voltage (or Swing) of the receiver,  $V_{ID}$ , is defined as the difference of the two complimentary input voltages:  $V_{SDn_RX}$  -  $V_{\overline{SDn_RX}}$ . The  $V_{ID}$  value can be either positive or negative.

## 4. Differential Peak Voltage, V<sub>DIFFD</sub>

The peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak Voltage,  $V_{DIFFp} = |A - B|$  Volts.

## 5. Differential Peak-to-Peak, VDIFFp-p

Since the differential output signal of the transmitter and the differential input signal of the receiver each range from A - B to -(A - B) Volts, the peak-to-peak value of the differential transmitter output signal or the differential

receiver input signal is defined as Differential Peak-to-Peak Voltage,  $V_{DIFFp-p} = 2*V_{DIFFp} =$

2 \* |(A - B)| Volts, which is twice of differential swing in amplitude, or twice of the differential

## 2.23.2 CCB/SYSCLK PLL Ratio

The CCB clock is the clock that drives the e500 core complex bus (CCB), and is also called the platform clock. The frequency of the CCB is set using the following reset signals, as shown in the following table:

- SYSCLK input signal

- Binary value on LA[28:31] at power up

Note that there is no default for this PLL ratio; these signals must be pulled to the desired values.

| Binary Value of LA[28:31] Signals | CCB:SYSCLK Ratio | Binary Value of LA[28:31] Signals | CCB:SYSCLK Ratio |

|-----------------------------------|------------------|-----------------------------------|------------------|

| 0000                              | Reserved         | 1000                              | 8:1              |

| 0001                              | Reserved         | 1001                              | 9:1              |

| 0010                              | Reserved         | 1010                              | 10:1             |

| 0011                              | 3:1              | 1011                              | Reserved         |

| 0100                              | 4:1              | 1100                              | 12:1             |

| 0101                              | 5:1              | 1101                              | Reserved         |

| 0110                              | 6:1              | 1110                              | Reserved         |

| 0111                              | Reserved         | 1111                              | Reserved         |

Table 75. CCB Clock Ratio

## 2.23.3 e500 Core PLL Ratio

This table describes the clock ratio between the e500 core complex bus (CCB) and the e500 core clock. This ratio is determined by the binary value of LBCTL, LALE and LGPL2 at power up, as shown in this table.

| Binary Value of<br>LBCTL, LALE,<br>LGPL2 Signals | e500 core: CCB Clock Ratio | Binary Value of<br>LBCTL, LALE,<br>LGPL2 Signals | e500 core: CCB Clock Ratio |

|--------------------------------------------------|----------------------------|--------------------------------------------------|----------------------------|

| 000                                              | 4:1                        | 100                                              | 2:1                        |

| 001                                              | 9:2                        | 101                                              | 5:2                        |

| 010                                              | Reserved                   | 110                                              | 3:1                        |

| 011                                              | 3:2                        | 111                                              | 7:2                        |

Table 76. e500 Core to CCB Clock Ratio

## 2.23.4 DDR/DDRCLK PLL Ratio

The DDR memory controller complex can be synchronous with, or asynchronous to, the CCB, depending on configuration.

The following table describes the clock ratio between the DDR memory controller complex and the DDR/DDRCLK PLL reference clock, DDRCLK, which is not the memory bus clock.

When synchronous mode is selected, the memory buses are clocked at half the CCB clock rate. The default mode of operation is for the DDR data rate for the DDR controller to be equal to the CCB clock rate in synchronous mode, or the resulting DDR PLL rate in asynchronous mode.

In asynchronous mode, the DDR PLL rate to DDRCLK ratios listed in Table 77 reflects the DDR data rate to DDRCLK ratio, since the DDR PLL rate in asynchronous mode means the DDR data rate resulting from DDR PLL output.

Please note that the DDR PLL reference clock input, DDRCLK, is only required in asynchronous mode.

The DDRCLKDR configuration register in the Global Utilities block allows the DDR controller to be run in a divided down mode where the DDR bus clock is half the speed of the default configuration. Changing of these defaults must be completed prior to initialization of the DDR controller.

| Functional Signals       | Reset Configuration<br>Name | Value (Binary) | DDR:DDRCLK Ratio |

|--------------------------|-----------------------------|----------------|------------------|

|                          |                             | 000            | 3:1              |

|                          |                             | 001            | 4:1              |

|                          |                             | 010            | 6:1              |

| TSEC_1588_TRIG_OUT[0:1], | of a data attraction        | 011            | 8:1              |

| TSEC1_1588_CLK_OUT       | cfg_ddr_pll[0:2]            | 100            | 10:1             |

|                          |                             | 101            | 12:1             |

|                          |                             | 110            | Reserved         |

|                          |                             | 111            | Synchronous mode |

| Table 77. DDR Clock Ratio |

|---------------------------|

|---------------------------|

## 2.23.5 PCI Clocks

The integrated PCI controller in this chip supports PCI input clock frequency in the range of 33–66 MHz. The PCI input clock can be applied from SYSCLK in synchronous mode or PCI1\_CLK in asynchronous mode. For specifications on the PCI1\_CLK, refer to the PCI 2.2 Specification.

The use of PCI1\_CLK is optional if SYSCLK is in the range of 33–66 MHz. If SYSCLK is outside this range then use of PCI1\_CLK is required as a separate PCI clock source, asynchronous with respect to SYSCLK.

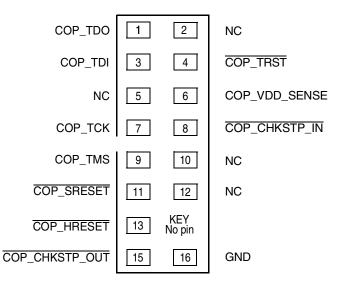

Figure 79. COP Connector Physical Pinout

# 3.11 Guidelines for High-Speed Interface Termination

## 3.11.1 SerDes1 Interface Entirely Unused

If the high-speed SerDes interface is not used at all, the unused pin should be terminated as described in this section. However, the SerDes must always have power applied to its supply pins. There are several reserved pins that need to be either left floating or connected to XGND. See SerDes1 in Table 1 for details.

The following pins must be left unconnected (float):

- SD1\_TX[7:4]

- SD1\_TX[7:4]

- Reserved pins T22, T23

The following pins must be connected to XGND:

- SD1\_RX[7:4]

- SD1\_RX[7:4]

- SD1\_REF\_CLK

- SD1 REF CLK

The POR configuration pin cfg\_io\_ports[0:2] on TSEC3\_TXD[6:3] can be used to power down SerDes 1 block for power saving. Note that both SVDD and XVDD must remain powered.

## 3.11.2 SerDes 1 Interface Partly Unused

If only part of the high speed SerDes interface pins are used, the remaining high-speed serial I/O pins should be terminated as described in this section.

The following pins must be left unconnected (float) if not used:

- SD1\_TX[7:4]

- SD1\_TX[7:4]

- Reserved pins: T22, T23

**Ordering Information**