# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.25GHz                                                                |

| Co-Processors/DSP               | · · · · · · · · · · · · · · · · · · ·                                  |

| RAM Controllers                 | DDR2, DDR3                                                             |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | · · · · · · · · · · · · · · · · · · ·                                  |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | SATA 3Gbps (2)                                                         |

| USB                             | USB 2.0 (3)                                                            |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 90°C (TA)                                                        |

| Security Features               | ·                                                                      |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8536avjatha |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Pin A | ssignments and Reset States                              |

|---|-------|----------------------------------------------------------|

|   | 1.1   | Pin Map                                                  |

| 2 | Elect | rical Characteristics                                    |

|   | 2.1   | Overall DC Electrical Characteristics                    |

|   | 2.2   | Power Sequencing                                         |

|   | 2.3   | Power Characteristics                                    |

|   | 2.4   | Input Clocks                                             |

|   | 2.5   | RESET Initialization                                     |

|   | 2.6   | DDR2 and DDR3 SDRAM                                      |

|   | 2.7   | eSPI                                                     |

|   | 2.8   | DUART                                                    |

|   | 2.9   | Ethernet: Enhanced Three-Speed Ethernet (eTSEC),         |

|   |       | MII Management                                           |

|   | 2.10  | Ethernet Management Interface Electrical Characteristics |

|   |       | 60                                                       |

|   | 2.11  | USB                                                      |

|   | 2.12  | enhanced Local Bus Controller (eLBC)65                   |

|   | 2.13  | Enhanced Secure Digital Host Controller (eSDHC)74        |

|   | 2.14  | Programmable Interrupt Controller (PIC)                  |

|   | 2.15  | JTAG                                                     |

|   | 2.16  | Serial ATA (SATA)                                        |

|   | 2.17  | l <sup>2</sup> C                                         |

|   | 2.18  | GPIO                                                     |

|   | 2.19  | PCI                                                      |

|   | 2.20  | High-Speed Serial Interfaces                             |

|   | 2.21  | PCI Express                                         |

|---|-------|-----------------------------------------------------|

|   | 2.23  | Clocking                                            |

|   | 2.24  | Thermal                                             |

| 3 | Hard  | ware Design Considerations 113                      |

|   | 3.1   | System Clocking 113                                 |

|   | 3.2   | Power Supply Design and Sequencing 113              |

|   | 3.3   | Pin States in Deep Sleep State 114                  |

|   | 3.4   | Decoupling Recommendations 114                      |

|   | 3.5   | SerDes Block Power Supply Decoupling                |

|   |       | Recommendations                                     |

|   | 3.6   | Connection Recommendations                          |

|   | 3.7   | Pull-Up and Pull-Down Resistor Requirements 115     |

|   | 3.8   | Output Buffer DC Impedance 115                      |

|   | 3.9   | Configuration Pin Muxing 116                        |

|   | 3.10  | JTAG Configuration Signals 117                      |

|   | 3.11  | Guidelines for High-Speed Interface Termination 119 |

| 4 | Orde  | ring Information                                    |

|   | 4.1   | Part Numbers Fully Addressed by this Document 121   |

|   | 4.2   | Part Marking 122                                    |

|   | 4.3   | Part Numbering 122                                  |

| 5 | Packa | age Information                                     |

|   | 5.1   | Package Parameters for the FC-PBGA 123              |

|   | 5.2   | Mechanical Dimensions of the FC-PBGA 124            |

| 6 | Produ | uct Documentation                                   |

| 7 | Docu  | ment Revision History                               |

**Pin Assignments and Reset States**

|    | A             | В                | С                | D                | E                | F                | G                | Н                 | J                | К                | L                      | М                   | N                 | Ρ             | _/_ |

|----|---------------|------------------|------------------|------------------|------------------|------------------|------------------|-------------------|------------------|------------------|------------------------|---------------------|-------------------|---------------|-----|

| 1  |               | GV <sub>DD</sub> | MDQS<br>[5]      | MDQ<br>[32]      | MDQ<br>[46]      | MDQ<br>[47]      | MDQ<br>[34]      | GND               | MDQ<br>[56]      | MDQ<br>[57]      | GND                    | GV <sub>DD</sub>    | MDQS<br>[7]       | MDQ<br>[58]   | N   |

| 2  | MDQ<br>[44]   | MDQ<br>[40]      | MDM<br>[5]       | MDQS<br>[5]      | GV <sub>DD</sub> | MDQ<br>[42]      | MDQ<br>[43]      | MDQ<br>[35]       | MDQ<br>[60]      | MDQ<br>[61]      | MDM<br>[7]             | MDQS<br>[7]         | GND               | MDM<br>[62]   |     |

| 3  | GND           | MDQ<br>[45]      | MDQ<br>[41]      | MCS<br>[0]       | GND              | MDQ<br>[33]      | GV <sub>DD</sub> | MDQ<br>[38]       | MDQ<br>[52]      | GV <sub>DD</sub> | MDM<br>[6]             | MDQS<br>[6]         | MDQ<br>[50]       | MDQ<br>[51]   |     |

| 4  | MBA<br>[0]    | MWE              | MCS<br>[2]       | GV <sub>DD</sub> | MDQ<br>[36]      | GND              | MDM<br>[4]       | GND               | MDQ<br>[39]      | MDQ<br>[53]      | MDQ<br>[49]            | MDQS<br>[6]         | MDQ<br>[54]       | MDQ<br>[55]   |     |

| 5  | MA<br>[10]    | MBA<br>[1]       | MRAS             | GND              | MODT<br>[0]      | GV <sub>DD</sub> | MDQ<br>[37]      | GV <sub>DD</sub>  | MDQS<br>[4]      | MDQS<br>[4]      | MDQ<br>[48]            | GND                 | GV <sub>DD</sub>  | GND           |     |

| 6  | MAPAR_<br>OUT | NC               | GND              | GV <sub>DD</sub> | MODT<br>[2]      | MODT<br>[3]      | MCS<br>[3]       | MCS<br>[1]        | МСК<br>[2]       | MCK<br>[2]       | SD2_<br>IMP_CAL<br>_TX | SD2_<br>REF_<br>CLK | S2GND             | SD2_RX<br>[0] |     |

| 7  | GND           | MA<br>[0]        | GV <sub>DD</sub> | NC               | MCAS             | MA<br>[13]       | GV <sub>DD</sub> | MODT<br>[1]       | NC               | GND              | SD2_<br>PLL_<br>TPD    | SD2_<br>REF_<br>CLK | S2V <sub>DD</sub> | SD2_RX<br>[0] |     |

| 8  | MCK<br>[3]    | MCK<br>[3]       | MA<br>[2]        | GND              | GV <sub>DD</sub> | GND              | MA<br>[1]        | MCK<br>[5]        | MCK<br>[5]       | GND              | Rsvd                   | S2GND               | SD2_RX<br>[1]     | S2GND         |     |

| 9  | МСК<br>[0]    | MCK<br>[0]       | GV <sub>DD</sub> | MA<br>[4]        | MA<br>[8]        | MA<br>[7]        | GV <sub>DD</sub> | MCKE<br>[3]       | NC               | NC               | Rsvd                   | S2V <sub>DD</sub>   | SD2_RX<br>[1]     | S2GND         |     |

| 10 | MA<br>[3]     | GND              | MA<br>[5]        | NC               | MA<br>[14]       | MA<br>[15]       | MCKE<br>[2]      | MCKE<br>[0]       | GV <sub>DD</sub> | MCKE<br>[1]      | NC                     | X2GND               | NC                | NC            |     |

| 11 | MA<br>[6]     | GV <sub>DD</sub> | MECC<br>[3]      | MA<br>[12]       | GV <sub>DD</sub> | MECC<br>[2]      | GV <sub>DD</sub> | <u>МСК</u><br>[1] | МСК<br>[1]       | GND              | x2V <sub>DD</sub>      | SD2_TX<br>[1]       | X2GND             | SD2_TX<br>[0] |     |

| 12 | MA<br>[11]    | MA<br>[9]        | GND              | MECC<br>[7]      | GND              | NC               | MECC<br>[0]      | GV <sub>DD</sub>  | GND              | GV <sub>DD</sub> | X2GND                  | SD2_TX<br>[1]       | x2V <sub>DD</sub> | SD2_TX<br>[0] |     |

| 13 | MAPAR_<br>ERR | MBA<br>[2]       | MECC<br>[6]      | MDQS<br>[8]      | MDQS<br>[8]      | MDM<br>[8]       | GND              | MCK<br>[4]        | МСК<br>[4]       | VDD_<br>CORE     | GND                    | VDD_<br>CORE        | GND               | VDD_<br>CORE  |     |

| 14 | GND           | MDQ<br>[27]      | GV <sub>DD</sub> | MECC<br>[1]      | GV <sub>DD</sub> | MECC<br>[5]      | MECC<br>[4]      | GV <sub>DD</sub>  | GND              | GV <sub>DD</sub> | VDD_<br>CORE           | GND                 | VDD_<br>CORE      | GND           |     |

| <  | 2             |                  |                  |                  |                  |                  | DET              |                   |                  |                  |                        |                     |                   |               |     |

Figure 3. Chip Pin Map Detail A

| Table | 1.  | Pinout | Listina | (continued) |

|-------|-----|--------|---------|-------------|

| labio | ••• | . moat | Lioung  | (oonaba)    |

| Signal               | Signal Name                    | Package Pin Number                                  | Pin Type | Power<br>Supply  | Notes  |

|----------------------|--------------------------------|-----------------------------------------------------|----------|------------------|--------|

|                      | Programmable I                 | nterrupt Controller                                 |          |                  |        |

| MCP                  | Machine check processor        | Y14                                                 | I        | OV <sub>DD</sub> |        |

| UDE                  | Unconditional debug event      | AB14                                                | I        | OV <sub>DD</sub> | —      |

| IRQ[0:8]             | External interrupts            | AG22,AF17,AB23,<br>AF19,AG17,AF16,<br>AA22,Y19,AB22 | I        | OV <sub>DD</sub> | _      |

| IRQ[9]/DMA_DREQ[3]   | External interrupt/DMA request | AE13                                                | I        | $OV_{DD}$        | 1      |

| IRQ[10]/DMA_DACK[3]  | External interrupt/DMA Ack     | AD13                                                | I/O      | $OV_{DD}$        | 1      |

| IRQ[11]/DMA_DDONE[3] | External interrupt/DMA done    | AD14                                                | I/O      | OV <sub>DD</sub> | 1      |

| IRQ_OUT              | Interrupt output               | AC17                                                | 0        | OV <sub>DD</sub> | 2,4    |

|                      | Ethernet Mana                  | gement Interface                                    |          |                  |        |

| EC_MDC               | Management data clock          | Y10                                                 | 0        | OV <sub>DD</sub> | 5,9,22 |

| EC_MDIO              | Management data In/Out         | Y11                                                 | I/O      | OV <sub>DD</sub> |        |

|                      | Gigabit Re                     | ference Clock                                       | ••       |                  | •      |

| EC_GTX_CLK125        | Reference clock                | AA6                                                 | I        | LV <sub>DD</sub> | 31     |

|                      | Three-Speed Ethernet Co        | ntroller (Gigabit Etherne                           | et 1)    |                  |        |

| TSEC1_TXD[7:0]       | Transmit data                  | AA8,AA5,Y8,Y5,W3,<br>W5,W4,W6                       | 0        | LV <sub>DD</sub> | 5,9,22 |

| TSEC1_TX_EN          | Transmit Enable                | W1                                                  | 0        | LV <sub>DD</sub> | 23     |

| TSEC1_TX_ER          | Transmit Error                 | AB5                                                 | 0        | LV <sub>DD</sub> | 5,9    |

| TSEC1_TX_CLK         | Transmit clock In              | AB4                                                 | I        | LV <sub>DD</sub> |        |

| TSEC1_GTX_CLK        | Transmit clock Out             | W2                                                  | 0        | LV <sub>DD</sub> | —      |

| TSEC1_CRS            | Carrier sense                  | AA9                                                 | I/O      | LV <sub>DD</sub> | 17     |

| TSEC1_COL            | Collision detect               | AB6                                                 | I        | LV <sub>DD</sub> | —      |

| TSEC1_RXD[7:0]       | Receive data                   | AB3,AB7,AB8,Y6,AA2,<br>Y3,Y1,Y2                     | I        | LV <sub>DD</sub> | _      |

| TSEC1_RX_DV          | Receive data valid             | AA1                                                 | I        | LV <sub>DD</sub> |        |

| TSEC1_RX_ER          | Receive data error             | Y9                                                  | I        | LV <sub>DD</sub> | —      |

| TSEC1_RX_CLK         | Receive clock                  | AA3                                                 | I        | LV <sub>DD</sub> | —      |

|                      | Three-Speed Ethernet Co        | ntroller (Gigabit Etherne                           | et 3)    |                  |        |

| TSEC3_TXD[7:0]       | Transmit data                  | T12,V8,U8,V9,T8,T7,<br>T5,T6                        | 0        | TV <sub>DD</sub> | 5,9,22 |

| TSEC3_TX_EN          | Transmit Enable                | V5                                                  | 0        | TV <sub>DD</sub> | 23     |

| TSEC3_TX_ER          | Transmit Error                 | U9                                                  | 0        | TV <sub>DD</sub> | 5,9    |

# 2.1.3 Output Driver Characteristics

This table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                                                | Notes |

|---------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>35                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V                             | 1     |

|                                       | 45(default)<br>45(default)<br>125       | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V<br>BV <sub>DD</sub> = 1.8 V |       |

| PCI signals                           | 25                                      | OV <sub>DD</sub> = 3.3 V                                                         | 2     |

|                                       | 42 (default)                            |                                                                                  |       |

| DDR2 signal                           | 16<br>32 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                                                         | 3     |

| DDR3 signal                           | 20<br>40 (half strength mode)           | GV <sub>DD</sub> = 1.5 V                                                         | 2     |

| TSEC signals                          | 42                                      | LV <sub>DD</sub> = 2.5/3.3 V                                                     | —     |

| DUART, system control, JTAG           | 42                                      | OV <sub>DD</sub> = 3.3 V                                                         | —     |

| I <sup>2</sup> C                      | 150                                     | OV <sub>DD</sub> = 3.3 V                                                         | —     |

### Table 4. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI1\_GNT1 signal at reset.

3. The drive strength of the DDR2 or DDR3 interface in half-strength mode is at T<sub>i</sub> = 105°C and at GV<sub>DD</sub> (min)

# 2.2 Power Sequencing

The chip requires its power rails to be applied in a specific sequence in order to ensure proper chip operation. These requirements are as follows for power up:

- 1. V<sub>DD\_PLAT</sub>, V<sub>DD\_CORE</sub> (if POWER\_EN is not used to control V<sub>DD\_CORE</sub>), AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, SV<sub>DD</sub>, SV<sub>DD</sub>, TV<sub>DD</sub>, XV<sub>DD</sub> and X2V<sub>DD</sub>

- 2. [Wait for POWER\_EN to assert], then V<sub>DD CORE</sub> (if POWER\_EN is used to control V<sub>DD CORE</sub>)

- 3. GV<sub>DD</sub>

All supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-up, then the sequencing for  $GV_{DD}$  is not required.

From a system standpoint, if any of the I/O power supplies ramp prior to the VDD platform supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-up, and extra current may be drawn by the chip.

During the Deep Sleep state, the VDD core supply is removed. But all other power supplies remain applied. Therefore, there is no requirement to apply the VDD core supply before any other power rails when the silicon waking from Deep Sleep.

# 2.3 **Power Characteristics**

The estimated power dissipation for the core complex bus (CCB) versus the core frequency for this family of PowerQUICC III chips is shown in the following table.

| Power Mode        | Core<br>Frequen<br>cy | CCB<br>Frequen<br>cy | DDR<br>Frequen<br>cy | V <sub>DD</sub><br>Platfor<br>m | V <sub>DD</sub><br>Core | Junction<br>Tempera<br>ture | Core              | Power   | Platform          | n Power <sup>9</sup> | Notes   |

|-------------------|-----------------------|----------------------|----------------------|---------------------------------|-------------------------|-----------------------------|-------------------|---------|-------------------|----------------------|---------|

|                   | (MHz)                 | (MHz)                | (MHz)                | (V)                             | (V)                     | (°C)                        | mean <sup>7</sup> | Max     | mean <sup>7</sup> | Max                  |         |

| Maximum (A)       |                       |                      |                      |                                 |                         | 105                         | _                 | 4.1/3.3 |                   | 4.7/3.7              | 1, 3, 8 |

| Thermal (W)       |                       |                      |                      |                                 |                         | /90                         | _                 | 3.7/2.9 |                   | 4.7/3.7              | 1, 4, 8 |

| Typical (W)       |                       |                      |                      |                                 |                         |                             | 1.5               | _       | 1.5               | —                    | 1, 2    |

| Doze (W)          | 600                   | 400                  | 400                  | 1.0                             | 1.0                     | 65                          | 1.2               | 1.9     | 1.4               | 1.9                  | 1       |

| Nap (W)           |                       |                      |                      |                                 |                         |                             | 0.8               | 1.5     | 1.4               | 1.9                  | 1       |

| Sleep (W)         |                       |                      |                      |                                 |                         |                             | 0.8               | 1.5     | 1.0               | 1.6                  | 1       |

| Deep Sleep<br>(W) |                       |                      |                      |                                 |                         | 35                          | 0                 | 0       | 0.6               | 1.1                  | 6       |

| Maximum (A)       |                       |                      |                      | 1.0                             | 1.0                     | 105                         | —                 | 4.5/3.7 |                   | 4.7/3.7              | 1, 3, 8 |

| Thermal (W)       |                       |                      | 400                  |                                 |                         | / 90                        | —                 | 3.9/3.1 |                   | 4.7/3.7              | 1, 4, 8 |

| Typical (W)       |                       | 400                  |                      |                                 |                         |                             | 1.7               | —       | 1.5               | —                    | 1, 2    |

| Doze (W)          | 800                   |                      |                      |                                 |                         | 65                          | 1.3               | 2.1     | 1.4               | 1.9                  | 1       |

| Nap (W)           |                       |                      |                      |                                 |                         |                             | 0.8               | 1.5     | 1.4               | 1.9                  | 1       |

| Sleep (W)         |                       |                      |                      |                                 |                         |                             | 0.8               | 1.5     | 1.0               | 1.6                  | 1       |

| Deep Sleep<br>(W) |                       |                      |                      |                                 |                         | 35                          | 0                 | 0       | 0.6               | 1.1                  | 1,6     |

| Maximum (A)       |                       |                      |                      |                                 |                         | 105                         | —                 | 4.8/4.0 |                   | 4.7/3.7              | 1, 3, 8 |

| Thermal (W)       |                       |                      |                      |                                 |                         | / 90                        | _                 | 4.1/3.3 | _                 | 4.7/3.7              | 1, 4, 8 |

| Typical (W)       |                       |                      |                      |                                 |                         |                             | 1.9               | —       | 1.5               | —                    | 1, 2    |

| Doze (W)          | 1000                  | 400                  | 400                  | 1.0                             | 1.0                     | 65                          | 1.4               | 2.2     | 1.4               | 1.9                  | 1       |

| Nap (W)           |                       |                      |                      | 1.0                             |                         |                             | 0.8               | 1.6     | 1.4               | 1.9                  | 1       |

| Sleep (W)         |                       |                      |                      |                                 |                         |                             | 0.8               | 1.6     | 1.0               | 1.6                  | 1       |

| Deep Sleep<br>(W) |                       |                      |                      |                                 |                         | 35                          | 0                 | 0       | 0.6               | 1.1                  | 1, 6    |

# 2.6.2.2 DDR2 and DDR3 SDRAM Interface Output AC Timing Specifications

This table contains the output AC timing targets for the DDR2 and DDR3 SDRAM interface.

### Table 19. DDR SDRAM Output AC Timing Specifications

At recommended operating conditions with GVDD of 1.8 V  $\pm$  5% for DDR2 or 1.5 V  $\pm$  5% for DDR3.

| Parameter                                      | Symbol <sup>1</sup>                         | Min  | Мах | Unit | Notes |

|------------------------------------------------|---------------------------------------------|------|-----|------|-------|

| MCK[n] cycle time, MCK[n]/MCK[n] crossing      | t <sub>MCK</sub>                            | 3.0  | 5   | ns   | 2     |

| ADDR/CMD output setup with respect to MCK      | t <sub>DDKHAS</sub>                         |      |     | ns   | 3     |

| 667 MHz                                        |                                             | 1.10 | _   |      | 7     |

| 533 MHz                                        |                                             | 1.48 | —   |      |       |

| 400 MHz                                        |                                             | 1.95 | _   |      |       |

| ADDR/CMD output hold with respect to MCK       | t <sub>DDKHAX</sub>                         |      |     | ns   | 3     |

| 667 MHz                                        |                                             | 1.10 | _   |      | 7     |

| 533 MHz                                        |                                             | 1.48 | _   |      |       |

| 400 MHz                                        |                                             | 1.95 | _   |      |       |

| MCS[n] output setup with respect to MCK        | t <sub>DDKHCS</sub>                         |      |     | ns   | 3     |

| 667 MHz                                        |                                             | 1.10 | _   |      | 7     |

| 533 MHz                                        |                                             | 1.48 | _   |      |       |

| 400 MHz                                        |                                             | 1.95 | _   |      |       |

| MCS[n] output hold with respect to MCK         | t <sub>DDKHCX</sub>                         |      |     | ns   | 3     |

| 667 MHz                                        |                                             | 1.10 | _   |      | 7     |

| 533 MHz                                        |                                             | 1.48 | _   |      |       |

| 400 MHz                                        |                                             | 1.95 | _   |      |       |

| MCK to MDQS Skew                               | t <sub>DDKHMH</sub>                         |      |     | ns   | 4     |

| <= 667 MHz                                     |                                             | -0.6 | 0.6 |      | 7     |

| MDQ/MECC/MDM output setup with respect to MDQS | t <sub>DDKHDS,</sub><br>t <sub>DDKLDS</sub> |      |     | ps   | 5     |

| 667 MHz                                        |                                             | 450  | _   |      | 7     |

| 533 MHz                                        |                                             | 538  | —   |      |       |

| 400 MHz                                        |                                             | 700  | —   |      |       |

| MDQ/MECC/MDM output hold with respect to MDQS  | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX |      |     | ps   | 5     |

| 667 MHz                                        |                                             | 450  | _   |      | 7     |

| 533 MHz                                        |                                             | 538  | _   |      |       |

| 400 MHz                                        |                                             | 700  | —   |      |       |

| MDQS preamble start                            | t <sub>DDKHMP</sub>                         |      |     | ns   | 6     |

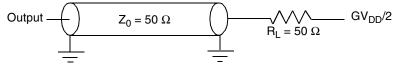

This figure provides the AC test load for the DDR bus.

Figure 11. DDR AC Test Load

# 2.7 eSPI

This section describes the DC and AC electrical specifications for the eSPI of the chip.

# 2.7.1 eSPI DC Electrical Characteristics

This table provides the DC electrical characteristics for the chip eSPI.

| Table 20. | SPI DC | Electrical | Characteristics |

|-----------|--------|------------|-----------------|

|-----------|--------|------------|-----------------|

| Characteristic      | Symbol          | Condition                      | Min  | Мах                    | Unit |

|---------------------|-----------------|--------------------------------|------|------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -6.0 mA      | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 6.0 mA       |      | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA       | _    | 0.4                    | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 \ V \le V_{IN} \le OV_{DD}$ | —    | ±10                    | μA   |

# 2.7.2 eSPI AC Timing Specifications

This table and provide the eSPI input and output AC timing specifications.

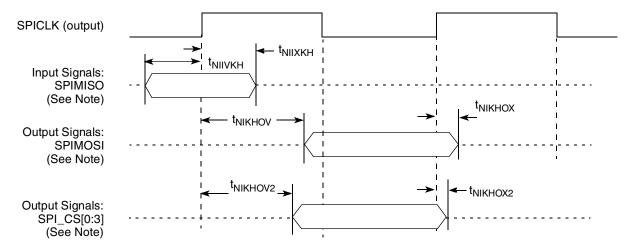

Table 21. SPI AC Timing Specifications<sup>1</sup>

| Characteristic                        | Symbol <sup>2</sup>  | Min | Мах | Unit | Note |

|---------------------------------------|----------------------|-----|-----|------|------|

| SPI_MOSI output—Master data hold time | t <sub>NIKHOX</sub>  | 0.5 | _   | ns   | 3    |

|                                       | t <sub>NIKHOX</sub>  | 4.0 |     |      | 4    |

| SPI_MOSI output—Master data delay     | t <sub>NIKHOV</sub>  |     | 6.0 |      | 3    |

|                                       | t <sub>NIKHOV</sub>  |     | 7.4 | ns   | 4    |

| SPI_CS outputs—Master data hold time  | t <sub>NIKHOX2</sub> | 0   | —   | ns   | —    |

| Characteristic                          | Symbol <sup>2</sup>  | Min | Max | Unit | Note |

|-----------------------------------------|----------------------|-----|-----|------|------|

| SPI_CS outputs—Master data delay        | t <sub>NIKHOV2</sub> | _   | 6.0 | ns   | _    |

| SPI inputs—Master data input setup time | t <sub>NIIVKH</sub>  | 5   |     | ns   |      |

| SPI inputs—Master data input hold time  | t <sub>NIIXKH</sub>  | 0   | _   | ns   | _    |

Table 21. SPI AC Timing Specifications<sup>1</sup> (continued)

Notes:

1. Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are measured at the pin.

2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>NIKHOV</sub> symbolizes the NMSI outputs internal timing (NI) for the time t<sub>SPI</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are valid (V).

3. SPCOM[RxDelay] is set to 0.

4. SPCOM[RxDelay] is set to 1.

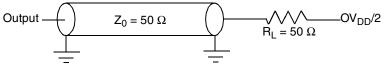

This figure provides the AC test load for the SPI.

This figure represents the AC timing from Table 21. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Note: The clock edge is selectable on SPI.

Figure 13. SPI AC Timing in Master mode (Internal Clock) Diagram

| Parameters                                                                                        | Parameters Symbol I                |           | Мах                                      | Unit | Notes  |

|---------------------------------------------------------------------------------------------------|------------------------------------|-----------|------------------------------------------|------|--------|

| Supply voltage 2.5 V                                                                              | LV <sub>DD</sub> /TV <sub>DD</sub> | 2.37      | 2.63                                     | V    | 1,2    |

| Output high voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, IOH = -1.0 mA)                  | V <sub>OH</sub>                    | 2.00      | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | _      |

| Output low voltage<br>(LV <sub>DD</sub> / <u>TV<sub>DD</sub></u> = Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>                    | GND – 0.3 | 0.40                                     | V    | —      |

| Input high voltage                                                                                | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$                  | V    | —      |

| Input low voltage                                                                                 | V <sub>IL</sub>                    | -0.3      | 0.70                                     | V    | —      |

| Input high current<br>(V <sub>IN</sub> = LV <sub>DD</sub> , V <sub>IN</sub> = TV <sub>DD</sub> )  | IIH                                | _         | 10                                       | μA   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                                                      | Ι <sub>ΙL</sub>                    | -15       |                                          | μA   | 3      |

#### Table 25. RGMII, RTBI, and FIFO DC Electrical Characteristics

Note:

<sup>1</sup> LV<sub>DD</sub> supports eTSECs 1.

$^2$  TV<sub>DD</sub> supports eTSECs 3.

<sup>3</sup> Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

# 2.9.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI are presented in this section.

# 2.9.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, since they have similar performance and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back out onto the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source-synchronous timing reference. Typically, the clock edge that launched the data can be used, since the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is relationship between the maximum FIFO speed and the platform speed. For more information see Section 2.4.6, "Platform to FIFO Restrictions."

A summary of the FIFO AC specifications appears in the following tables.

### Table 26. FIFO Mode Transmit AC Timing Specification

| Parameter/Condition                       | Symbol            | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------|-----|-----|-----|------|

| TX_CLK, GTX_CLK clock period <sup>2</sup> | t <sub>FIT</sub>  | 6.0 | 8.0 | 100 | ns   |

| TX_CLK, GTX_CLK duty cycle                | t <sub>FITH</sub> | 45  | 50  | 55  | %    |

| TX_CLK, GTX_CLK peak-to-peak jitter       | t <sub>FITJ</sub> | _   | —   | 250 | ps   |

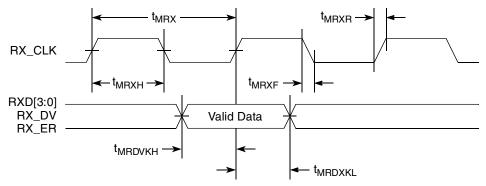

This figure shows the MII receive AC timing diagram.

Figure 21. MII Receive AC Timing Diagram

# 2.9.2.4 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

# 2.9.2.4.1 TBI Transmit AC Timing Specifications

This table provides the TBI transmit AC timing specifications.

### Table 32. TBI Transmit AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition            | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit |

|--------------------------------|-------------------------------------|-----|-----|-----|------|

| GTX_CLK clock period           | t <sub>TTX</sub>                    | —   | 8.0 | —   | ns   |

| GTX_CLK duty cycle             | t <sub>TTXH</sub> /t <sub>TTX</sub> | 40  | _   | 60  | %    |

| GTX_CLK to TCG[9:0] delay time | t <sub>TTKHDX</sub> 2               | 1.0 | _   | 5.0 | ns   |

| GTX_CLK rise (20%-80%)         | t <sub>TTXR</sub>                   | _   | _   | 1.0 | ns   |

| GTX_CLK fall time (80%-20%)    | t <sub>TTXF</sub>                   | _   |     | 1.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state )(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the invalid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

2. Data valid tTTKHDV to GTX\_CLK Min Setup time is a function of clock period and max hold time. (Min Setup = Cycle time - Max Hold)

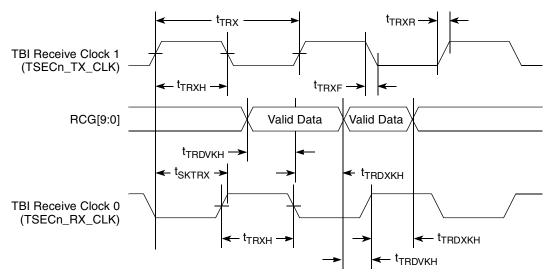

This figure shows the TBI transmit AC timing diagram.

This figure shows the TBI receive AC timing diagram.

Figure 23. TBI Receive AC Timing Diagram

# 2.9.2.5 TBI Single-Clock Mode AC Specifications

When the eTSEC is configured for TBI modes, all clocks are supplied from external sources to the relevant eTSEC interface. In single-clock TBI mode, when a 125-MHz TBI receive clock is supplied on TSEC*n* pin (no receive clock is used on in this mode, whereas for the dual-clock mode this is the PMA0 receive clock). The 125-MHz transmit clock is applied on the in all TBI modes.

A summary of the single-clock TBI mode AC specifications for receive appears in the following table.

### Table 34. TBI single-clock Mode Receive AC Timing Specification

At recommended operating conditions with  $\text{LV}_{\text{DD}}/\text{TV}_{\text{DD}}$  of 3.3 V  $\pm$  5%

| Parameter/Condition                       | Symbol             | Min | Тур | Max | Unit |

|-------------------------------------------|--------------------|-----|-----|-----|------|

| RX_CLK clock period                       | t <sub>TRR</sub>   | 7.5 | 8.0 | 8.5 | ns   |

| RX_CLK duty cycle                         | t <sub>TRRH</sub>  | 40  | 50  | 60  | %    |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>  | —   | -   | 250 | ps   |

| Rise time RX_CLK (20%-80%)                | t <sub>TRRR</sub>  | —   |     | 1.0 | ns   |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>  | —   | _   | 1.0 | ns   |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>TRRDV</sub> | 2.0 | _   | —   | ns   |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>TRRDX</sub> | 1.0 |     |     | ns   |

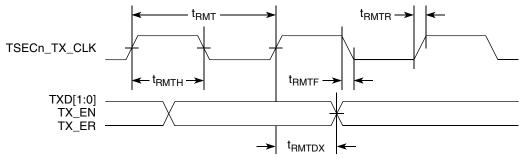

### Table 36. RMII Transmit AC Timing Specifications (continued)

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                             | Symbol <sup>1</sup> | Min | Тур | Мах  | Unit |

|-------------------------------------------------|---------------------|-----|-----|------|------|

| Rise time TSECn_TX_CLK (20%–80%)                | t <sub>RMTR</sub>   | 1.0 |     | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%-20%)                | t <sub>RMTF</sub>   | 1.0 | _   | 2.0  | ns   |

| TSECn_TX_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>  | 2.0 |     | 10.0 | ns   |

#### Note:

The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

This figure shows the RMII transmit AC timing diagram.

Figure 26. RMII Transmit AC Timing Diagram

#### 2.9.2.7.2 RMII Receive AC Timing Specifications

### Table 37. RMII Receive AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition              | Symbol <sup>1</sup> | Min  | Тур  | Мах  | Unit |

|----------------------------------|---------------------|------|------|------|------|

| TSECn_RX_CLK clock period        | t <sub>RMR</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_RX_CLK duty cycle          | t <sub>RMRH</sub>   | 35   | 50   | 65   | %    |

| TSECn_RX_CLK peak-to-peak jitter | t <sub>RMRJ</sub>   |      |      | 250  | ps   |

| Rise time TSECn_RX_CLK (20%–80%) | t <sub>RMRR</sub>   | 1.0  | _    | 2.0  | ns   |

When operating in SGMII mode, the eTSEC EC\_GTX\_CLK125 clock is not required for this port. Instead, SerDes reference clock is required on SD2\_REF\_CLK and SD2\_REF\_CLK pins.

# 2.9.3.1 DC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

The characteristics and DC requirements of the separate SerDes reference clock are described in Section 2.20, "High-Speed Serial Interfaces."

# 2.9.3.2 AC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK

This table lists the SGMII SerDes reference clock AC requirements. Please note that SD2\_REF\_CLK and SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

| Symbol             | Parameter Description                                                                    | Min | Typical | Max | Units | Notes |

|--------------------|------------------------------------------------------------------------------------------|-----|---------|-----|-------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                        | —   | 10 (8)  | —   | ns    | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles |     | _       | 100 | ps    | —     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location              | -50 | _       | 50  | ps    | 2,3   |

## Table 38. SD2\_REF\_CLK and SD2\_REF\_CLK AC Requirements

Notes:

1.8 ns applies only when 125 MHz SerDes2 reference clock frequency is selected via cfg\_srds\_sgmii\_refclk during POR.

2. In a frequency band from 150 kHz to 15 MHz, at BER of 10E-12.

3. Total peak-to-peak deterministic jitter "Dj" should be less than or equal to 50 ps.

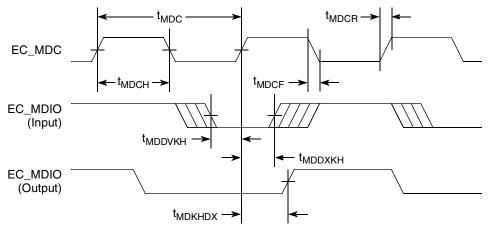

### Table 45. MII Management AC Timing Specifications (continued)

At recommended operating conditions with OVDD is  $3.3 \text{ V} \pm 5\%$ .

| Parameter/Condition         | Symbol <sup>1</sup> | Min | Тур | Мах | Unit | Notes |

|-----------------------------|---------------------|-----|-----|-----|------|-------|

| EC_MDIO to EC_MDC hold time | t <sub>MDDXKH</sub> | 0   | _   | —   | ns   | —     |

| EC_MDC rise time            | t <sub>MDCR</sub>   | —   | _   | 10  | ns   | —     |

| EC_MDC fall time            | t <sub>MDHF</sub>   | _   | _   | 10  | ns   | —     |

Notes:

1. The symbols used for timing specifications herein follow the pattern of t(first two letters of functional block)(signal)(state)

(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. This parameter is dependent on the eTSEC system clock speed, which is half of the Platform Frequency ( $f_{CCB}$ ). The actual EC\_MDC output clock frequency for a specific eTSEC port can be programmed by configuring the MgmtClk bit field of chip's MIIMCFG register, based on the platform (CCB) clock running for the chip. The formula is: Platform Frequency (CCB)/(2\*Frequency Divider determined by MIICFG[MgmtClk] encoding selection). For example, if MIICFG[MgmtClk] = 000 and the platform (CCB) is currently running at 533 MHz,  $f_{MDC} = 533/(2*4*8) = 533/64 = 8.3$  MHz. That is, for a system running at a particular platform frequency ( $f_{CCB}$ ), the EC\_MDC output clock frequency can be programmed between maximum  $f_{MDC} = f_{CCB}/64$  and minimum  $f_{MDC} = f_{CCB}/448$ . See the MPC8536E reference manual's MIIMCFG register section for more detail.

- 3. This parameter is dependent on the platform clock frequency. The delay is equal to 16 platform clock periods +/-3ns. For example, with a platform clock of 333MHz, the min/max delay is 48ns +/-3ns. Similarly, if the platform clock is 400MHz, the min/max delay is 40ns +/-3ns).

- 5. t<sub>CLKplb clk</sub> is the platform (CCB) clock

- 6. EC\_MDC to EC\_MDIO Data valid t<sub>MDKHDV</sub> is a function of clock period and max delay time t<sub>MDKHDX</sub>. (Min Setup = Cycle time Max Hold)

This figure shows the MII management AC timing diagram.

Figure 35. MII Management Interface Timing Diagram

# 2.11 USB

This section provides the AC and DC electrical specifications for the USB interface of the chip.

# 2.11.1 USB DC Electrical Characteristics

This table provides the DC electrical characteristics for the USB interface.

| Parameter                                             | Symbol          | Min                    | Max                    | Unit |

|-------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                              | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                               | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| Input current                                         | I <sub>IN</sub> | —                      | ±5                     | μA   |

| High-level output voltage,<br>$I_{OH} = -100 \ \mu A$ | V <sub>OH</sub> | OV <sub>DD</sub> - 0.2 | Ι                      | V    |

| Low-level output voltage,<br>$I_{OL} = 100 \mu A$     | V <sub>OL</sub> | —                      | 0.2                    | V    |

#### Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 2.11.2 USB AC Electrical Specifications

This table describes the general timing parameters of the USB interface of the chip.

Table 47. USB General Timing Parameters<sup>6</sup>

| Parameter                                | Symbol <sup>1</sup> | Min | Мах | Unit | Notes |

|------------------------------------------|---------------------|-----|-----|------|-------|

| usb clock cycle time                     | t <sub>USCK</sub>   | 15  | _   | ns   | 2-5   |

| Input setup to usb clock - all inputs    | t <sub>USIVKH</sub> | 4   | —   | ns   | 2-5   |

| input hold to usb clock - all inputs     | t <sub>USIXKH</sub> | 1   | _   | ns   | 2-5   |

| usb clock to output valid - all outputs  | t <sub>USKHOV</sub> | —   | 7   | ns   | 2-5   |

| Output hold from usb clock - all outputs | t <sub>USKHOX</sub> | 2   | —   | ns   | 2-5   |

#### Notes:

The symbols for timing specifications follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>USIXKH</sub> symbolizes usb timing (US) for the input (I) to go invalid (X) with respect to the time the usb clock reference (K) goes high (H). Also, t<sub>USKHOX</sub> symbolizes USB timing (US) for the USB clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to USB clock.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of the USB clock to  $0.4 \times OV_{DD}$  of the signal in question for 3.3 V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to that of the leakage current specification.

- 6. When switching the data pins from outputs to inputs using the USBn\_DIR pin, the output timings will be violated on that cycle because the output buffers are tristated asynchronously. This should not be a problem, because the PHY should not be functionally looking at these signals on that cycle as per ULPI specifications

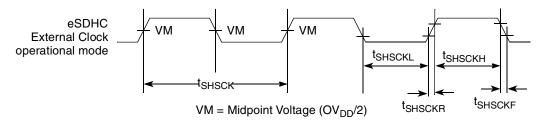

This figure provides the eSDHC clock input timing diagram.

Figure 43. eSDHC Clock Input Timing Diagram

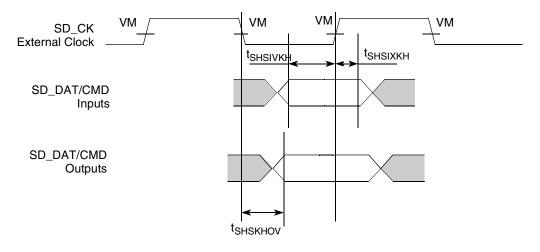

This figure provides the data and command input/output timing diagram.

VM = Midpoint Voltage (OV<sub>DD</sub>/2)

Figure 44. eSDHC Data and Command Input/Output Timing Diagram Referenced to Clock

# 2.14 Programmable Interrupt Controller (PIC)

In IRQ edge trigger mode, when an external interrupt signal is asserted (according to the programmed polarity), it must remain the assertion for at least 3 system clocks (SYSCLK periods).

# 2.15 JTAG

This section describes the DC and AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the chip.

# 2.15.1 JTAG DC Electrical Characteristics

This table provides the DC electrical characteristics for the JTAG interface.

Table 57. JTAG DC Electrical Characteristics

| Parameter                | Symbol <sup>1</sup> | Min  | Мах                    | Unit |

|--------------------------|---------------------|------|------------------------|------|

| High-level input voltage | V <sub>IH</sub>     | 2    | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage  | V <sub>IL</sub>     | -0.3 | 0.8                    | V    |

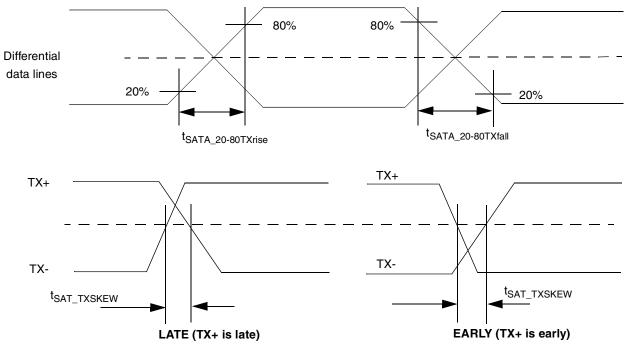

Figure 50. Signal Rise and Fall Times and Differential Skew

# 2.16.3 Differential Receiver (RX) Input Characteristics

This table provides the differential receiver (RX) input characteristics for the SATA interface.

| Parameter                                        | Symbol                    | Min        | Typical | Мах        | Units | Notes |

|--------------------------------------------------|---------------------------|------------|---------|------------|-------|-------|

| RX Differential Input<br>Voltage<br>1.5G<br>3.0G | V <sub>SATA_RXDIFF</sub>  | 240<br>240 | 400     | 600<br>750 | mVp-p | 1     |

| RX rise/fall time<br>1.5G<br>3.0G                | t <sub>SATA_20-80RX</sub> | 100<br>67  |         | 273<br>136 | ps    | _     |

| RX Differential skew<br>1.5G<br>3.0G             | <sup>t</sup> sata_rxskew  | _          |         | 50         | ps    | _     |

| RX Differential pair<br>impedance<br>1.5G        |                           | 85         | _       | 115        | ohm   | _     |

| RX Single-Ended<br>impedance<br>1.5G             | Z <sub>SATA_RXSEIM</sub>  | 40         | _       | _          | ohm   | _     |

| DC Coupled<br>Common Mode<br>Voltage             | V <sub>dc_cm</sub>        | 200        | 250     | 450        | mV    | 5     |

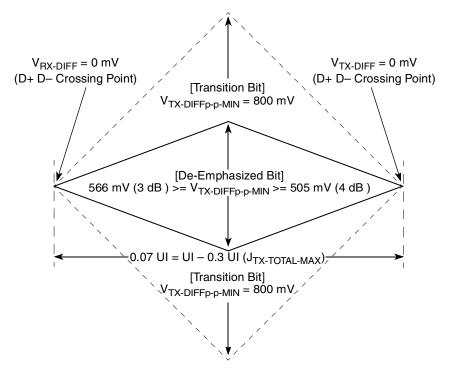

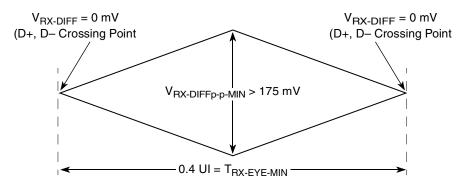

# 2.21.4.2 Transmitter Compliance Eye Diagrams

The TX eye diagram in Figure 69 is specified using the passive compliance/test measurement load (see Figure 71) in place of any real PCI Express interconnect + RX component.

There are two eye diagrams that must be met for the transmitter. Both eye diagrams must be aligned in time using the jitter median to locate the center of the eye diagram. The different eye diagrams will differ in voltage depending whether it is a transition bit or a de-emphasized bit. The exact reduced voltage level of the de-emphasized bit will always be relative to the transition bit.

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

### NOTE

It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function (that is, least squares and median deviation fits).

Figure 69. Minimum Transmitter Timing and Voltage Output Compliance Specifications

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

#### NOTE

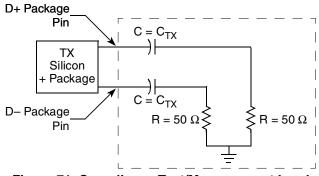

The reference impedance for return loss measurements is 50. to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50. probes—see Figure 71). Note that the series capacitors, CTX, are optional for the return loss measurement.

Figure 70. Minimum Receiver Eye Timing and Voltage Compliance Specification

# 2.22.1 Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in the following figure.

#### NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

Figure 71. Compliance Test/Measurement Load

# 2.23 Clocking

This section describes the PLL configuration of the chip. Note that the platform clock is identical to the core complex bus (CCB) clock.

| Characteristic                    | JEDEC Board             | Symbol                | Value | Unit | Notes |

|-----------------------------------|-------------------------|-----------------------|-------|------|-------|

| Junction-to-ambient (@200 ft/min) | Four layer board (2s2p) | $R_{	extsf{	heta}JA}$ | 14    | °C/W | 1, 2  |

| Junction-to-board thermal         | —                       | $R_{\theta JB}$       | 10    | °C/W | 3     |

| Junction-to-case thermal          | —                       | $R_{	extsf{	heta}JC}$ | < 0.1 | °C/W | 4     |

### Table 79. Package Thermal Characteristics (continued)

Notes

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 and JESD51-6 with the board (JESD51-9) horizontal.

- 3. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 4. Thermal resistance between the active surface of the die and the case top surface determined by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature. Actual thermal resistance is less than 0.1 •C/W

Simulations with heat sinks were done with the package mounted on the 2s2p thermal test board. The thermal interface material was a typical thermal grease such as Dow Corning 340 or Wakefield 120 grease. For system thermal modeling, the chip's thermal model without a lid is shown in Figure 72 The substrate is modeled as a block 29 x 29 x 1.2 mm with an in-plane conductivity of 19.8 W/m•K and a through-plane conductivity of 1.13 W/m•K. The solder balls and air are modeled as a single block 29 x 29 x 0.5 mm with an in-plane conductivity of 0.034 W/m•K and a through plane conductivity of 12.1 W/m•K. The die is modeled as 9.6 x 9.57 mm with a thickness of 0.75 mm. The bump/underfill layer is modeled as a collapsed thermal resistance between the die and substrate assuming a conductivity of 7.5 W/m•K in the thickness dimension of 0.07 mm. The die is centered on the substrate. The thermal model uses approximate dimensions to reduce grid. Please refer to the case outline for actual dimensions.

# 2.24.2 Recommended Thermal Model

This table shows the chip's thermal model.

| Conductivity  | Value                                   | Units                   |

|---------------|-----------------------------------------|-------------------------|

|               | Die (9.6x9.6 × 0.85 m                   | וויש<br>וm)             |

| Silicon       | Temperature dependent                   | —                       |

| Bump/Underfil | l (9.6 x 9.6 × 0.07 mm) Colla           | psed Thermal Resistance |

| Kz            | 7.5                                     | W/m•K                   |

|               | Substrate (29 × 29 × 1.2                | 2 mm)                   |

| Kx            | 19.8                                    | W/m•K                   |

| Ку            | 19.8                                    |                         |

| Kz            | 1.13                                    |                         |

|               | Solder and Air (29 $\times$ 29 $\times$ | 0.5 mm)                 |

| Kx            | 0.034                                   | W/m∙K                   |

| Ку            | 0.034                                   |                         |

| Kz            | 12.1                                    |                         |

### Table 80. Thermal Model