#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 800MHz                                                                  |

| Co-Processors/DSP               | Security; SEC                                                           |

| RAM Controllers                 | DDR2, DDR3                                                              |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (2)                                                     |

| SATA                            | SATA 3Gbps (2)                                                          |

| USB                             | USB 2.0 (3)                                                             |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | 0°C ~ 90°C (TA)                                                         |

| Security Features               | Cryptography                                                            |

| Package / Case                  | 783-BBGA, FCBGA                                                         |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8536eavjanga |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Pin Assignments and Reset States

|   | R                      | Т                            | U                             | V                            | W                             | Y                    | AA                            | AB                            | AC                            | AD                           | AE                                | AF                            | AG                         | AH                      |          |

|---|------------------------|------------------------------|-------------------------------|------------------------------|-------------------------------|----------------------|-------------------------------|-------------------------------|-------------------------------|------------------------------|-----------------------------------|-------------------------------|----------------------------|-------------------------|----------|

| V | MDQ<br>[59]            | AVDD_<br>SRDS2               | TSEC3_<br>RX_CLK              | TSEC3_<br>RXD<br>[3]         | TSEC1_<br>TX_EN               | TSEC1_<br>RXD<br>[1] | TSEC1_<br>RX_DV               | USB1_D<br>[0]                 | USB1_D<br>[2]                 | USB1_<br>CLK                 | USB1_D<br>[5]                     | USB1_D<br>[7]                 | USB1_<br>STP               | USB1_<br>DIR            | 1        |

|   | MDQ<br>[63]            | AGND_<br>SRDS2               | TSEC3_<br>RXD<br>[1]          | TSEC3_<br>RX_DV              | TSEC1_<br>GTX_CLK             | TSEC1_<br>RXD<br>[0] | TSEC1_<br>RXD<br>[3]          | USB1_D<br>[1]                 | USB1_D<br>[3]                 | USB1_D<br>[4]                | USB1_D<br>[6]                     | USB1_<br>NXT                  | OV <sub>DD</sub>           | USB1_<br>PWR-<br>FAULT  | 2        |

|   | GV <sub>DD</sub>       | SD2_<br>PLL_<br>TPA          | TSEC3_<br>RXD<br>[2]          | TSEC3_<br>RXD<br>[0]         | TSEC1_<br>TXD<br>[3]          | TSEC1_<br>RXD<br>[2] | TSEC1_<br>RX_CLK              | TSEC1_<br>RXD<br>[7]          | USB1_<br>PCTL0/<br>GPIO[6]    | USB2_D<br>[0]                | USB2_D<br>[1]                     | GND                           | USB3_D<br>[1]              | USB3_D<br>[0]           | 3        |

|   | Rvsd                   | TSEC3_<br>RX_ER              | GND                           | TV <sub>DD</sub>             | TSEC1_<br>TXD<br>[1]          | GND                  | LV <sub>DD</sub>              | TSEC1_<br>TX_CLK              | USB1_<br>PCTL1/<br>GPIO[7]    | OV <sub>DD</sub>             | USB2_D<br>[2]                     | USB2_D<br>[3]                 | USB3_D<br>[3]              | USB3_D<br>[2]           | 4        |

|   | Rvsd                   | TSEC3_<br>TXD<br>[1]         | TSEC3_<br>GTX_CLK             | TSEC3_<br>TX_EN              | TSEC1_<br>TXD<br>[2]          | TSEC1_<br>TXD<br>[4] | TSEC1_<br>TXD<br>[6]          | TSEC1_<br>TX_ER               | GND                           | USB2_<br>CLK                 | USB2_D<br>[4]                     | USB2_D<br>[5]                 | USB3_D<br>[4]              | USB3_<br>CLK            | 5        |

|   | S2V <sub>DD</sub>      | TSEC3_<br>TXD<br>[0]         | TSEC3_<br>RXD<br>[5]          | TSEC3_<br>RXD<br>[4]         | TSEC1_<br>TXD<br>[0]          | TSEC1_<br>RXD<br>[4] | EC_GTX_<br>CLK125             | TSEC1_<br>COL                 | USB2_D<br>[6]                 | DMA_<br>DACK[0]/<br>GPIO[10] | USB2_D<br>[7]                     | OV <sub>DD</sub>              | USB3_D<br>[6]              | USB3_D<br>[5]           | 6        |

|   | SD2_<br>IMP_CAL<br>_RX | TSEC3_<br>TXD<br>[2]         | TV <sub>DD</sub>              | GND                          | TSEC_<br>1588_TRIG<br>_IN[1]  | GND                  | LV <sub>DD</sub>              | TSEC1_<br>RXD<br>[6]          | USB2_<br>NXT                  | USB2_<br>STP                 | GND                               | USB2_<br>DIR                  | USB3_<br>NXT               | USB3_D<br>[7]           | 7        |

|   | NC                     | TSEC3_<br>TXD<br>[3]         | TSEC3_<br>TXD<br>[5]          | TSEC3_<br>TXD<br>[6]         | TSEC_<br>1588_TRIG<br>_IN[0]  | TSEC1_<br>TXD<br>[5] | TSEC1_<br>TXD<br>[7]          | TSEC1_<br>RXD<br>[5]          | USB2_<br>PWR-<br>FAULT        | SPI_<br>CLK                  | SDHC_<br>DAT[4]/SPI<br>_CS[0]     | SPI_<br>MOSI                  | USB3_<br>DIR               | USB3_<br>STP            | 8        |

|   | NC                     | TSEC3_<br>COL                | TSEC3_<br>TX_ER               | TSEC3_<br>TXD<br>[4]         | TSEC_<br>1588_<br>CLK         | TSEC1_<br>RX_ER      | TSEC1_<br>CRS                 | GND                           | USB2_<br>PCTL1/<br>GPIO[9]    | SPI_<br>MISO                 | GND                               | SDHC_<br>DAT[6]/SPI<br>_CS[2] | USB2_<br>PCTL0/<br>GPIO[8] | Rsvd                    | 9        |

|   | NC                     | TSEC3_<br>CRS                | TSEC3_<br>TX_CLK              | TSEC_<br>1588_CLK<br>_OUT    | TSEC_<br>1588_TRIG<br>_OUT[1] | EC_<br>MDC           | SDHC_<br>DAT[7]/SPI<br>_CS[3] | DMA_<br>DREQ[0]/<br>GPIO[14]  | SDHC_<br>DAT[5]/SPI<br>_CS[1] | ov <sub>DD</sub>             | DMA_<br>DACK[1]/<br>GPIO[11]      | UART_<br>SOUT<br>[0]          | SDHC_<br>WP/GPIO<br>[5]    | SDHC_<br>CMD            | 10       |

|   | X2V <sub>DD</sub>      | TSEC_<br>1588_PULSE<br>_OUT2 | TSEC_<br>1588_TRIG<br>_OUT[0] | TSEC_<br>1588_PULSE<br>_OUT1 | MSRCID<br>[4]                 | EC_<br>MDIO          | DMA_<br>DDONE[0]/<br>GPIO[12] | DMA_<br>DDONE[1]/<br>GPI0[13] | GND                           | DMA_<br>DREQ[1]/<br>GPIO[15] | UART_<br>CTS<br>[0]               | OV <sub>DD</sub>              | SDHC_<br>DAT<br>[3]        | SDHC_<br>CD/GPIO<br>[4] | 11       |

|   | X2GND                  | TSEC3_<br>TXD<br>[7]         | TSEC3_<br>RXD<br>[7]          | MSRCID<br>[2]                | MSRCID<br>[0]                 | UART_<br>CTS<br>[1]  | UART_<br>SOUT<br>[1]          | UART_<br>RTS<br>[0]           | UART_<br>SIN<br>[0]           | UART_<br>RTS<br>[1]          | GND                               | UART_<br>SIN<br>[1]           | SDHC_<br>DAT<br>[0]        | SDHC_<br>DAT<br>[1]     | 12       |

|   | GND                    | VDD_<br>CORE                 | TSEC3_<br>RXD<br>[6]          | MDVAL                        | MSRCID<br>[1]                 | GND                  | TEST_<br>SEL                  | OV <sub>DD</sub>              | DDRCLK                        | IRQ[10]/<br>DMA_<br>DACK[3]  | <u>IRQ[9]/</u><br>DMA_<br>DREQ[3] | PCI1_<br>REQ<br>[2]           | SDHC_<br>CLK               | SDHC_<br>DAT<br>[2]     | 13       |

|   | VDD_<br>CORE           | GND                          | VDD_<br>CORE                  | GND                          | MSRCID<br>[3]                 | MCP                  | GND                           | UDE                           | PCI1_GNT<br>[4]/GPIO<br>[3]   | IRQ[11]/<br>DMA_<br>DDONE[3] | OV <sub>DD</sub>                  | PCI1_<br>GNT<br>[2]           | IIC2_<br>SDA               | SYSCLK                  | 14       |

|   |                        |                              |                               |                              |                               |                      | DETA                          | AIL B                         |                               |                              |                                   |                               |                            | Z                       | <u>ל</u> |

Figure 4. Chip Pin Map Detail B

#### **Pin Assignments and Reset States**

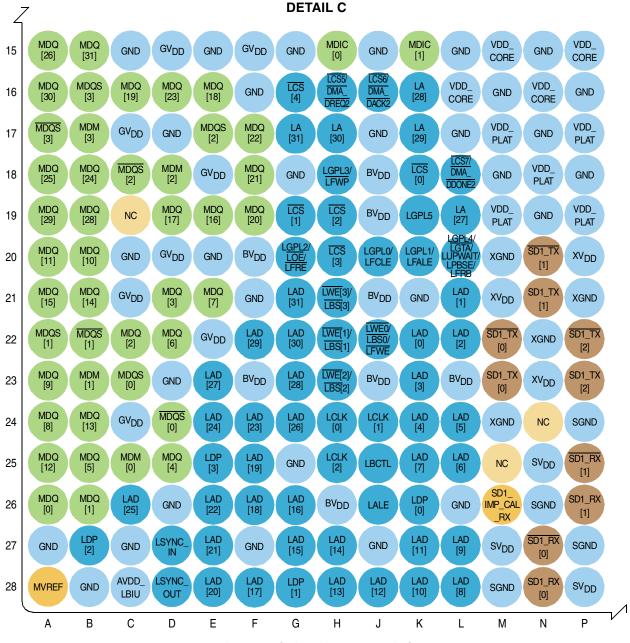

Figure 5. Chip Pin Map Detail C

#### **Pin Assignments and Reset States**

| Signal    | Signal Name                          | Package Pin Number                                                                                                                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes |

|-----------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

|           | DDR SDRAM                            | Memory Interface                                                                                                                                                                                                                                                        |          |                  |       |

| MDQ[0:63] | Data                                 | A26,B26,C22,D21,D25,<br>B25,D22,E21,A24,A23,<br>B20,A20,A25,B24,B21,<br>A21,E19,D19,E16,C16,<br>F19,F18,F17,D16,B18,<br>A18,A15,B14,B19,A19,<br>A16,B15,D1,F3,G1,H2,<br>E4,G5,H3,J4,B2,C3,F2,<br>G2,A2,B3,E1,F1,L5,L4,<br>N3,P3,J3,K4,N4,P4,J1,<br>K1,P1,R1,J2,K2,P2,R2 | I/O      | GV <sub>DD</sub> | _     |

| MECC[0:7] | Error Correcting Code                | G12,D14,F11,C11,<br>G14,F14,C13,D12                                                                                                                                                                                                                                     | I/O      | GV <sub>DD</sub> | _     |

| MAPAR_ERR | Address Parity Error                 | A13                                                                                                                                                                                                                                                                     | I        | GV <sub>DD</sub> | _     |

| MAPAR_OUT | Address Parity Out                   | A6                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

| MDM[0:8]  | Data Mask                            | C25,B23,D18,B17,G4,<br>C2,L3,L2,F13                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _     |

| MDQS[0:8] | Data Strobe                          | D24,B22,C18,A17,J5,<br>C1,M4,M2,E13                                                                                                                                                                                                                                     | I/O      | GV <sub>DD</sub> | —     |

| MDQS[0:8] | Data Strobe                          | C23,A22,E17,B16,K5,<br>D2,M3,N1,D13                                                                                                                                                                                                                                     | I/O      | GV <sub>DD</sub> | —     |

| MA[0:15]  | Address                              | B7,G8,C8,A10,D9,C10,<br>A11,F9,E9,B12,A5,<br>A12,D11,F7,E10,F10                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | _     |

| MBA[0:2]  | Bank Select                          | A4,B5,B13                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | —     |

| MWE       | Write Enable                         | B4                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

| MRAS      | Row Address Strobe                   | C5                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

| MCAS      | Column Address Strobe                | E7                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

| MCS[0:3]  | Chip Select                          | D3,H6,C4,G6                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | —     |

| MCKE[0:3] | Clock Enable                         | H10,K10,G10,H9                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | 11    |

| MCK[0:5]  | Differential Clock 3 Pairs /<br>DIMM | A9,J11,J6,A8,J13,H8                                                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _     |

| MCK[0:5]  | Differential Clock 3 Pairs /<br>DIMM | B9,H11,K6,B8,H13,J8 O GV <sub>DD</sub>                                                                                                                                                                                                                                  |          | GV <sub>DD</sub> | —     |

| MODT[0:3] | On Die Termination                   | E5,H7,E6,F6                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | -     |

| MDIC[0:1] | Calibration                          | H15,K15                                                                                                                                                                                                                                                                 | I/O      | GV <sub>DD</sub> | 26    |

|           | Local Bus C                          | ontroller Interface                                                                                                                                                                                                                                                     |          |                  |       |

#### Table 1. Pinout Listing (continued)

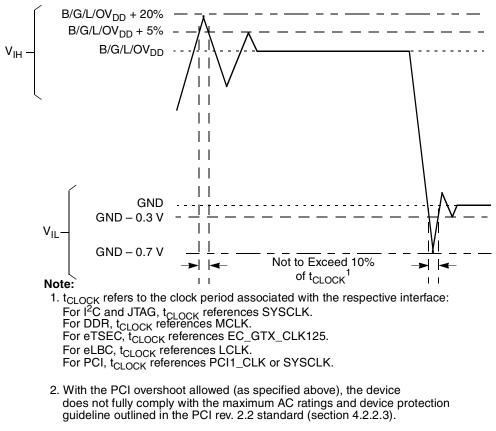

This figure shows the undershoot and overshoot voltages at the interfaces of the chip.

#### Figure 7. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>/LV<sub>DD</sub>

The core voltage must always be provided at nominal 1.0 V. (See Table 3 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 3. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR2 and DDR3 SDRAM interface uses differential receivers referenced by the externally supplied MVREF*n* signal (nominally set to GVDD/2) as is appropriate for the SSTL\_1.8 electrical signaling standard for DDR2 or 1.5-V electrical signaling for DDR3. The DDR DQS receivers cannot be operated in single-ended fashion. The complement signal must be properly driven and cannot be grounded.

| Power Mode        | Core<br>Frequen<br>cy | CCB<br>Frequen<br>cy | DDR<br>Frequen<br>cy | V <sub>DD</sub><br>Platfor<br>m | V <sub>DD</sub><br>Core | Junction<br>Tempera<br>ture | Core              | Power   | Platform          | ı Power <sup>9</sup> | Notes   |

|-------------------|-----------------------|----------------------|----------------------|---------------------------------|-------------------------|-----------------------------|-------------------|---------|-------------------|----------------------|---------|

|                   | (MHz)                 | (MHz)                | (MHz)                | (V)                             | (V)                     | (°C)                        | mean <sup>7</sup> | Мах     | mean <sup>7</sup> | Max                  |         |

| Maximum (A)       |                       |                      |                      |                                 |                         | 105                         |                   | 5.3/4.4 | _                 | 5.0/4.0              | 1, 3, 8 |

| Thermal (W)       | 1250                  | 500                  | 500                  | 1.0                             | 1.0                     | / 90                        |                   | 4.4/3.6 | _                 | 5.0/4.0              | 1, 4, 8 |

| Typical (W)       |                       |                      |                      |                                 |                         | 65                          | 2.2               |         | 1.7               |                      | 1       |

| Doze (W)          |                       |                      |                      |                                 |                         |                             | 1.6               | 2.4     | 1.5               | 2.1                  | 1       |

| Nap (W)           |                       |                      |                      |                                 |                         |                             | 0.8               | 1.6     | 1.5               | 2.1                  | 1       |

| Sleep (W)         |                       |                      |                      |                                 |                         |                             | 0.8               | 1.6     | 1.1               | 1.7                  | 1       |

| Deep Sleep<br>(W) |                       |                      |                      |                                 |                         | 35                          | 0                 | 0       | 0.6               | 1.2                  | 1, 6    |

#### Table 5. Power Dissipation (continued)<sup>5</sup>

#### Notes:

1. These values specify the power consumption at nominal voltage and apply to all valid processor bus frequencies and configurations. The values do not include power dissipation for I/O supplies.

- Typical power is an average value measured at the nominal recommended core voltage (V<sub>DD</sub>) and 65°C junction temperature (see Table 3) while running the Dhrystone benchmark.

- 3. Maximum power is the maximum power measured with the worst process and recommended core and platform voltage (V<sub>DD</sub>) at maximum operating junction temperature (see Table 3) while running a smoke test which includes an entirely L1-cache-resident, contrived sequence of instructions which keep the execution unit maximally busy.

- 4. Thermal power is the maximum power measured with worst case process and recommended core and platform voltage (V<sub>DD</sub>) at maximum operating junction temperature (see Table 3) while running the Dhrystone benchmark.

- 6. Maximum power is the maximum number measured with USB1, eTSEC1, and DDR blocks enabled. The Mean power is the mean power measured with only external interrupts enabled and DDR in self refresh.

- 7. Mean power is provided for information purposes only and is the mean power consumed by a statistically significant range of devices.

- 8. Maximum operating junction temperature (see Table 3) for Commercial Tier is 90 <sup>0</sup>C, for Industrial Tier is 105 <sup>0</sup>C.

- 9. Platform power is the power supplied to all the  $V_{DD}\ _{PLAT}$  pins.

See Section 2.23.6.1, "SYSCLK to Platform Frequency Options," for the full range of CCB frequencies that the chip supports.

### 2.4.6 Platform to FIFO Restrictions

Please note the following FIFO maximum speed restrictions based on platform speed. The "platform clock (CCB) frequency" in the following formula refers to the maximum platform (CCB) frequency of the speed bins the part belongs to, which is defined in Table 73.

For FIFO GMII mode:

FIFO TX/RX clock frequency <= platform clock frequency/3.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz

For FIFO encoded mode:

FIFO TX/RX clock frequency <= platform clock frequency/3.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency should be no more than 167 MHz

### 2.4.7 Other Input Clocks

For information on the input clocks of other functional blocks of the platform such as SerDes, and eTSEC, see the specific section of this document.

## 2.5 **RESET** Initialization

This section describes the AC electrical specifications for the RESET initialization timing requirements of the chip. This table provides the RESET initialization AC timing specifications for the DDR SDRAM component(s).

| Parameter/Condition                                                                                            | Min | Max | Unit    | Notes |

|----------------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HREST                                                                               | 100 |     | μs      | —     |

| Minimum assertion time for SRESET                                                                              | 3   |     | Sysclk  | 1     |

| PLL input setup time with stable SYSCLK before HRESET negation                                                 | 100 | —   | μs      | —     |

| Input setup time for POR configurations (other than PLL config) with respect to negation of HRESET             | 4   | —   | SYSCLKs | 1     |

| Input hold time for all POR configurations (including PLL config) with respect to negation of HRESET           | 2   | —   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively driven POR configurations with respect to negation of HRESET | _   | 5   | SYSCLKs | 1     |

| HRESET rise time                                                                                               | _   | 1   | SYSCLK  | -     |

Table 10. RESET Initialization Timing Specifications

Notes:

1. SYSCLK is the primary clock input for the chip.

This table provides the PLL lock times.

Table 11. PLL Lock Times

| Parameter/Condition | Min | Max | Unit | Notes |

|---------------------|-----|-----|------|-------|

| PLL lock times      | —   | 100 | μs   | —     |

| Local bus PLL       | —   | 50  | μs   | —     |

| PCI bus lock time   | —   | 50  | μs   | —     |

### 2.9.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps) — FIFO/GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics

The electrical characteristics specified here apply to all FIFO mode, gigabit media independent interface (GMII), media independent interface (MII), ten-bit interface (TBI), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), and reduced media independent interface (RMII) signals except management data input/output (MDIO) and management data clock (MDC), and serial gigabit media independent interface (SGMII). The RGMII, RTBI and FIFO mode interfaces are defined for 2.5 V, while the GMII, MII, RMII, and TBI interfaces can operate at 3.3V.

The GMII, MII, or TBI interface timing is compliant with IEEE 802.3. The RGMII and RTBI interfaces follow the Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3 (12/10/2000). The RMII interface follows the RMII Consortium RMII Specification Version 1.2 (3/20/1998).

The electrical characteristics for MDIO and MDC are specified in Section 2.10, "Ethernet Management Interface Electrical Characteristics."

The electrical characteristics for SGMII is specified in Section 2.9.3, "SGMII Interface Electrical Characteristics." The SGMII interface conforms (with exceptions) to the Serial-GMII Specification Version 1.8.

### 2.9.1.1 GMII, MII, TBI, RGMII, RMII and RTBI DC Electrical Characteristics

All GMII, MII, TBI, RGMII, RMII and RTBI drivers and receivers comply with the DC parametric attributes specified in the following tables. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter                                                                                        | Symbol                               | Min  | Мах                                      | Unit | Notes  |

|--------------------------------------------------------------------------------------------------|--------------------------------------|------|------------------------------------------|------|--------|

| Supply voltage 3.3 V                                                                             | LV <sub>DD</sub><br>TV <sub>DD</sub> | 3.13 | 3.47                                     | V    | 1, 2   |

| Output high voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, IOH = -4.0 mA)                 | VOH                                  | 2.40 | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | —      |

| Output low voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, IOL = 4.0 mA)                   | VOL                                  | GND  | 0.50                                     | V    | —      |

| Input high voltage                                                                               | V <sub>IH</sub>                      | 1.90 | $LV_{DD}/TV_{DD} + 0.3$                  | V    | —      |

| Input low voltage                                                                                | V <sub>IL</sub>                      | -0.3 | 0.90                                     | V    | —      |

| Input high current<br>(V <sub>IN</sub> = LV <sub>DD</sub> , V <sub>IN</sub> = TV <sub>DD</sub> ) | IIH                                  | _    | 40                                       | μΑ   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                                                     | IIL                                  | -600 | —                                        | μA   | 3      |

Table 24. GMII, MII, RMII, and TBI DC Electrical Characteristics

#### Notes:

<sup>1</sup> LV<sub>DD</sub> supports eTSECs 1.

<sup>2</sup> TV<sub>DD</sub> supports eTSECs 3.

$^{3}$  The symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

| Parameters                                                                                        | Symbol                             | Min       | Мах                                      | Unit | Notes  |

|---------------------------------------------------------------------------------------------------|------------------------------------|-----------|------------------------------------------|------|--------|

| Supply voltage 2.5 V                                                                              | LV <sub>DD</sub> /TV <sub>DD</sub> | 2.37      | 2.63                                     | V    | 1,2    |

| Output high voltage<br>(LV <sub>DD</sub> /TV <sub>DD</sub> = Min, IOH = -1.0 mA)                  | V <sub>OH</sub>                    | 2.00      | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | _      |

| Output low voltage<br>(LV <sub>DD</sub> / <u>TV<sub>DD</sub></u> = Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>                    | GND – 0.3 | 0.40                                     | V    | —      |

| Input high voltage                                                                                | V <sub>IH</sub>                    | 1.70      | $LV_{DD}/TV_{DD} + 0.3$                  | V    | —      |

| Input low voltage                                                                                 | V <sub>IL</sub>                    | -0.3      | 0.70                                     | V    | —      |

| Input high current<br>(V <sub>IN</sub> = LV <sub>DD</sub> , V <sub>IN</sub> = TV <sub>DD</sub> )  | IIH                                | _         | 10                                       | μΑ   | 1, 2,3 |

| Input low current<br>(V <sub>IN</sub> = GND)                                                      | Ι <sub>ΙL</sub>                    | -15       |                                          | μA   | 3      |

#### Table 25. RGMII, RTBI, and FIFO DC Electrical Characteristics

Note:

<sup>1</sup> LV<sub>DD</sub> supports eTSECs 1.

$^2$  TV<sub>DD</sub> supports eTSECs 3.

<sup>3</sup> Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

### 2.9.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI are presented in this section.

### 2.9.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, since they have similar performance and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back out onto the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source-synchronous timing reference. Typically, the clock edge that launched the data can be used, since the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is relationship between the maximum FIFO speed and the platform speed. For more information see Section 2.4.6, "Platform to FIFO Restrictions."

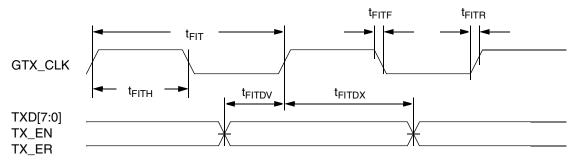

A summary of the FIFO AC specifications appears in the following tables.

#### Table 26. FIFO Mode Transmit AC Timing Specification

| Parameter/Condition                       | Symbol            | Min | Тур | Max | Unit |

|-------------------------------------------|-------------------|-----|-----|-----|------|

| TX_CLK, GTX_CLK clock period <sup>2</sup> | t <sub>FIT</sub>  | 6.0 | 8.0 | 100 | ns   |

| TX_CLK, GTX_CLK duty cycle                | t <sub>FITH</sub> | 45  | 50  | 55  | %    |

| TX_CLK, GTX_CLK peak-to-peak jitter       | t <sub>FITJ</sub> | _   | —   | 250 | ps   |

| Parameter/Condition                                   | Symbol               | Min | Тур | Max  | Unit |

|-------------------------------------------------------|----------------------|-----|-----|------|------|

| Rise time TX_CLK (20%–80%)                            | t <sub>FITR</sub>    | _   | —   | 0.75 | ns   |

| Fall time TX_CLK (80%–20%)                            | t <sub>FITF</sub>    | _   | —   | 0.75 | ns   |

| GTX_CLK to FIFO data TXD[7:0], TX_ER, TX_EN hold time | t <sub>FITDX</sub> 1 | 0.5 | —   | 3.0  | ns   |

#### Table 26. FIFO Mode Transmit AC Timing Specification (continued)

#### Note:

1. Data valid tFITDV to GTX\_CLK Min Setup time is a function of clock period and max hold time. (Min Setup = Cycle time – Max Hold)

2. The minimum cycle period (or maximum frequency) of the RX\_CLK is dependent on the maximum platform frequency of the speed bins the part belongs to as well as the FIFO mode under operation. See Section 2.4.6, "Platform to FIFO Restrictions," for more detailed description.

| Parameter/Condition                         | Symbol                               | Min | Тур | Мах  | Unit |

|---------------------------------------------|--------------------------------------|-----|-----|------|------|

| RX_CLK clock period <sup>1</sup>            | t <sub>FIR</sub>                     | 6.0 | 8.0 | 100  | ns   |

| RX_CLK duty cycle                           | t <sub>FIRH</sub> /t <sub>FIRH</sub> | 45  | 50  | 55   | %    |

| RX_CLK peak-to-peak jitter                  | t <sub>FIRJ</sub>                    |     | —   | 250  | ps   |

| Rise time RX_CLK (20%–80%)                  | t <sub>FIRR</sub>                    | _   | —   | 0.75 | ns   |

| Fall time RX_CLK (80%–20%)                  | t <sub>FIRF</sub>                    | _   |     | 0.75 | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>FIRDV</sub>                   | 1.5 | —   | —    | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>FIRDX</sub>                   | 0.5 | —   | —    | ns   |

#### Table 27. FIFO Mode Receive AC Timing Specification

#### Note:

1. The minimum cycle period (or maximum frequency) of the RX\_CLK is dependent on the maximum platform frequency of the speed bins the part belongs to as well as the FIFO mode under operation. See Section 2.4.6, "Platform to FIFO Restrictions," for more detailed description.

Timing diagrams for FIFO appear in the following figures.

Figure 14. FIFO Transmit AC Timing Diagram

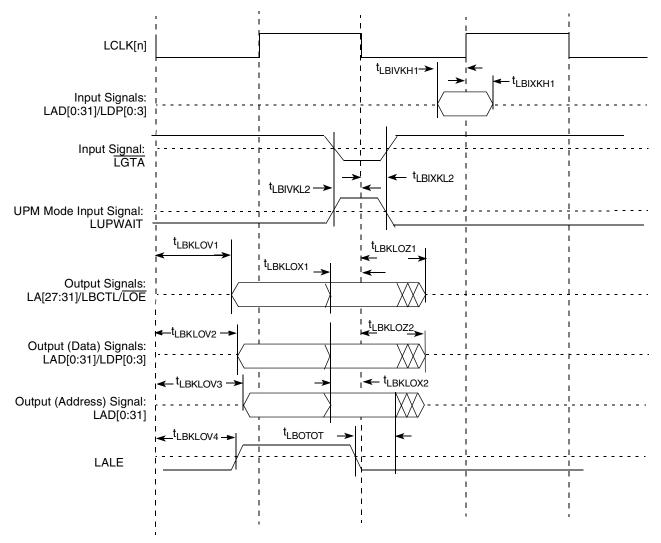

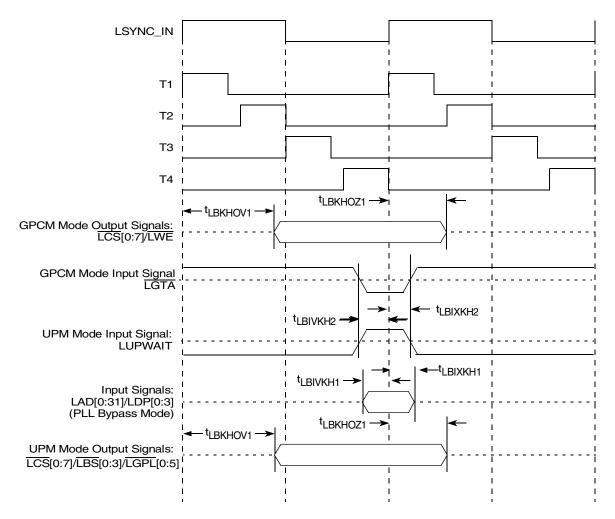

| Parameter                                                          | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|--------------------------------------------------------------------|----------------------|-----|-----|------|-------|

| Output hold from local bus clock for LAD/LDP                       | t <sub>LBKHOX2</sub> | 0.7 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) | t <sub>LBKHOZ1</sub> | —   | 2.5 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP               | t <sub>LBKHOZ2</sub> |     | 2.5 | ns   | 5     |

Table 51. Local Bus General Timing Parameters (BV<sub>DD</sub> = 3.3 V DC) (continued)

Note:

- The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6.t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. tLBOTOT is guaranteed with LBCR[AHD] = 0.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BVDD/2.

This table describes the general timing parameters of the local bus interface at  $BV_{DD} = 2.5 \text{ V DC}$ .

| Parameter                                                                       | Configuration | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|---------------------------------------------------------------------------------|---------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | —             | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | —             | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | —             | <b>t</b> LBKSKEW                    | —   | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | —             | t <sub>LBIVKH1</sub>                | 1.9 | _   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | —             | t <sub>LBIVKH2</sub>                | 1.8 | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | —             | t <sub>LBIXKH1</sub>                | 1.1 | _   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | —             | t <sub>LBIXKH2</sub>                | 1.1 | _   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | —             | t <sub>LBOTOT</sub>                 | 1.5 |     | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | —             | t <sub>LBKHOV1</sub>                |     | 2.4 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                                       | —             | t <sub>LBKHOV2</sub>                | _   | 2.5 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | —             | t <sub>LBKHOV3</sub>                | _   | 2.4 | ns   | 3     |

| Local bus clock to LALE assertion                                               | _             | t <sub>LBKHOV4</sub>                | _   | 2.4 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | _             | t <sub>LBKHOX1</sub>                | 0.8 | _   | ns   | 3     |

Table 52. Local Bus General Timing Parameters (BV<sub>DD</sub> = 2.5 V DC)

#### Figure 40. Local Bus Signals (PLL Bypass Mode)

This table describes the general timing parameters of the local bus interface at  $V_{DD} = 3.3$  V DC with PLL disabled.

Table 54. Local Bus General Timing Parameters—PLL Bypassed

| Parameter                                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 12   |     | ns   | 2     |

| Local bus duty cycle                                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | _     |

| Input setup to local bus clock (except LUPWAIT)                       | t <sub>LBIVKH1</sub>                | 5.1  | —   | ns   | 4, 5  |

| LUPWAIT input setup to local bus clock                                | t <sub>LBIVKL2</sub>                | 4.2  | —   | ns   | 4, 5  |

| Input hold from local bus clock (except LUPWAIT)                      | t <sub>LBIXKH1</sub>                | -1.4 | —   | ns   | 4, 5  |

| LUPWAIT input hold from local bus clock                               | t <sub>LBIXKL2</sub>                | -2.0 | —   | ns   | 4, 5  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.4  | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKLOV1</sub>                | _    | 0.5 | ns   | 4     |

Figure 42. Local Bus Signals, GPCM/UPM Signals for LCRR[CLKDIV] = 8 or 16(PLL Enabled)

### 2.13 Enhanced Secure Digital Host Controller (eSDHC)

This section describes the DC and AC electrical specifications for the eSDHC interface of the chip.

### 2.13.1 eSDHC DC Electrical Characteristics

This table provides the DC electrical characteristics for the eSDHC interface of the chip.

#### Table 55. eSDHC interface DC Electrical Characteristics

At recommended operating conditions (see Table 3)

| Characteristic               | Symbol                           | Condition                          | Min          | Max         | Unit | Notes |

|------------------------------|----------------------------------|------------------------------------|--------------|-------------|------|-------|

| Input high voltage           | V <sub>IH</sub>                  | —                                  | 0.625 * OVDD | OVDD+0.3    | V    | _     |

| Input low voltage            | V <sub>IL</sub>                  | —                                  | -0.3         | 0.25 * OVDD | V    | _     |

| Input/Output leakage current | I <sub>IN</sub> /I <sub>OZ</sub> | —                                  | -10          | 10          | uA   |       |

| Output high voltage          | V <sub>OH</sub>                  | I <sub>OH</sub> = -100 uA @OVDDmin | 0.75 * OVDD  | _           | V    | _     |

| Parameter                                                                                                | Symbol                    | Min       | Typical | Мах            | Units | Notes   |

|----------------------------------------------------------------------------------------------------------|---------------------------|-----------|---------|----------------|-------|---------|

| RX Differential Mode<br>Return loss<br>150 MHz - 300 MHz<br>300 MHz - 600 MHz<br>600 MHz - 1.2 GHz       | RL <sub>SATA_RXDD11</sub> |           | <br>    | 18<br>14<br>10 | dB    | 2, 3    |

| 1.2 GHz - 2.4 GHz<br>2.4 GHz - 3.0 GHz<br>3.0 GHz - 5.0 GHz                                              |                           | <br><br>_ |         | 8<br>3<br>1    |       |         |

| RX Common Mode<br>Return loss<br>150 MHz - 300 MHz<br>300 MHz - 600 MHz<br>600 MHz - 1.2 GHz             | RL <sub>SATA_RXCC11</sub> | <br><br>  |         | 5<br>5<br>2    | dB    | 2, 3, 4 |

| 1.2 GHz - 2.4 GHz<br>2.4 GHz - 3.0 GHz<br>3.0 GHz - 5.0 GHz                                              |                           | <br><br>  |         | 2<br>2<br>1    |       |         |

| RX Impedance Balance<br>150 MHz - 300 MHz<br>300 MHz - 600 MHz<br>600 MHz - 1.2 GHz<br>1.2 GHz - 2.4 GHz | RL <sub>SATA_RXDC11</sub> | <br>      |         | 30<br>30<br>20 | dB    | 2, 3    |

| 2.4 GHz - 3.0 GHz<br>3.0 GHz - 5.0 GHz                                                                   |                           |           |         | 10<br>4<br>4   |       |         |

| Deterministic jitter<br>1.5G<br>3.0G                                                                     | U <sub>SATA_RXDJ</sub>    | _         | _       | 0.4<br>0.47    | UI    | _       |

| Total Jitter<br>1.5G<br>3.0G                                                                             | U <sub>SATA_RXTJ</sub>    | _         | _       | 0.65<br>0.65   | UI    | _       |

Table 61. Differential Receiver (RX) Input Characteristics (continued)

Notes:

1. The min values apply only to Gen1m, and Gen2m. the min values for Gen1i is 325 mVp-p and for Gen2i is 275 mVp-p.

2. Only applies when operating in 3.0Gb data rate mode.

3. The max value stated for 3.0 GHz - 5.0 GHz range only applies to Gen2i mode and not to Gen2m mode.

4. The max value stated for 2.4 GHz - 3.0 GHz range only applies to Gen2i mode for Gen2m the value is 1.

5. Only applies to Gen1i mode.

## 2.16.4 Out-of-Band (OOB) Electrical Characteristics

This table provides the Out-of-Band (OOB) electrical characteristics for the SATA interface of the chip.

| Table 62. Out-of-Band (OOB) Electrical Characteristics |  |

|--------------------------------------------------------|--|

|--------------------------------------------------------|--|

| Parameter                                              | Symbol                               | Min      | Typical    | Max        | Units | Notes |

|--------------------------------------------------------|--------------------------------------|----------|------------|------------|-------|-------|

| OOB Signal Detection Threshold<br>1.5G                 |                                      |          |            |            |       | _     |

| 3.0G                                                   | V <sub>SATA_OOBDETE</sub>            | 50<br>75 | 100<br>125 | 200<br>200 | mVp-p |       |

| UI During OOB Signaling                                | T <sub>SATA_UIOOB</sub>              | 646.67   | 666.67     | 686.67     | ps    | -     |

| COMINIT/ COMRESET and COMWAKE<br>Transmit Burst Length | T <sub>SATA_UIOOBTXB</sub>           | _        | 160        | _          | UI    | _     |

| COMINIT/ COMRESET Transmit Gap Length                  | T <sub>SATA_UIOOBTXG</sub><br>ap     | _        | 480        | _          | UI    | _     |

| COMWAKE Transmit Gap Length                            | T <sub>SATA_UIOOBTX</sub><br>WakeGap | _        | 160        |            | UI    | —     |

| COMWAKE Gap Detection Windows                          | T <sub>SATA_</sub> OOBDet<br>WakeGap | 55       | —          | 175        | ns    | —     |

| COMINIT/ COMRESET<br>Gap Detection Windows             | T <sub>SATA_OOBDet</sub><br>COMGap   | 175      |            | 525        | ns    |       |

# 2.17 l<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the chip.

# 2.17.1 I<sup>2</sup>C DC Electrical Characteristics

This table provides the DC electrical characteristics for the  $I^2C$  interfaces.

### Table 63. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $OV_{DD}$  of 3.3 V ± 5%.

| Parameter                | Symbol           | Min                 | Max                               | Unit | Notes |

|--------------------------|------------------|---------------------|-----------------------------------|------|-------|

| Supply voltage 3.3 V     | OV <sub>DD</sub> | 3.13                | 3.47                              | V    |       |

| Input high voltage level | V <sub>IH</sub>  | $0.7 	imes OV_{DD}$ | OV <sub>DD</sub> + 0.3            | V    | _     |

| Input low voltage level  | V <sub>IL</sub>  | -0.3                | $0.3\times\text{OV}_{\text{DD}}$  | V    | _     |

| Low level output voltage | V <sub>OL</sub>  | 0                   | $0.2\times \text{OV}_{\text{DD}}$ | V    | 1     |

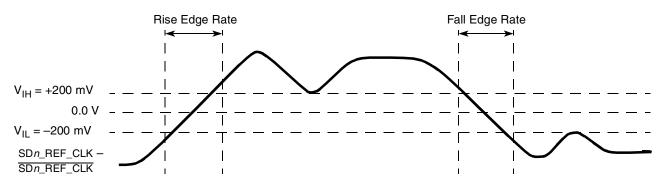

### 2.20.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100KHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15MHz is filtered by the PLL. The most problematic phase noise occurs in the 1-15MHz range. The source impedance of the clock driver should be 50 ohms to match the transmission line and reduce reflections which are a source of noise to the system.

This table describes some AC parameters common to SGMII and PCI Express protocols.

#### Table 69. SerDes Reference Clock Common AC Parameters

At recommended operating conditions with  $XV_{DD_SRDS1}$  or  $XV_{DD_SRDS2} = 1.0V \pm 5\%$ .

| Parameter                                                                  | Symbol                | Min  | Max  | Unit | Notes |

|----------------------------------------------------------------------------|-----------------------|------|------|------|-------|

| Rising Edge Rate                                                           | Rise Edge Rate        | 1.0  | 4.0  | V/ns | 2, 3  |

| Falling Edge Rate                                                          | Fall Edge Rate        | 1.0  | 4.0  | V/ns | 2, 3  |

| Differential Input High Voltage                                            | V <sub>IH</sub>       | +200 | —    | mV   | 2     |

| Differential Input Low Voltage                                             | V <sub>IL</sub>       | _    | -200 | mV   | 2     |

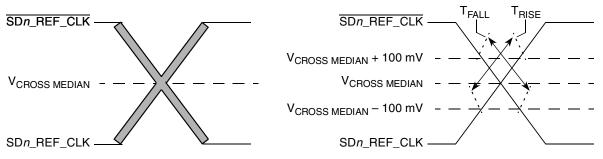

| Rising edge rate (SDn_REF_CLK) to falling edge rate (SDn_REF_CLK) matching | Rise-Fall<br>Matching | —    | 20   | %    | 1, 4  |

Notes:

- 1. Measurement taken from single ended waveform.

- 2. Measurement taken from differential waveform.

- 3. Measured from -200 mV to +200 mV on the differential waveform (derived from SDn\_REF\_CLK minus SDn\_REF\_CLK). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV measurement window is centered on the differential zero crossing. See Figure 66.

- 4. Matching applies to rising edge rate for SDn\_REF\_CLK and falling edge rate for SDn\_REF\_CLK. It is measured using a 200 mV window centered on the median cross point where SDn\_REF\_CLK rising meets SDn\_REF\_CLK falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The Rise Edge Rate of SDn\_REF\_CLK should be compared to the Fall Edge Rate of SDn\_REF\_CLK, the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 67.

Figure 66. Differential Measurement Points for Rise and Fall Time

Figure 67. Single-Ended Measurement Points for Rise and Fall Time Matching

The other detailed AC requirements of the SerDes Reference Clocks is defined by each interface protocol based on application usage. See the following sections for detailed information:

- Section 2.9.3.2, "AC Requirements for SGMII SD2\_REF\_CLK and SD2\_REF\_CLK"

- Section 2.21.2, "AC Requirements for PCI Express SerDes Clocks"

#### 2.20.2.4.1 Spread Spectrum Clock

SD1\_REF\_CLK/SD1\_REF\_CLK were designed to work with a spread spectrum clock (+0 to -0.5% spreading at 30–33 kHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation should be used.

SD2\_REF\_CLK/SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

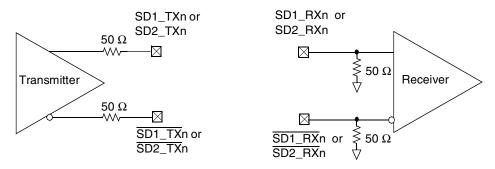

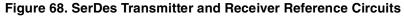

### 2.20.3 SerDes Transmitter and Receiver Reference Circuits

This figure shows the reference circuits for SerDes data lane's transmitter and receiver.

The DC and AC specification of SerDes data lanes are defined in each interface protocol section below (PCI Express, SATA or SGMII) in this document based on the application usage:

- Section 2.9.3, "SGMII Interface Electrical Characteristics"

- Section 2.21, "PCI Express"

- Section 2.16, "Serial ATA (SATA)"

Please note that external AC Coupling capacitor is required for the above three serial transmission protocols with the capacitor value defined in specification of each protocol section.

| Symbol               | Parameter  | Min | Nom | Max | Units | Comments                                                                                                                                                                                                                          |

|----------------------|------------|-----|-----|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L <sub>TX-SKEW</sub> | Total Skew |     |     | 20  | ns    | Skew across all lanes on a Link. This includes<br>variation in the length of SKP ordered set (for<br>example, COM and one to five Symbols) at<br>the RX as well as any delay differences<br>arising from the interconnect itself. |

Table 72. Differential Receiver (RX) Input Specifications (continued)

#### Notes:

- 1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point and measured over any 250 consecutive UIs. The test load in Figure 71 should be used as the RX device when taking measurements (also refer to the Receiver compliance eye diagram shown in Figure 70). If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as a reference for the eye diagram.

- 3. A T<sub>RX-EYE</sub> = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the Transmitter and interconnect collected any 250 consecutive UIs. The T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total. UI jitter budget collected over any 250 consecutive TX UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as the reference for the eye diagram.

- 4. The Receiver input impedance shall result in a differential return loss greater than or equal to 15 dB with the D+ line biased to 300 mV and the D- line biased to -300 mV and a common mode return loss greater than or equal to 6 dB (no bias required) over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements for is 50 ohms to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50 ohm probes see Figure 71). Note: that the series capacitors CTX is optional for the return loss measurement.

- 5. Impedance during all LTSSM states. When transitioning from a Fundamental Reset to Detect (the initial state of the LTSSM) there is a 5 ms transition time before Receiver termination values must be met on all un-configured Lanes of a Port.

- 6. The RX DC Common Mode Impedance that exists when no power is present or Fundamental Reset is asserted. This helps ensure that the Receiver Detect circuit will not falsely assume a Receiver is powered on when it is not. This term must be measured at 300 mV above the RX ground.

- 7. It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function. Least squares and median deviation fits have worked well with experimental and simulated data.

### 2.22 Receiver Compliance Eye Diagrams

The RX eye diagram in Figure 70 is specified using the passive compliance/test measurement load (see Figure 71) in place of any real PCI Express RX component.

Note: In general, the minimum Receiver eye diagram measured with the compliance/test measurement load (see Figure 71) will be larger than the minimum Receiver eye diagram measured over a range of systems at the input Receiver of any real PCI Express component. The degraded eye diagram at the input Receiver is due to traces internal to the package as well as silicon parasitic characteristics which cause the real PCI Express component to vary in impedance from the compliance/test measurement load. The input Receiver eye diagram is implementation specific and is not specified. RX component designer should provide additional margin to adequately compensate for the degraded minimum Receiver eye diagram (shown in Figure 70) expected at the input Receiver based on some adequate combination of system simulations and the Return Loss measured looking into the RX package and silicon. The RX eye diagram must be aligned in time using the jitter median to locate the center of the eye diagram.

The eye diagram must be valid for any 250 consecutive UIs.

Please note that the DDR PLL reference clock input, DDRCLK, is only required in asynchronous mode.

The DDRCLKDR configuration register in the Global Utilities block allows the DDR controller to be run in a divided down mode where the DDR bus clock is half the speed of the default configuration. Changing of these defaults must be completed prior to initialization of the DDR controller.

| Functional Signals       | Reset Configuration<br>Name | Value (Binary) | DDR:DDRCLK Ratio |

|--------------------------|-----------------------------|----------------|------------------|

|                          |                             | 000            | 3:1              |

|                          |                             | 001            | 4:1              |

|                          |                             | 010            | 6:1              |

| TSEC_1588_TRIG_OUT[0:1], | cfg_ddr_pll[0:2]            | 011            | 8:1              |

| TSEC1_1588_CLK_OUT       | cig_ddi_pii[0.2]            | 100            | 10:1             |

|                          |                             | 101            | 12:1             |

|                          |                             | 110            | Reserved         |

|                          |                             | 111            | Synchronous mode |

| Table 77. DDR Clock Ratio |

|---------------------------|

|---------------------------|

### 2.23.5 PCI Clocks

The integrated PCI controller in this chip supports PCI input clock frequency in the range of 33–66 MHz. The PCI input clock can be applied from SYSCLK in synchronous mode or PCI1\_CLK in asynchronous mode. For specifications on the PCI1\_CLK, refer to the PCI 2.2 Specification.

The use of PCI1\_CLK is optional if SYSCLK is in the range of 33–66 MHz. If SYSCLK is outside this range then use of PCI1\_CLK is required as a separate PCI clock source, asynchronous with respect to SYSCLK.

#### Hardware Design Considerations

The heat sink removes most of the heat from the chip for most applications. Heat generated on the active side of the chip is conducted through the silicon and through the heat sink attach material (or thermal interface material), and finally to the heat sink. The junction-to-case thermal resistance is low enough that the heat sink attach material and heat sink thermal resistance are the dominant terms.

### 2.24.3.2 Thermal Interface Materials

A thermal interface material is required at the package-to-heat sink interface to minimize the thermal contact resistance. The performance of thermal interface materials improves with increased contact pressure. This performance characteristic chart is generally provided by the thermal interface vendors.

# 3 Hardware Design Considerations

This section provides electrical and thermal design recommendations for successful application of the chip.

# 3.1 System Clocking

This chip includes seven PLLs:

- The platform PLL generates the platform clock from the externally supplied SYSCLK input. The frequency ratio between the platform and SYSCLK is selected using the platform PLL ratio configuration bits as described in Section 2.23.2, "CCB/SYSCLK PLL Ratio."

- The e500 core PLL generates the core clock as a slave to the platform clock. The frequency ratio between the e500 core clock and the platform clock is selected using the e500 PLL ratio configuration bits as described in Section 2.23.3, "e500 Core PLL Ratio."

- The PCI PLL generates the clocking for the PCI bus

- The local bus PLL generates the clock for the local bus.

- There is a PLL for the SerDes1 block to be used for PCI Express interface

- There is a PLL for the SerDes2 block to be used for SGMII and SATA interfaces.

- The DDR PLL generates the DDR clock from the externally supplied DDRCLK input in asynchronous mode. The frequency ratio between the DDR clock and DDRCLK is described in Section 2.23.4, "DDR/DDRCLK PLL Ratio."

# 3.2 Power Supply Design and Sequencing

### 3.2.1 PLL Power Supply Filtering

Each of the PLLs listed above is provided with power through independent power supply pins (AV<sub>DD</sub>\_PLAT, AV<sub>DD</sub>\_CORE, AV<sub>DD</sub>\_PCI, AV<sub>DD</sub>\_LBIU, and AV<sub>DD</sub>\_SRDS respectively). The AV<sub>DD</sub> level should always be equivalent to V<sub>DD</sub>, and preferably these voltages will be derived directly from V<sub>DD</sub> through a low frequency filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide independent filter circuits per PLL power supply as illustrated in Figure 75, one to each of the  $AV_{DD}$  pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of 783 FC-PBGA the footprint, without the inductance of vias.

These capacitors should have a value of 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON). However, customers should work directly with their power regulator vendor for best values types and quantity of bulk capacitors.

# 3.5 SerDes Block Power Supply Decoupling Recommendations

he SerDes1 and SerDes2 blocks require a clean, tightly regulated source of power ( $SnV_{DD}$  and  $XnV_{DD}$ ) to ensure low jitter on transmit and reliable recovery of data in the receiver. An appropriate decoupling scheme is outlined below.

Only surface mount technology (SMT) capacitors should be used to minimize inductance. Connections from all capacitors to power and ground should be done with multiple vias to further reduce inductance.

- First, the board should have at least 10 x 10-nF SMT ceramic chip capacitors as close as possible to the supply balls of the chip. Where the board has blind vias, these capacitors should be placed directly below the chip supply and ground connections. Where the board does not have blind vias, these capacitors should be placed in a ring around the chip as close to the supply and ground connections as possible.

- Second, there should be a  $1-\mu F$  ceramic chip capacitor from each SerDes supply (SnV<sub>DD</sub> and XnV<sub>DD</sub>) to the board ground plane on each side of the chip. This should be done for all SerDes supplies.

- Third, between the chip and any SerDes voltage regulator there should be a 10-μF, low equivalent series resistance (ESR) SMT tantalum chip capacitor and a 100-μF, low ESR SMT tantalum chip capacitor. This should be done for all SerDes supplies.

### 3.6 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. All unused active low inputs should be tied to  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  as required. All unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected. Power and ground connections must be made to all external  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  as for the chip.

### 3.7 Pull-Up and Pull-Down Resistor Requirements

The chip requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and MPIC interrupt pins.

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 78. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion will give unpredictable results.

The following pins must NOT be pulled down during power-on reset: TSEC1\_TXD[3], HRESET\_REQ, TRIG\_OUT/READY/QUIESCE, MSRCID[2:4], ASLEEP. The UART\_SOUT[0:1] and TEST\_SEL pins must be set to a proper state during POR configuration. Please refer to the pinlist table (see Table 62) of the individual chip for more details.

See the PCI 2.2 specification for all pull-ups required for PCI.

### 3.8 Output Buffer DC Impedance

The chip drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).