Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

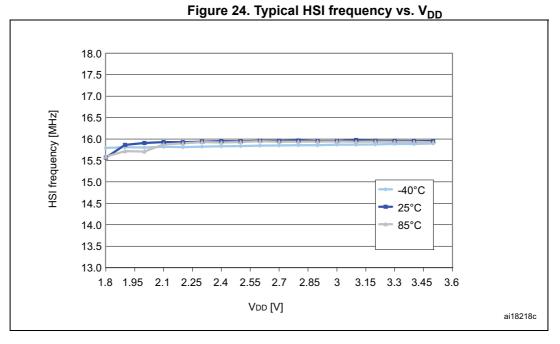

| Speed                      | 16MHz                                                                |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, POR, PWM, WDT                       |

| Number of I/O              | 54                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 2K x 8                                                               |

| RAM Size                   | 4K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                          |

| Data Converters            | A/D 28x12b; D/A 2x12b                                                |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | 64-LQFP (10x10)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151r8t3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 47. | TS characteristics                                                        | <br>111 |

|-----------|---------------------------------------------------------------------------|---------|

| Table 48. | Comparator 1 characteristics                                              | <br>111 |

| Table 49. | Comparator 2 characteristics                                              | <br>112 |

| Table 50. | DAC characteristics                                                       | <br>113 |

| Table 51. | DAC accuracy                                                              | <br>114 |

| Table 52. | DAC output on PB4-PB5-PB6                                                 | <br>114 |

| Table 53. | ADC1 characteristics                                                      | <br>115 |

| Table 54. | ADC1 accuracy with VDDA = 3.3 V to 2.5 V.                                 | <br>117 |

| Table 55. | ADC1 accuracy with VDDA = 2.4 V to 3.6 V.                                 | <br>117 |

| Table 56. | ADC1 accuracy with VDDA = VREF+ = 1.8 V to 2.4 V.                         | <br>117 |

| Table 57. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 16 MHz                        | <br>119 |

| Table 58. | EMS data                                                                  | <br>121 |

| Table 59. | EMI data                                                                  | <br>122 |

| Table 60. | ESD absolute maximum ratings                                              | <br>122 |

| Table 61. | Electrical sensitivities                                                  |         |

| Table 62. | Thermal characteristics.                                                  | <br>123 |

| Table 63. | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package                 |         |

|           | mechanical data                                                           | <br>125 |

| Table 64. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat                         |         |

|           | package mechanical data                                                   | <br>128 |

| Table 65. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                   |         |

|           | mechanical data                                                           | <br>132 |

| Table 66. | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |         |

|           | package mechanical data                                                   | <br>136 |

| Table 67. | WLCSP32 - 32-ball, 1.913 x 3.329 mm, 0.4 mm pitch wafer level chip scale  |         |

|           | package mechanical data                                                   |         |

| Table 68. | WLCSP32 recommended PCB design rules                                      |         |

| Table 69. | Ordering information scheme                                               | <br>141 |

| Table 70. | Document revision history                                                 | <br>142 |

# 2.1 STM8L ultra-low-power 8-bit family benefits

High-density and medium+ density STM8L15xx6/8 devices are part of the STM8L ultra-low-power family providing the following benefits:

- Integrated system

- Up to 64 Kbyte of high-density embedded Flash program memory

- Up to 2 Kbyte of data EEPROM

- Up to 4 Kbyte of RAM

- Internal high-speed and low-power low speed RC.

- Embedded reset

- ultra-low-power consumption

- 1 μA in Active-halt mode

- Clock gated system and optimized power management

- Capability to execute from RAM for Low-power wait mode and Low-power run mode

- Advanced features

- Up to 16 MIPS at 16 MHz CPU clock frequency

- Direct memory access (DMA) for memory-to-memory or peripheral-to-memory access.

- Short development cycles

- Application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals.

- Wide choice of development tools

STM8L ultra-low-power microcontrollers can operate either from 1.8 to 3.6 V (down to 1.65 V at power-down) or from 1.65 to 3.6 V. They are available in the -40 to +85  $^{\circ}$ C and -40 to +125  $^{\circ}$ C temperature ranges.

These features make the STM8L ultra-low-power microcontroller families suitable for a wide range of applications:

- Medical and handheld equipment

- Application control and user interface

- PC peripherals, gaming, GPS and sport equipment

- Alarm systems, wired and wireless sensors

- Metering

The devices are offered in five different packages from 32 to 80 pins. Different sets of peripherals are included depending on the device. Refer to *Section 3* for an overview of the complete range of peripherals proposed in this family.

All STM8L ultra-low-power products are based on the same architecture with the same memory mapping and a coherent pinout.

*Figure 1* shows the block diagram of the High-density and medium+ density STM8L15xx6/8 families.

# 3.14.1 16-bit advanced control timer (TIM1)

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver.

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- 3 independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- 1 additional capture/compare channel which is not connected to an external I/O

- Synchronization module to control the timer with external signals

- Break input to force timer outputs into a defined state

- 3 complementary outputs with adjustable dead time

- Encoder mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

# 3.14.2 16-bit general purpose timers (TIM2, TIM3, TIM5)

- 16-bit autoreload (AR) up/down-counter

- 7-bit prescaler adjustable to fixed power of 2 ratios (1...128)

- 2 individually configurable capture/compare channels

- PWM mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

- Synchronization with other timers or external signals (external clock, reset, trigger and enable)

# 3.14.3 8-bit basic timer (TIM4)

The 8-bit timer consists of an 8-bit up auto-reload counter driven by a programmable prescaler. It can be used for timebase generation with interrupt generation on timer overflow or for DAC trigger generation.

# 3.15 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

### 3.15.1 Window watchdog timer

The window watchdog (WWDG) is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

# 3.15.2 Independent watchdog timer

The independent watchdog peripheral (IWDG) can be used to resolve processor malfunctions due to hardware or software failures.

DocID17943 Rev 10

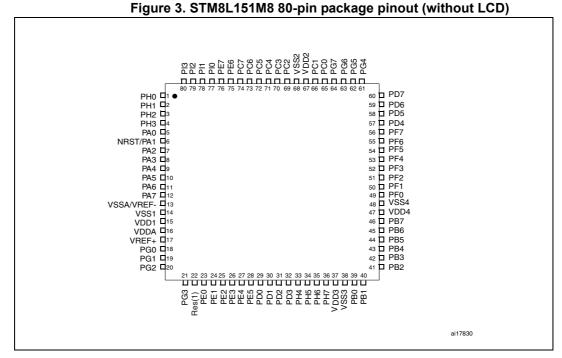

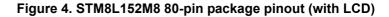

# 4 Pin description

1. Pin 22 is reserved and must be tied to  $V_{\mbox{\scriptsize DD}}.$

2. The above figure shows the package top view.

1. The above figure shows the package top view.

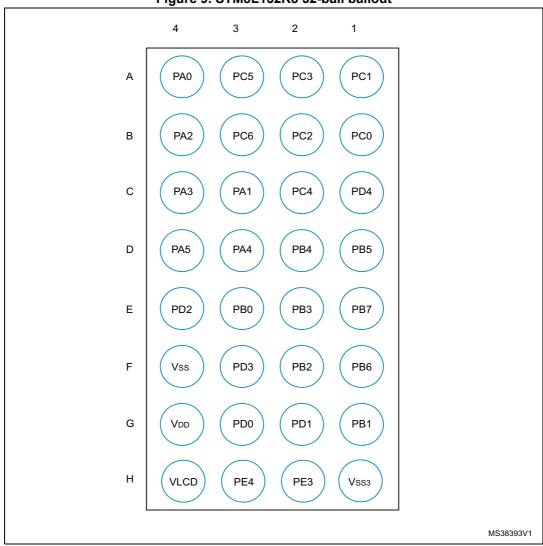

Figure 9. STM8L152K8 32-ball ballout

Warning: For the 32-pin STM8L152K8 devices, some active I/O pins are not bonded out of the package. Effectively, all ports available on 48-pin devices must be considered as active ports also for 32-pin devices - see Table 5: High-density and medium+ density STM8L15x pin description for more details. To avoid spurious effects, users have to configure active ports as input pull-up. A small increase in consumption (typ. < 300 µA) may occur during the power up and reset phase until these ports are properly configured.

|        | Table 5. High-density and medium+ density STM |                            |         |                                                                                        |      |                   |          |     |                |                  |                  |    |                                |                                                                                                                            |

|--------|-----------------------------------------------|----------------------------|---------|----------------------------------------------------------------------------------------|------|-------------------|----------|-----|----------------|------------------|------------------|----|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Pi     | n nu                                          | ımb                        | er      |                                                                                        |      |                   | I        | npu | t              | 0                | utpu             | ıt |                                |                                                                                                                            |

| LQFP80 | LQFP64                                        | <b>UFQFPN48 and LQFP48</b> | WLCSP32 | Pin name                                                                               | Type | I/O level         | floating | ndm | Ext. interrupt | High sink/source | OD               | ЬР | Main function<br>(after reset) | Default alternate<br>function                                                                                              |

| 44     | 36                                            | -                          |         | PB5/SPI1_SCK/<br>LCD_SEG15 <sup>(3)</sup> /ADC1_IN13<br>/ [COMP1_INP]                  | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x                | х  | Port B5                        | SPI1 clock / LCD<br>segment 15 /<br>ADC1_IN13/<br>[Comparator 1 positive<br>input]                                         |

| -      | -                                             | 29                         |         | PB5/SPI1_SCK/<br>LCD_SEG15 <sup>(3)</sup> /ADC1_IN13<br>/DAC_OUT2/<br>[COMP1_INP]      | I/O  | FT <sup>(6)</sup> | x        | x   | х              | HS               | x                | x  | Port B5                        | [SPI1 clock] / LCD<br>segment 15 /<br>ADC1_IN13<br>/ DAC channel 2 output/<br>[Comparator 1 positive<br>input]             |

| 45     | 37                                            | -                          | -       | PB6/SPI1_MOSI/<br>LCD_SEG16 <sup>(3)</sup> /ADC1_IN12<br>/[COMP1_INP]                  | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x                | x  | Port B6                        | SPI1 master out/slave<br>in/<br>LCD segment 16 /<br>ADC1_IN12/<br>[Comparator 1 positive<br>input]                         |

| -      | -                                             | 30                         | F1      | PB6/SPI1_MOSI/<br>LCD_SEG16 <sup>(3)</sup> /ADC1_IN12<br>/DAC_OUT2/ <i>[COMP1_INP]</i> | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x                | x  | Port B6                        | SPI1 master out/<br>slave in / LCD segment<br>16 / ADC1_IN12 / DAC<br>channel 2<br>output/[Comparator 1<br>positive input] |

| 46     | 38                                            | 31                         | E1      | PB7/SPI1_MISO/<br>LCD_SEG17 <sup>(3)</sup> /<br>ADC1_IN11/ <i>[COMP1_INP]</i>          | I/O  | FT <sup>(6)</sup> | x        | х   | х              | HS               | х                | х  | Port B7                        | SPI1 master in- slave<br>out/<br>LCD segment 17 /<br>ADC1_IN11/[Comparato<br>r 1 positive input]                           |

| 65     | 53                                            | 37                         | B1      | PC0/I2C1_SDA                                                                           | I/O  | FT <sup>(6)</sup> | Х        | -   | Х              |                  | T <sup>(7)</sup> |    | Port C0                        | I2C1 data                                                                                                                  |

| 66     | 54                                            | 38                         | A1      | PC1/l2C1_SCL                                                                           | I/O  | FT <sup>(6)</sup> | X        | -   | Х              |                  | T <sup>(7)</sup> |    | Port C1                        | I2C1 clock                                                                                                                 |

| 69     | 57                                            | 41                         |         | PC2/USART1_RX/<br>LCD_SEG22/ADC1_IN6/<br><i>[COMP1_INP]</i> /VREFINT                   | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x                | х  | Port C2                        | USART1 receive /<br>LCD segment 22 /<br>ADC1_IN6/ [Comparator<br>1 positive input] /Internal<br>reference voltage output   |

| -      | -                                             | 42                         | A2      | PC3/USART1_TX/<br>LCD_SEG23 <sup>(3)</sup> /<br>ADC1_IN5                               | I/O  | FT <sup>(6)</sup> | x        | x   | х              | HS               | х                | х  | Port C3                        | USART1 transmit /<br>LCD segment 23 /<br>ADC1_IN5                                                                          |

## Table 5. High-density and medium+ density STM8L15x pin description (continued)

| Table 5. High-density and me    | dium+ density STM8L15x r | oin description (continued) |

|---------------------------------|--------------------------|-----------------------------|

| Table of fight actionly and the |                          |                             |

| Pi     | in nu  |                     |         | 5. High-density and med                                                                               |      |                   | -        | npu |                |                  | utpu |    |                                |                                                                                                                                                                |

|--------|--------|---------------------|---------|-------------------------------------------------------------------------------------------------------|------|-------------------|----------|-----|----------------|------------------|------|----|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP80 | LQFP64 | UFQFPN48 and LQFP48 | WLCSP32 | Pin name                                                                                              | Type | I/O level         | floating | ndw | Ext. interrupt | High sink/source | QO   | РР | Main function<br>(after reset) | Default alternate<br>function                                                                                                                                  |

| -      | -      | 46                  | _(4)    | PC7/LCD_SEG25 <sup>(3)</sup> /<br>ADC1_IN3/USART3_CK/<br>[COMP2_INM] /<br>[COMP1_INP] /<br>[LCD_COM5] | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | x  | Port C7                        | LCD segment 25<br>/ADC1_IN3/ USART3<br>synchronous clock/<br>[Comparator 2 negative<br>input] / [Comparator 1<br>positive input]/<br>[LCD_COM5] <sup>(3)</sup> |

| 29     | 25     | 20                  | G3      | PD0/TIM3_CH2/<br>[ADC1_TRIG] <sup>(2)</sup> /<br>LCD_SEG7 <sup>(3)</sup> /ADC1_IN22/<br>[COMP2_INP]   | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | х    | x  | Port D0                        | Timer 3 - channel 2 /<br>[ADC1_Trigger] / LCD<br>segment 7 / ADC1_IN22<br>/ [Comparator 2 positive<br>input]                                                   |

| 30     | 26     | 21                  | G2      | PD1/TIM3_ETR/<br>LCD_COM3 <sup>(3)</sup> /ADC1_IN21/<br>[COMP1_INP]//<br>[COMP2_INP]                  | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | x  | Port D1                        | Timer 3 - trigger /<br>LCD_COM3 /<br>ADC1_IN21 /<br>[Comparator 1 positive<br>input] /[Comparator 2<br>positive input]                                         |

| 31     | 27     | 22                  | E4      | PD2/TIM1_CH1<br>/LCD_SEG8 <sup>(3)</sup> /ADC1_IN20/<br><i>[COMP1_INP]</i>                            | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | x  | Port D2                        | Timer 1 - channel 1 /<br>LCD segment 8 /<br>ADC1_IN20/<br>[Comparator 1 positive<br>input]                                                                     |

| 32     | 28     | 23                  | F3      | PD3/ TIM1_ETR/<br>LCD_SEG9 <sup>(3)</sup> /<br>ADC1_IN19/<br><i>[COMP1_INP]</i>                       | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | x  | Port D3                        | Timer 1 - trigger /<br>LCD segment 9 /<br>ADC1_IN19/<br>[Comparator 1 positive<br>input]                                                                       |

| 57     | 45     | -                   | -       | PD4/TIM1_CH2<br>/LCD_SEG18 <sup>(3)</sup> /<br>ADC1_IN10/<br><i>[COMP1_INP]</i>                       | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | x  | Port D4                        | Timer 1 - channel 2 /<br>LCD segment 18 /<br>ADC1_IN10/<br>[Comparator 1 positive<br>input]                                                                    |

| -      | -      | 33                  | C1      | PD4/TIM1_CH2<br>/LCD_SEG18 <sup>(3)/</sup><br>ADC1_IN10/SPI2_MISO/<br><i>[COMP1_INP]</i>              | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | x  | Port D4                        | Timer 1 - channel 2 /<br>LCD segment 18 /<br>ADC1_IN10/SPI2<br>master in/slave out/<br>[Comparator 1 positive<br>input]                                        |

DocID17943 Rev 10

| Pi     | in nu  | Imb                 | er      |                  |      |           | Input    |     |                | Output           |    |    |                                |                               |  |  |

|--------|--------|---------------------|---------|------------------|------|-----------|----------|-----|----------------|------------------|----|----|--------------------------------|-------------------------------|--|--|

| LQFP80 | LQFP64 | UFQFPN48 and LQFP48 | WLCSP32 | Pin name         | Type | I/O level | floating | mbn | Ext. interrupt | High sink/source | OD | ЬР | Main function<br>(after reset) | Default alternate<br>function |  |  |

| 48     | -      | -                   | -       | V <sub>SS4</sub> | S    | -         | -        | -   | -              | -                | -  | -  | IOs grou                       | Os ground voltage             |  |  |

| 47     | -      | -                   | -       | V <sub>DD4</sub> | S    | -         | -        | -   | -              | -                | -  | -  | IOs supp                       | upply voltage                 |  |  |

At power-up, the PA1/NRST pin is a reset input pin with pull-up. To be used as a general purpose pin (PA1), it can be configured only as output push-pull, not as output open-drain nor as a general purpose input. Refer to Section Configuring NRST/PA1 pin as general purpose output in the STM8L15xxx and STM8L16xxx reference manual (RM0031).

2. [] Alternate function remapping option (if the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

3. Available on STM8L152x6/8 devices only.

4. Even if this I/O is not available on the device pin, it is considered as active and must be configured to input pull up or output mode by software to avoid spurious behavior and increased consumption.

- 5. A pull-up is applied to PB0 and PB4 during the reset phase. These two pins are input floating after reset release.

- 6. In the 5 V tolerant I/Os, the protection diode to  $V_{DD}$  is not implemented.

- 7. In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up and protection diode to V<sub>DD</sub> are not implemented).

- 8. Available on STM8L152xx devices only. On STM8L151xx devices it is reserved and must be tied to V<sub>DD</sub>.

- 9. The PA0 pin is in input pull-up during the reset phase and after reset release.

10. High Sink LED driver capability available on PA0.

*Note:* Slope control of all GPIO pins can be programmed except true open drain pins and by default is limited to 2 MHz.

### System configuration options

As shown in *Table 5: High-density and medium+ density STM8L15x pin description*, some alternate functions can be remapped on different I/O ports by programming one of the two remapping registers described in the "Routing interface (RI) and system configuration controller" section in the STM8L05xxx, STM8L15xxx and STM8L16xxx reference manual (RM0031).

# 8 Unique ID

STM8 devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory.

- To activate secure boot processes

| Address | Content          | Unique ID bits             |   |   |     |          |   |   |   |  |  |  |

|---------|------------------|----------------------------|---|---|-----|----------|---|---|---|--|--|--|

| Address | description      | 7                          | 6 | 5 | 4   | 3        | 2 | 1 | 0 |  |  |  |

| 0x4926  | X co-ordinate on | U_ID[7:0]                  |   |   |     |          |   |   |   |  |  |  |

| 0x4927  | the wafer        | U_ID[15:8]                 |   |   |     |          |   |   |   |  |  |  |

| 0x4928  | Y co-ordinate on |                            |   |   | U_I | D[23:16] |   |   |   |  |  |  |

| 0x4929  | the wafer        | U_ID[31:24]                |   |   |     |          |   |   |   |  |  |  |

| 0x492A  | Wafer number     |                            |   |   | U_I | D[39:32] |   |   |   |  |  |  |

| 0x492B  |                  |                            |   |   | U_I | D[47:40] |   |   |   |  |  |  |

| 0x492C  |                  |                            |   |   | U_I | D[55:48] |   |   |   |  |  |  |

| 0x492D  |                  |                            |   |   | U_I | D[63:56] |   |   |   |  |  |  |

| 0x492E  | Lot number       |                            |   |   | U_I | D[71:64] |   |   |   |  |  |  |

| 0x492F  | 1                | U_ID[79:72]<br>U_ID[87:80] |   |   |     |          |   |   |   |  |  |  |

| 0x4930  | 1                |                            |   |   |     |          |   |   |   |  |  |  |

| 0x4931  | 1                |                            |   |   | U_I | D[95:88] |   |   |   |  |  |  |

### Table 14. Unique ID registers (96 bits)

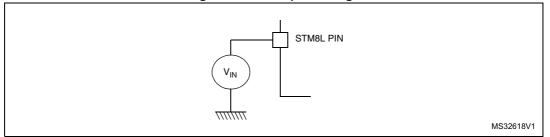

# 9.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 12*.

# 9.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Device mission profile(application conditions) is compliant with JEDEC JESD47 Qualification Standard. Extended mission profiles are available on demand.

| Symbol                            | Ratings                                                              | Min                   | Max                   | Unit |

|-----------------------------------|----------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub> | External supply voltage (including V <sub>DDA</sub> ) <sup>(1)</sup> | - 0.3                 | 4.0                   |      |

|                                   | Input voltage on true open-drain pins (PC0 and PC1)                  | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 4.0 |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on five-volt tolerant (FT) pins                        | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> +4.0  | V    |

|                                   | Input voltage on any other pin                                       | V <sub>ss</sub> - 0.3 | V <sub>DD</sub> + 4.0 |      |

| V <sub>ESD</sub>                  | Electrostatic discharge voltage                                      | ratings (electri      | ical sensitivity)     |      |

Table 15. Voltage characteristics

1. All power (V<sub>DD1</sub>, V<sub>DD2</sub>, V<sub>DD3</sub>, V<sub>DD4</sub>, V<sub>DD4</sub>) and ground (V<sub>SS1</sub>, V<sub>SS2</sub>, V<sub>SS3</sub>, V<sub>SS4</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply.

2. V<sub>IN</sub> maximum must always be respected. Refer to Table 16. for maximum allowed injected current values.

| Symbol            | Parameter          | Conditions                                      | Min. | Тур. | Max. | Unit |

|-------------------|--------------------|-------------------------------------------------|------|------|------|------|

| M                 | PVD threshold 0    | Falling edge                                    | 1.80 | 1.84 | 1.88 |      |

| V <sub>PVD0</sub> | PVD threshold 0    | Rising edge                                     | 1.88 | 1.94 | 1.99 |      |

| M                 | PVD threshold 1    | Falling edge                                    | 1.98 | 2.04 | 2.09 |      |

| V <sub>PVD1</sub> | PVD Inreshold 1    | Rising edge                                     | 2.08 | 2.14 | 2.18 |      |

| M                 | PVD threshold 2    | Falling edge                                    | 2.2  | 2.24 | 2.28 |      |

| V <sub>PVD2</sub> | PVD Infeshold 2    | Rising edge                                     | 2.28 | 2.34 | 2.38 |      |

| V                 | PVD threshold 3    | Falling edge                                    | 2.39 | 2.44 | 2.48 | v    |

| V <sub>PVD3</sub> |                    | Rising edge                                     | 2.47 | 2.54 | 2.58 | V    |

| M                 | PVD threshold 4    | Falling edge                                    | 2.57 | 2.64 | 2.69 |      |

| V <sub>PVD4</sub> |                    | Rising edge                                     | 2.68 | 2.74 | 2.79 |      |

| M                 | PVD threshold 5    | Falling edge                                    | 2.77 | 2.83 | 2.88 |      |

| V <sub>PVD5</sub> | PVD threshold 5    | Rising edge                                     | 2.87 | 2.94 | 2.99 |      |

| M                 | PVD threshold 6    | Falling edge                                    | 2.97 | 3.05 | 3.09 |      |

| V <sub>PVD6</sub> | PVD threshold 6    | Rising edge                                     | 3.08 | 3.15 | 3.20 |      |

|                   |                    | BOR0 threshold                                  | -    | 40   | -    |      |

| Vhyst             | Hysteresis voltage | All BOR and PVD<br>thresholds<br>excepting BOR0 | -    | 100  | -    | mV   |

1. Data guaranteed by design.

2. Data based on characterization results.

### **Electrical parameters**

- 7. RTC enabled. Clock source = LSE

- 8. Wakeup time until start of interrupt vector fetch. The first word of interrupt routine is fetched 4 CPU cycles after  $t_{WU}$ .

- 9. ULP=0 or ULP=1 and FWU=1 in the PWR\_CSR2 register.

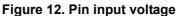

# Table 25. Typical current consumption in Active-halt mode, RTC clocked by LSE external crystal

| Symbol                             | Parameter                          | Condition               | Тур.                  | Unit |    |

|------------------------------------|------------------------------------|-------------------------|-----------------------|------|----|

|                                    |                                    | V - 1 9 V               | LSE                   | 1.2  |    |

|                                    | Supply current in Active-halt mode | V <sub>DD</sub> = 1.8 V | LSE/32 <sup>(3)</sup> | 0.9  |    |

| L (2)                              |                                    | V - 2 V                 | LSE                   | 1.4  |    |

| I <sub>DD(AH)</sub> <sup>(2)</sup> |                                    | V <sub>DD</sub> = 3 V   | LSE/32 <sup>(3)</sup> | 1.1  | μΑ |

|                                    |                                    | V - 2 6 V               | LSE                   | 1.6  |    |

|                                    |                                    | V <sub>DD</sub> = 3.6 V | LSE/32 <sup>(3)</sup> | 1.3  |    |

1. No floating I/O, unless otherwise specified.

2. Based on measurements on bench with 32.768 kHz external crystal oscillator.

3. RTC clock is LSE divided by 32.

# Figure 20. Typical I<sub>DD(AH)</sub> vs. V<sub>DD</sub> (LSI clock source)

# LSE external clock (LSEBYP=1 in CLK\_ECKCR)

The LSE is available on STM8L151xx and STM8L152xx devices only.

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol                              | Parameter                             | Min.                | Тур.   | Max.                  | Unit |

|-------------------------------------|---------------------------------------|---------------------|--------|-----------------------|------|

| f <sub>LSE_ext</sub> <sup>(1)</sup> | External clock source frequency       |                     | 32.768 |                       | kHz  |

| V <sub>LSEH</sub> <sup>(2)</sup>    | OSC32_IN input pin high level voltage | $0.7 \times V_{DD}$ |        | V <sub>DD</sub>       | V    |

| V <sub>LSEL</sub> <sup>(2)</sup>    | OSC32_IN input pin low level voltage  | V <sub>SS</sub>     |        | 0.3 x V <sub>DD</sub> | v    |

| C <sub>in(LSE)</sub> <sup>(1)</sup> | OSC32_IN input capacitance            |                     | 0.6    |                       | pF   |

| I <sub>LEAK_LSE</sub>               | OSC32_IN input leakage current        |                     |        | ±1                    | μA   |

### Table 30. LSE external clock characteristics

1. Guaranteed by design.

2. Data based on characterization results.

### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                              | Parameter                                   | Conditions                              | Min.               | Тур. | Max.                                              | Unit |

|-------------------------------------|---------------------------------------------|-----------------------------------------|--------------------|------|---------------------------------------------------|------|

| f <sub>HSE</sub>                    | High speed external oscillator<br>frequency |                                         | 1                  |      | 16                                                | MHz  |

| R <sub>F</sub>                      | Feedback resistor                           |                                         |                    | 200  |                                                   | kΩ   |

| C <sup>(1)(2)</sup>                 | Recommended load capacitance                |                                         |                    | 20   |                                                   | pF   |

|                                     | HSE oscillator power consumption            | C = 20 pF,<br>f <sub>OSC</sub> = 16 MHz |                    |      | 2.5 (startup)<br>0.7 (stabilized) <sup>(3)</sup>  | mA   |

| IDD(HSE)                            |                                             | C = 10 pF,<br>f <sub>OSC</sub> =16 MHz  |                    |      | 2.5 (startup)<br>0.46 (stabilized) <sup>(3)</sup> | IIIA |

| 9 <sub>m</sub>                      | Oscillator transconductance                 |                                         | 3.5 <sup>(3)</sup> |      |                                                   | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | $V_{\text{DD}}$ is stabilized           |                    | 1    |                                                   | ms   |

1.  $C=C_{L1}=C_{L2}$  is approximately equivalent to 2 x crystal  $C_{LOAD}$ .

2. The oscillator selection can be optimized in terms of supply current using a high quality resonator with small  $R_m$  value. Refer to crystal manufacturer for more details

3. Guaranteed by design.

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 16 MHz oscillation. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

### 4. Guaranteed by design.

## Low speed internal RC oscillator (LSI)

In the following table, data are based on characterization results.

| Symbol               | Parameter                                     | Conditions <sup>(1)</sup>    | Min. | Тур. | Max.               | Unit |

|----------------------|-----------------------------------------------|------------------------------|------|------|--------------------|------|

| f <sub>LSI</sub>     | Frequency                                     |                              | 26   | 38   | 56                 | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time                    |                              |      |      | 200 <sup>(2)</sup> | μs   |

| D <sub>(LSI)</sub>   | LSI oscillator frequency drift <sup>(3)</sup> | 0 °C ≤T <sub>A</sub> ≤ 85 °C | -12  |      | 11                 | %    |

1.  $V_{DD}$  = 1.65 V to 3.6 V,  $T_A$  = -40 to 125 °C unless otherwise specified.

2. Guaranteed by design.

3. This is a deviation for an individual part, once the initial frequency has been measured.

### **Flash memory**

| Symbol                          | Parameter                                                                                                    | Conditions                                                                                                     | Min.                      | Тур. | Max.<br>(1) | Unit    |

|---------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------|------|-------------|---------|

| $V_{DD}$                        | Operating voltage<br>(all modes, read/write/erase)                                                           | f <sub>SYSCLK</sub> = 16 MHz                                                                                   | 1.65                      |      | 3.6         | V       |

| +                               | Programming time for 1 or 128 bytes (block)<br>erase/write cycles (on programmed byte)                       | -                                                                                                              | -                         | 6    | -           | ms      |

| t <sub>prog</sub>               | Programming time for 1 to 128 bytes (block) write cycles (on erased byte)                                    | -                                                                                                              | -                         | 3    | -           | 1115    |

|                                 | Programming/oroging consumption                                                                              | T <sub>A</sub> =+25 °C, V <sub>DD</sub> = 3.0 V                                                                | -                         | 0.7  | -           | mA      |

| Iprog                           | Programming/ erasing consumption                                                                             | T <sub>A</sub> =+25 °C, V <sub>DD</sub> = 1.8 V                                                                | -                         | 0.7  | -           |         |

|                                 | Data retention (program memory) after 10000 erase/write cycles at $T_A$ =-40 $\tau$ o +85 °C (6 suffix)      | T <sub>RET</sub> =+85 °C                                                                                       | 30 <sup>(1)</sup>         | -    | -           |         |

| + (2)                           | Data retention (program memory) after 10000 erase/write cycles at $T_A$ =-40 $\tau$ o +125 °C (3 suffix)     | T <sub>RET</sub> =+125 °C                                                                                      | 5 <sup>(1)</sup>          | -    | -           |         |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (data memory) after 300000 erase/write cycles at $T_A$ =-40 $\tau$ o +85 °C (6 suffix)        | T <sub>RET</sub> =+85 °C                                                                                       | 30 <sup>(1)</sup>         | -    | -           | years   |

|                                 | Data retention (data memory) after 300000<br>erase/write cycles at $T_A$ =-40 $\tau$ o +125 °C<br>(3 suffix) | T <sub>RET</sub> =+125 °C                                                                                      | 5 <sup>(1)</sup>          | -    | -           |         |

|                                 | Erase/write cycles (program memory)                                                                          | T <sub>A</sub> =-40 το +85 °C                                                                                  | 10 <sup>(1)</sup>         | -    | -           |         |

| N <sub>RW</sub> <sup>(3)</sup>  | Erase/write cycles (data memory)                                                                             | (6 suffix),<br>T <sub>A</sub> =-40 το +105 °C<br>(7 suffix) or<br>T <sub>A</sub> =-40 το +125 °C<br>(3 suffix) | 300 <sup>(1)</sup><br>(4) | -    | -           | kcycles |

### Table 36. Flash program and data EEPROM memory

1. Data based on characterization results.

2. Conforming to JEDEC JESD22a117

3. The physical granularity of the memory is 4 bytes, so cycling is performed on 4 bytes even when a write/erase operation addresses a single byte.

4. Data based on characterization performed on the whole data memory.

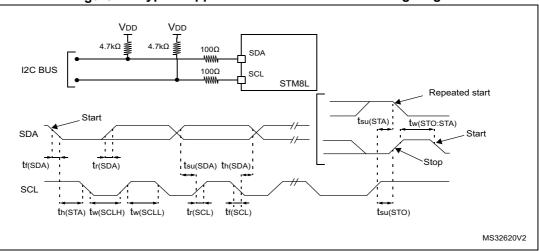

Figure 42. Typical application with I<sup>2</sup>C bus and timing diagram

1. Measurement points are done at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}$

# 9.3.13 12-bit DAC characteristics

In the following table, data are guaranteed by design.

| Symbol                            | Parameter                                                                                                                                                             | Conditions                                                 | Min. | Тур. | Max.                     | Unit |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|------|--------------------------|------|

| V <sub>DDA</sub>                  | Analog supply voltage                                                                                                                                                 | -                                                          | 1.8  | -    | 3.6                      | v    |

| V <sub>REF+</sub>                 | Reference supply voltage                                                                                                                                              | -                                                          | 1.8  | -    | V <sub>DDA</sub>         | V    |

|                                   | Current consumption on V <sub>REF+</sub>                                                                                                                              | V <sub>REF+</sub> = 3.3 V, no load,<br>middle code (0x800) | -    | 130  | 220                      |      |

| I <sub>VREF</sub>                 | supply                                                                                                                                                                | V <sub>REF+</sub> = 3.3 V, no load,<br>worst code (0x000)  | -    | 220  | 350                      |      |

|                                   | Current consumption on V <sub>DDA</sub>                                                                                                                               | V <sub>DDA</sub> = 3.3 V, no load,<br>middle code (0x800)  | -    | 210  | 320                      | μA   |

| I <sub>VDDA</sub>                 | supply                                                                                                                                                                | V <sub>DDA</sub> = 3.3 V, no load,<br>worst code (0x000)   | -    | 320  | 520                      |      |

| T <sub>A</sub>                    | Temperature range                                                                                                                                                     |                                                            | -40  | -    | 125                      | °C   |

| R <sub>L</sub> <sup>(1) (2)</sup> | Resistive load                                                                                                                                                        | DACOUT buffer ON                                           | 5    | -    | -                        | kΩ   |

| R <sub>O</sub>                    | Output impedance                                                                                                                                                      | DACOUT buffer OFF                                          | -    | 8    | 10                       | kΩ   |

| C <sub>L</sub> <sup>(3)</sup>     | Capacitive load                                                                                                                                                       |                                                            | -    | -    | 50                       | pF   |

| DAC_OUT                           |                                                                                                                                                                       | DACOUT buffer ON                                           | 0.2  | -    | V <sub>DDA</sub> - 0.2   | V    |

| (4)                               | DAC_OUT voltage                                                                                                                                                       | DACOUT buffer OFF                                          | 0    | -    | V <sub>REF+</sub> -1 LSB | V    |

| t <sub>settling</sub>             | Settling time (full scale: for a 12-<br>bit input code transition between<br>the lowest and the highest input<br>codes when DAC_OUT reaches<br>the final value ±1LSB) | $R_L \ge 5 \ k\Omega, C_L \le 50 \ pF$                     | -    | 7    | 12                       | μs   |

| Update rate                       | Max frequency for a correct<br>DAC_OUT (@95%) change<br>when small variation of the input<br>code (from code i to i+1LSB).                                            | $R_L \ge 5 \text{ k}\Omega, C_L \le 50 \text{ pF}$         | -    | -    | 1                        | Msps |

| t <sub>WAKEUP</sub>               | Wakeup time from OFF state.<br>Input code between lowest and<br>highest possible codes.                                                                               | $R_L \ge 5 k\Omega, C_L \le 50 pF$                         | -    | 9    | 15                       | μs   |

| PSRR+                             | Power supply rejection ratio (to V <sub>DDA</sub> ) (static DC measurement)                                                                                           | R <sub>L</sub> ≥ 5 kΩ, C <sub>L</sub> ≤50 pF               | -    | -60  | -35                      | dB   |

| Tahlo | 50  | DAC | characteristics |

|-------|-----|-----|-----------------|

| Iable | 50. | DAC | Characteristics |

1. Resistive load between DACOUT and GNDA

2. Output on PF0 or PF1

3. Capacitive load at DACOUT pin

4. It gives the output excursion of the DAC

| Symbol                           | Parameter                               | Conditions                                                                     | Min.                   | Тур. | Max.                        | Unit |

|----------------------------------|-----------------------------------------|--------------------------------------------------------------------------------|------------------------|------|-----------------------------|------|

|                                  |                                         | V <sub>AIN</sub> PF0/1/2/3 fast<br>channels<br>V <sub>DDA</sub> < 2.4 V        | 0.43 <sup>(3)(4)</sup> | -    | -                           |      |

| t <sub>S</sub>                   | Sampling time                           | V <sub>AIN</sub> PF0/1/2/3 fast<br>channels<br>2.4 V ≤V <sub>DDA</sub> ≤ 3.6 V | 0.22 <sup>(3)(4)</sup> | -    | -                           | μs   |

|                                  |                                         | $V_{AIN}$ on slow channels $V_{DDA}$ < 2.4 V                                   | 0.86 <sup>(3)(4)</sup> | -    | -                           |      |

|                                  |                                         | $V_{AIN}$ on slow channels 2.4 V $\leq V_{DDA} \leq$ 3.6 V                     | 0.41 <sup>(3)(4)</sup> | -    | -                           |      |

| +                                | 12-bit conversion time                  | -                                                                              | 12 + t <sub>S</sub>    |      | 1/f <sub>ADC</sub>          |      |

| t <sub>conv</sub>                |                                         | 16 MHz                                                                         | 1 <sup>(3)</sup>       |      | μs                          |      |

| t <sub>WKUP</sub>                | Wakeup time from OFF state              | -                                                                              | -                      | -    | 3                           | μs   |

| t <sub>IDLE</sub> <sup>(5)</sup> | Time before a new conversion            | -                                                                              | -                      | -    | 8                           | S    |

| t <sub>VREFINT</sub>             | Internal reference voltage startup time | -                                                                              | -                      | -    | refer to<br><i>Table 46</i> | ms   |

### Table 53. ADC1 characteristics (continued)

The current consumption through V<sub>REF</sub> is composed of two parameters:

one constant (max 300 μA)

one variable (max 400 μA), only during sampling time + 2 first conversion pulses.

So, peak consumption is 300+400 = 700 μA and average consumption is 300 + [(4 sampling + 2) /16] x 400 = 450 μA at 1Msps

2.  $V_{REF-}$  must be tied to ground.

3. Minimum sampling and conversion time is reached for maximum  $R_{AIN}\text{=}$  0.5 k $\Omega.$

4. Value obtained for continuous conversion on fast channel.

5. The time between 2 conversions, or between ADC ON and the first conversion must be lower than  $t_{\text{IDLE.}}$

## 9.3.15 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

### Functional EMS (electromagnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                            | Conditio                                                                                                                              | Level/<br>Class |    |

|-------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|----|

| V <sub>FESD</sub> | Voltage limits to be applied on<br>any I/O pin to induce a functional<br>disturbance | $V_{DD} = 3.3 \text{ V},  \text{T}_{\text{A}} = +25 ^{\circ}\text{C},$<br>$f_{\text{CPU}} = 16 \text{ MHz},$<br>conforms to IEC 61000 |                 | 2B |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on                  | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = +25 °C,<br>f <sub>CPU</sub> = 16 MHz,                                                       | Using HSI       | 4A |

| *EFIB             | V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance          | conforms to IEC 61000                                                                                                                 | Using HSE       | 2B |

Table 58. EMS data

|                   |       | millimeters |       | inches <sup>(2)</sup> |        |        |  |

|-------------------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol            | Min   | Тур         | Мах   | Min                   | Тур    | Max    |  |

| А                 | 0.525 | 0.555       | 0.585 | 0.0207                | 0.0219 | 0.0230 |  |

| A1                | -     | 0.175       | -     | -                     | 0.0069 | -      |  |

| A2                | -     | 0.380       | -     | -                     | 0.0150 | -      |  |

| A3 <sup>(3)</sup> | -     | 0.025       | -     | -                     | 0.0010 | -      |  |

| b <sup>(4)</sup>  | 0.220 | 0.250       | 0.280 | 0.0087                | 0.0098 | 0.0110 |  |

| D                 | 1.878 | 1.913       | 1.948 | 0.0739                | 0.0753 | 0.0767 |  |

| E                 | 3.294 | 3.329       | 3.364 | 0.1297                | 0.1311 | 0.1324 |  |

| е                 | -     | 0.400       | -     | -                     | 0.0157 | -      |  |

| e1                | -     | 1.200       | -     | -                     | 0.0472 | -      |  |

| e2                | -     | 2.800       | -     | -                     | 0.1102 | -      |  |

| F                 | -     | 0.3565      | -     | -                     | 0.0140 | -      |  |

| G                 | -     | 0.2645      | -     | -                     | 0.0104 | -      |  |

| aaa               | -     | -           | 0.100 | -                     | -      | 0.0039 |  |

| bbb               | -     | -           | 0.100 | -                     | -      | 0.0039 |  |

| CCC               | -     | -           | 0.100 | -                     | -      | 0.0039 |  |

| ddd               | -     | -           | 0.050 | -                     | -      | 0.0020 |  |

| eee               | -     | -           | 0.050 | -                     | -      | 0.0020 |  |

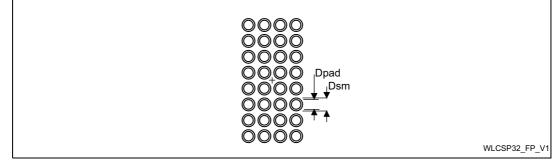

# Table 67. WLCSP32 - 32-ball, 1.913 x 3.329 mm, 0.4 mm pitch wafer level chip scale package mechanical data<sup>(1)</sup>

1. Preliminary data.

2. Values in inches are converted from mm and rounded to 4 decimal digits.

3. Back side coating.

4. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

# Figure 61. WLCSP32 - 32-ball, 1.913 x 3.329 mm, 0.4 mm pitch wafer level chip scale package recommended footprint