Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, LCD, POR, PWM, WDT                    |

| Number of I/O              | 28                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 2K x 8                                                                 |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 20x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-UFBGA, WLCSP                                                        |

| Supplier Device Package    | •                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l152k8y6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Device overview

# Table 2. High-density and medium+ density STM8L15xx6/8 low power device features and peripheral counts

| Fea                                  | atures           | STM8L15xC8                     | STM8L15xK8          | STM8L15xR8                           | STM8L15xM8                       | STM8L15xR6                     |

|--------------------------------------|------------------|--------------------------------|---------------------|--------------------------------------|----------------------------------|--------------------------------|

| Flash (Kbyte)                        |                  | 64                             | 64                  | 64                                   | 64                               | 32                             |

| Data EEPROM (                        | (Kbyte)          | 2                              | 2                   | 2 2                                  |                                  | 1                              |

| RAM (Kbyte)                          |                  | 4                              | 4 4                 |                                      | 4                                | 2                              |

| LCD                                  |                  | 8x24 or<br>4x28 <sup>(1)</sup> | 4x15 <sup>(1)</sup> | 8x36 or<br>4x40 <sup>(1)</sup>       | 8x40 or<br>4x44 <sup>(1)</sup>   | 8x36 or<br>4x40 <sup>(1)</sup> |

|                                      | Basic            | 1<br>(8-bit)                   | 1<br>(8-bit)        | 1<br>(8-bit)                         | 1<br>(8-bit)                     | 1<br>(8-bit)                   |

| Timers                               | General purpose  | 3<br>(16-bit)                  | 3<br>(16-bit)       | 3<br>(16-bit)                        | 3<br>(16-bit)                    | 3<br>(16-bit)                  |

|                                      | Advanced control | 1<br>(16-bit)                  | 1<br>(16-bit)       | 1<br>(16-bit)                        | 1<br>(16-bit)                    | 1<br>(16-bit)                  |

|                                      | SPI              | 2                              | 1                   | 2                                    | 2                                | 2                              |

| Communication interfaces             | I2C              | 1                              | 1                   | 1                                    | 1                                | 1                              |

| interfaces                           | USART            | 3                              | 2                   | 3                                    | 3                                | 3                              |

| GPIOs                                |                  | 41 <sup>(2)</sup>              | 28 <sup>(2)</sup>   | 54 <sup>(2)</sup> 68 <sup>(2)</sup>  |                                  | 54 <sup>(2)</sup>              |

| 12-bit synchroniz<br>(number of chan |                  | 1<br>(25)                      | 1<br>(18)           | 1<br>(28)                            | 1<br>(28)                        | 1<br>(28)                      |

| 12-Bit DAC                           |                  | 2                              | 1                   | 2                                    | 2                                | 2                              |

| Number of chan                       | nels             | 2                              | 1                   | 2                                    | 2                                | 2                              |

| Comparators (C                       | OMP1/COMP2)      | 2                              | 2                   | 2                                    | 2                                | 2                              |

| Others                               |                  |                                |                     |                                      | ndent watchdog<br>and 32-kHz ext |                                |

| CPU frequency                        |                  |                                |                     | 16 MHz                               |                                  |                                |

| Operating voltag                     | je               | 1.8                            | ,                   | to 1.65 V at pov<br>to 3.6 V without | ver-down) with B<br>BOR          | OR                             |

| Operating tempe                      | erature          | -                              | –40 to +85 °C /     | –40 to +105 °C                       | / -40 to +125 °C                 | 5                              |

| Packages                             |                  | UFQFPN48<br>LQFP48             | WLCSP32             | LQFP64                               | LQFP80                           | LQFP64                         |

1. STM8L152x6/8 versions only.

2. The number of GPIOs given in this table includes the NRST/PA1 pin but the application can use the NRST/PA1 pin as general purpose output only (PA1).

# 3.2 Central processing unit STM8

### 3.2.1 Advanced STM8 Core

The 8-bit STM8 core is designed for code efficiency and performance with an Harvard architecture and a 3-stage pipeline.

It contains 6 internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing, and 80 instructions.

#### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16 Mbyte linear memory space

- 16-bit stack pointer access to a 64 Kbyte level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

#### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for lookup tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

#### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

### 3.2.2 Interrupt controller

The high-density and medium+ density STM8L15xx6/8x devices feature a nested vectored interrupt controller:

- Nested interrupts with 3 software priority levels

- 32 interrupt vectors with hardware priority

- Up to 40 external interrupt sources on 11 vectors

- Trap and reset interrupts

#### 3.3.3 Voltage regulator

The high-density and medium+ density STM8L15xx6/8 devices embed an internal voltage regulator for generating the 1.8 V power supply for the core and peripherals.

This regulator has two different modes:

- Main voltage regulator mode (MVR) for Run, Wait for interrupt (WFI) and Wait for event (WFE) modes.

- Low-power voltage regulator mode (LPVR) for Halt, Active-halt, Low-power run and Low-power wait modes.

When entering Halt or Active-halt modes, the system automatically switches from the MVR to the LPVR in order to reduce current consumption.

### 3.4 Clock management

The clock controller distributes the system clock (SYSCLK) coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness.

#### Features

- Clock prescaler: to get the best compromise between speed and current consumption the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** Clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- System clock sources: 4 different clock sources can be used to drive the system clock:

- 1-16 MHz High speed external crystal (HSE)

- 16 MHz High speed internal RC oscillator (HSI)

- 32.768 Low speed external crystal (LSE) available on STM8L151xx and STM8L152xx devices

- 38 kHz Low speed internal RC (LSI)

- **RTC and LCD clock sources:** the above four sources can be chosen to clock the RTC and the LCD, whatever the system clock.

- **Startup clock:** After reset, the microcontroller restarts by default with an internal 2 MHz clock (HSI/8). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- **Clock security system (CSS):** This feature can be enabled by software. If a HSE clock failure occurs, the system clock is automatically switched to HSI.

- **Configurable main clock output (CCO):** This outputs an external clock for use by the application.

# 3.6 LCD (Liquid crystal display)

The LCD is only available on STM8L152x6/8 devices.

The liquid crystal display drives up to 8 common terminals and up to 40 segment terminals to drive up to 320 pixels. It can also be configured to drive up to 4 common and 44 segments (up to 176 pixels).

- Internal step-up converter to guarantee contrast control whatever V<sub>DD</sub>.

- Static 1/2, 1/3, 1/4, 1/8 duty supported.

- Static 1/2, 1/3, 1/4 bias supported.

- Phase inversion to reduce power consumption and EMI.

- Up to 8 pixels which can programmed to blink.

- The LCD controller can operate in Halt mode.

Note: Unnecessary segments and common pins can be used as general I/O pins.

### 3.7 Memories

The high-density and medium+ density STM8L15xx6/8 devices have the following main features:

- Up to 4 Kbyte of RAM

- The non-volatile memory is divided into three arrays:

- Up to 64 Kbyte of medium-density embedded Flash program memory

- Up to 2 Kbyte of Data EEPROM

- Option bytes.

The EEPROM embeds the error correction code (ECC) feature. It supports the read-whilewrite (RWW): it is possible to execute the code from the program matrix while programming/erasing the data matrix.

The option byte protects part of the Flash program memory from write and readout piracy.

### 3.8 DMA

A 4-channel direct memory access controller (DMA1) offers a memory-to-memory and peripherals-from/to-memory transfer capability. The 4 channels are shared between the following IPs with DMA capability: ADC1, DAC1, DAC2, I2C1, SPI1, SPI2, USART1, USART2, USART3, and the 5 Timers.

| Pi     | n nı   |                     |         | 5. High-density and med                                                                                  |      |                   |          | npu |                |                  | utpu |    |                                |                                                                                                                            |

|--------|--------|---------------------|---------|----------------------------------------------------------------------------------------------------------|------|-------------------|----------|-----|----------------|------------------|------|----|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| LQFP80 | LQFP64 | UFQFPN48 and LQFP48 | WLCSP32 | Pin name                                                                                                 | Type | I/O level         | floating | ndw | Ext. interrupt | High sink/source | OD   | РР | Main function<br>(after reset) | Default alternate<br>function                                                                                              |

| 11     | 7      | 7                   | _(4)    | PA6/ADC1_TRIG/<br>LCD_COM2 <sup>(3)</sup> /ADC1_IN0/<br><i>[COMP1_INP]</i>                               | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | х  | Port A6                        | ADC1 - trigger /<br>LCD_COM2 / ADC1<br>input 0/<br>[Comparator 1 positive<br>input]                                        |

| 12     | 8      | 8                   | _(4)    | PA7/LCD_SEG0 <sup>(3)</sup> /<br>TIM5_CH1                                                                | I/O  | FT <sup>(6)</sup> | x        | х   | х              | HS               | х    | х  | Port A7                        | LCD segment 0 /<br>TIM5 channel 1                                                                                          |

| 39     | 31     | 24                  | E3      | PB0 <sup>(5)/</sup> TIM2_CH1/<br>LCD_SEG10 <sup>(3)</sup> /ADC1_IN18<br>/ [COMP1_INP]                    | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | x  | Port B0                        | Timer 2 - channel 1<br>/LCD segment 10/<br>ADC1_IN18/<br>[Comparator 1 positive<br>input]                                  |

| 40     | 32     | 25                  | G1      | PB1/TIM3_CH1/<br>LCD_SEG11 <sup>(3)</sup> /ADC1_IN17<br>/ [COMP1_INP]                                    | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | х  | Port B1                        | Timer 3 - channel 1<br>/ LCD segment 11 /<br>ADC1_IN17/<br>[Comparator 1 positive<br>input]                                |

| 41     | 33     | 26                  | F2      | PB2/<br>TIM2_CH2/LCD_SEG12 <sup>(3)/</sup><br>ADC1_IN16/ <i>[COMP1_INP]</i>                              | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | х  | Port B2                        | Timer 2 - channel 2<br>/ LCD segment 12 /<br>ADC1_IN16/<br>[Comparator 1 positive<br>input]                                |

| 42     | 34     | 27                  | E2      | PB3/TIM2_ETR/<br>LCD_SEG13 <sup>(3)</sup> /ADC1_IN15<br>/[COMP1_INP]                                     | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | х  | Port B3                        | Timer 2 - trigger<br>/ LCD segment 13<br>/ADC1_IN15/<br>[Comparator 1 positive<br>input]                                   |

| 43     | 35     | -                   |         | PB4 <sup>(5)</sup> /SPI1_NSS/<br>LCD_SEG14 <sup>(3)</sup> /ADC1_IN14<br>/[COMP1_INP]                     | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | х  | Port B4                        | SPI1 master/slave select<br>/ LCD segment 14 /<br>ADC1_IN14/<br>[Comparator 1 positive<br>input]                           |

| -      | -      | 28                  | D2      | PB4 <sup>(5)</sup> /SPI1_NSS/<br>LCD_SEG14 <sup>(3)</sup> /ADC1_IN14<br>/DAC_OUT2/<br><i>[COMP1_INP]</i> | I/O  | FT <sup>(6)</sup> | x        | x   | x              | HS               | x    | x  | Port B4                        | SPI1 master/slave select<br>/ LCD segment 14 /<br>ADC1_IN14 /<br>DAC channel 2 output/<br>[Comparator 1 positive<br>input] |

| Address                   | Block | Register label | Register name                          | Reset status |

|---------------------------|-------|----------------|----------------------------------------|--------------|

| 0x00 5262                 |       | TIM2_CCR1L     | TIM2 capture/compare register 1 low    | 0x00         |

| 0x00 5263                 |       | TIM2_CCR2H     | TIM2 capture/compare register 2 high   | 0x00         |

| 0x00 5264                 | TIM2  | TIM2_CCR2L     | TIM2 capture/compare register 2 low    | 0x00         |

| 0x00 5265                 |       | TIM2_BKR       | TIM2 break register                    | 0x00         |

| 0x00 5266                 |       | TIM2_OISR      | TIM2 output idle state register        | 0x00         |

| 0x00 5267 to<br>0x00 527F |       |                | Reserved area (25 byte)                |              |

| 0x00 5280                 |       | TIM3_CR1       | TIM3 control register 1                | 0x00         |

| 0x00 5281                 |       | TIM3_CR2       | TIM3 control register 2                | 0x00         |

| 0x00 5282                 |       | TIM3_SMCR      | TIM3 Slave mode control register       | 0x00         |

| 0x00 5283                 |       | TIM3_ETR       | TIM3 external trigger register         | 0x00         |

| 0x00 5284                 |       | TIM3_DER       | TIM3 DMA1 request enable register      | 0x00         |

| 0x00 5285                 |       | TIM3_IER       | TIM3 interrupt enable register         | 0x00         |

| 0x00 5286                 |       | TIM3_SR1       | TIM3 status register 1                 | 0x00         |

| 0x00 5287                 |       | TIM3_SR2       | TIM3 status register 2                 | 0x00         |

| 0x00 5288                 |       | TIM3_EGR       | TIM3 event generation register         | 0x00         |

| 0x00 5289                 |       | TIM3_CCMR1     | TIM3 Capture/Compare mode register 1   | 0x00         |

| 0x00 528A                 |       | TIM3_CCMR2     | TIM3 Capture/Compare mode register 2   | 0x00         |

| 0x00 528B                 | TIM3  | TIM3_CCER1     | TIM3 Capture/Compare enable register 1 | 0x00         |

| 0x00 528C                 |       | TIM3_CNTRH     | TIM3 counter high                      | 0x00         |

| 0x00 528D                 |       | TIM3_CNTRL     | TIM3 counter low                       | 0x00         |

| 0x00 528E                 |       | TIM3_PSCR      | TIM3 prescaler register                | 0x00         |

| 0x00 528F                 |       | TIM3_ARRH      | TIM3 Auto-reload register high         | 0xFF         |

| 0x00 5290                 |       | TIM3_ARRL      | TIM3 Auto-reload register low          | 0xFF         |

| 0x00 5291                 |       | TIM3_CCR1H     | TIM3 Capture/Compare register 1 high   | 0x00         |

| 0x00 5292                 |       | TIM3_CCR1L     | TIM3 Capture/Compare register 1 low    | 0x00         |

| 0x00 5293                 |       | TIM3_CCR2H     | TIM3 Capture/Compare register 2 high   | 0x00         |

| 0x00 5294                 |       | TIM3_CCR2L     | TIM3 Capture/Compare register 2 low    | 0x00         |

| 0x00 5295                 |       | TIM3_BKR       | TIM3 break register                    | 0x00         |

| 0x00 5296                 |       | TIM3_OISR      | TIM3 output idle state register        | 0x00         |

| 0x00 5297 to<br>0x00 52AF |       |                | Reserved area (25 byte)                |              |

Table 9. General hardware register map (continued)

| Address                   | Block | Register label    | Register name                                           | Reset status |

|---------------------------|-------|-------------------|---------------------------------------------------------|--------------|

| 0x00 5386 to<br>0x00 5387 |       |                   | Reserved area (2 byte)                                  |              |

| 0x00 5388                 | DAC   | DAC_CH1RDHRH      | DAC channel 1 right aligned data holding register high  | 0x00         |

| 0x00 5389                 |       | DAC_CH1RDHRL      | DAC channel 1 right aligned data holding register low   | 0x00         |

| 0x00 538A to<br>0x00 538B |       |                   | Reserved area (2 byte)                                  |              |

| 0x00 538C                 | DAC   | DAC_CH1LDHRH      | DAC channel 1 left aligned data holding register high   | 0x00         |

| 0x00 538D                 | DAC   | DAC_CH1LDHRL      | DAC channel 1 left aligned data holding<br>register low | 0x00         |

| 0x00 538E<br>to 0x00 538F |       |                   | Reserved area (2 byte)                                  |              |

| 0x00 5390                 | DAC   | DAC_CH1DHR8       | DAC channel 1 8-bit data holding register               | 0x00         |

| 0x00 5391 to<br>0x00 5393 |       |                   | Reserved area (3 byte)                                  |              |

| 0x00 5394                 | – DAC | DAC_CH2RDHRH      | DAC channel 2 right aligned data holding register high  | 0x00         |

| 0x00 5395                 | DAC   | DAC_CH2RDHRL      | DAC channel 2 right aligned data holding register low   | 0x00         |

| 0x00 5396 to<br>0x00 5397 |       |                   | Reserved area (2 byte)                                  |              |

| 0x00 5398                 | DAC   | DAC_CH2LDHRH      | DAC channel 2 left aligned data holding register high   | 0x00         |

| 0x00 5399                 | DAC   | DAC_CH2LDHRL      | DAC channel 2 left aligned data holding register low    | 0x00         |

| 0x00 539A<br>to 0x00 539B |       |                   | Reserved area (2 byte)                                  |              |

| 0x00 539C                 | DAC   | DAC_CH2DHR8       | DAC channel 2 8-bit data holding register               | 0x00         |

| 0x00 539D<br>to 0x00 539F |       |                   | Reserved area (3 byte)                                  |              |

| 0x00 53A0                 | DAC   | DAC_DCH1RDHR<br>H | DAC channel 1 right aligned data holding register high  | 0x00         |

| 0x00 53A1                 |       | DAC_DCH1RDHRL     | DAC channel 1 right aligned data holding register low   | 0x00         |

| 0x00 53A2<br>to 0x00 53AB |       |                   | Reserved area (3 byte)                                  | •            |

Table 9. General hardware register map (continued)

6 Interrupt vector mapping

|            | Table 11. Interrupt mapping    |                                                                                                                         |                             |                                       |                                      |                                                     |                   |  |  |  |

|------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|--|--|--|

| IRQ<br>No. | Source<br>block                | Description                                                                                                             | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |  |  |  |

| -          | RESET                          | Reset                                                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8000         |  |  |  |

| -          | TRAP                           | Software interrupt                                                                                                      | -                           | -                                     | -                                    | -                                                   | 0x00 8004         |  |  |  |

| 0          | TLI <sup>(2)</sup>             | External Top level Interrupt                                                                                            | -                           | -                                     | -                                    | -                                                   | 0x00 8008         |  |  |  |

| 1          | FLASH                          | EOP/WR_PG_DIS                                                                                                           | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 800C         |  |  |  |

| 2          | DMA1 0/1                       | DMA1 channels 0/1                                                                                                       | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8010         |  |  |  |

| 3          | DMA1 2/3                       | DMA1 channels 2/3                                                                                                       | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8014         |  |  |  |

| 4          | RTC/LSE_<br>CSS                | RTC alarm interrupt/LSE<br>CSS interrupt                                                                                | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8018         |  |  |  |

| 5          | EXTI<br>E/F/PVD <sup>(4)</sup> | PortE/F interrupt/PVD interrupt                                                                                         | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 801C         |  |  |  |

| 6          | EXTIB/G                        | External interrupt port B/G                                                                                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8020         |  |  |  |

| 7          | EXTID/H                        | External interrupt port D/H                                                                                             | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8024         |  |  |  |

| 8          | EXTI0                          | External interrupt 0                                                                                                    | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8028         |  |  |  |

| 9          | EXTI1                          | External interrupt 1                                                                                                    | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 802C         |  |  |  |

| 10         | EXTI2                          | External interrupt 2                                                                                                    | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8030         |  |  |  |

| 11         | EXTI3                          | External interrupt 3                                                                                                    | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8034         |  |  |  |

| 12         | EXTI4                          | External interrupt 4                                                                                                    | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8038         |  |  |  |

| 13         | EXTI5                          | External interrupt 5                                                                                                    | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 803C         |  |  |  |

| 14         | EXTI6                          | External interrupt 6                                                                                                    | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8040         |  |  |  |

| 15         | EXTI7                          | External interrupt 7                                                                                                    | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8044         |  |  |  |

| 16         | LCD                            | LCD interrupt                                                                                                           | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8048         |  |  |  |

| 17         | CLK/<br>TIM1/<br>DAC           | System clock switch/CSS interrupt/TIM1 break/DAC                                                                        | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 804C         |  |  |  |

| 18         | COMP1/<br>COMP2<br>ADC1        | Comparator 1 and 2 interrupt/ADC1                                                                                       | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8050         |  |  |  |

| 19         | TIM2/<br>USART2                | TIM2 update<br>/overflow/trigger/break/<br>USART2 transmission<br>complete/transmit data<br>register empty<br>interrupt | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8054         |  |  |  |

#### Table 11. Interrupt mapping

| IRQ<br>No. | Source<br>block        | Description                                                                                                             | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |  |  |

|------------|------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|--|--|

| 20         | TIM2/<br>USART2        | Capture/Compare/USART<br>2 interrupt                                                                                    | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8058         |  |  |

| 21         | TIM3/<br>USART3        | TIM3 Update<br>/Overflow/Trigger/Break/<br>USART3 transmission<br>complete/transmit data<br>register empty<br>interrupt | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 805C         |  |  |

| 22         | TIM3/<br>USART3        | TIM3 Capture/Compare/<br>USART3 Receive register<br>data full/overrun/idle line<br>detected/parity error/<br>interrupt  | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8060         |  |  |

| 23         | TIM1                   | Update /overflow/trigger/<br>COM                                                                                        | -                           | -                                     | -                                    | Yes <sup>(3)</sup>                                  | 0x00 8064         |  |  |

| 24         | TIM1                   | Capture/Compare                                                                                                         | -                           | -                                     | -                                    | Yes <sup>(3)</sup>                                  | 0x00 8068         |  |  |

| 25         | TIM4                   | Update/overflow/trigger                                                                                                 | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 806C         |  |  |

| 26         | SPI1                   | End of Transfer                                                                                                         | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8070         |  |  |

| 27         | USART 1/<br>TIM5       | USART1 transmission<br>complete/transmit data<br>register empty/<br>TIM5 update/overflow/<br>trigger/break              | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8074         |  |  |

| 28         | USART 1/<br>TIM5       | USART1 Receive register<br>data full/overrun/idle line<br>detected/parity error/<br>TIM5 capture/compare                | -                           | -                                     | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 8078         |  |  |

| 29         | I <sup>2</sup> C1/SPI2 | I <sup>2</sup> C1 interrupt <sup>(5)</sup> /<br>SPI2                                                                    | Yes                         | Yes                                   | Yes                                  | Yes <sup>(3)</sup>                                  | 0x00 807C         |  |  |

#### Table 11. Interrupt mapping (continued)

1. The Low-power wait mode is entered when executing a WFE instruction in Low-power run mode.

2. The TLI interrupt is the logic OR between TIM2 overflow interrupt, and TIM4 overflow interrupts.

3. In WFE mode, this interrupt is served if it has been previously enabled. After processing the interrupt, the processor goes back to WFE mode. When this interrupt is configured as a wakeup event, the CPU wakes up and resumes processing.

4. The interrupt from PVD is logically OR-ed with Port E and F interrupts. Register EXTI\_CONF allows to select between Port E and Port F interrupt (see *External interrupt port select register (EXTI\_CONF)* in the RM0031).

5. The device is woken up from Halt or Active-halt mode only when the address received matches the interface address.

# 9 Electrical parameters

### 9.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

### 9.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A$ = 25 °C and  $T_A$  =  $T_A$  max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

### 9.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25 \degree C$ ,  $V_{DD} = 3 \lor V$ . They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

### 9.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

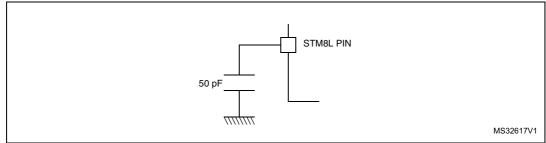

### 9.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 11*.

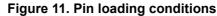

### 9.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 12*.

# 9.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Device mission profile(application conditions) is compliant with JEDEC JESD47 Qualification Standard. Extended mission profiles are available on demand.

| Symbol                            | Ratings                                                              | Min                                       | Max                   | Unit |

|-----------------------------------|----------------------------------------------------------------------|-------------------------------------------|-----------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub> | External supply voltage (including V <sub>DDA</sub> ) <sup>(1)</sup> | - 0.3                                     | 4.0                   |      |

|                                   | Input voltage on true open-drain pins (PC0 and PC1)                  | V <sub>SS</sub> - 0.3                     | V <sub>DD</sub> + 4.0 |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on five-volt tolerant (FT) pins                        | V <sub>SS</sub> - 0.3                     | V <sub>DD</sub> +4.0  | V    |

|                                   | Input voltage on any other pin                                       | V <sub>ss</sub> - 0.3                     | 4.0                   |      |

| V <sub>ESD</sub>                  | Electrostatic discharge voltage                                      | see Absolut<br>ratings (electri<br>on pag |                       |      |

Table 15. Voltage characteristics

1. All power (V<sub>DD1</sub>, V<sub>DD2</sub>, V<sub>DD3</sub>, V<sub>DD4</sub>, V<sub>DD4</sub>) and ground (V<sub>SS1</sub>, V<sub>SS2</sub>, V<sub>SS3</sub>, V<sub>SS4</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply.

2. V<sub>IN</sub> maximum must always be respected. Refer to Table 16. for maximum allowed injected current values.

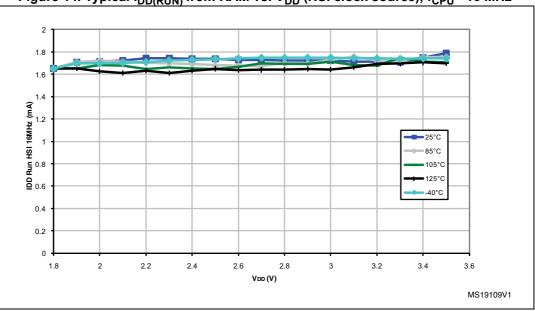

Figure 14. Typical I<sub>DD(RUN)</sub> from RAM vs. V<sub>DD</sub> (HSI clock source), f<sub>CPU</sub> =16 MHz

1. Typical current consumption measured with code executed from RAM.

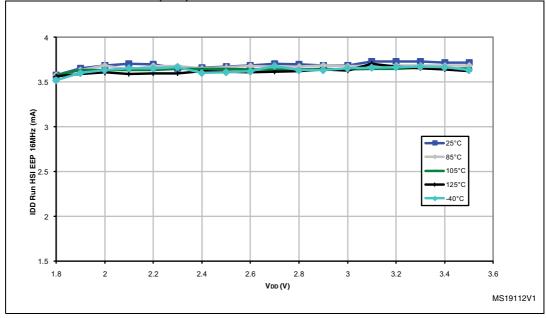

Figure 15. Typical  $I_{DD(RUN)}$  from Flash vs.  $V_{DD}$  (HSI clock source),  $f_{CPU}$  = 16 MHz

1. Typical current consumption measured with code executed from Flash.

In the following table, data are based on characterization results, unless otherwise specified.

|                       |                         |                                                              |                                                                          | -                                   |       |              | N                   | lax                 |                     |    |

|-----------------------|-------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------|-------|--------------|---------------------|---------------------|---------------------|----|

| Symbol                | Parameter               | Conditions <sup>(1)</sup>                                    |                                                                          | Тур                                 | 55°C  | 85 °C<br>(2) | 105 °C<br>(3)       | 125 °C<br>(4)       | Unit                |    |

|                       |                         |                                                              |                                                                          | f <sub>CPU</sub> = 125 kHz          | 0.21  | 0.29         | 0.33                | 0.36                | 0.43                |    |

|                       |                         |                                                              |                                                                          | f <sub>CPU</sub> = 1 MHz            | 0.25  | 0.33         | 0.37                | 0.4                 | 0.47                |    |

|                       |                         |                                                              | HSI                                                                      | f <sub>CPU</sub> = 4 MHz            | 0.32  | 0.4          | 0.44                | 0.47                | 0.54                |    |

|                       |                         | CPU not                                                      |                                                                          | f <sub>CPU</sub> = 8 MHz            | 0.42  | 0.496        | 0.54                | 0.56                | 0.64                |    |

|                       | Supply                  | clocked,<br>all peripherals<br>OFF,<br>code<br>executed from |                                                                          | f <sub>CPU</sub> = 16 MHz           | 0.66  | 0.736        | 0.78 <sup>(6)</sup> | 0.8 <sup>(6)</sup>  | 0.88 <sup>(6)</sup> | mA |

|                       |                         |                                                              | HSE<br>external<br>clock<br>(f <sub>CPU</sub> =f <sub>HSE</sub> )<br>(7) | f <sub>CPU</sub> = 125 kHz          | 0.19  | 0.21         | 0.3                 | 0.35                | 0.41                |    |

|                       |                         |                                                              |                                                                          | f <sub>CPU</sub> = 1 MHz            | 0.2   | 0.23         | 0.32                | 0.36                | 0.43                |    |

| I <sub>DD(Wait)</sub> | current in<br>Wait mode | RAM<br>with Flash in                                         |                                                                          | f <sub>CPU</sub> = 4 MHz            | 0.27  | 0.3          | 0.39                | 0.43                | 0.5                 |    |

|                       |                         | I <sub>DDQ</sub> mode, <sup>(5)</sup>                        |                                                                          | f <sub>CPU</sub> = 8 MHz            | 0.37  | 0.4          | 0.49                | 0.53                | 0.6                 |    |

|                       |                         | V <sub>DD</sub> from<br>1.65 V to                            |                                                                          | f <sub>CPU</sub> = 16 MHz           | 0.63  | 0.66         | 0.75 <sup>(6)</sup> | 0.79 <sup>(6)</sup> | 0.86 <sup>(6)</sup> |    |

|                       |                         | 3.6 V                                                        | LSI                                                                      | f <sub>CPU</sub> = f <sub>LSI</sub> | 0.028 | 0.037        | 0.039               | 0.044               | 0.054               |    |

|                       |                         | LSE <sup>(8)</sup><br>external<br>clock<br>(32.768<br>kHz)   | external<br>clock<br>(32.768                                             | f <sub>CPU</sub> = f <sub>LSE</sub> | 0.027 | 0.035        | 0.038               | 0.042               | 0.051               |    |

Table 21. Total current consumption in Wait mode

### 9.3.6 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error, out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation, LCD levels, etc.).

The test results are given in the following table.

|                  |                                                | Functional s       |                    |      |

|------------------|------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                    | Negative injection | Positive injection | Unit |

|                  | Injected current on true open-drain pins       | -5                 | +0                 |      |

| I <sub>INJ</sub> | Injected current on all 5 V tolerant (FT) pins | -5                 | +0                 | mA   |

|                  | Injected current on any other pin              | -5                 | +5                 |      |

#### Table 37. I/O current injection susceptibility

### 9.3.7 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

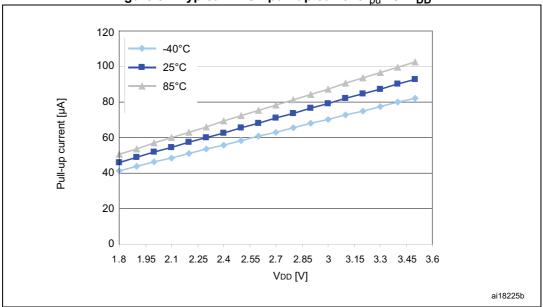

Figure 37. Typical NRST pull-up current I<sub>pu</sub> vs. V<sub>DD</sub>

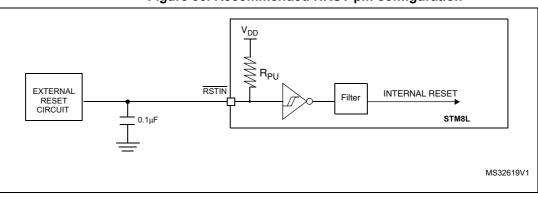

The reset network shown in *Figure 38* protects the device against parasitic resets. The user must ensure that the level on the NRST pin can go below the  $V_{IL}$  max. level specified in *Table 42*. Otherwise the reset is not taken into account internally. For power consumption-sensitive applications, the capacity of the external reset capacitor can be reduced to limit the charge/discharge current. If the NRST signal is used to reset the external circuitry, the user must pay attention to the charge/discharge time of the external capacitor to meet the reset timing conditions of the external devices. The minimum recommended capacity is 10 nF.

Figure 38. Recommended NRST pin configuration

### I<sup>2</sup>C - Inter IC control interface

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{SYSCLK}},$  and  $T_{\text{A}}$  unless otherwise specified.

The STM8L I<sup>2</sup>C interface (I2C1) meets the requirements of the Standard I<sup>2</sup>C communication protocol described in the following table with the restriction mentioned below:

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                               | Standard            | mode I <sup>2</sup> C | Fast mo             | de l <sup>2</sup> C <sup>(1)</sup> | Unit |  |  |

|--------------------------------------------|-----------------------------------------|---------------------|-----------------------|---------------------|------------------------------------|------|--|--|

| Symbol                                     | Falameter                               | Min. <sup>(2)</sup> | Max. <sup>(2)</sup>   | Min. <sup>(2)</sup> | Max. <sup>(2)</sup>                | Unit |  |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                 | -                     | 1.3                 | -                                  |      |  |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                 | -                     | 0.6                 | -                                  | μs   |  |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                 | -                     | 100                 | -                                  |      |  |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0                   | -                     | 0                   | 900                                |      |  |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                   | 1000                  | -                   | 300                                | ns   |  |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -                   | 300                   | -                   | 300                                |      |  |  |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                 | -                     | 0.6                 | -                                  |      |  |  |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                 | -                     | 0.6                 | -                                  | μs   |  |  |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                 | -                     | 0.6                 | -                                  | μs   |  |  |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                 | -                     | 1.3                 | -                                  | μs   |  |  |

| Cb                                         | Capacitive load for each bus line       | _                   | 400                   | -                   | 400                                | pF   |  |  |

Table 44. I2C characteristics

1. f<sub>SYSCLK</sub> must be at least equal to 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz).

2. Data based on standard  $I^2C$  protocol requirement, not tested in production.

Note: For speeds around 200 kHz, the achieved speed can have a  $\pm$ 5% tolerance. For other speed ranges, the achieved speed can have a  $\pm$ 2% tolerance. The above variations depend on the accuracy of the external components used.

#### Static latch-up

• LU: 3 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Table | 61          | Electrical | sensitivities  |

|-------|-------------|------------|----------------|

| Iabic | <b>U</b> I. | LIECUICAI  | 36113111411163 |

| Symbol | Parameter             | Class |

|--------|-----------------------|-------|

| LU     | Static latch-up class | II    |

### 9.4 Thermal characteristics

The maximum chip junction temperature  $(T_{Jmax})$  must never exceed the values given in *Table 18: General operating conditions on page 70.*

The maximum chip-junction temperature, T<sub>Jmax</sub>, in degree Celsius, may be calculated using the following equation:

$$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$$

Where:

- T<sub>Amax</sub> is the maximum ambient temperature in °C

- $\Theta_{IA}$  is the package junction-to-ambient thermal resistance in ° C/W

- P<sub>Dmax</sub> is the sum of P<sub>INTmax</sub> and P<sub>I/Omax</sub> (P<sub>Dmax</sub> = P<sub>INTmax</sub> + P<sub>I/Omax</sub>)

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum power dissipation on output pins Where:

$\mathsf{P}_{\mathsf{I}/\mathsf{Omax}} = \Sigma \; (\mathsf{V}_{\mathsf{OL}} * \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) * \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual  $V_{OL}/I_{OL}$  and  $V_{OH}/I_{OH}$  of the I/Os at low and high level in the application.

| Symbol | Parameter                                                   | Value | Unit |  |

|--------|-------------------------------------------------------------|-------|------|--|

| ΘJA    | Thermal resistance junction-ambient<br>LQFP 48 - 7 x 7 mm   | 65    |      |  |

|        | Thermal resistance junction-ambient<br>UFQFPN 48 - 7 x 7mm  | 32    |      |  |

|        | Thermal resistance junction-ambient<br>WLCSP32              | 63    | °C/W |  |

|        | Thermal resistance junction-ambient<br>LQFP 64 - 10 x 10 mm | 48    |      |  |

|        | Thermal resistance junction-ambient<br>LQFP 80 - 14 x 14 mm | 38    |      |  |

1. Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

# 10.2 LQFP64 package information

SEATING PLANE С 0.25 mm GAUGE PLANE ¥ G 7 D K D1 L1 D3 48 33 32 49 <u>A A A A A A A A A A A A A</u> b E3 Ш ш 64 17 ₽₽₽₽₽₽₽₽₽₽₽₽₽₽₽₽₽ 16 PIN 1 IDENTIFICATION 1 ⊾e 5W\_ME\_V3

Figure 51. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 64. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat |

|-------------------------------------------------------------|

| package mechanical data                                     |

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах   | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| Е      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

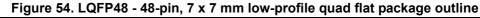

#### 10.3 LQFP48 package information

SEATING PLANE A2 ŨŦŨŦŨŦŨŦĬĦŮ<del>Ÿ</del>ŨŦŨŦŨŦŨŦŎŹ F 0.25 mm GAUGE PLANE ĸ D A1 D1 L1 D3 24 37 Œ b

8 E ш

13

12 e

**CHE**

Ē ----------

48

PIN 1 IDENTIFICATION 1

€

5B\_ME\_V2

<sup>1.</sup> Drawing is not to scale.

| Date        | Revision | Changes                                                                                                                                                                                                 |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-Feb-2017 | 10       | Updated value of feature 12-bit synchronized ADC (number of channels) for STM8L15xK8 on <i>Table 2: High-density and medium+ density STM8L15xx6/8 low power device features and peripheral counts</i> . |

Table 70. Document revision history (continued)