Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Active                                                               |

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, LCD, POR, PWM, WDT                  |

| Number of I/O              | 68                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 2K x 8                                                               |

| RAM Size                   | 4K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                          |

| Data Converters            | A/D 28x12b; D/A 2x12b                                                |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 80-LQFP                                                              |

| Supplier Device Package    | 80-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l152m8t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.2 Central processing unit STM8

# 3.2.1 Advanced STM8 Core

The 8-bit STM8 core is designed for code efficiency and performance with an Harvard architecture and a 3-stage pipeline.

It contains 6 internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing, and 80 instructions.

#### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16 Mbyte linear memory space

- 16-bit stack pointer access to a 64 Kbyte level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for lookup tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

#### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

# 3.2.2 Interrupt controller

The high-density and medium+ density STM8L15xx6/8x devices feature a nested vectored interrupt controller:

- Nested interrupts with 3 software priority levels

- 32 interrupt vectors with hardware priority

- Up to 40 external interrupt sources on 11 vectors

- Trap and reset interrupts

|           |        | Register label | Register label Register name      |      |

|-----------|--------|----------------|-----------------------------------|------|

| 0x00 500F |        | PD_ODR         | Port D data output latch register | 0x00 |

| 0x00 5010 |        | PD_IDR         | Port D input pin value register   | 0xXX |

| 0x00 5011 | Port D | PD_DDR         | Port D data direction register    | 0x00 |

| 0x00 5012 |        | PD_CR1         | Port D control register 1         | 0x00 |

| 0x00 5013 |        | PD_CR2         | Port D control register 2         | 0x00 |

| 0x00 5014 |        | PE_ODR         | Port E data output latch register | 0x00 |

| 0x00 5015 |        | PE_IDR         | Port E input pin value register   | 0xXX |

| 0x00 5016 | Port E | PE_DDR         | Port E data direction register    | 0x00 |

| 0x00 5017 |        | PE_CR1         | Port E control register 1         | 0x00 |

| 0x00 5018 |        | PE_CR2         | Port E control register 2         | 0x00 |

| 0x00 5019 |        | PF_ODR         | Port F data output latch register | 0x00 |

| 0x00 501A |        | PF_IDR         | Port F input pin value register   | 0xXX |

| 0x00 501B | Port F | PF_DDR         | Port F data direction register    | 0x00 |

| 0x00 501C | _      | PF_CR1         | Port F control register 1         | 0x00 |

| 0x00 501D |        | PF_CR2         | Port F control register 2         | 0x00 |

| 0x00 501E |        | PG_ODR         | Port F data output latch register | 0x00 |

| 0x00 501F |        | PG_IDR         | Port G input pin value register   | 0xXX |

| 0x00 5020 | Port G | PG_DDR         | Port G data direction register    | 0x00 |

| 0x00 5021 |        | PG_CR1         | Port G control register 1         | 0x00 |

| 0x00 5022 |        | PG_CR2         | Port G control register 2         | 0x00 |

| 0x00 5023 |        | PH_ODR         | Port H data output latch register | 0x00 |

| 0x00 5024 |        | PH_IDR         | Port H input pin value register   | 0xXX |

| 0x00 5025 | Port H | PH_DDR         | Port H data direction register    | 0x00 |

| 0x00 5026 |        | PH_CR1         | Port H control register 1         | 0x00 |

| 0x00 5027 |        | PH_CR2         | Port H control register 2         | 0x00 |

| 0x00 5028 |        | PI_ODR         | Port I data output latch register | 0x00 |

| 0x00 5029 |        | PI_IDR         | Port I input pin value register   | 0xXX |

| 0x00 502A | Port I | PI_DDR         | Port I data direction register    | 0x00 |

| 0x00 502B |        | PI_CR1         | Port I control register 1         | 0x00 |

| 0x00 502C |        | PI_CR2         | Port I control register 2         | 0x00 |

Table 8. I/O port hardware register map (continued)

| Table 9. General hardware register map (continued) |            |                |                                           |                     |  |

|----------------------------------------------------|------------|----------------|-------------------------------------------|---------------------|--|

| Address                                            | Block      | Register label | Register name                             | Reset status        |  |

| 0x00 509D                                          |            | SYSCFG_RMPCR3  | Remapping register 3                      | 0x00                |  |

| 0x00 509E                                          | SYSCFG     | SYSCFG_RMPCR1  | Remapping register 1                      | 0x00                |  |

| 0x00 509F                                          |            | SYSCFG_RMPCR2  | Remapping register 2                      | 0x00                |  |

| 0x00 50A0                                          |            | EXTI_CR1       | External interrupt control register 1     | 0x00                |  |

| 0x00 50A1                                          |            | EXTI_CR2       | External interrupt control register 2     | 0x00                |  |

| 0x00 50A2                                          | ITC - EXTI | EXTI_CR3       | External interrupt control register 3     | 0x00                |  |

| 0x00 50A3                                          |            | EXTI_SR1       | External interrupt status register 1      | 0x00                |  |

| 0x00 50A4                                          |            | EXTI_SR2       | External interrupt status register 2      | 0x00                |  |

| 0x00 50A5                                          |            | EXTI_CONF1     | External interrupt port select register 1 | 0x00                |  |

| 0x00 50A6                                          |            | WFE_CR1        | WFE control register 1                    | 0x00                |  |

| 0x00 50A7                                          |            | WFE_CR2        | WFE control register 2                    | 0x00                |  |

| 0x00 50A8                                          | WFE        | WFE_CR3        | WFE control register 3                    | 0x00                |  |

| 0x00 50A9                                          |            | WFE_CR4        | WFE control register 4                    | 0x00                |  |

| 0x00 50AA                                          |            | EXTI_CR4       | External interrupt control register 4     | 0x00                |  |

| 0x00 50AB                                          | ITC - EXTI | EXTI_CONF2     | External interrupt port select register 2 | 0x00                |  |

| 0x00 50A9<br>to<br>0x00 50AF                       |            |                | Reserved area (7 byte)                    |                     |  |

| 0x00 50B0                                          |            | RST_CR         | Reset control register                    | 0x00                |  |

| 0x00 50B1                                          | RST        | RST_SR         | Reset status register                     | 0x01                |  |

| 0x00 50B2                                          |            | PWR CSR1       | Power control and status register 1       | 0x00                |  |

| 0x00 50B3                                          | PWR        | PWR CSR2       | Power control and status register 2       | 0x00                |  |

| 0x00 50B4<br>to<br>0x00 50BF                       |            |                | Reserved area (12 byte)                   |                     |  |

| 0x00 50C0                                          |            | CLK_CKDIVR     | Clock master divider register             | 0x03                |  |

| 0x00 50C1                                          |            | CLK_CRTCR      | Clock RTC register                        | 0x00 <sup>(1)</sup> |  |

| 0x00 50C2                                          |            | CLK_ICKCR      | Internal clock control register           | 0x11                |  |

| 0x00 50C3                                          |            | CLK_PCKENR1    | Peripheral clock gating register 1        | 0x00                |  |

| 0x00 50C4                                          |            | CLK_PCKENR2    | Peripheral clock gating register 2        | 0x00                |  |

| 0x00 50C5                                          | - CLK      | CLK_CCOR       | Configurable clock control register       | 0x00                |  |

| 0x00 50C6                                          |            | CLK_ECKCR      | External clock control register           | 0x00                |  |

| 0x00 50C7                                          |            | CLK_SCSR       | System clock status register              | 0x01                |  |

| 0x00 50C8                                          |            | CLK_SWR        | System clock switch register              | 0x01                |  |

| 0x00 50C9                                          |            | CLK_SWCR       | Clock switch control register             | 0xX0                |  |

|                                                    |            |                |                                           |                     |  |

Table 9. General hardware register map (continued)

| Address                   | Block | Register label         | Register name                        | Reset status        |  |  |

|---------------------------|-------|------------------------|--------------------------------------|---------------------|--|--|

| 0x00 5148                 |       | RTC_CR1                | Control register 1                   | 0x00 <sup>(1)</sup> |  |  |

| 0x00 5149                 |       | RTC_CR2                | Control register 2                   | 0x00 <sup>(1)</sup> |  |  |

| 0x00 514A                 | - DTO | RTC_CR3                | Control register 3                   | 0x00 <sup>(1)</sup> |  |  |

| 0x00 514B                 | RTC   |                        | Reserved area (1 byte)               |                     |  |  |

| 0x00 514C                 |       | RTC_ISR1               | Initialization and status register 1 | 0x01                |  |  |

| 0x00 514D                 |       | RTC_ISR2               | Initialization and Status register 2 | 0x00                |  |  |

| 0x00 514E<br>0x00 514F    |       |                        | Reserved area (2 byte)               |                     |  |  |

| 0x00 5150                 |       | RTC_SPRERH             | Synchronous prescaler register high  | 0x00 <sup>(1)</sup> |  |  |

| 0x00 5151                 | RTC   | RTC_SPRERL             | Synchronous prescaler register low   | 0xFF <sup>(1)</sup> |  |  |

| 0x00 5152                 |       | RTC_APRER              | Asynchronous prescaler register      | 0x7F <sup>(1)</sup> |  |  |

| 0x00 5153                 |       |                        | Reserved area (1 byte)               | •                   |  |  |

| 0x00 5154                 | RTC   | RTC_WUTRH              | Wakeup timer register high           | 0xFF <sup>(1)</sup> |  |  |

| 0x00 5155                 |       | RTC_WUTRL              | Wakeup timer register low            | 0xFF <sup>(1)</sup> |  |  |

| 0x00 5156                 |       | Reserved area (1 byte) |                                      |                     |  |  |

| 0x00 5157                 |       | RTC_SSRL               | Subsecond register low               | 0x00                |  |  |

| 0x00 5158                 |       | RTC_SSRH               | Subsecond register high              | 0x00                |  |  |

| 0x00 5159                 |       | RTC_WPR                | Write protection register            | 0x00                |  |  |

| 0x00 5158                 |       | RTC_SSRH               | Subsecond register high              | 0x00                |  |  |

| 0x00 5159                 |       | RTC_WPR                | Write protection register            | 0x00                |  |  |

| 0x00 515A                 | RTC   | RTC_SHIFTRH            | Shift register high                  | 0x00                |  |  |

| 0x00 515B                 |       | RTC_SHIFTRL            | Shift register low                   | 0x00                |  |  |

| 0x00 515C                 |       | RTC_ALRMAR1            | Alarm A register 1                   | 0x00 <sup>(1)</sup> |  |  |

| 0x00 515D                 |       | RTC_ALRMAR2            | Alarm A register 2                   | 0x00 <sup>(1)</sup> |  |  |

| 0x00 515E                 |       | RTC_ALRMAR3            | Alarm A register 3                   | 0x00 <sup>(1)</sup> |  |  |

| 0x00 515F                 |       | RTC_ALRMAR4            | Alarm A register 4                   | 0x00 <sup>(1)</sup> |  |  |

| 0x00 5160 to<br>0x00 5163 |       | Reserved area (4 byte) |                                      |                     |  |  |

| 0x00 5164                 |       | RTC_ALRMASSRH          | Alarm A subsecond register high      | 0x00 <sup>(1)</sup> |  |  |

| 0x00 5165                 | RTC   | RTC_ALRMASSRL          | Alarm A subsecond register low       | 0x00 <sup>(1)</sup> |  |  |

| 0x00 5166                 |       | RTC_ALRMASSMS<br>KR    | Alarm A masking register             | 0x00 <sup>(1)</sup> |  |  |

| 0x00 5167 to<br>0x00 5169 |       |                        | Reserved area (3 byte)               |                     |  |  |

Table 9. General hardware register map (continued)

| Table 9. General | hardware regist | ter map (continued) |

|------------------|-----------------|---------------------|

|                  | naranaro rogio  |                     |

|                           | Table 9. General hardware register map (continued) |                |                                         |                     |  |  |

|---------------------------|----------------------------------------------------|----------------|-----------------------------------------|---------------------|--|--|

| Address                   | Block                                              | Register label | Register name                           | Reset status        |  |  |

| 0x00 516A                 |                                                    | RTC_CALRH      | Calibration register high               | 0x00 <sup>(1)</sup> |  |  |

| 0x00 516B                 | RTC                                                | RTC_CALRL      | Calibration register low                | 0x00 <sup>(1)</sup> |  |  |

| 0x00 516C                 | RIC                                                | RTC_TCR1       | Tamper control register 1               | 0x00 <sup>(1)</sup> |  |  |

| 0x00 516D                 |                                                    | RTC_TCR2       | Tamper control register 2               | 0x00 <sup>(1)</sup> |  |  |

| 0x00 516E to<br>0x00 518A |                                                    |                | Reserved area                           |                     |  |  |

| 0x00 5190                 | CSSLSE                                             | CSSLSE_CSR     | CSS on LSE control and status register  | 0x00 <sup>(1)</sup> |  |  |

| 0x00 519A to<br>0x00 51FF |                                                    |                | Reserved area                           |                     |  |  |

| 0x00 5200                 |                                                    | SPI1_CR1       | SPI1 control register 1                 | 0x00                |  |  |

| 0x00 5201                 |                                                    | SPI1_CR2       | SPI1 control register 2                 | 0x00                |  |  |

| 0x00 5202                 |                                                    | SPI1_ICR       | SPI1 interrupt control register         | 0x00                |  |  |

| 0x00 5203                 | 0.514                                              | SPI1_SR        | SPI1 status register                    | 0x02                |  |  |

| 0x00 5204                 | SPI1                                               | SPI1_DR        | SPI1 data register                      | 0x00                |  |  |

| 0x00 5205                 |                                                    | SPI1_CRCPR     | SPI1 CRC polynomial register            | 0x07                |  |  |

| 0x00 5206                 |                                                    | SPI1_RXCRCR    | SPI1 Rx CRC register                    | 0x00                |  |  |

| 0x00 5207                 |                                                    | SPI1_TXCRCR    | SPI1 Tx CRC register                    | 0x00                |  |  |

| 0x00 5208                 |                                                    |                | L                                       |                     |  |  |

| to<br>0x00 520F           |                                                    |                | Reserved area (8 byte)                  |                     |  |  |

| 0x00 5210                 |                                                    | I2C1_CR1       | I2C1 control register 1                 | 0x00                |  |  |

| 0x00 5211                 |                                                    | I2C1_CR2       | I2C1 control register 2                 | 0x00                |  |  |

| 0x00 5212                 |                                                    | I2C1_FREQR     | I2C1 frequency register                 | 0x00                |  |  |

| 0x00 5213                 |                                                    | I2C1_OARL      | I2C1 own address register low           | 0x00                |  |  |

| 0x00 5214                 |                                                    | I2C1_OARH      | I2C1 own address register high          | 0x00                |  |  |

| 0x00 5215                 |                                                    | I2C1_OARH      | I2C1 own address register for dual mode | 0x00                |  |  |

| 0x00 5216                 |                                                    | I2C1_DR        | I2C1 data register                      | 0x00                |  |  |

| 0x00 5217                 | I2C1                                               | I2C1_SR1       | I2C1 status register 1                  | 0x00                |  |  |

| 0x00 5218                 |                                                    | I2C1_SR2       | I2C1 status register 2                  | 0x00                |  |  |

| 0x00 5219                 |                                                    | I2C1_SR3       | I2C1 status register 3                  | 0x0X                |  |  |

| 0x00 521A                 |                                                    | I2C1_ITR       | I2C1 interrupt control register         | 0x00                |  |  |

| 0x00 521B                 |                                                    | I2C1_CCRL      | I2C1 clock control register low         | 0x00                |  |  |

| 0x00 521C                 |                                                    | I2C1_CCRH      | I2C1 clock control register high        | 0x00                |  |  |

| 0x00 521D                 |                                                    | I2C1_TRISER    | I2C1 TRISE register                     | 0x02                |  |  |

| 0x00 521E                 | 1                                                  | I2C1_PECR      | I2C1 packet error checking register     | 0x00                |  |  |

DocID17943 Rev 10

| Address                      | Block                  | Register label | Register name                             | Reset<br>status |  |

|------------------------------|------------------------|----------------|-------------------------------------------|-----------------|--|

| 0x00 7F90                    |                        | DM_BK1RE       | DM breakpoint 1 register extended byte    | 0xFF            |  |

| 0x00 7F91                    |                        | DM_BK1RH       | DM breakpoint 1 register high byte        | 0xFF            |  |

| 0x00 7F92                    |                        | DM_BK1RL       | DM breakpoint 1 register low byte         | 0xFF            |  |

| 0x00 7F93                    |                        | DM_BK2RE       | DM breakpoint 2 register extended byte    | 0xFF            |  |

| 0x00 7F94                    |                        | DM_BK2RH       | DM breakpoint 2 register high byte        | 0xFF            |  |

| 0x00 7F95                    | DM                     | DM_BK2RL       | DM breakpoint 2 register low byte         | 0xFF            |  |

| 0x00 7F96                    |                        | DM_CR1         | DM Debug module control register 1        | 0x00            |  |

| 0x00 7F97                    |                        | DM_CR2         | DM Debug module control register 2        | 0x00            |  |

| 0x00 7F98                    |                        | DM_CSR1        | DM Debug module control/status register 1 | 0x10            |  |

| 0x00 7F99                    |                        | DM_CSR2        | DM Debug module control/status register 2 | 0x00            |  |

| 0x00 7F9A                    |                        | DM_ENFCTR      | DM enable function register               | 0xFF            |  |

| 0x00 7F9B<br>to<br>0x00 7F9F | Reserved area (5 byte) |                |                                           |                 |  |

# Table 10. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

# 8 Unique ID

STM8 devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory.

- To activate secure boot processes

| Address | Content          | Unique ID bits             |             |   |     |          |   |          |   |

|---------|------------------|----------------------------|-------------|---|-----|----------|---|----------|---|

| Address | description      | 7                          | 6           | 5 | 4   | 3        | 2 | 1        | 0 |

| 0x4926  | X co-ordinate on |                            |             |   | U   | _ID[7:0] |   | <u>.</u> |   |

| 0x4927  | the wafer        |                            |             |   | U_  | ID[15:8] |   |          |   |

| 0x4928  | Y co-ordinate on |                            |             |   | U_I | D[23:16] |   |          |   |

| 0x4929  | the wafer        |                            | U_ID[31:24] |   |     |          |   |          |   |

| 0x492A  | Wafer number     | U_ID[39:32]                |             |   |     |          |   |          |   |

| 0x492B  |                  | U_ID[47:40]                |             |   |     |          |   |          |   |

| 0x492C  |                  | U_ID[55:48]<br>U_ID[63:56] |             |   |     |          |   |          |   |

| 0x492D  |                  |                            |             |   |     |          |   |          |   |

| 0x492E  | Lot number       | U_ID[71:64]                |             |   |     |          |   |          |   |

| 0x492F  | 1                | U_ID[79:72]<br>U_ID[87:80] |             |   |     |          |   |          |   |

| 0x4930  | 1                |                            |             |   |     |          |   |          |   |

| 0x4931  | 1                |                            | U_ID[95:88] |   |     |          |   |          |   |

#### Table 14. Unique ID registers (96 bits)

# 9 Electrical parameters

# 9.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

# 9.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A$ = 25 °C and  $T_A$  =  $T_A$  max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

# 9.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25 \degree C$ ,  $V_{DD} = 3 \lor V$ . They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

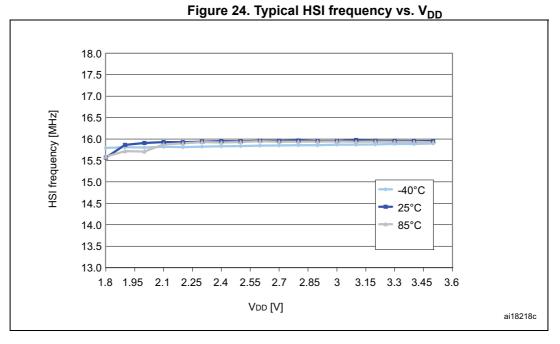

# 9.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 9.1.4 Loading capacitor

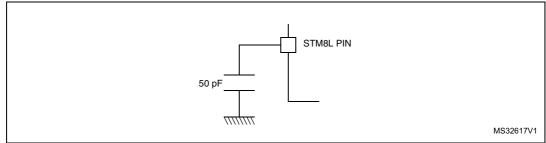

The loading conditions used for pin parameter measurement are shown in *Figure 11*.

| Symbol                 | Ratings                                                                     | Max.     | Unit |

|------------------------|-----------------------------------------------------------------------------|----------|------|

| I <sub>VDD</sub>       | Total current into V <sub>DD</sub> power line (source)                      | 80       |      |

| I <sub>VSS</sub>       | Total current out of V <sub>SS</sub> ground line (sink)                     | 80       |      |

|                        | Output current sunk by IR_TIM pin<br>(with high sink LED driver capability) | 80       |      |

| I <sub>IO</sub>        | Output current sunk by any other I/O and control pin                        | 25       |      |

|                        | Output current sourced by any I/Os and control pin                          | - 25     | mA   |

|                        | Injected current on true open-drain pins (PC0 and PC1) <sup>(1)</sup>       | - 5 / +0 |      |

| I <sub>INJ(PIN)</sub>  | Injected current on five-volt tolerant (FT) pins <sup>(1)</sup>             | - 5 / +0 |      |

|                        | Injected current on any other pin <sup>(2)</sup>                            | - 5 / +5 |      |

| ΣΙ <sub>INJ(PIN)</sub> | Total injected current (sum of all I/O and control pins) $^{(3)}$           | ± 25     |      |

| Table 16. Current characteris | stics |

|-------------------------------|-------|

|-------------------------------|-------|

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 15.* for maximum allowed input voltage values.

2. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 15*. for maximum allowed input voltage values.

3. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Table 17. Thermal characteristics |

|-----------------------------------|

|-----------------------------------|

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | C    |

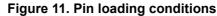

Figure 13. Power supply thresholds

In the following table, data are based on characterization results, unless otherwise specified.

|                       | Parameter                         | Conditions <sup>(1)</sup>                                                                                                                                         |                                     | Тур                                 | Max   |              |                     |                     |                     |    |

|-----------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------|-------|--------------|---------------------|---------------------|---------------------|----|

| Symbol                |                                   |                                                                                                                                                                   |                                     |                                     | 55°C  | 85 °C<br>(2) | 105 °C<br>(3)       | 125 °C<br>(4)       | Unit                |    |

|                       |                                   |                                                                                                                                                                   |                                     | f <sub>CPU</sub> = 125 kHz          | 0.21  | 0.29         | 0.33                | 0.36                | 0.43                |    |

|                       |                                   |                                                                                                                                                                   |                                     | f <sub>CPU</sub> = 1 MHz            | 0.25  | 0.33         | 0.37                | 0.4                 | 0.47                |    |

|                       | Supply<br>current in<br>Wait mode | HSI<br>CPU not                                                                                                                                                    | HSI                                 | f <sub>CPU</sub> = 4 MHz            | 0.32  | 0.4          | 0.44                | 0.47                | 0.54                |    |

|                       |                                   |                                                                                                                                                                   | f <sub>CPU</sub> = 8 MHz            | 0.42                                | 0.496 | 0.54         | 0.56                | 0.64                |                     |    |

|                       |                                   | clocked,                                                                                                                                                          | locked,                             | f <sub>CPU</sub> = 16 MHz           | 0.66  | 0.736        | 0.78 <sup>(6)</sup> | 0.8 <sup>(6)</sup>  | 0.88 <sup>(6)</sup> | mA |

|                       |                                   | all peripherals<br>OFF,                                                                                                                                           |                                     | f <sub>CPU</sub> = 125 kHz          | 0.19  | 0.21         | 0.3                 | 0.35                | 0.41                |    |

|                       |                                   | Vait mode RAM<br>Vait mode RAM<br>Vait mode $P_{DDQ}$ mode, <sup>(5)</sup><br>V <sub>DD</sub> from<br>1.65 V to<br>3.6 V<br>LSI<br>LSE <sup>(8)</sup><br>external |                                     | f <sub>CPU</sub> = 1 MHz            | 0.2   | 0.23         | 0.32                | 0.36                | 0.43                |    |

| I <sub>DD(Wait)</sub> |                                   |                                                                                                                                                                   | clock f                             | f <sub>CPU</sub> = 4 MHz            | 0.27  | 0.3          | 0.39                | 0.43                | 0.5                 |    |

|                       |                                   |                                                                                                                                                                   |                                     | f <sub>CPU</sub> = 8 MHz            | 0.37  | 0.4          | 0.49                | 0.53                | 0.6                 |    |

|                       |                                   |                                                                                                                                                                   |                                     | f <sub>CPU</sub> = 16 MHz           | 0.63  | 0.66         | 0.75 <sup>(6)</sup> | 0.79 <sup>(6)</sup> | 0.86 <sup>(6)</sup> |    |

|                       |                                   |                                                                                                                                                                   | LSI                                 | f <sub>CPU</sub> = f <sub>LSI</sub> | 0.028 | 0.037        | 0.039               | 0.044               | 0.054               |    |

|                       |                                   |                                                                                                                                                                   | f <sub>CPU</sub> = f <sub>LSE</sub> | 0.027                               | 0.035 | 0.038        | 0.042               | 0.051               |                     |    |

Table 21. Total current consumption in Wait mode

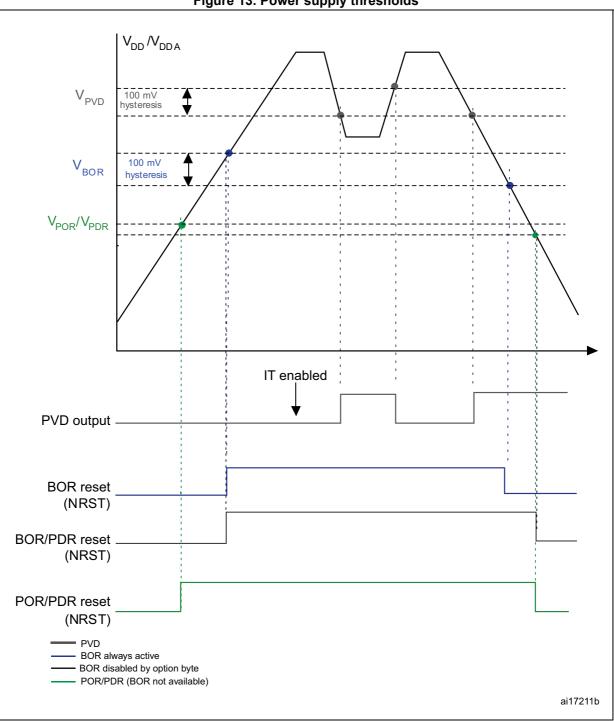

Figure 19. Typical  $I_{DD(LPW)}$  vs.  $V_{DD}$  (LSI clock source), all peripherals OFF

1. Typical current consumption measured with code executed from RAM.

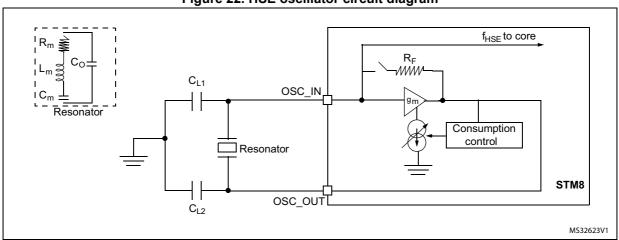

#### Figure 22. HSE oscillator circuit diagram

### HSE oscillator critical g<sub>m</sub> formula

$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$

$R_m$ : Motional resistance (see crystal specification),  $L_m$ : Motional inductance (see crystal specification),  $C_m$ : Motional capacitance (see crystal specification), Co: Shunt capacitance (see crystal specification),  $C_{L1}=C_{L2}=C$ : Grounded external capacitance  $g_m >> g_{mcrit}$

#### LSE crystal/ceramic resonator oscillator

The LSE is available on STM8L151x6/8 and STM8L152x6/8 devices.

The LSE clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                              | Parameter                                  | Conditions              | Min.             | Тур.   | Max. | Unit |

|-------------------------------------|--------------------------------------------|-------------------------|------------------|--------|------|------|

| f <sub>LSE</sub>                    | Low speed external oscillator<br>frequency |                         |                  | 32.768 |      | kHz  |

| R <sub>F</sub>                      | Feedback resistor                          | ∆V = 200 mV             |                  | 1.2    |      | MΩ   |

| C <sup>(1)(2)</sup>                 | Recommended load capacitance               |                         |                  | 8      |      | pF   |

|                                     |                                            | V <sub>DD</sub> = 1.8 V |                  | 450    |      |      |

| I <sub>DD(LSE)</sub>                | LSE oscillator power consumption           | V <sub>DD</sub> = 3 V   |                  | 600    |      | nA   |

|                                     |                                            | V <sub>DD</sub> = 3.6 V |                  | 750    |      |      |

| 9 <sub>m</sub>                      | Oscillator transconductance                |                         | 3 <sup>(3)</sup> |        |      | µA/V |

| t <sub>SU(LSE)</sub> <sup>(4)</sup> | Startup time                               | $V_{DD}$ is stabilized  |                  | 1      |      | S    |

| Table 32. LSE oscilla | tor characteristics |

|-----------------------|---------------------|

|-----------------------|---------------------|

1.  $C=C_{L1}=C_{L2}$  is approximately equivalent to 2 x crystal  $C_{LOAD}$ .

3. Guaranteed by design.

<sup>2.</sup> The oscillator selection can be optimized in terms of supply current using a high quality resonator with a small R<sub>m</sub> value. Refer to crystal manufacturer for more details.

#### 4. Guaranteed by design.

# Low speed internal RC oscillator (LSI)

In the following table, data are based on characterization results.

| Symbol               | Parameter                                     | Conditions <sup>(1)</sup>    | Min. | Тур. | Max.               | Unit |

|----------------------|-----------------------------------------------|------------------------------|------|------|--------------------|------|

| f <sub>LSI</sub>     | Frequency                                     |                              | 26   | 38   | 56                 | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time                    |                              |      |      | 200 <sup>(2)</sup> | μs   |

| D <sub>(LSI)</sub>   | LSI oscillator frequency drift <sup>(3)</sup> | 0 °C ≤T <sub>A</sub> ≤ 85 °C | -12  |      | 11                 | %    |

1.  $V_{DD}$  = 1.65 V to 3.6 V,  $T_A$  = -40 to 125 °C unless otherwise specified.

2. Guaranteed by design.

3. This is a deviation for an individual part, once the initial frequency has been measured.

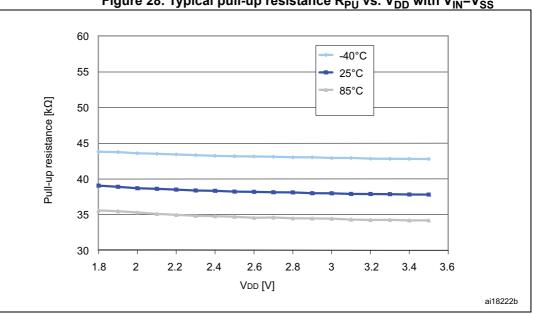

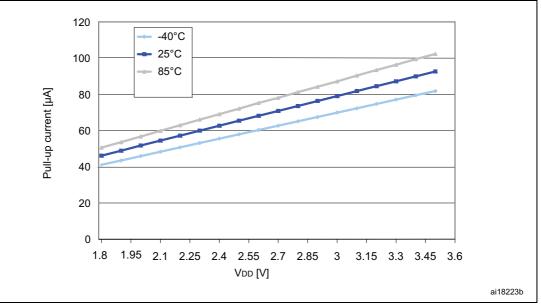

Figure 28. Typical pull-up resistance  $R_{PU}$  vs.  $V_{DD}$  with  $V_{IN}=V_{SS}$

## **Output driving current**

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                     | Parameter                                     | Conditions                                                                                                                                                    | Min  | Тур | Max <sup>(1)</sup> | Unit       |  |

|----------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------------|--|

| V <sub>DDA</sub>           | Analog supply voltage                         | -                                                                                                                                                             | 1.65 |     | 3.6                | V          |  |

| V <sub>IN</sub>            | Comparator 2 input voltage range              | -                                                                                                                                                             | 0    |     | $V_{DDA}$          | V          |  |

| t                          | Comparator startup time                       | Fast mode                                                                                                                                                     | -    | 15  | 20                 |            |  |

| t <sub>START</sub>         |                                               | Slow mode                                                                                                                                                     | -    | 20  | 25                 |            |  |

| t                          | Propagation delay <sup>(2)</sup> in slow mode | $1.65~V \leq V_{DDA} \leq 2.7~V$                                                                                                                              | -    | 1.8 | 3.5                | μs         |  |

| t <sub>d slow</sub>        | Propagation delay. In slow mode               | $2.7~V \leq V_{DDA} \leq 3.6~V$                                                                                                                               | -    | 2.5 | 6                  |            |  |

| +                          | Propagation delay <sup>(2)</sup> in fast mode | $1.65~V \leq V_{DDA} \leq 2.7~V$                                                                                                                              | -    | 0.8 | 2                  |            |  |

| t <sub>d fast</sub>        | Propagation delay. In fast mode               | $2.7 \text{ V} \leq \text{V}_{\text{DDA}} \leq 3.6 \text{ V}$                                                                                                 | -    | 1.2 | 4                  |            |  |

| V <sub>offset</sub>        | Comparator offset error                       | -                                                                                                                                                             | -    | ±4  | <u>+2</u> 0        | mV         |  |

| d <sub>Threshold</sub> /dt | Threshold voltage temperature coefficient     | $\begin{split} V_{DDA} &= 3.3V \\ T_A &= 0 \text{ to } 50 ^{\circ}\text{C} \\ V &= V_{REF+},  3/4 \\ V_{REF+}, \\ 1/2  V_{REF+},  1/4  V_{REF+}. \end{split}$ | -    | 15  | 30                 | ppm<br>/°C |  |

|                            | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                                     | -    | 3.5 | 5                  | μA         |  |

| ICOMP2                     |                                               | Slow mode                                                                                                                                                     | -    | 0.5 | 2                  | μΛ         |  |

Table 49. Comparator 2 characteristics

1. Based on characterization.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (necessary for comparator operation) is not included.

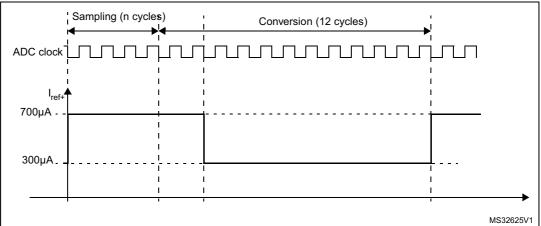

# Figure 45. Maximum dynamic current consumption on V<sub>REF+</sub> supply pin during ADC conversion

|                | Ts<br>(µs) | R <sub>AIN</sub> max (kohm)      |                                  |                                  |                                  |  |  |

|----------------|------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|--|--|

| Ts<br>(cycles) |            | Slow cl                          | hannels                          | Fast channels                    |                                  |  |  |

|                | . ,        | 2.4 V < V <sub>DDA</sub> < 3.6 V | 1.8 V < V <sub>DDA</sub> < 2.4 V | 2.4 V < V <sub>DDA</sub> < 3.3 V | 1.8 V < V <sub>DDA</sub> < 2.4 V |  |  |

| 4              | 0.25       | Not allowed                      | Not allowed                      | 0.7                              | Not allowed                      |  |  |

| 9              | 0.5625     | 0.8                              | Not allowed                      | 2.0                              | 1.0                              |  |  |

| 16             | 1          | 2.0                              | 0.8                              | 4.0                              | 3.0                              |  |  |

| 24             | 1.5        | 3.0                              | 1.8                              | 6.0                              | 4.5                              |  |  |

| 48             | 3          | 6.8                              | 4.0                              | 15.0                             | 10.0                             |  |  |

| 96             | 6          | 15.0                             | 10.0                             | 30.0                             | 20.0                             |  |  |

| 192            | 12         | 32.0                             | 25.0                             | 50.0                             | 40.0                             |  |  |

| 384            | 24         | 50.0                             | 50.0                             | 50.0                             | 50.0                             |  |  |

# Table 57. $R_{AIN}$ max for $f_{ADC} = 16 \text{ MHz}^{(1)}$

1. Guaranteed by design.

#### General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 46* or *Figure 47*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. Good quality ceramic 10 nF capacitors should be used. They should be placed as close as possible to the chip.

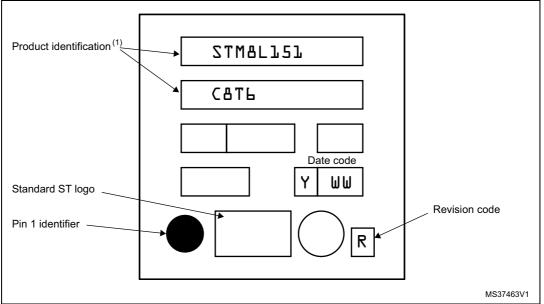

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 56. LQFP48 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Date        | Revision | 70. Document revision history (continued) Changes                                                                                                                                               |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision | -                                                                                                                                                                                               |

|             |          | <ul> <li>Updated</li> <li>Table 63: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data,</li> <li>Figure 48: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat</li> </ul> |

|             |          | package outline,<br>– Figure 49: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat                                                                                                              |

|             |          | <ul> <li>– Table 64: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package</li> </ul>                                                                                                       |

|             |          | mechanical data,                                                                                                                                                                                |

|             |          | <ul> <li>Figure 51: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat<br/>package outline,</li> </ul>                                                                                           |

|             |          | <ul> <li>Figure 52: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat<br/>package recommended footprint,</li> </ul>                                                                             |

| 19-Feb-2015 | 7        | <ul> <li>Table 65: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package<br/>mechanical data,</li> </ul>                                                                                      |

|             |          | <ul> <li>Figure 54: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package<br/>outline.</li> </ul>                                                                                             |

|             |          | <ul> <li>Table 66: UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine<br/>pitch quad flat package mechanical data,</li> </ul>                                                            |

|             |          | <ul> <li>Figure 57: UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin<br/>fine pitch quad flat package outline,</li> </ul>                                                                   |

|             |          | – Figure 58: UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin                                                                                                                               |

|             |          | fine pitch quad flat package recommended footprint.<br>Added:                                                                                                                                   |

|             |          | <ul> <li>Figure 50: LQFP80 marking example (package top view)</li> </ul>                                                                                                                        |

|             |          | <ul> <li>Figure 53: LQFP64 marking example (package top view)</li> </ul>                                                                                                                        |

|             |          | <ul> <li>Figure 56: LQFP48 marking example (package top view)</li> </ul>                                                                                                                        |

|             |          | <ul> <li>Figure 59: UFQFPN48 marking example (package top view)</li> </ul>                                                                                                                      |

|             |          | Added                                                                                                                                                                                           |

|             |          | - Figure 9: STM8L152K8 32-ball ballout and the related warning,                                                                                                                                 |

|             |          | <ul> <li>Section 10.5: WLCSP32 package information.</li> </ul>                                                                                                                                  |

|             |          | Updated:                                                                                                                                                                                        |

|             |          | - Table 1: Device summary,                                                                                                                                                                      |

| 07-Sep-2015 | 8        | <ul> <li>Table 2: High-density and medium+ density STM8L15xx6/8 low<br/>power device features and peripheral counts,</li> </ul>                                                                 |

| 07-36p-2013 | 0        | - Table 5: High-density and medium+ density STM8L15x pin                                                                                                                                        |

|             |          | description,                                                                                                                                                                                    |

|             |          | <ul> <li>Table 18: General operating conditions,</li> </ul>                                                                                                                                     |

|             |          | <ul> <li>Table 60: ESD absolute maximum ratings,</li> </ul>                                                                                                                                     |

|             |          | <ul> <li>Table 62: Thermal characteristics,</li> </ul>                                                                                                                                          |

|             |          | <ul> <li>Table 69: Ordering information scheme.</li> </ul>                                                                                                                                      |

| 08-Dec-2016 | 9        | Updated TIM3 channel 3 to TIM3 channel 1 (LQFP80 pin 77) and SPI2 clock to SPI1 clock (LQFP80 pin 51) in <i>Table 5: High-density and medium+ density STM8L15x pin description</i> .            |

|             |          | Updated BOR_TH reference (OPT5) in <i>Table 13: Option byte description</i> .                                                                                                                   |

| Date        | Revision Changes |                                                                                                                                                                                                         |  |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15-Feb-2017 | 10               | Updated value of feature 12-bit synchronized ADC (number of channels) for STM8L15xK8 on <i>Table 2: High-density and medium+ density STM8L15xx6/8 low power device features and peripheral counts</i> . |  |

Table 70. Document revision history (continued)