Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                  |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 22                                                          |

| Program Memory Size        | 32KB (32K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 2K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 6x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-LQFP                                                     |

| Supplier Device Package    | 32-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08ac32cfje |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Section Number**

Title

## Page

| 4.2 | Register | r Addresses and Bit Assignments              | 44 |

|-----|----------|----------------------------------------------|----|

| 4.3 | RAM      | -                                            | 50 |

| 4.4 | FLASH    |                                              | 51 |

|     | 4.4.1    | Features                                     | 51 |

|     | 4.4.2    | Program and Erase Times                      | 51 |

|     | 4.4.3    | Program and Erase Command Execution          | 52 |

|     | 4.4.4    | Burst Program Execution                      | 54 |

|     | 4.4.5    | Access Errors                                | 57 |

|     | 4.4.6    | FLASH Block Protection                       | 57 |

|     | 4.4.7    | Vector Redirection                           | 58 |

| 4.5 | Security | /                                            | 58 |

| 4.6 | FLASH    | Registers and Control Bits                   | 59 |

|     | 4.6.1    | FLASH Clock Divider Register (FCDIV)         | 59 |

|     | 4.6.2    | FLASH Options Register (FOPT and NVOPT)      | 61 |

|     | 4.6.3    | FLASH Configuration Register (FCNFG)         | 61 |

|     | 4.6.4    | FLASH Protection Register (FPROT and NVPROT) | 63 |

|     | 4.6.5    | FLASH Status Register (FSTAT)                | 63 |

|     | 4.6.6    | FLASH Command Register (FCMD)                | 64 |

# Chapter 5 Resets, Interrupts, and System Configuration

| 5.1 | Introdu  | ction                                                     | 67 |

|-----|----------|-----------------------------------------------------------|----|

| 5.2 | Feature  | s                                                         | 67 |

| 5.3 | MCU R    | leset                                                     | 67 |

| 5.4 | Comput   | ter Operating Properly (COP) Watchdog                     | 68 |

| 5.5 | Interrup | ots                                                       | 69 |

|     | 5.5.1    | Interrupt Stack Frame                                     | 70 |

|     | 5.5.2    | External Interrupt Request (IRQ) Pin                      | 70 |

|     | 5.5.3    | Interrupt Vectors, Sources, and Local Masks               | 71 |

| 5.6 | Low-Vo   | bltage Detect (LVD) System                                | 73 |

|     | 5.6.1    | Power-On Reset Operation                                  | 73 |

|     | 5.6.2    | LVD Reset Operation                                       | 73 |

|     | 5.6.3    | LVD Interrupt Operation                                   | 73 |

|     | 5.6.4    | Low-Voltage Warning (LVW)                                 | 73 |

| 5.7 | Real-Ti  | me Interrupt (RTI)                                        | 73 |

| 5.8 | MCLK     | Output                                                    | 74 |

| 5.9 | Reset, I | nterrupt, and System Control Registers and Control Bits   | 74 |

|     | 5.9.1    | Interrupt Pin Request Status and Control Register (IRQSC) | 75 |

|     | 5.9.2    | System Reset Status Register (SRS)                        | 76 |

|     | 5.9.3    | System Background Debug Force Reset Register (SBDFR)      | 77 |

|     | 5.9.4    | System Options Register (SOPT)                            | 77 |

|     | 5.9.5    | System MCLK Control Register (SMCLK)                      |    |

|     |          |                                                           |    |

## **Section Number**

## Title

## Page

| 5.9.6  | System Device Identification Register (SDIDH, SDIDL)            | 79 |

|--------|-----------------------------------------------------------------|----|

| 5.9.7  | System Real-Time Interrupt Status and Control Register (SRTISC) | 80 |

| 5.9.8  | System Power Management Status and Control 1 Register (SPMSC1)  |    |

| 5.9.9  | System Power Management Status and Control 2 Register (SPMSC2)  |    |

| 5.9.10 | System Options Register 2 (SOPT2)                               |    |

## Chapter 6 Parallel Input/Output

| 6.1 | Introduc | tion                                               |  |

|-----|----------|----------------------------------------------------|--|

| 6.2 | Pin Dese | criptions                                          |  |

| 6.3 | Parallel | I/O Control                                        |  |

| 6.4 | Pin Con  | trol                                               |  |

|     | 6.4.1    | Internal Pullup Enable                             |  |

|     | 6.4.2    | Output Slew Rate Control Enable                    |  |

|     | 6.4.3    | Output Drive Strength Select                       |  |

| 6.5 | Pin Beh  | avior in Stop Modes                                |  |

| 6.6 | Parallel | I/O and Pin Control Registers                      |  |

|     |          | Port A I/O Registers (PTAD and PTADD)              |  |

|     |          | Port A Pin Control Registers (PTAPE, PTASE, PTADS) |  |

|     |          | Port B I/O Registers (PTBD and PTBDD)              |  |

|     | 6.6.4    | Port B Pin Control Registers (PTBPE, PTBSE, PTBDS) |  |

|     | 6.6.5    | Port C I/O Registers (PTCD and PTCDD)              |  |

|     | 6.6.6    | Port C Pin Control Registers (PTCPE, PTCSE, PTCDS) |  |

|     | 6.6.7    | Port D I/O Registers (PTDD and PTDDD)              |  |

|     | 6.6.8    | Port D Pin Control Registers (PTDPE, PTDSE, PTDDS) |  |

|     | 6.6.9    | Port E I/O Registers (PTED and PTEDD)              |  |

|     |          | Port E Pin Control Registers (PTEPE, PTESE, PTEDS) |  |

|     |          | Port F I/O Registers (PTFD and PTFDD)              |  |

|     |          | Port F Pin Control Registers (PTFPE, PTFSE, PTFDS) |  |

|     |          | Port G I/O Registers (PTGD and PTGDD)              |  |

|     |          | Port G Pin Control Registers (PTGPE, PTGSE, PTGDS) |  |

# Chapter 7 Central Processor Unit (S08CPUV2)

| 7.1 | Introdu | ction                          | 109 |

|-----|---------|--------------------------------|-----|

|     | 7.1.1   | Features                       | 109 |

| 7.2 | Progran | nmer's Model and CPU Registers | 110 |

|     | _       | Accumulator (A)                |     |

|     |         | Index Register (H:X)           |     |

|     | 7.2.3   | Stack Pointer (SP)             | 111 |

|     | 7.2.4   | Program Counter (PC)           | 111 |

|     | 7.2.5   | Condition Code Register (CCR)  | 111 |

|     |         |                                |     |

## **Section Number**

## Title

## Page

|     | 9.3.4     | Voltage Reference Low (V <sub>REFL</sub> ) | 143 |

|-----|-----------|--------------------------------------------|-----|

|     | 9.3.5     | Analog Channel Inputs (ADx)                | 143 |

| 9.4 | Registe   | r Definition                               | 143 |

|     | 9.4.1     | Status and Control Register 1 (ADCSC1)     | 143 |

|     | 9.4.2     | Status and Control Register 2 (ADCSC2)     | 145 |

|     | 9.4.3     | Data Result High Register (ADCRH)          |     |

|     | 9.4.4     | Data Result Low Register (ADCRL)           |     |

|     | 9.4.5     | Compare Value High Register (ADCCVH)       | 147 |

|     | 9.4.6     | Compare Value Low Register (ADCCVL)        | 147 |

|     | 9.4.7     | Configuration Register (ADCCFG)            | 147 |

|     | 9.4.8     | Pin Control 1 Register (APCTL1)            |     |

|     | 9.4.9     | Pin Control 2 Register (APCTL2)            | 150 |

|     | 9.4.10    | Pin Control 3 Register (APCTL3)            | 151 |

| 9.5 | Functio   | nal Description                            | 152 |

|     | 9.5.1     | Clock Select and Divide Control            | 152 |

|     | 9.5.2     | Input Select and Pin Control               | 153 |

|     | 9.5.3     | Hardware Trigger                           | 153 |

|     | 9.5.4     | Conversion Control                         | 153 |

|     | 9.5.5     | Automatic Compare Function                 | 156 |

|     | 9.5.6     | MCU Wait Mode Operation                    | 156 |

|     | 9.5.7     | MCU Stop3 Mode Operation                   | 156 |

|     | 9.5.8     | MCU Stop1 and Stop2 Mode Operation         | 157 |

| 9.6 | Initializ | ation Information                          | 157 |

|     | 9.6.1     | ADC Module Initialization Example          | 157 |

| 9.7 |           | tion Information                           |     |

|     | 9.7.1     | External Pins and Routing                  | 159 |

|     |           | Sources of Error                           |     |

# Chapter 10 Internal Clock Generator (S08ICGV4)

| 10.1 | Introduction                                               |  |

|------|------------------------------------------------------------|--|

|      | 10.1.1 Features                                            |  |

|      | 10.1.2 Modes of Operation                                  |  |

|      | 10.1.3 Block Diagram                                       |  |

| 10.2 | External Signal Description                                |  |

|      | 10.2.1 EXTAL — External Reference Clock / Oscillator Input |  |

|      | 10.2.2 XTAL — Oscillator Output                            |  |

|      | 10.2.3 External Clock Connections                          |  |

|      | 10.2.4 External Crystal/Resonator Connections              |  |

| 10.3 | Register Definition                                        |  |

|      | 10.3.1 ICG Control Register 1 (ICGC1)                      |  |

|      | 10.3.2 ICG Control Register 2 (ICGC2)                      |  |

|      |                                                            |  |

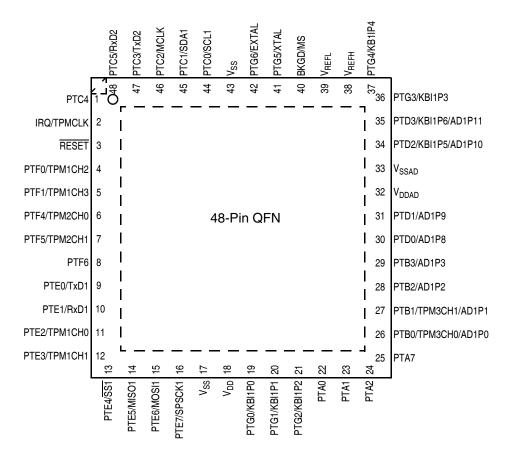

Figure 2-2. MC9S08AC60 Series in 48-Pin QFN Package

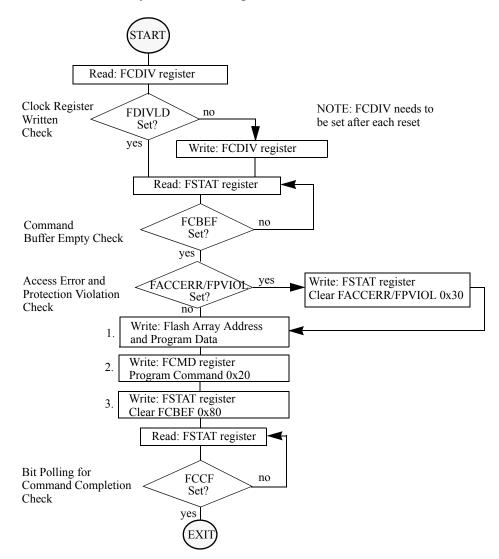

FCBEF to launch the command. The FCDIV register must be initialized before using any FLASH commands. This must be done only once following a reset.

Figure 4-2. Example Program Command Flow

Chapter 5 Resets, Interrupts, and System Configuration

Either RTI clock source can be used when the MCU is in run, wait or stop3 mode. When using the external oscillator in stop3, it must be enabled in stop (OSCSTEN = 1) and configured for low bandwidth operation (RANGE = 0). Only the internal 1-kHz clock source can be selected to wake the MCU from stop2 mode.

The SRTISC register includes a read-only status flag, a write-only acknowledge bit, and a 3-bit control value (RTIS2:RTIS1:RTIS0) used to disable the clock source to the real-time interrupt or select one of seven wakeup periods. The RTI has a local interrupt enable, RTIE, to allow masking of the real-time interrupt. The RTI can be disabled by writing each bit of RTIS to zeroes, and no interrupts will be generated. See Section 5.9.7, "System Real-Time Interrupt Status and Control Register (SRTISC)," for detailed information about this register.

# 5.8 MCLK Output

The PTC2 pin is shared with the MCLK clock output. Setting the pin enable bit, MPE, causes the PTC2 pin to output a divided version of the internal MCU bus clock. The divide ratio is determined by the MCSEL bits. When MPE is set, the PTC2 pin is forced to operate as an output pin regardless of the state of the port data direction control bit for the pin. If the MCSEL bits are all 0s, the pin is driven low. The slew rate and drive strength for the pin are controlled by PTCSE2 and PTCDS2, respectively. The maximum clock output frequency is limited if slew rate control is enabled, see the electrical chapter for pin rise and fall times with slew rate enabled.

# 5.9 Reset, Interrupt, and System Control Registers and Control Bits

One 8-bit register in the direct page register space and eight 8-bit registers in the high-page register space are related to reset and interrupt systems.

Refer to the direct-page register summary in Chapter 4, "Memory," of this data sheet for the absolute address assignments for all registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some control bits in the SOPT and SPMSC2 registers are related to modes of operation. Although brief descriptions of these bits are provided here, the related functions are discussed in greater detail in Chapter 3, "Modes of Operation."

## 6.4.1 Internal Pullup Enable

An internal pullup device can be enabled for each port pin by setting the corresponding bit in one of the pullup enable registers (PTxPEn). The pullup device is disabled if the pin is configured as an output by the parallel I/O control logic or any shared peripheral function regardless of the state of the corresponding pullup enable register bit. The pullup device is also disabled if the pin is controlled by an analog function.

## 6.4.2 Output Slew Rate Control Enable

Slew rate control can be enabled for each port pin by setting the corresponding bit in one of the slew rate control registers (PTxSEn). When enabled, slew control limits the rate at which an output can transition in order to reduce EMC emissions. Slew rate control has no effect on pins which are configured as inputs.

## 6.4.3 Output Drive Strength Select

An output pin can be selected to have high output drive strength by setting the corresponding bit in one of the drive strength select registers (PTxDSn). When high drive is selected a pin is capable of sourcing and sinking greater current. Even though every I/O pin can be selected as high drive, the user must ensure that the total current source and sink limits for the chip are not exceeded. Drive strength selection is intended to affect the DC behavior of I/O pins. However, the AC behavior is also affected. High drive allows a pin to drive a greater load with the same switching speed as a low drive enabled pin into a smaller load. Because of this the EMC emissions may be affected by enabling pins as high drive.

#### Chapter 6 Parallel Input/Output

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBDS7 | PTBDS6 | PTBDS5 | PTBDS4 | PTBDS3 | PTBDS2 | PTBDS1 | PTBDS0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

ī.

## Figure 6-11. Internal Drive Strength Selection for Port B (PTBDS)

## Table 6-10. PTBDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBDS[7:0] | <ul> <li>Output Drive Strength Selection for Port B Bits — Each of these control bits selects between low and high output drive for the associated PTB pin.</li> <li>0 Low output drive enabled for port B bit n.</li> <li>1 High output drive enabled for port B bit n.</li> </ul> |

Chapter 6 Parallel Input/Output

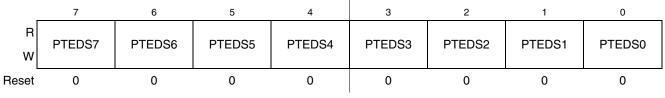

## Figure 6-26. Output Drive Strength Selection for Port E (PTEDS)

## Table 6-25. PTEDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTEDS[7:0] | <ul> <li>Output Drive Strength Selection for Port E Bits — Each of these control bits selects between low and high output drive for the associated PTE pin.</li> <li>0 Low output drive enabled for port E bit n.</li> <li>1 High output drive enabled for port E bit n.</li> </ul> |

Cyclic Redundancy Check (S08CRCV1)

# 8.3 Register Definition

## 8.3.1 Memory Map

Table 8-1. CRC Register Summary

| Name |        | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|------|--------|--------|--------|--------|--------|--------|--------|-------|-------|

| CRCH | R<br>W | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| CRCL | R<br>W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

## 8.3.2 Register Descriptions

The CRC module includes:

• A 16-bit CRC result and seed register (CRCH:CRCL)

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all CRC registers. This section refers to registers only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

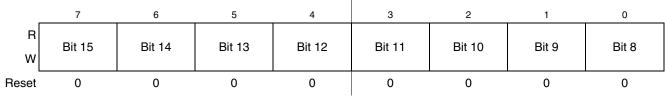

## 8.3.2.1 CRC High Register (CRCH)

## Figure 8-3. CRC High Register (CRCH)

#### Table 8-2. Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>CRCH | <b>CRCH</b> This is the high byte of the 16-bit CRC register. A write to CRCH will load the high byte of the initial 16-bit seed value directly into bits 15-8 of the shift register in the CRC generator. The CRC generator will then expect the low byte of the seed value to be written to CRCL and loaded directly into bits 7-0 of the shift register. Once both seed bytes written to CRCH:CRCL have been loaded into the CRC generator, and a byte of data has been written to CRCL, the shift register will begin shifting. A read of CRCH will read bits 15-8 of the current CRC calculation result directly out of the shift register in the CRC generator. |

#### Analog-to-Digital Converter (S08ADC10V1)

- 2. Update status and control register 2 (ADCSC2) to select the conversion trigger (hardware or software) and compare function options, if enabled.

- 3. Update status and control register 1 (ADCSC1) to select whether conversions will be continuous or completed only once, and to enable or disable conversion complete interrupts. The input channel on which conversions will be performed is also selected here.

## 9.6.1.2 Pseudo — Code Example

In this example, the ADC module will be set up with interrupts enabled to perform a single 10-bit conversion at low power with a long sample time on input channel 1, where the internal ADCK clock will be derived from the bus clock divided by 1.

## ADCCFG = 0x98 (%10011000)

| Bit 7   | ADLPC  | 1  | Configures for low power (lowers maximum clock speed) |

|---------|--------|----|-------------------------------------------------------|

| Bit 6:5 | ADIV   | 00 | Sets the ADCK to the input clock $\div$ 1             |

| Bit 4   | ADLSMP | 1  | Configures for long sample time                       |

| Bit 3:2 | MODE   | 10 | Sets mode at 10-bit conversions                       |

| Bit 1:0 | ADICLK | 00 | Selects bus clock as input clock source               |

|         |        |    |                                                       |

## ADCSC2 = 0x00 (%00000000)

| Bit 7   | ADACT | 0  | Flag indicates if a conversion is in progress |

|---------|-------|----|-----------------------------------------------|

| Bit 6   | ADTRG | 0  | Software trigger selected                     |

| Bit 5   | ACFE  | 0  | Compare function disabled                     |

| Bit 4   | ACFGT | 0  | Not used in this example                      |

| Bit 3:2 |       | 00 | Unimplemented or reserved, always reads zero  |

| Bit 1:0 |       | 00 | Reserved for internal use; always write zero  |

#### ADCSC1 = 0x41 (%01000001)

| Bit 7   | COCO | 0     | Read-only flag which is set when a conversion completes |

|---------|------|-------|---------------------------------------------------------|

| Bit 6   | AIEN | 1     | Conversion complete interrupt enabled                   |

| Bit 5   | ADCO | 0     | One conversion only (continuous conversions disabled)   |

| Bit 4:0 | ADCH | 00001 | Input channel 1 selected as ADC input channel           |

## ADCRH/L = 0xxx

Holds results of conversion. Read high byte (ADCRH) before low byte (ADCRL) so that conversion data cannot be overwritten with data from the next conversion.

## ADCCVH/L = 0xxx

Holds compare value when compare function enabled

#### APCTL1=0x02

AD1 pin I/O control disabled. All other AD pins remain general purpose I/O pins

#### APCTL2=0x00

All other AD pins remain general purpose I/O pins

MC9S08AC60 Series Data Sheet, Rev. 3

#### Chapter 11 Inter-Integrated Circuit (S08IICV2)

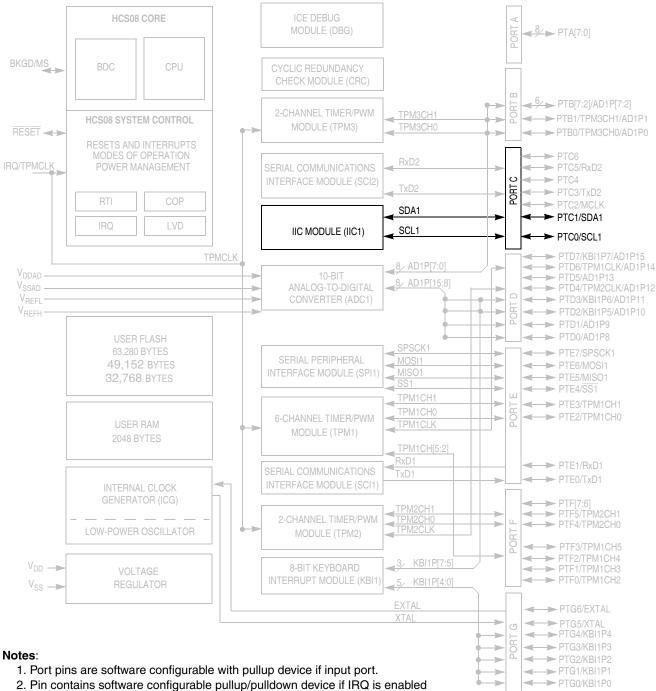

- Pin contains software configurable pullup/pulldown device if IRQ is enabled (IRQPE = 1). Pulldown is enabled if rising edge detect is selected (IRQEDG = 1)

- 3. Pin contains integrated pullup device.

- 4. PTD3, PTD2, PTD7, and PTG4 contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

- 5. TPMCLK, TPM1CLK, and TPM2CLK options are configured via software; out of reset, TPM1CLK, TPM2CLK, and TPMCLK are available to TPM1, TPM2, and TPM3 respectively.

#### Figure 11-1. Block Diagram Highlighting the IIC Module

MC9S08AC60 Series Data Sheet, Rev. 3

The most common uses of the SPI system include connecting simple shift registers for adding input or output ports or connecting small peripheral devices such as serial A/D or D/A converters. Although Figure 14-2 shows a system where data is exchanged between two MCUs, many practical systems involve simpler connections where data is unidirectionally transferred from the master MCU to a slave or from a slave to the master MCU.

## 14.1.2.2 SPI Module Block Diagram

Figure 14-3 is a block diagram of the SPI module. The central element of the SPI is the SPI shift register. Data is written to the double-buffered transmitter (write to SPID) and gets transferred to the SPI shift register at the start of a data transfer. After shifting in a byte of data, the data is transferred into the double-buffered receiver where it can be read (read from SPID). Pin multiplexing logic controls connections between MCU pins and the SPI module.

When the SPI is configured as a master, the clock output is routed to the SPSCK pin, the shifter output is routed to MOSI, and the shifter input is routed from the MISO pin.

When the SPI is configured as a slave, the SPSCK pin is routed to the clock input of the SPI, the shifter output is routed to MISO, and the shifter input is routed from the MOSI pin.

In the external SPI system, simply connect all SPSCK pins to each other, all MISO pins together, and all MOSI pins together. Peripheral devices often use slightly different names for these pins.

## 15.3 TPMV3 Differences from Previous Versions

The TPMV3 is the latest version of the Timer/PWM module that addresses errata found in previous versions. The following section outlines the differences between TPMV3 and TPMV2 modules, and any considerations that should be taken when porting code.

| Action                                                                                               | TPMV3                                                                                                                                                                                          | TPMV2                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Write to TPMxCnTH:L registers <sup>1</sup>                                                           |                                                                                                                                                                                                |                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| Any write to TPMxCNTH or TPMxCNTL registers                                                          | Clears the TPM counter<br>(TPMxCNTH:L) and the<br>prescaler counter.                                                                                                                           | Clears the TPM counter<br>(TPMxCNTH:L) only.                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Read of TPMxCNTH:L registers <sup>1</sup>                                                            |                                                                                                                                                                                                |                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| In BDM mode, any read of TPMxCNTH:L registers                                                        | Returns the value of the TPM counter that is frozen.                                                                                                                                           | If only one byte of the<br>TPMxCNTH:L registers was<br>read before the BDM mode<br>became active, returns the<br>latched value of TPMxCNTH:L<br>from the read buffer (instead of<br>the frozen TPM counter value).             |  |  |  |  |  |  |  |

| In BDM mode, a write to TPMxSC, TPMxCNTH or TPMxCNTL                                                 | Clears this read coherency mechanism.                                                                                                                                                          | Does not clear this read coherency mechanism.                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Read of TPMxCnVH:L registers <sup>2</sup>                                                            |                                                                                                                                                                                                |                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| In BDM mode, any read of TPMxCnVH:L registers                                                        | Returns the value of the TPMxCnVH:L register.                                                                                                                                                  | If only one byte of the<br>TPMxCnVH:L registers was<br>read before the BDM mode<br>became active, returns the<br>latched value of TPMxCNTH:L<br>from the read buffer (instead of<br>the value in the TPMxCnVH:L<br>registers). |  |  |  |  |  |  |  |

| In BDM mode, a write to TPMxCnSC                                                                     | Clears this read coherency mechanism.                                                                                                                                                          | Does not clear this read coherency mechanism.                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Write to TPMxCnVH:L registers                                                                        |                                                                                                                                                                                                |                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| In Input Capture mode, writes to TPMxCnVH:L registers <sup>3</sup>                                   | Not allowed.                                                                                                                                                                                   | Allowed.                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| In Output Compare mode, when (CLKSB:CLKSA not = 0:0),<br>writes to TPMxCnVH:L registers <sup>3</sup> | Update the TPMxCnVH:L<br>registers with the value of<br>their write buffer at the next<br>change of the TPM counter<br>(end of the prescaler<br>counting) after the second<br>byte is written. | Always update these registers<br>when their second byte is<br>written.                                                                                                                                                         |  |  |  |  |  |  |  |

#### Table 15-1. TPMV2 and TPMV3 Porting Considerations

• Non-intrusive commands can be executed at any time even while the user's program is running. Non-intrusive commands allow a user to read or write MCU memory locations or access status and control registers within the background debug controller.

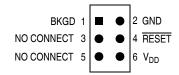

Typically, a relatively simple interface pod is used to translate commands from a host computer into commands for the custom serial interface to the single-wire background debug system. Depending on the development tool vendor, this interface pod may use a standard RS-232 serial port, a parallel printer port, or some other type of communications such as a universal serial bus (USB) to communicate between the host PC and the pod. The pod typically connects to the target system with ground, the BKGD pin, RESET, and sometimes  $V_{DD}$ . An open-drain connection to reset allows the host to force a target system reset, which is useful to regain control of a lost target system or to control startup of a target system before the on-chip nonvolatile memory has been programmed. Sometimes  $V_{DD}$  can be used to allow the pod to use power from the target system to avoid the need for a separate power supply. However, if the pod is powered separately, it can be connected to a running target system without forcing a target system reset or otherwise disturbing the running application program.

Figure 16-1. BDM Tool Connector

## 16.2.1 BKGD Pin Description

BKGD is the single-wire background debug interface pin. The primary function of this pin is for bidirectional serial communication of active background mode commands and data. During reset, this pin is used to select between starting in active background mode or starting the user's application program. This pin is also used to request a timed sync response pulse to allow a host development tool to determine the correct clock frequency for background debug serial communications.

BDC serial communications use a custom serial protocol first introduced on the M68HC12 Family of microcontrollers. This protocol assumes the host knows the communication clock rate that is determined by the target BDC clock rate. All communication is initiated and controlled by the host that drives a high-to-low edge to signal the beginning of each bit time. Commands and data are sent most significant bit first (MSB first). For a detailed description of the communications protocol, refer to Section 16.2.2, "Communication Details."

If a host is attempting to communicate with a target MCU that has an unknown BDC clock rate, a SYNC command may be sent to the target MCU to request a timed sync response signal from which the host can determine the correct communication speed.

BKGD is a pseudo-open-drain pin and there is an on-chip pullup so no external pullup resistor is required. Unlike typical open-drain pins, the external RC time constant on this pin, which is influenced by external capacitance, plays almost no role in signal rise time. The custom protocol provides for brief, actively driven speedup pulses to force rapid rise times on this pin without risking harmful drive level conflicts. Refer to Section 16.2.2, "Communication Details," for more detail.

#### **Development Support**

the host must perform ((8 - CNT) - 1) dummy reads of the FIFO to advance it to the first significant entry in the FIFO.

In most trigger modes, the information stored in the FIFO consists of 16-bit change-of-flow addresses. In these cases, read DBGFH then DBGFL to get one coherent word of information out of the FIFO. Reading DBGFL (the low-order byte of the FIFO data port) causes the FIFO to shift so the next word of information is available at the FIFO data port. In the event-only trigger modes (see Section 16.3.5, "Trigger Modes"), 8-bit data information is stored into the FIFO. In these cases, the high-order half of the FIFO (DBGFH) is not used and data is read out of the FIFO by simply reading DBGFL. Each time DBGFL is read, the FIFO is shifted so the next data value is available through the FIFO data port at DBGFL.

In trigger modes where the FIFO is storing change-of-flow addresses, there is a delay between CPU addresses and the input side of the FIFO. Because of this delay, if the trigger event itself is a change-of-flow address or a change-of-flow address appears during the next two bus cycles after a trigger event starts the FIFO, it will not be saved into the FIFO. In the case of an end-trace, if the trigger event is a change-of-flow, it will be saved as the last change-of-flow entry for that debug run.

The FIFO can also be used to generate a profile of executed instruction addresses when the debugger is not armed. When ARM = 0, reading DBGFL causes the address of the most-recently fetched opcode to be saved in the FIFO. To use the profiling feature, a host debugger would read addresses out of the FIFO by reading DBGFH then DBGFL at regular periodic intervals. The first eight values would be discarded because they correspond to the eight DBGFL reads needed to initially fill the FIFO. Additional periodic reads of DBGFH and DBGFL return delayed information about executed instructions so the host debugger can develop a profile of executed instruction addresses.

## 16.3.3 Change-of-Flow Information

To minimize the amount of information stored in the FIFO, only information related to instructions that cause a change to the normal sequential execution of instructions is stored. With knowledge of the source and object code program stored in the target system, an external debugger system can reconstruct the path of execution through many instructions from the change-of-flow information stored in the FIFO.

For conditional branch instructions where the branch is taken (branch condition was true), the source address is stored (the address of the conditional branch opcode). Because BRA and BRN instructions are not conditional, these events do not cause change-of-flow information to be stored in the FIFO.

Indirect JMP and JSR instructions use the current contents of the H:X index register pair to determine the destination address, so the debug system stores the run-time destination address for any indirect JMP or JSR. For interrupts, RTI, or RTS, the destination address is stored in the FIFO as change-of-flow information.

## 16.3.4 Tag vs. Force Breakpoints and Triggers

Tagging is a term that refers to identifying an instruction opcode as it is fetched into the instruction queue, but not taking any other action until and unless that instruction is actually executed by the CPU. This distinction is important because any change-of-flow from a jump, branch, subroutine call, or interrupt causes some instructions that have been fetched into the instruction queue to be thrown away without being executed.

Development Support

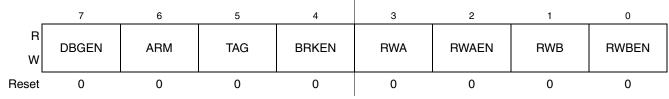

## 16.4.3.7 Debug Control Register (DBGC)

This register can be read or written at any time.

Figure 16-7. Debug Control Register (DBGC)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DBGEN | <ul> <li>Debug Module Enable — Used to enable the debug module. DBGEN cannot be set to 1 if the MCU is secure.</li> <li>0 DBG disabled</li> <li>1 DBG enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                  |

| 6<br>ARM   | <ul> <li>Arm Control — Controls whether the debugger is comparing and storing information in the FIFO. A write is used to set this bit (and ARMF) and completion of a debug run automatically clears it. Any debug run can be manually stopped by writing 0 to ARM or to DBGEN.</li> <li>0 Debugger not armed</li> <li>1 Debugger armed</li> </ul>                                                                                                                                                                                                        |

| 5<br>TAG   | Tag/Force Select — Controls whether break requests to the CPU will be tag or force type requests. If         BRKEN = 0, this bit has no meaning or effect.         0 CPU breaks requested as force type requests         1 CPU breaks requested as tag type requests                                                                                                                                                                                                                                                                                      |

| 4<br>BRKEN | <ul> <li>Break Enable — Controls whether a trigger event will generate a break request to the CPU. Trigger events can cause information to be stored in the FIFO without generating a break request to the CPU. For an end trace, CPU break requests are issued to the CPU when the comparator(s) and R/W meet the trigger requirements. For a begin trace, CPU break requests are issued when the FIFO becomes full. TRGSEL does not affect the timing of CPU break requests not enabled</li> <li>1 Triggers cause a break request to the CPU</li> </ul> |

| 3<br>RWA   | <ul> <li>R/W Comparison Value for Comparator A — When RWAEN = 1, this bit determines whether a read or a write access qualifies comparator A. When RWAEN = 0, RWA and the R/W signal do not affect comparator A.</li> <li>0 Comparator A can only match on a write cycle</li> <li>1 Comparator A can only match on a read cycle</li> </ul>                                                                                                                                                                                                                |

| 2<br>RWAEN | <ul> <li>Enable R/W for Comparator A — Controls whether the level of R/W is considered for a comparator A match.</li> <li>0 R/W is not used in comparison A</li> <li>1 R/W is used in comparison A</li> </ul>                                                                                                                                                                                                                                                                                                                                             |

| 1<br>RWB   | <ul> <li>R/W Comparison Value for Comparator B — When RWBEN = 1, this bit determines whether a read or a write access qualifies comparator B. When RWBEN = 0, RWB and the R/W signal do not affect comparator B.</li> <li>0 Comparator B can match only on a write cycle</li> <li>1 Comparator B can match only on a read cycle</li> </ul>                                                                                                                                                                                                                |

| 0<br>RWBEN | <ul> <li>Enable R/W for Comparator B — Controls whether the level of R/W is considered for a comparator B match.</li> <li>0 R/W is not used in comparison B</li> <li>1 R/W is used in comparison B</li> </ul>                                                                                                                                                                                                                                                                                                                                             |

Appendix A Electrical Characteristics and Timing Specifications

# A.6 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

| Num | С | Parameter                                                                                                                                                                                                                                                                           | Symbol             | Min                                                                                              | Typ <sup>1</sup> | Max                    | Unit |  |

|-----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------|------------------|------------------------|------|--|

|     |   | Output high voltage — Low Drive (PTxDSn = 0)<br>5 V, $I_{Load} = -2 \text{ mA}$<br>3 V, $I_{Load} = -0.6 \text{ mA}$<br>5 V, $I_{Load} = -0.4 \text{ mA}$<br>3 V, $I_{Load} = -0.24 \text{ mA}$<br>Output high voltage — High Drive (PTxDSn = 1)                                    |                    | $V_{DD} - 1.5$<br>$V_{DD} - 1.5$<br>$V_{DD} - 0.8$<br>$V_{DD} - 0.8$                             |                  |                        |      |  |

| 1 P |   | 5 V, $I_{Load} = -10$ mA<br>3 V, $I_{Load} = -3$ mA<br>5 V, $I_{Load} = -2$ mA<br>3 V, $I_{Load} = -0.4$ mA                                                                                                                                                                         |                    | V <sub>DD</sub> - 1.5<br>V <sub>DD</sub> - 1.5<br>V <sub>DD</sub> - 0.8<br>V <sub>DD</sub> - 0.8 |                  |                        | v    |  |

|     |   | Output low voltage — Low Drive (PTxDSn = 0)<br>5  V, I <sub>Load</sub> = 2 mA<br>3  V, I <sub>Load</sub> = 0.6 mA<br>5  V, I <sub>Load</sub> = 0.4 mA<br>3  V, I <sub>Load</sub> = 0.24 mA                                                                                          |                    | 1.5<br>1.5<br>0.8<br>0.8                                                                         |                  |                        |      |  |

| 2   | Ρ | Output low voltage — High Drive (PTxDSn = 1)<br>$5 \text{ V}, \text{ I}_{\text{Load}} = 10 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = 3 \text{ mA}$<br>$5 \text{ V}, \text{ I}_{\text{Load}} = 2 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = 0.4 \text{ mA}$ |                    | 1.5<br>1.5<br>0.8<br>0.8                                                                         |                  | <br>                   | v    |  |

| 3   | Ρ | Output high current — Max total I <sub>OH</sub> for all ports<br>5V<br>3V                                                                                                                                                                                                           | I <sub>ОНТ</sub>   |                                                                                                  |                  | 100<br>60              | mA   |  |

| 4   | Ρ | Output low current — Max total I <sub>OL</sub> for all ports<br>5V<br>3V                                                                                                                                                                                                            | I <sub>OLT</sub>   |                                                                                                  |                  | 100<br>60              | mA   |  |

| 5   | Ρ | Input high $2.7v \le V_{DD} 4.5v$                                                                                                                                                                                                                                                   | V <sub>IH</sub>    | 0.70xV <sub>DD</sub>                                                                             | _                | —                      |      |  |

|     |   | voltage; all $4.5v \le V_{DD} \le 5.5v$                                                                                                                                                                                                                                             | V <sub>IH</sub>    | 0.65xV <sub>DD</sub>                                                                             |                  |                        | v    |  |

| 6   | Ρ | Input low voltage; all digital inputs                                                                                                                                                                                                                                               | V <sub>IL</sub>    | —                                                                                                | —                | 0.35 x V <sub>DD</sub> |      |  |

| 7   | Ρ | Input hysteresis; all digital inputs                                                                                                                                                                                                                                                | V <sub>hys</sub>   | 0.06 x V <sub>DD</sub>                                                                           |                  |                        | mV   |  |

| 8   | Ρ | Input leakage current; input only pins <sup>2</sup>                                                                                                                                                                                                                                 | ll <sub>In</sub> l | —                                                                                                | 0.1              | 1                      | μA   |  |

| 9   | Ρ | High Impedance (off-state) leakage current <sup>2</sup>                                                                                                                                                                                                                             | ll <sub>oz</sub> l | —                                                                                                | 0.1              | 1                      | μA   |  |

| 10  | Ρ | Internal pullup resistors <sup>3</sup>                                                                                                                                                                                                                                              | R <sub>PU</sub>    | 20                                                                                               | 45               | 65                     | kΩ   |  |

| 11  | Ρ | Internal pulldown resistors <sup>4</sup>                                                                                                                                                                                                                                            | R <sub>PD</sub>    | 20                                                                                               | 45               | 65                     | kΩ   |  |

| 12  | С | Input Capacitance; all non-supply pins                                                                                                                                                                                                                                              | C <sub>In</sub>    | _                                                                                                | —                | 8                      | pF   |  |

| 13  | D | RAM retention voltage                                                                                                                                                                                                                                                               | V <sub>RAM</sub>   | —                                                                                                | 0.6              | 1.0                    | V    |  |

| 14  | Ρ | POR rearm voltage                                                                                                                                                                                                                                                                   | V <sub>POR</sub>   | 0.9                                                                                              | 1.4              | 2.0                    | V    |  |

| 15  | D | POR rearm time                                                                                                                                                                                                                                                                      | t <sub>POR</sub>   | 10                                                                                               | _                |                        | μS   |  |

#### Table A-6. DC Characteristics

Appendix A Electrical Characteristics and Timing Specifications

# A.7 Supply Current Characteristics

Table A-7. Supply Current Characteristics

| Num | С | Parameter                                          | Symbol                | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max <sup>2</sup>        | Unit       | Temp<br>(°C)                |

|-----|---|----------------------------------------------------|-----------------------|------------------------|------------------|-------------------------|------------|-----------------------------|

|     | _ | Run supply current <sup>3</sup> measured at        |                       | 5                      | 1.0              | 1.3 <sup>4</sup>        | mA         |                             |

| 1   | С | (CPU clock = 2 MHz, $f_{Bus} = 1$ MHz)             | RI <sub>DD</sub>      | 3                      | 0.9              | 1.1                     |            | –40 to 125°C                |

|     |   | Run supply current <sup>5</sup> measured at        |                       | 5                      | 6.5              | 8.0 <sup>6</sup>        | -          |                             |

| 2   | С | (CPU clock = 16 MHz, f <sub>Bus</sub> = 8 MHz)     | RI <sub>DD</sub>      | 3                      | 5.5              | 6.5                     | mA         | –40 to 125°C                |

|     |   | P Stop2 mode supply current                        |                       | 5                      | 0.900            | 18.0<br>60 <sup>4</sup> | μA         | –40 to 85°C<br>–40 to 125°C |

| 3   | Р |                                                    | S2I <sub>DD</sub>     | 5                      | 0.900            |                         |            |                             |

|     |   |                                                    | טט                    | 3                      | 0.720            | 17.0<br>50              | μ <b>A</b> | −40 to 85°C −40 to 125°C    |

|     |   | Stop3 mode supply current                          | S3I <sub>DD</sub>     |                        |                  | 20.0                    | μA         | –40 to 85°C                 |

| 4   | Р |                                                    |                       | 5 0                    | 0.975            | 90 <sup>4</sup>         |            | –40 to 125°C                |

|     |   |                                                    |                       | _                      |                  | 19.0                    | μA         | -40 to 85°C                 |

|     |   |                                                    |                       | 3                      | 0.825            | 85                      | PT -       | –40 to 125°C                |

|     |   | RTI adder to stop2 or stop3 <sup>7</sup>           | S23I <sub>ddrti</sub> | 5                      | 300              | 500                     | nA         | -40 to 85°C                 |

| 5   | С |                                                    |                       |                        |                  | 500                     |            | -40 to 125°C                |

|     |   |                                                    |                       | 3                      | 300              | 500<br>500              | nA         | –40 to 85°C<br>–40 to 125°C |

|     |   |                                                    |                       |                        |                  | 500                     |            |                             |

| 6   | 6 | C LVD adder to stop3 (LVDE = LVDSE = 1)            | S3I <sub>DDLVD</sub>  | 5                      | 110              | 180                     | μA         | −40 to 85°C<br>−40 to 125°C |

| 0   |   |                                                    |                       | 3                      | 90               |                         | μA         | -40 to 85°C                 |

|     |   |                                                    |                       | •                      |                  | 160                     | P          | –40 to 125°C                |

| 7   | с | Adder to stop3 for oscillator enabled <sup>8</sup> | S3I <sub>DDOSC</sub>  | 5,3                    | 5                | 8                       | μA         | -40 to 85°C                 |

|     | - | (OSCSTEN =1)                                       | - DDOSC               | - , -                  | -                | -                       | μA         | –40 to 125°C                |

<sup>1</sup> Typical values are based on characterization data at 25°C unless otherwise stated. See Figure A-5 through Figure A-7 for typical curves across voltage/temperature.

<sup>2</sup> Values given here are preliminary estimates prior to completing characterization.

<sup>3</sup> All modules except ADC active, ICG configured for FBE, and does not include any dc loads on port pins

<sup>4</sup> Every unit tested to this parameter. All other values in the Max column are guaranteed by characterization.

<sup>5</sup> All modules except ADC active, ICG configured for FBE, and does not include any dc loads on port pins

<sup>6</sup> Every unit tested to this parameter. All other values in the Max column are guaranteed by characterization.

<sup>7</sup> Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode. Wait mode typical is 560  $\mu$ A at 3 V with f<sub>Bus</sub> = 1 MHz.

<sup>8</sup> Values given under the following conditions: low range operation (RANGE = 0) with a 32.768kHz crystal, low power mode (HGO = 0), clock monitor disabled (LOCD = 1).