Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 34                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LQFP                                                                |

| Supplier Device Package    | 44-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08ac48cfge |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 4 Memory

# 4.1 MC9S08AC60 Series Memory Map

As shown in Figure 4-1, on-chip memory in the MC9S08AC60 Series series of MCUs consists of RAM, FLASH program memory for nonvolatile data storage, plus I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (\$0000 through \$006F)

- High-page registers (\$1800 through \$185F)

- Nonvolatile registers (\$FFB0 through \$FFBF)

Chapter 4 Memory

## 4.2 Register Addresses and Bit Assignments

The registers in the MC9S08AC60 Series are divided into these three groups:

- Direct-page registers are located in the first 112 locations in the memory map, so they are accessible with efficient direct addressing mode instructions.

- High-page registers are used much less often, so they are located above 0x1800 in the memory map. This leaves more room in the direct page for more frequently used registers and variables.

- The nonvolatile register area consists of a block of 16 locations in FLASH memory at \$FFB0-\$FFBF.

Nonvolatile register locations include:

- Three values which are loaded into working registers at reset

- An 8-byte backdoor comparison key which optionally allows a user to gain controlled access to secure memory

Because the nonvolatile register locations are FLASH memory, they must be erased and programmed like other FLASH memory locations.

Direct-page registers can be accessed with efficient direct addressing mode instructions. Bit manipulation instructions can be used to access any bit in any direct-page register. Table 4-2 is a summary of all user-accessible direct-page registers and control bits.

The direct page registers in Table 4-2 can use the more efficient direct addressing mode which only requires the lower byte of the address. Because of this, the lower byte of the address in column one is shown in bold text. In Table 4-3 and Table 4-4 the whole address in column one is shown in bold. In Table 4-2, Table 4-3, and Table 4-4, the register names in column two are shown in bold to set them apart from the bit names to the right. Cells that are not associated with named bits are shaded. A shaded cell with a 0 indicates this unused bit always reads as a 0. Shaded cells with dashes indicate unused or reserved bit locations that could read as 1s or 0s.

| Address           | Register Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|-------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x183B<br>0x183F  | Reserved      | _      | _      | _      | _      | _      | _      | _      | _      |

| 0x1840            | ΡΤΑΡΕ         | PTAPE7 | PTAPE6 | PTAPE5 | PTAPE4 | PTAPE3 | PTAPE2 | PTAPE1 | PTAPE0 |

| 0x1841            | PTASE         | PTASE7 | PTASE6 | PTASE5 | PTASE4 | PTASE3 | PTASE2 | PTASE1 | PTASE0 |

| 0x1842            | PTADS         | PTADS7 | PTADS6 | PTADS5 | PTADS4 | PTADS3 | PTADS2 | PTADS1 | PTADS0 |

| 0x1843            | Reserved      | —      | _      | _      | _      | —      | _      | —      | —      |

| 0x1844            | PTBPE         | PTBPE7 | PTBPE6 | PTBPE5 | PTBPE4 | PTBPE3 | PTBPE2 | PTBPE1 | PTBPE0 |

| 0x1845            | PTBSE         | PTBSE7 | PTBSE6 | PTBSE5 | PTBSE4 | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| 0x1846            | PTBDS         | PTBDS7 | PTBDS6 | PTBDS5 | PTBDS4 | PTBDS3 | PTBDS2 | PTBDS1 | PTBDS0 |

| 0x1847            | Reserved      |        |        |        | _      | —      |        |        |        |

| 0x1848            | PTCPE         | 0      | PTCPE6 | PTCPE5 | PTCPE4 | PTCPE3 | PTCPE2 | PTCPE1 | PTCPE0 |

| 0x1849            | PTCSE         | 0      | PTCSE6 | PTCSE5 | PTCSE4 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| 0x184A            | PTCDS         | 0      | PTCDS6 | PTCDS5 | PTCDS4 | PTCDS3 | PTCDS2 | PTCDS1 | PTCDS0 |

| 0x184B            | Reserved      | —      | _      | _      | -      | —      |        | —      | —      |

| 0x184C            | PTDPE         | PTDPE7 | PTDPE6 | PTDPE5 | PTDPE4 | PTDPE3 | PTDPE2 | PTDPE1 | PTDPE0 |

| 0x184D            | PTDSE         | PTDSE7 | PTDSE6 | PTDSE5 | PTDSE4 | PTDSE3 | PTDSE2 | PTDSE1 | PTDSE0 |

| 0x184E            | PTDDS         | PTDDS7 | PTDDS6 | PTDDS5 | PTDDS4 | PTDDS3 | PTDDS2 | PTDDS1 | PTDDS0 |

| 0x184F            | Reserved      |        |        | _      |        | _      |        | _      |        |

| 0x1850            | PTEPE         | PTEPE7 | PTEPE6 | PTEPE5 | PTEPE4 | PTEPE3 | PTEPE2 | PTEPE1 | PTEPE0 |

| 0x1851            | PTESE         | PTESE7 | PTESE6 | PTESE5 | PTESE4 | PTESE3 | PTESE2 | PTESE1 | PTESE0 |

| 0x1852            | PTEDS         | PTEDS7 | PTEDS6 | PTEDS5 | PTEDS4 | PTEDS3 | PTEDS2 | PTEDS1 | PTEDS0 |

| 0x1853            | Reserved      | —      | _      | —      | _      | —      | _      | —      | —      |

| 0x1854            | PTFPE         | PTFPE7 | PTFPE6 | PTFPE5 | PTFPE4 | PTFPE3 | PTFPE2 | PTFPE1 | PTFPE0 |

| 0x1855            | PTFSE         | PTFSE7 | PTFSE6 | PTFSE5 | PTFSE4 | PTFSE3 | PTFSE2 | PTFSE1 | PTFSE0 |

| 0x1856            | PTFDS         | PTFDS7 | PTFDS6 | PTFDS5 | PTFDS4 | PTFDS3 | PTFDS2 | PTFDS1 | PTFDS0 |

| 0x1857            | Reserved      | —      | _      | —      | _      | —      | _      | —      | —      |

| 0x1858            | PTGPE         | 0      | PTGPE6 | PTGPE5 | PTGPE4 | PTGPE3 | PTGPE2 | PTGPE1 | PTGPE0 |

| 0x1859            | PTGSE         | 0      | PTGSE6 | PTGSE5 | PTGSE4 | PTGSE3 | PTGSE2 | PTGSE1 | PTGSE0 |

| 0x185A            | PTGDS         | 0      | PTGDS6 | PTGDS5 | PTGDS4 | PTGDS3 | PTGDS2 | PTGDS1 | PTGDS0 |

| 0x185B–<br>0x185F | Reserved      | —      |        |        |        | —      |        | —      |        |

Table 4-3. High-Page Register Summary (Sheet 3 of 3)

<sup>1</sup> This reserved bit must always be written to 0.

Nonvolatile FLASH registers, shown in Table 4-4, are located in the FLASH memory. These registers include an 8-byte backdoor key which optionally can be used to gain access to secure memory resources. During reset events, the contents of NVPROT and NVOPT in the nonvolatile register area of the FLASH memory are transferred into corresponding FPROT and FOPT working registers in the high-page registers to control security and block protection options.

Chapter 4 Memory

| Address            | Register Name                                        | Bit 7 | 6                     | 5    | 4    | 3    | 2    | 1     | Bit 0 |

|--------------------|------------------------------------------------------|-------|-----------------------|------|------|------|------|-------|-------|

| \$FFB0 –<br>\$FFB7 | NVBACKKEY                                            |       | 8-Byte Comparison Key |      |      |      |      |       |       |

| \$FFB8 –<br>\$FFBB | Reserved                                             | _     | —                     | —    | —    | —    | —    | —     | —     |

| \$FFBC             | Reserved for stor-<br>age of 250 kHz<br>ICGTRM value | _     | _                     | _    | _    | _    | _    | _     | _     |

| \$FFBD             | NVPROT                                               | FPS7  | FPS6                  | FPS5 | FPS4 | FPS3 | FPS2 | FPS1  | FPDIS |

| \$FFBE             | Reserved for stor-<br>age of 243 kHz<br>ICGTRM value | _     | _                     | _    | _    | _    | _    | _     | —     |

| \$FFBF             | NVOPT                                                | KEYEN | FNORED                | 0    | 0    | 0    | 0    | SEC01 | SEC00 |

#### Table 4-4. Nonvolatile Register Summary

Provided the key enable (KEYEN) bit is 1, the 8-byte comparison key can be used to temporarily disengage memory security. This key mechanism can be accessed only through user code running in secure memory. (A security key cannot be entered directly through background debug commands.) This security key can be disabled completely by programming the KEYEN bit to 0. If the security key is disabled, the only way to disengage security is by mass erasing the FLASH if needed (normally through the background debug interface) and verifying that FLASH is blank. To avoid returning to secure mode after the next reset, program the security bits (SEC01:SEC00) to the unsecured state (1:0).

## 4.3 RAM

The MC9S08AC60 Series includes static RAM. The locations in RAM below 0x0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data when the MCU is in low-power wait, stop2, or stop3 mode. At power-on, the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention.

For compatibility with older M68HC05 MCUs, the HCS08 resets the stack pointer to 0x00FF. In the MC9S08AC60 Series, it is usually best to re-initialize the stack pointer to the top of the RAM so the direct page RAM can be used for frequently accessed RAM variables and bit-addressable program variables. Include the following 2-instruction sequence in your reset initialization routine (where RamLast is equated to the highest address of the RAM in the Freescale-provided equate file).

| JDHX<br>XS | ;point one past RAM<br>;SP<-(H:X-1) |

|------------|-------------------------------------|

|            |                                     |

#### **Chapter 4 Memory**

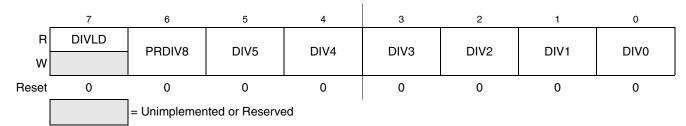

#### Figure 4-5. FLASH Clock Divider Register (FCDIV)

#### Table 4-6. FCDIV Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DIVLD    | <ul> <li>Divisor Loaded Status Flag — When set, this read-only status flag indicates that the FCDIV register has been written since reset. Reset clears this bit and the first write to this register causes this bit to become set regardless of the data written.</li> <li>0 FCDIV has not been written since reset; erase and program operations disabled for FLASH.</li> <li>1 FCDIV has been written since reset; erase and program operations enabled for FLASH.</li> </ul>                                                                                                                                                                                                                                         |

| 6<br>PRDIV8   | <ul> <li>Prescale (Divide) FLASH Clock by 8</li> <li>O Clock input to the FLASH clock divider is the bus rate clock.</li> <li>1 Clock input to the FLASH clock divider is the bus rate clock divided by 8.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5<br>DIV[5:0] | <b>Divisor for FLASH Clock Divider</b> — The FLASH clock divider divides the bus rate clock (or the bus rate clock divided by 8 if PRDIV8 = 1) by the value in the 6-bit DIV5:DIV0 field plus one. The resulting frequency of the internal FLASH clock must fall within the range of 200 kHz to 150 kHz for proper FLASH operations. Program/erase timing pulses are one cycle of this internal FLASH clock, which corresponds to a range of 5 $\mu$ s to 6.7 $\mu$ s. The automated programming logic uses an integer number of these pulses to complete an erase or program operation. See Equation 4-1 and Equation 4-2. Table 4-7 shows the appropriate values for PRDIV8 and DIV5:DIV0 for selected bus frequencies. |

if PRDIV8 = 0 — f<sub>FCLK</sub> = f<sub>Bus</sub> ÷ ([DIV5:DIV0] + 1)

Eqn. 4-1

if PRDIV8 = 1 —  $f_{FCLK} = f_{Bus} \div (8 \times ([DIV5:DIV0] + 1))$

Eqn. 4-2

| f <sub>Bus</sub> | PRDIV8<br>(Binary) | DIV5:DIV0<br>(Decimal) | f <sub>FCLK</sub> | Program/Erase Timing Pulse<br>(5 μs Min, 6.7 μs Max) |

|------------------|--------------------|------------------------|-------------------|------------------------------------------------------|

| 20 MHz           | 1                  | 12                     | 192.3 kHz         | 5.2 μs                                               |

| 10 MHz           | 0                  | 49                     | 200 kHz           | 5 μs                                                 |

| 8 MHz            | 0                  | 39                     | 200 kHz           | 5 μs                                                 |

| 4 MHz            | 0                  | 19                     | 200 kHz           | 5 μs                                                 |

| 2 MHz            | 0                  | 9                      | 200 kHz           | 5 μs                                                 |

| 1 MHz            | 0                  | 4                      | 200 kHz           | 5 μs                                                 |

| 200 kHz          | 0                  | 0                      | 200 kHz           | 5 μs                                                 |

| 150 kHz          | 0                  | 0                      | 150 kHz           | 6.7 μs                                               |

#### Table 4-7. FLASH Clock Divider Settings

Chapter 5 Resets, Interrupts, and System Configuration

- Illegal opcode detect

- Background debug forced reset

- The reset pin ( $\overline{\text{RESET}}$ )

- Clock generator loss of lock and loss of clock reset

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register. Whenever the MCU enters reset, the internal clock generator (ICG) module switches to self-clocked mode with the frequency of  $f_{Self}$  reset selected. The reset pin is driven low for 34 bus cycles where the internal bus frequency is half the ICG frequency. After the 34 bus cycles are completed, the pin is released and will be pulled up by the internal pullup resistor, unless it is held low externally. After the pin is released, it is sampled after another 38 bus cycles to determine whether the reset pin is the cause of the MCU reset.

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COPE becomes set in SOPT enabling the COP watchdog (see Section 5.9.4, "System Options Register (SOPT)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPE. The COP counter is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP counter.

The COPCLKS bit in SOPT2 (see Section 5.9.10, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 1-kHz clock source. With each clock source, there is an associated short and long time-out controlled by COPT in SOPT. Table 5-1 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the bus clock source and the associated long time-out (2<sup>18</sup> cycles).

| Cont    | rol Bits | - Clock Source | COP Overflow Count                          |

|---------|----------|----------------|---------------------------------------------|

| COPCLKS | СОРТ     |                | COP Overnow Count                           |

| 0       | 0        | ~1 kHz         | 2 <sup>5</sup> cycles (32 ms) <sup>1</sup>  |

| 0       | 1        | ~1 kHz         | 2 <sup>8</sup> cycles (256 ms) <sup>1</sup> |

| 1       | 0        | Bus            | 2 <sup>13</sup> cycles                      |

| 1       | 1        | Bus            | 2 <sup>18</sup> cycles                      |

<sup>1</sup> Values are shown in this column based on  $t_{RTI} = 1$  ms. See  $t_{RTI}$  in the appendix Section A.10.1, "Control Timing," for the tolerance of this value.

## 5.5.2 External Interrupt Request (IRQ) Pin

External interrupts are managed by the IRQSC status and control register. When the IRQ function is enabled, synchronous logic monitors the pin for edge-only or edge-and-level events. When the MCU is in stop mode and system clocks are shut down, a separate asynchronous path is used so the IRQ (if enabled) can wake the MCU.

### 5.5.2.1 Pin Configuration Options

The IRQ pin enable (IRQPE) control bit in the IRQSC register must be 1 in order for the IRQ pin to act as the interrupt request (IRQ) input. As an IRQ input, the user can choose the polarity of edges or levels detected (IRQEDG), whether the pin detects edges-only or edges and levels (IRQMOD), and whether an event causes an interrupt or only sets the IRQF flag which can be polled by software.

The IRQ pin, when enabled, defaults to use an internal pull device (IRQPDD = 0), configured as a pull-up or pull-down depending on the polarity chosen. If the user desires to use an external pull-up or pull-down, the IRQPDD can be written to a 1 to turn off the internal device.

BIH and BIL instructions may be used to detect the level on the IRQ pin when the pin is configured to act as the IRQ input.

#### NOTE

- The voltage measured on the pulled up IRQ pin may be as low as  $V_{DD}$ -0.7 V. The internal gates connected to this pin are pulled all the way to  $V_{DD}$ . All other pins with the enabled pullup resistor will have an unloaded measurement of  $V_{DD}$ .

- When enabling the IRQ pin for use, the IRQF will be set, and should be cleared prior to enabling the interrupt. When configuring the pin for falling edge and level sensitivity in a 5V system, it is necessary to wait at least 6 cycles between clearing the flag and enabling the interrupt.

### 5.5.2.2 Edge and Level Sensitivity

The IRQMOD control bit reconfigures the detection logic so it detects edge events and pin levels. In this edge detection mode, the IRQF status flag becomes set when an edge is detected (when the IRQ pin changes from the deasserted to the asserted level), but the flag is continuously set (and cannot be cleared) as long as the IRQ pin remains at the asserted level.

### 5.5.3 Interrupt Vectors, Sources, and Local Masks

Table 5-2 provides a summary of all interrupt sources. Higher-priority sources are located toward the bottom of the table. The high-order byte of the address for the interrupt service routine is located at the first address in the vector address column, and the low-order byte of the address for the interrupt service routine is located at the next higher address.

When an interrupt condition occurs, an associated flag bit becomes set. If the associated local interrupt enable is 1, an interrupt request is sent to the CPU. Within the CPU, if the global interrupt mask (I bit in the CCR) is 0, the CPU will finish the current instruction, stack the PCL, PCH, X, A, and CCR CPU

Chapter 6 Parallel Input/Output

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTASE7 | PTASE6 | PTASE5 | PTASE4 | PTASE3 | PTASE2 | PTASE1 | PTASE0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-5. Slew Rate Control Enable for Port A (PTASE)

#### Table 6-4. PTASE Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTASEn] | <ul> <li>Output Slew Rate Control Enable for Port A Bits — Each of these control bits determine whether output slew rate control is enabled for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port A bit n.</li> <li>Output slew rate control enabled for port A bit n.</li> </ul> |

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTADS7 | PTADS6 | PTADS5 | PTADS4 | PTADS3 | PTADS2 | PTADS1 | PTADS0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-6. Drive Strength Selection for Port A (PTADS)

#### Table 6-5. PTADS Register Field Descriptions

| Field  | Description                                                                                                                                                                                                                                                                         |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTADSn | <ul> <li>Output Drive Strength Selection for Port A Bits — Each of these control bits selects between low and high output drive for the associated PTA pin.</li> <li>0 Low output drive enabled for port A bit n.</li> <li>1 High output drive enabled for port A bit n.</li> </ul> |

Chapter 6 Parallel Input/Output

|       | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| R     | 0 | PTGDS6 | PTGDS5 | PTGDS4 | PTGDS3 | PTGDS2 | PTGDS1 | PTGDS0 |

| w     |   | FIGD30 | FIGD00 | FTGD34 | FIGD33 | FIGD32 | FIGDST | FTGD30 |

| Reset | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

ī.

### Figure 6-36. Output Drive Strength Selection for Port G (PTGDS)

#### Table 6-35. PTGDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTGDS[6:0] | <ul> <li>Output Drive Strength Selection for Port G Bits — Each of these control bits selects between low and high output drive for the associated PTG pin.</li> <li>0 Low output drive enabled for port G bit n.</li> <li>1 High output drive enabled for port G bit n.</li> </ul> |

\_\_\_\_\_

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                                     | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                                    |                       | Affect<br>on CCR                  |  |  |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------|-----------------------|-----------------------------------|--|--|

| Form                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                               | PdA                                                 | _                                                                                | δ                               | Details                                                  | <b>V</b> 1 1 <b>H</b> | INZC                              |  |  |

| CMP #opr8i<br>CMP opr8a<br>CMP opr16a<br>CMP oprx16,X<br>CMP oprx8,X<br>CMP ,X<br>CMP oprx16,SP<br>CMP oprx8,SP | Compare Accumulator with Memory<br>A – M<br>(CCR Updated But Operands Not Changed)                                                                                                                                                                                                                                                                                                                            | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | Al ii<br>Bl dd<br>Cl hh ll<br>Dl ee ff<br>El ff<br>Fl<br>9E Dl ee ff<br>9E El ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>prpp<br>prpp  | \$11−                 | -\$\$\$                           |  |  |

| COM opr8a<br>COMA<br>COMX<br>COM oprx8,X<br>COM ,X<br>COM oprx8,SP                                              | $\begin{array}{lll} \mbox{Complement} & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \\ \mbox{(One's Complement)} & \mbox{A} \leftarrow (\overline{A}) = \$ FF - (A) \\ & \mbox{X} \leftarrow (\overline{X}) = \$ FF - (X) \\ & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \\ & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \\ & \mbox{M} \leftarrow (\overline{M}) = \$ FF - (M) \end{array}$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33 dd<br>43<br>53<br>63 ff<br>73<br>9E 63 ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp               | 011-                  | - ↓ ↓ 1                           |  |  |

| CPHX opr16a<br>CPHX #opr16i<br>CPHX opr8a<br>CPHX oprx8,SP                                                      | Compare Index Register (H:X) with Memory<br>(H:X) – (M:M + \$0001)<br>(CCR Updated But Operands Not Changed)                                                                                                                                                                                                                                                                                                  | EXT<br>IMM<br>DIR<br>SP1                            | 3E hh ll<br>65 jj kk<br>75 dd<br>9E F3 ff                                        | 6<br>3<br>5<br>6                | prrfpp<br>ppp<br>rrfpp<br>prrfpp                         | \$11-                 | - ‡ ‡ ‡                           |  |  |

| CPX #opr8i<br>CPX opr8a<br>CPX opr16a<br>CPX oprx16,X<br>CPX oprx8,X<br>CPX ,X<br>CPX oprx16,SP<br>CPX oprx8,SP | Compare X (Index Register Low) with<br>Memory<br>X – M<br>(CCR Updated But Operands Not Changed)                                                                                                                                                                                                                                                                                                              | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A3 ii<br>B3 dd<br>C3 hh 11<br>D3 ee ff<br>E3 ff<br>F3<br>9E D3 ee ff<br>9E E3 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | \$11-                 | -\$\$\$                           |  |  |

| DAA                                                                                                             | Decimal Adjust Accumulator<br>After ADD or ADC of BCD Values                                                                                                                                                                                                                                                                                                                                                  | INH                                                 | 72                                                                               | 1                               | р                                                        | U 1 1 –               | $ \uparrow$ $\uparrow$ $\uparrow$ |  |  |

| DBNZ opr8a,rel<br>DBNZA rel<br>DBNZX rel<br>DBNZ oprx8,X,rel<br>DBNZ ,X,rel<br>DBNZ oprx8,SP,rel                | Decrement A, X, or M and Branch if Not Zero<br>(if (result) ≠ 0)<br>DBNZX Affects X Not H                                                                                                                                                                                                                                                                                                                     | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B dd rr<br>4B rr<br>5B rr<br>6B ff rr<br>7B rr<br>9E 6B ff rr                   | 7<br>4<br>4<br>7<br>6<br>8      | rfwpppp<br>fppp<br>fppp<br>rfwpppp<br>rfwppp<br>prfwppp  | -11-                  |                                   |  |  |

| DEC opr8a<br>DECA<br>DECX<br>DEC oprx8,X<br>DEC ,X<br>DEC oprx8,SP                                              | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                          | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A dd<br>4A<br>5A<br>6A ff<br>7A<br>9E 6A ff                                     | 5<br>1<br>1<br>5<br>4<br>6      | rfwpp<br>p<br>rfwpp<br>rfwp<br>prfwp                     | \$11−                 | -\$\$-                            |  |  |

| DIV                                                                                                             | Divide A $\leftarrow$ (H:A)÷(X); H $\leftarrow$ Remainder                                                                                                                                                                                                                                                                                                                                                     | INH                                                 | 52                                                                               | 6                               | ffffp                                                    | - 1 1 -               | ‡‡                                |  |  |

| EOR #opr8i<br>EOR opr8a<br>EOR opr16a<br>EOR oprx16,X<br>EOR oprx8,X<br>EOR ,X<br>EOR oprx16,SP<br>EOR oprx8,SP | Exclusive OR Memory with Accumulator $A \leftarrow (A \oplus M)$                                                                                                                                                                                                                                                                                                                                              | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A8 ii<br>B8 dd<br>C8 hh ll<br>D8 ee ff<br>E8 ff<br>F8<br>9E D8 ee ff<br>9E E8 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>rpp<br>rpp<br>rfp<br>pprpp<br>prpp  | 011-                  | -\$\$-                            |  |  |

| Table 7.0  | Instruction   | Cat Cummer  | . 10 |               |

|------------|---------------|-------------|------|---------------|

| Table 7-2. | . Instruction | Set Summary | y (3 | Sheel 4 01 9) |

## 9.3.1 Analog Power (V<sub>DDAD</sub>)

The ADC analog portion uses  $V_{DDAD}$  as its power connection. In some packages,  $V_{DDAD}$  is connected internally to  $V_{DD}$ . If externally available, connect the  $V_{DDAD}$  pin to the same voltage potential as  $V_{DD}$ . External filtering may be necessary to ensure clean  $V_{DDAD}$  for good results.

## 9.3.2 Analog Ground (V<sub>SSAD</sub>)

The ADC analog portion uses  $V_{SSAD}$  as its ground connection. In some packages,  $V_{SSAD}$  is connected internally to  $V_{SS}$ . If externally available, connect the  $V_{SSAD}$  pin to the same voltage potential as  $V_{SS}$ .

## 9.3.3 Voltage Reference High (V<sub>REFH</sub>)

$V_{REFH}$  is the high reference voltage for the converter. In some packages,  $V_{REFH}$  is connected internally to  $V_{DDAD}$ . If externally available,  $V_{REFH}$  may be connected to the same potential as  $V_{DDAD}$ , or may be driven by an external source that is between the minimum  $V_{DDAD}$  spec and the  $V_{DDAD}$  potential ( $V_{REFH}$  must never exceed  $V_{DDAD}$ ).

## 9.3.4 Voltage Reference Low (V<sub>REFL</sub>)

$V_{REFL}$  is the low reference voltage for the converter. In some packages,  $V_{REFL}$  is connected internally to  $V_{SSAD}$ . If externally available, connect the  $V_{REFL}$  pin to the same voltage potential as  $V_{SSAD}$ .

### 9.3.5 Analog Channel Inputs (ADx)

The ADC module supports up to 28 separate analog inputs. An input is selected for conversion through the ADCH channel select bits.

## 9.4 **Register Definition**

These memory mapped registers control and monitor operation of the ADC:

- Status and control register, ADCSC1

- Status and control register, ADCSC2

- Data result registers, ADCRH and ADCRL

- Compare value registers, ADCCVH and ADCCVL

- Configuration register, ADCCFG

- Pin enable registers, APCTL1, APCTL2, APCTL3

## 9.4.1 Status and Control Register 1 (ADCSC1)

This section describes the function of the ADC status and control register (ADCSC1). Writing ADCSC1 aborts the current conversion and initiates a new conversion (if the ADCH bits are equal to a value other than all 1s).

| Table 9-8. Input | t Clock Select |

|------------------|----------------|

|------------------|----------------|

| ADICLK       | Selected Clock Source      |  |  |  |

|--------------|----------------------------|--|--|--|

| 00 Bus clock |                            |  |  |  |

| 01           | 01 Bus clock divided by 2  |  |  |  |

| 10           | Alternate clock (ALTCLK)   |  |  |  |

| 11           | Asynchronous clock (ADACK) |  |  |  |

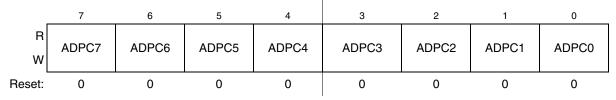

#### Pin Control 1 Register (APCTL1) 9.4.8

The pin control registers are used to disable the I/O port control of MCU pins used as analog inputs. APCTL1 is used to control the pins associated with channels 0–7 of the ADC module.

Figure 9-11. Pin Control 1 Register (APCTL1)

| Field      | Description                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADPC7 | <ul> <li>ADC Pin Control 7 — ADPC7 is used to control the pin associated with channel AD7.</li> <li>0 AD7 pin I/O control enabled</li> <li>1 AD7 pin I/O control disabled</li> </ul> |

| 6<br>ADPC6 | <ul> <li>ADC Pin Control 6 — ADPC6 is used to control the pin associated with channel AD6.</li> <li>0 AD6 pin I/O control enabled</li> <li>1 AD6 pin I/O control disabled</li> </ul> |

| 5<br>ADPC5 | <ul> <li>ADC Pin Control 5 — ADPC5 is used to control the pin associated with channel AD5.</li> <li>0 AD5 pin I/O control enabled</li> <li>1 AD5 pin I/O control disabled</li> </ul> |

| 4<br>ADPC4 | <ul> <li>ADC Pin Control 4 — ADPC4 is used to control the pin associated with channel AD4.</li> <li>0 AD4 pin I/O control enabled</li> <li>1 AD4 pin I/O control disabled</li> </ul> |

| 3<br>ADPC3 | <ul> <li>ADC Pin Control 3 — ADPC3 is used to control the pin associated with channel AD3.</li> <li>0 AD3 pin I/O control enabled</li> <li>1 AD3 pin I/O control disabled</li> </ul> |

| 2<br>ADPC2 | <ul> <li>ADC Pin Control 2 — ADPC2 is used to control the pin associated with channel AD2.</li> <li>0 AD2 pin I/O control enabled</li> <li>1 AD2 pin I/O control disabled</li> </ul> |

### 11.1.1 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Start and stop signal generation/detection

- Repeated start signal generation

- Acknowledge bit generation/detection

- Bus busy detection

- General call recognition

- 10-bit address extension

## 11.1.2 Modes of Operation

A brief description of the IIC in the various MCU modes is given here.

- **Run mode** This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module continues to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- **Stop mode** The IIC is inactive in stop3 mode for reduced power consumption. The stop instruction does not affect IIC register states. Stop2 resets the register contents.

### 11.1.3 Block Diagram

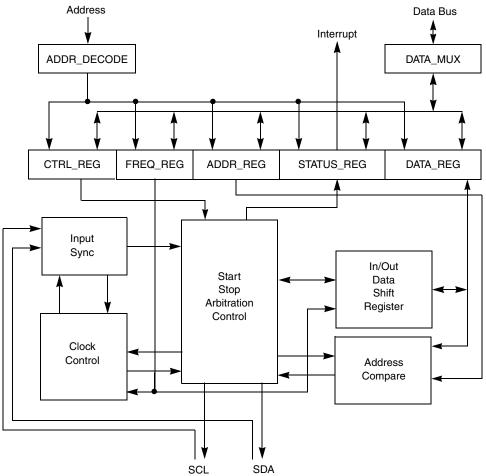

Figure 11-2 is a block diagram of the IIC.

Inter-Integrated Circuit (S08IICV2)

Figure 11-2. IIC Functional Block Diagram

# 11.2 External Signal Description

This section describes each user-accessible pin signal.

### 11.2.1 SCL — Serial Clock Line

The bidirectional SCL is the serial clock line of the IIC system.

### 11.2.2 SDA — Serial Data Line

The bidirectional SDA is the serial data line of the IIC system.

## **11.3 Register Definition**

This section consists of the IIC register descriptions in address order.

Refer to the direct-page register summary in the memory chapter of this document for the absolute address assignments for all IIC registers. This section refers to registers and control bits only by their names. A

## 11.4.1.5 Repeated Start Signal

As shown in Figure 11-9, a repeated start signal is a start signal generated without first generating a stop signal to terminate the communication. This is used by the master to communicate with another slave or with the same slave in different mode (transmit/receive mode) without releasing the bus.

### 11.4.1.6 Arbitration Procedure

The IIC bus is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, a clock synchronization procedure determines the bus clock, for which the low period is equal to the longest clock low period and the high is equal to the shortest one among the masters. The relative priority of the contending masters is determined by a data arbitration procedure, a bus master loses arbitration if it transmits logic 1 while another master transmits logic 0. The losing masters immediately switch over to slave receive mode and stop driving SDA output. In this case, the transition from master to slave mode does not generate a stop condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

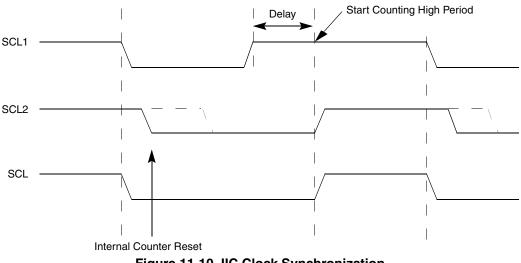

### 11.4.1.7 Clock Synchronization

Because wire-AND logic is performed on the SCL line, a high-to-low transition on the SCL line affects all the devices connected on the bus. The devices start counting their low period and after a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is still within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 11-10). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

Figure 11-10. IIC Clock Synchronization

MC9S08AC60 Series Data Sheet, Rev. 3

Serial Communications Interface (S08SCIV4)

Timer/PWM Module (S08TPMV3)

### 15.6.1.1 Counter Clock Source

The 2-bit field, CLKSB:CLKSA, in the timer status and control register (TPMxSC) selects one of three possible clock sources or OFF (which effectively disables the TPM). See Table 15-5. After any MCU reset, CLKSB:CLKSA=0:0 so no clock source is selected, and the TPM is in a very low power state. These control bits may be read or written at any time and disabling the timer (writing 00 to the CLKSB:CLKSA field) does not affect the values in the counter or other timer registers.

# Chapter 16 Development Support

# 16.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC) and the on-chip debug module (DBG). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip FLASH and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins (not even in test modes). Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

The alternate BDC clock source for MC9S08AC60 Series is the ICGLCLK. See Chapter 10, "Internal Clock Generator (S08ICGV4)" for more information about ICGCLK and how to select clock sources.

Appendix A Electrical Characteristics and Timing Specifications

# A.6 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

| Num | С | Parameter                                                                                                                                                                                                                                                                                                                                    | Symbol             | Min                                                                                              | Typ <sup>1</sup> | Max                    | Unit |

|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------|------------------|------------------------|------|

|     |   | Output high voltage — Low Drive (PTxDSn = 0)<br>$5 \text{ V}, \text{ I}_{\text{Load}} = -2 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = -0.6 \text{ mA}$<br>$5 \text{ V}, \text{ I}_{\text{Load}} = -0.4 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = -0.24 \text{ mA}$<br>Output high voltage — High Drive (PTxDSn = 1) |                    | $V_{DD} - 1.5$<br>$V_{DD} - 1.5$<br>$V_{DD} - 0.8$<br>$V_{DD} - 0.8$                             |                  |                        |      |

| 1   | Ρ | 5 V, $I_{Load} = -10$ mA<br>3 V, $I_{Load} = -3$ mA<br>5 V, $I_{Load} = -2$ mA<br>3 V, $I_{Load} = -0.4$ mA                                                                                                                                                                                                                                  |                    | V <sub>DD</sub> - 1.5<br>V <sub>DD</sub> - 1.5<br>V <sub>DD</sub> - 0.8<br>V <sub>DD</sub> - 0.8 |                  |                        | V    |

|     |   | Output low voltage — Low Drive (PTxDSn = 0)<br>5  V, I <sub>Load</sub> = 2 mA<br>3  V, I <sub>Load</sub> = 0.6 mA<br>5  V, I <sub>Load</sub> = 0.4 mA<br>3  V, I <sub>Load</sub> = 0.24 mA                                                                                                                                                   |                    | 1.5<br>1.5<br>0.8<br>0.8                                                                         |                  |                        |      |

| 2   | Ρ | Output low voltage — High Drive (PTxDSn = 1)<br>$5 \text{ V}, \text{ I}_{\text{Load}} = 10 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = 3 \text{ mA}$<br>$5 \text{ V}, \text{ I}_{\text{Load}} = 2 \text{ mA}$<br>$3 \text{ V}, \text{ I}_{\text{Load}} = 0.4 \text{ mA}$                                                          |                    | 1.5<br>1.5<br>0.8<br>0.8                                                                         |                  | <br>                   | v    |

| 3   | Ρ | Output high current — Max total I <sub>OH</sub> for all ports<br>5V<br>3V                                                                                                                                                                                                                                                                    | I <sub>ОНТ</sub>   |                                                                                                  |                  | 100<br>60              | mA   |

| 4   | Ρ | Output low current — Max total I <sub>OL</sub> for all ports<br>5V<br>3V                                                                                                                                                                                                                                                                     | I <sub>OLT</sub>   |                                                                                                  |                  | 100<br>60              | mA   |

| 5   | Ρ | Input high $2.7v \le V_{DD} 4.5v$                                                                                                                                                                                                                                                                                                            | V <sub>IH</sub>    | 0.70xV <sub>DD</sub>                                                                             | _                | —                      |      |

|     |   | voltage; all $4.5v \le V_{DD} \le 5.5v$                                                                                                                                                                                                                                                                                                      | V <sub>IH</sub>    | 0.65xV <sub>DD</sub>                                                                             |                  |                        | v    |

| 6   | Ρ | Input low voltage; all digital inputs                                                                                                                                                                                                                                                                                                        | V <sub>IL</sub>    | —                                                                                                | —                | 0.35 x V <sub>DD</sub> |      |

| 7   | Ρ | Input hysteresis; all digital inputs                                                                                                                                                                                                                                                                                                         | V <sub>hys</sub>   | 0.06 x V <sub>DD</sub>                                                                           |                  |                        | mV   |

| 8   | Ρ | Input leakage current; input only pins <sup>2</sup>                                                                                                                                                                                                                                                                                          | ll <sub>In</sub> l | —                                                                                                | 0.1              | 1                      | μA   |

| 9   | Ρ | High Impedance (off-state) leakage current <sup>2</sup>                                                                                                                                                                                                                                                                                      | ll <sub>oz</sub> l | —                                                                                                | 0.1              | 1                      | μA   |

| 10  | Ρ | Internal pullup resistors <sup>3</sup>                                                                                                                                                                                                                                                                                                       | R <sub>PU</sub>    | 20                                                                                               | 45               | 65                     | kΩ   |

| 11  | Ρ | Internal pulldown resistors <sup>4</sup>                                                                                                                                                                                                                                                                                                     | R <sub>PD</sub>    | 20                                                                                               | 45               | 65                     | kΩ   |

| 12  | С | Input Capacitance; all non-supply pins                                                                                                                                                                                                                                                                                                       | C <sub>In</sub>    | _                                                                                                | —                | 8                      | pF   |

| 13  | D | RAM retention voltage                                                                                                                                                                                                                                                                                                                        | V <sub>RAM</sub>   | —                                                                                                | 0.6              | 1.0                    | V    |

| 14  | Ρ | POR rearm voltage                                                                                                                                                                                                                                                                                                                            | V <sub>POR</sub>   | 0.9                                                                                              | 1.4              | 2.0                    | V    |

| 15  | D | POR rearm time                                                                                                                                                                                                                                                                                                                               | t <sub>POR</sub>   | 10                                                                                               | _                |                        | μS   |

#### Table A-6. DC Characteristics

# A.12 FLASH Specifications

This section provides details about program/erase times and program-erase endurance for the FLASH memory.

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see Chapter 4, "Memory."

| Num | С | Characteristic                                                                                                    | Symbol                  | Min    | Typ <sup>1</sup> | Max  | Unit              |

|-----|---|-------------------------------------------------------------------------------------------------------------------|-------------------------|--------|------------------|------|-------------------|

| 1   | Ρ | Supply voltage for program/erase                                                                                  | V <sub>prog/erase</sub> | 2.7    |                  | 5.5  | V                 |

| 2   | Ρ | Supply voltage for read operation                                                                                 | V <sub>Read</sub>       | 2.7    |                  | 5.5  | V                 |

| 3   | Ρ | Internal FCLK frequency <sup>2</sup>                                                                              | f <sub>FCLK</sub>       | 150    |                  | 200  | kHz               |

| 4   | Ρ | Internal FCLK period (1/FCLK)                                                                                     | t <sub>Fcyc</sub>       | 5      |                  | 6.67 | μS                |

| 5   | Ρ | Byte program time (random location) <sup>(2)</sup>                                                                | t <sub>prog</sub>       | 9      |                  |      | t <sub>Fcyc</sub> |

| 6   | С | Byte program time (burst mode) <sup>(2)</sup>                                                                     | t <sub>Burst</sub>      | 4      |                  |      | t <sub>Fcyc</sub> |

| 7   | Ρ | Page erase time <sup>3</sup>                                                                                      | t <sub>Page</sub>       | 4000   |                  |      | t <sub>Fcyc</sub> |

| 8   | Ρ | Mass erase time <sup>(2)</sup>                                                                                    | t <sub>Mass</sub>       | 20,000 |                  |      | t <sub>Fcyc</sub> |

| 9   | с | Program/erase endurance <sup>4</sup><br>T <sub>L</sub> to T <sub>H</sub> = $-40^{\circ}$ C to + 125°C<br>T = 25°C |                         | 10,000 | <br>100,000      |      | cyces             |

| 10  | С | Data retention <sup>5</sup>                                                                                       | t <sub>D_ret</sub>      | 15     | 100              |      | years             |

<sup>1</sup> Typical values are based on characterization data at  $V_{DD}$  = 5.0 V, 25°C unless otherwise stated.

<sup>2</sup> The frequency of this clock is controlled by a software setting.

<sup>3</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

- <sup>4</sup> Typical endurance for FLASH was evaluated for this product family on the 9S12Dx64. For additional information on how Freescale Semiconductor defines typical endurance, please refer to Engineering Bulletin EB619/D, *Typical Endurance for Nonvolatile Memory.*

- <sup>5</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines typical data retention, please refer to Engineering Bulletin EB618/D, *Typical Data Retention for Nonvolatile Memory.*