# E·XFL

### NXP USA Inc. - MC9S08AC48CPUE Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 54                                                                     |

| Program Memory Size        | 48KB (48K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08ac48cpue |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Section Number**

Title

### Page

| 7.3 | Address | sing Modes                      | 112 |

|-----|---------|---------------------------------|-----|

|     | 7.3.1   | Inherent Addressing Mode (INH)  | 113 |

|     | 7.3.2   | Relative Addressing Mode (REL)  | 113 |

|     | 7.3.3   | Immediate Addressing Mode (IMM) | 113 |

|     | 7.3.4   | Direct Addressing Mode (DIR)    | 113 |

|     | 7.3.5   | Extended Addressing Mode (EXT)  | 113 |

|     | 7.3.6   | Indexed Addressing Mode         | 113 |

| 7.4 | Special | Operations                      | 114 |

|     | 7.4.1   | Reset Sequence                  | 115 |

|     | 7.4.2   | Interrupt Sequence              | 115 |

|     |         | Wait Mode Operation             |     |

|     | 7.4.4   | Stop Mode Operation             | 116 |

|     |         | BGND Instruction                |     |

| 7.5 | HCS08   | Instruction Set Summary         | 117 |

# Chapter 8 Cyclic Redundancy Check (S08CRCV1)

| 8.1 | Introduc  | ction                                                | 129 |

|-----|-----------|------------------------------------------------------|-----|

|     | 8.1.1     | Features                                             | 129 |

|     | 8.1.2     | Modes of Operation                                   | 131 |

|     | 8.1.3     | Block Diagram                                        | 131 |

| 8.2 | Externa   | l Signal Description                                 | 131 |

| 8.3 | Registe   | r Definition                                         | 132 |

|     | 8.3.1     | Memory Map                                           | 132 |

|     |           | Register Descriptions                                |     |

| 8.4 | Function  | nal Description                                      | 133 |

|     | 8.4.1     | ITU-T (CCITT) recommendations & expected CRC results | 134 |

| 8.5 | Initializ | ation Information                                    | 134 |

|     |           |                                                      |     |

# Chapter 9 Analog-to-Digital Converter (S08ADC10V1)

| 9.1 | Overvie | W                                           | 137 |

|-----|---------|---------------------------------------------|-----|

| 9.2 | Channel | Assignments                                 | 137 |

|     |         | Alternate Clock                             |     |

|     | 9.2.2   | Hardware Trigger                            | 138 |

|     |         | Temperature Sensor                          |     |

|     |         | Features                                    |     |

|     | 9.2.5   | Block Diagram                               | 141 |

| 9.3 |         | I Signal Description                        |     |

|     |         | Analog Power (V <sub>DDAD</sub> )           |     |

|     |         | Analog Ground (V <sub>SSAD</sub> )          |     |

|     |         | Voltage Reference High (V <sub>REFH</sub> ) |     |

|     |         |                                             |     |

When security is enabled, the RAM is considered a secure memory resource and is not accessible through BDM or through code executing from non-secure memory. See Section 4.5, "Security" for a detailed description of the security feature.

# 4.4 FLASH

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire background debug interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths. For a more detailed discussion of in-circuit and in-application programming, refer to the *HCS08 Family Reference Manual, Volume I*, Freescale Semiconductor document order number HCS08RMv1/D.

### 4.4.1 Features

Features of the FLASH memory include:

- FLASH Size

- MC9S08AC60 61268 bytes (120 pages of 512 bytes each)

- MC9S08AC48 49152 bytes (96 pages of 512 bytes each)

- MC9S08AC32 32768 bytes (64 pages of 512 bytes each)

- Single power supply program and erase

- Command interface for fast program and erase operation

- Up to 100,000 program/erase cycles at typical voltage and temperature

- Flexible block protection

- Security feature for FLASH and RAM

- Auto power-down for low-frequency read accesses

### 4.4.2 Program and Erase Times

Before any program or erase command can be accepted, the FLASH clock divider register (FCDIV) must be written to set the internal clock for the FLASH module to a frequency ( $f_{FCLK}$ ) between 150 kHz and 200 kHz (see Table 4.6.1). This register can be written only once, so normally this write is done during reset initialization. FCDIV cannot be written if the access error flag, FACCERR in FSTAT, is set. The user must ensure that FACCERR is not set before writing to the FCDIV register. One period of the resulting clock ( $1/f_{FCLK}$ ) is used by the command processor to time program and erase pulses. An integer number of these timing pulses is used by the command processor to complete a program or erase command.

Table 4-5 shows program and erase times. The bus clock frequency and FCDIV determine the frequency of FCLK ( $f_{FCLK}$ ). The time for one cycle of FCLK is  $t_{FCLK} = 1/f_{FCLK}$ . The times are shown as a number of cycles of FCLK and as an absolute time for the case where  $t_{FCLK} = 5 \ \mu s$ . Program and erase times

### 4.4.5 Access Errors

An access error occurs whenever the command execution protocol is violated.

- Any of the following specific actions will cause the access error flag (FACCERR) in FSTAT to be set. FACCERR must be cleared by writing a 1 to FACCERR in FSTAT before any command can be processed.

- Writing to a FLASH address before the internal FLASH clock frequency has been set by writing to the FCDIV register

- Writing to a FLASH address while FCBEF is not set (A new command cannot be started until the command buffer is empty.)

- Writing a second time to a FLASH address before launching the previous command (There is only one write to FLASH for every command.)

- Writing a second time to FCMD before launching the previous command (There is only one write to FCMD for every command.)

- Writing to any FLASH control register other than FCMD after writing to a FLASH address

- Writing any command code other than the five allowed codes (\$05, \$20, \$25, \$40, or \$41) to FCMD

- Writing any FLASH control register other than the write to FSTAT (to clear FCBEF and launch the command) after writing the command to FCMD

- The MCU enters stop mode while a program or erase command is in progress (The command is aborted.)

- Writing the byte program, burst program, or page erase command code (\$20, \$25, or \$40) with a background debug command while the MCU is secured (The background debug controller can only do blank check and mass erase commands when the MCU is secure.)

- Writing 0 to FCBEF to cancel a partial command

### 4.4.6 FLASH Block Protection

Block protection prevents program or erase changes for FLASH memory locations in a designated address range. Mass erase is disabled when any block of FLASH is protected. The MC9S08AC60 Series allows a block of memory at the end of FLASH, and/or the entire FLASH memory to be block protected. A disable control bit and a 7-bit control field, allows the user to set the size of this block. All eight of these control bits are located in the FPROT register (see Section 4.6.4, "FLASH Protection Register (FPROT and NVPROT)").

At reset, the high-page register (FPROT) is loaded with the contents of the NVPROT location which is in the nonvolatile register block of the FLASH memory. The value in FPROT cannot be changed directly from application software so a runaway program cannot alter the block protection settings. If the last 512 bytes of FLASH which includes the NVPROT register is protected, the application program cannot alter the block protection settings (intentionally or unintentionally). The FPROT control bits can be written by background debug commands to allow a way to erase a protected FLASH memory.

One use for block protection is to block protect an area of FLASH memory for a bootloader program. This bootloader program then can be used to erase the rest of the FLASH memory and reprogram it. Because the bootloader is protected, it remains intact even if MCU power is lost in the middle of an erase and reprogram operation.

**Chapter 4 Memory**

Chapter 5 Resets, Interrupts, and System Configuration

- Illegal opcode detect

- Background debug forced reset

- The reset pin ( $\overline{\text{RESET}}$ )

- Clock generator loss of lock and loss of clock reset

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register. Whenever the MCU enters reset, the internal clock generator (ICG) module switches to self-clocked mode with the frequency of  $f_{Self}$  reset selected. The reset pin is driven low for 34 bus cycles where the internal bus frequency is half the ICG frequency. After the 34 bus cycles are completed, the pin is released and will be pulled up by the internal pullup resistor, unless it is held low externally. After the pin is released, it is sampled after another 38 bus cycles to determine whether the reset pin is the cause of the MCU reset.

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COPE becomes set in SOPT enabling the COP watchdog (see Section 5.9.4, "System Options Register (SOPT)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPE. The COP counter is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP counter.

The COPCLKS bit in SOPT2 (see Section 5.9.10, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 1-kHz clock source. With each clock source, there is an associated short and long time-out controlled by COPT in SOPT. Table 5-1 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the bus clock source and the associated long time-out (2<sup>18</sup> cycles).

| Cont    | rol Bits | Clock Source | COP Overflow Count                          |  |  |

|---------|----------|--------------|---------------------------------------------|--|--|

| COPCLKS | СОРТ     |              | COP Overnow Count                           |  |  |

| 0       | 0        | ~1 kHz       | 2 <sup>5</sup> cycles (32 ms) <sup>1</sup>  |  |  |

| 0       | 1        | ~1 kHz       | 2 <sup>8</sup> cycles (256 ms) <sup>1</sup> |  |  |

| 1       | 0        | Bus          | 2 <sup>13</sup> cycles                      |  |  |

| 1       | 1        | Bus          | 2 <sup>18</sup> cycles                      |  |  |

<sup>1</sup> Values are shown in this column based on  $t_{RTI} = 1$  ms. See  $t_{RTI}$  in the appendix Section A.10.1, "Control Timing," for the tolerance of this value.

#### Chapter 5 Resets, Interrupts, and System Configuration

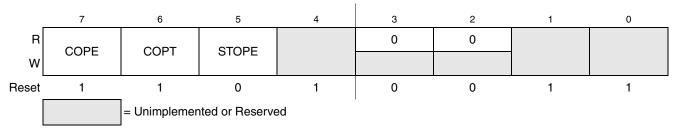

#### Figure 5-5. System Options Register (SOPT)

#### Table 5-6. SOPT Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COPE  | <ul> <li>COP Watchdog Enable — This write-once bit defaults to 1 after reset.</li> <li>0 COP watchdog timer disabled.</li> <li>1 COP watchdog timer enabled (force reset on timeout).</li> </ul>                                                                                                    |

| 6<br>COPT  | <ul> <li>COP Watchdog Timeout — This write-once bit defaults to 1 after reset.</li> <li>0 Short timeout period selected.</li> <li>1 Long timeout period selected.</li> </ul>                                                                                                                        |

| 5<br>STOPE | <ul> <li>Stop Mode Enable — This write-once bit defaults to 0 after reset, which disables stop mode. If stop mode is disabled and a user program attempts to execute a STOP instruction, an illegal opcode reset is forced.</li> <li>0 Stop mode disabled.</li> <li>1 Stop mode enabled.</li> </ul> |

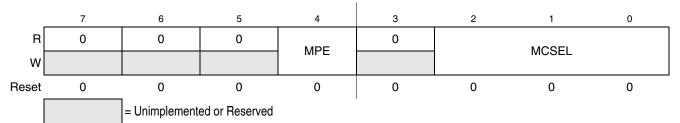

### 5.9.5 System MCLK Control Register (SMCLK)

This register is used to control the MCLK clock output.

### Figure 5-6. System MCLK Control Register (SMCLK)

#### Table 5-7. SMCLK Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MPE     | <ul> <li>MCLK Pin Enable — This bit is used to enable the MCLK function.</li> <li>0 MCLK output disabled.</li> <li>1 MCLK output enabled on PTC2 pin.</li> </ul>                                                                                                                     |

| 2:0<br>MCSEL | <b>MCLK Divide Select</b> — These bits are used to select the divide ratio for the MCLK output according to the formula below when the MCSEL bits are not equal to all zeroes. In the case that the MCSEL bits are all zero and MPE is set, the pin is driven low. See Equation 5-1. |

#### MCLK frequency = Bus Clock frequency ÷ (2 \* MCSEL)

Eqn. 5-1

MC9S08AC60 Series Data Sheet, Rev. 3

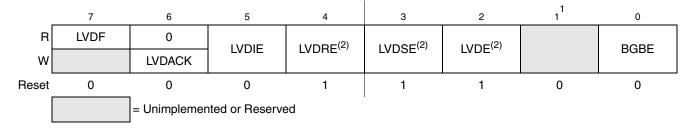

### 5.9.8 System Power Management Status and Control 1 Register (SPMSC1)

<sup>1</sup> Bit 1 is a reserved bit that must always be written to 0.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

### Figure 5-10. System Power Management Status and Control 1 Register (SPMSC1)

| Field       | Description                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVDF   | <b>Low-Voltage Detect Flag</b> — Provided LVDE = 1, this read-only status bit indicates a low-voltage detect event.                                                                                                                                                                                    |

| 6<br>LVDACK | <b>Low-Voltage Detect Acknowledge</b> — This write-only bit is used to acknowledge low voltage detection errors (write 1 to clear LVDF). Reads always return 0.                                                                                                                                        |

| 5<br>LVDIE  | <ul> <li>Low-Voltage Detect Interrupt Enable — This read/write bit enables hardware interrupt requests for LVDF.</li> <li>Hardware interrupt disabled (use polling).</li> <li>Request a hardware interrupt when LVDF = 1.</li> </ul>                                                                   |

| 4<br>LVDRE  | <ul> <li>Low-Voltage Detect Reset Enable — This read/write bit enables LVDF events to generate a hardware reset (provided LVDE = 1).</li> <li>0 LVDF does not generate hardware resets.</li> <li>1 Force an MCU reset when LVDF = 1.</li> </ul>                                                        |

| 3<br>LVDSE  | <ul> <li>Low-Voltage Detect Stop Enable — Provided LVDE = 1, this read/write bit determines whether the low-voltage detect function operates when the MCU is in stop mode.</li> <li>0 Low-voltage detect disabled during stop mode.</li> <li>1 Low-voltage detect enabled during stop mode.</li> </ul> |

| 2<br>LVDE   | <ul> <li>Low-Voltage Detect Enable — This read/write bit enables low-voltage detect logic and qualifies the operation of other bits in this register.</li> <li>UVD logic disabled.</li> <li>LVD logic enabled.</li> </ul>                                                                              |

| 0<br>BGBE   | <ul> <li>Bandgap Buffer Enable — The BGBE bit is used to enable an internal buffer for the bandgap voltage reference for use by the ADC module on one of its internal channels.</li> <li>0 Bandgap buffer disabled.</li> <li>1 Bandgap buffer enabled.</li> </ul>                                      |

### Table 5-12. SPMSC1 Register Field Descriptions

### 6.4.1 Internal Pullup Enable

An internal pullup device can be enabled for each port pin by setting the corresponding bit in one of the pullup enable registers (PTxPEn). The pullup device is disabled if the pin is configured as an output by the parallel I/O control logic or any shared peripheral function regardless of the state of the corresponding pullup enable register bit. The pullup device is also disabled if the pin is controlled by an analog function.

### 6.4.2 Output Slew Rate Control Enable

Slew rate control can be enabled for each port pin by setting the corresponding bit in one of the slew rate control registers (PTxSEn). When enabled, slew control limits the rate at which an output can transition in order to reduce EMC emissions. Slew rate control has no effect on pins which are configured as inputs.

# 6.4.3 Output Drive Strength Select

An output pin can be selected to have high output drive strength by setting the corresponding bit in one of the drive strength select registers (PTxDSn). When high drive is selected a pin is capable of sourcing and sinking greater current. Even though every I/O pin can be selected as high drive, the user must ensure that the total current source and sink limits for the chip are not exceeded. Drive strength selection is intended to affect the DC behavior of I/O pins. However, the AC behavior is also affected. High drive allows a pin to drive a greater load with the same switching speed as a low drive enabled pin into a smaller load. Because of this the EMC emissions may be affected by enabling pins as high drive.

# 7.4.3 Wait Mode Operation

The WAIT instruction enables interrupts by clearing the I bit in the CCR. It then halts the clocks to the CPU to reduce overall power consumption while the CPU is waiting for the interrupt or reset event that will wake the CPU from wait mode. When an interrupt or reset event occurs, the CPU clocks will resume and the interrupt or reset event will be processed normally.

If a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in wait mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in wait mode.

# 7.4.4 Stop Mode Operation

Usually, all system clocks, including the crystal oscillator (when used), are halted during stop mode to minimize power consumption. In such systems, external circuitry is needed to control the time spent in stop mode and to issue a signal to wake up the target MCU when it is time to resume processing. Unlike the earlier M68HC05 and M68HC08 MCUs, the HCS08 can be configured to keep a minimum set of clocks running in stop mode. This optionally allows an internal periodic signal to wake the target MCU from stop mode.

When a host debug system is connected to the background debug pin (BKGD) and the ENBDM control bit has been set by a serial command through the background interface (or because the MCU was reset into active background mode), the oscillator is forced to remain active when the MCU enters stop mode. In this case, if a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in stop mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in stop mode.

Recovery from stop mode depends on the particular HCS08 and whether the oscillator was stopped in stop mode. Refer to the Modes of Operation chapter for more details.

# 7.4.5 BGND Instruction

The BGND instruction is new to the HCS08 compared to the M68HC08. BGND would not be used in normal user programs because it forces the CPU to stop processing user instructions and enter the active background mode. The only way to resume execution of the user program is through reset or by a host debug system issuing a GO, TRACE1, or TAGGO serial command through the background debug interface.

Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program.

### Table 7-2. . Instruction Set Summary (Sheet 9 of 9)

| Source<br>Form | Operation                                                            | ddress<br>Mode | Object Code | Cycles | Cyc-by-Cyc<br>Details | on (    | ect<br>CCR<br>I N Z C |

|----------------|----------------------------------------------------------------------|----------------|-------------|--------|-----------------------|---------|-----------------------|

| TXS            | Transfer Index Reg. to SP SP $\leftarrow$ (H:X) – \$0001             | INH            | 94          | 2      | fp                    | - 1 1 - |                       |

| WAIT           | Enable Interrupts; Wait for Interrupt I bit $\leftarrow$ 0; Halt CPU | INH            | 8F          | 2+     | fp                    | -11-    | 0                     |

Source Form: Everything in the source forms columns, except expressions in italic characters, is literal information which must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic and the characters (#, () and +) are always a literal characters.

- Any label or expression that evaluates to a single integer in the range 0-7. n

- opr8i Any label or expression that evaluates to an 8-bit immediate value.

- opr16i Any label or expression that evaluates to a 16-bit immediate value.

- opr8a Any label or expression that evaluates to an 8-bit direct-page address (\$00xx).

- Any label or expression that evaluates to a 16-bit address. opr16a

- oprx8 Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing.

- Any label or expression that evaluates to a 16-bit value, used for indexed addressing. oprx16

- Any label or expression that refers to an address that is within -128 to +127 locations from the start of the next instruction. rel

#### **Operation Symbols:**

- Accumulator А

- CCR Condition code register

- н Index register high byte

- Μ Memory location

- Any bit п

- Operand (one or two bytes) opr

- PC Program counter

- Program counter high byte PCH

- Program counter low byte PCL

- Relative program counter offset byte rel

- SP Stack pointer

- SPL Stack pointer low byte

- Х Index register low byte

- & Logical AND

- L Logical OR

- $\oplus$ Logical EXCLUSIVE OR

- Contents of ()

- Add +

- Subtract, Negation (two's complement)

- × Multiply

- Divide ÷

- # Immediate value

- Loaded with ←

- Concatenated with :

#### CCR Bits:

- V Overflow bit

- Half-carry bit н

- L Interrupt mask

- Ν Negative bit

- Ζ Zero bit

- С Carry/borrow bit

- Addressing Modes:

- DIR Direct addressing mode FXT

- Extended addressing mode IMM

- Immediate addressing mode

- INH Inherent addressing mode

- Indexed, no offset addressing mode IX

- IX1 Indexed, 8-bit offset addressing mode

- IX2 Indexed, 16-bit offset addressing mode

- Indexed, no offset, post increment addressing mode IX+

- Indexed, 8-bit offset, post increment addressing mode IX1+

- REL Relative addressing mode

- Stack pointer, 8-bit offset addressing mode SP1

- Stack pointer 16-bit offset addressing mode SP2

#### Cycle-by-Cycle Codes:

- Free cycle. This indicates a cycle where the CPU f does not require use of the system buses. An f cycle is always one cycle of the system bus clock and is always a read cycle.

- Progryam fetch; read from next consecutive р location in program memory

- Read 8-bit operand r

- s Push (write) one byte onto stack

- Pop (read) one byte from stack u

- Read vector from \$FFxx (high byte first) v

- Write 8-bit operand w

#### CCR Effects:

MC9S08AC60 Series Data Sheet, Rev. 3

- Set or cleared \$

- Not affected

- U Undefined

5. Repeat steps 3-4 until the end of all data to be checked.

# Chapter 11 Inter-Integrated Circuit (S08IICV2)

# 11.1 Introduction

The inter-integrated circuit (IIC) provides a method of communication between a number of devices. The interface is designed to operate up to 100 kbps with maximum bus loading and timing. The device is capable of operating at higher baud rates, up to a maximum of clock/20, with reduced bus loading. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400 pF.

For additional detail, please refer to volume 1 of the *HCS08 Reference Manual*, (Freescale Semiconductor document order number HCS08RMv1/D).

The MC9S08AC60 series of microcontrollers has an inter-integrated circuit (IIC) module for communication with other integrated circuits.

# 11.4 Functional Description

This section provides a complete functional description of the IIC module.

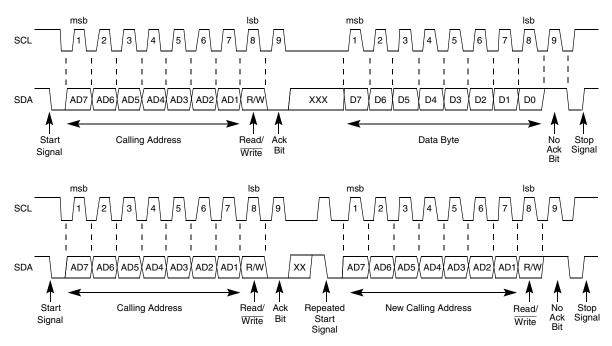

### 11.4.1 IIC Protocol

The IIC bus system uses a serial data line (SDA) and a serial clock line (SCL) for data transfer. All devices connected to it must have open drain or open collector outputs. A logic AND function is exercised on both lines with external pull-up resistors. The value of these resistors is system dependent.

Normally, a standard communication is composed of four parts:

- Start signal

- Slave address transmission

- Data transfer

- Stop signal

The stop signal should not be confused with the CPU stop instruction. The IIC bus system communication is described briefly in the following sections and illustrated in Figure 11-9.

Figure 11-9. IIC Bus Transmission Signals

### 11.4.1.1 Start Signal

When the bus is free, no master device is engaging the bus (SCL and SDA lines are at logical high), a master may initiate communication by sending a start signal. As shown in Figure 11-9, a start signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

#### Serial Communications Interface (S08SCIV4)

status flag is set. If RDRF was already set indicating the receive data register (buffer) was already full, the overrun (OR) status flag is set and the new data is lost. Because the SCI receiver is double-buffered, the program has one full character time after RDRF is set before the data in the receive data buffer must be read to avoid a receiver overrun.

When a program detects that the receive data register is full (RDRF = 1), it gets the data from the receive data register by reading SCIxD. The RDRF flag is cleared automatically by a 2-step sequence which is normally satisfied in the course of the user's program that handles receive data. Refer to Section 13.3.4, "Interrupts and Status Flags" for more details about flag clearing.

### 13.3.3.1 Data Sampling Technique

The SCI receiver uses a 16× baud rate clock for sampling. The receiver starts by taking logic level samples at 16 times the baud rate to search for a falling edge on the RxD serial data input pin. A falling edge is defined as a logic 0 sample after three consecutive logic 1 samples. The 16× baud rate clock is used to divide the bit time into 16 segments labeled RT1 through RT16. When a falling edge is located, three more samples are taken at RT3, RT5, and RT7 to make sure this was a real start bit and not merely noise. If at least two of these three samples are 0, the receiver assumes it is synchronized to a receive character.

The receiver then samples each bit time, including the start and stop bits, at RT8, RT9, and RT10 to determine the logic level for that bit. The logic level is interpreted to be that of the majority of the samples taken during the bit time. In the case of the start bit, the bit is assumed to be 0 if at least two of the samples at RT3, RT5, and RT7 are 0 even if one or all of the samples taken at RT8, RT9, and RT10 are 1s. If any sample in any bit time (including the start and stop bits) in a character frame fails to agree with the logic level for that bit, the noise flag (NF) will be set when the received character is transferred to the receive data buffer.

The falling edge detection logic continuously looks for falling edges, and if an edge is detected, the sample clock is resynchronized to bit times. This improves the reliability of the receiver in the presence of noise or mismatched baud rates. It does not improve worst case analysis because some characters do not have any extra falling edges anywhere in the character frame.

In the case of a framing error, provided the received character was not a break character, the sampling logic that searches for a falling edge is filled with three logic 1 samples so that a new start bit can be detected almost immediately.

In the case of a framing error, the receiver is inhibited from receiving any new characters until the framing error flag is cleared. The receive shift register continues to function, but a complete character cannot transfer to the receive data buffer if FE is still set.

### 13.3.3.2 Receiver Wakeup Operation

Receiver wakeup is a hardware mechanism that allows an SCI receiver to ignore the characters in a message that is intended for a different SCI receiver. In such a system, all receivers evaluate the first character(s) of each message, and as soon as they determine the message is intended for a different receiver, they write logic 1 to the receiver wake up (RWU) control bit in SCIxC2. When RWU bit is set, the status flags associated with the receiver (with the exception of the idle bit, IDLE, when RWUID bit is set) are inhibited from setting, thus eliminating the software overhead for handling the unimportant

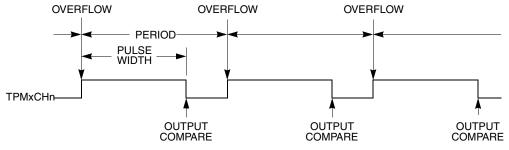

In output compare mode, values are transferred to the corresponding timer channel registers only after both 8-bit halves of a 16-bit register have been written and according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), the registers are updated at the next change of the TPM counter (end of the prescaler counting) after the second byte is written.

The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An output compare event sets a flag bit (CHnF) which may optionally generate a CPU-interrupt request.

### 15.6.2.3 Edge-Aligned PWM Mode

This type of PWM output uses the normal up-counting mode of the timer counter (CPWMS=0) and can be used when other channels in the same TPM are configured for input capture or output compare functions. The period of this PWM signal is determined by the value of the modulus register (TPMxMODH:TPMxMODL) plus 1. The duty cycle is determined by the setting in the timer channel register (TPMxCnVH:TPMxCnVL). The polarity of this PWM signal is determined by the setting in the ELSnA control bit. 0% and 100% duty cycle cases are possible.

The output compare value in the TPM channel registers determines the pulse width (duty cycle) of the PWM signal (Figure 15-15). The time between the modulus overflow and the output compare is the pulse width. If ELSnA=0, the counter overflow forces the PWM signal high, and the output compare forces the PWM signal low. If ELSnA=1, the counter overflow forces the PWM signal low, and the output compare forces the PWM signal high.

Figure 15-15. PWM Period and Pulse Width (ELSnA=0)

When the channel value register is set to 0x0000, the duty cycle is 0%. 100% duty cycle can be achieved by setting the timer-channel register (TPMxCnVH:TPMxCnVL) to a value greater than the modulus setting. This implies that the modulus setting must be less than 0xFFFF in order to get 100% duty cycle.

Because the TPM may be used in an 8-bit MCU, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers TPMxCnVH and TPMxCnVL, actually write to buffer registers. In edge-aligned PWM mode, values are transferred to the corresponding timer-channel registers according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If

#### Development Support

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

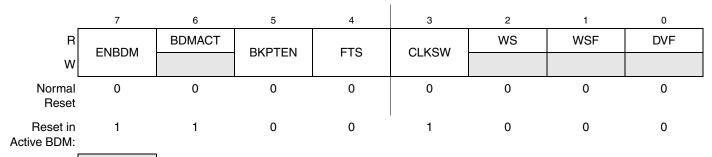

# 16.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

#### **Development Support**

the host must perform ((8 - CNT) - 1) dummy reads of the FIFO to advance it to the first significant entry in the FIFO.

In most trigger modes, the information stored in the FIFO consists of 16-bit change-of-flow addresses. In these cases, read DBGFH then DBGFL to get one coherent word of information out of the FIFO. Reading DBGFL (the low-order byte of the FIFO data port) causes the FIFO to shift so the next word of information is available at the FIFO data port. In the event-only trigger modes (see Section 16.3.5, "Trigger Modes"), 8-bit data information is stored into the FIFO. In these cases, the high-order half of the FIFO (DBGFH) is not used and data is read out of the FIFO by simply reading DBGFL. Each time DBGFL is read, the FIFO is shifted so the next data value is available through the FIFO data port at DBGFL.

In trigger modes where the FIFO is storing change-of-flow addresses, there is a delay between CPU addresses and the input side of the FIFO. Because of this delay, if the trigger event itself is a change-of-flow address or a change-of-flow address appears during the next two bus cycles after a trigger event starts the FIFO, it will not be saved into the FIFO. In the case of an end-trace, if the trigger event is a change-of-flow, it will be saved as the last change-of-flow entry for that debug run.

The FIFO can also be used to generate a profile of executed instruction addresses when the debugger is not armed. When ARM = 0, reading DBGFL causes the address of the most-recently fetched opcode to be saved in the FIFO. To use the profiling feature, a host debugger would read addresses out of the FIFO by reading DBGFH then DBGFL at regular periodic intervals. The first eight values would be discarded because they correspond to the eight DBGFL reads needed to initially fill the FIFO. Additional periodic reads of DBGFH and DBGFL return delayed information about executed instructions so the host debugger can develop a profile of executed instruction addresses.

### 16.3.3 Change-of-Flow Information

To minimize the amount of information stored in the FIFO, only information related to instructions that cause a change to the normal sequential execution of instructions is stored. With knowledge of the source and object code program stored in the target system, an external debugger system can reconstruct the path of execution through many instructions from the change-of-flow information stored in the FIFO.

For conditional branch instructions where the branch is taken (branch condition was true), the source address is stored (the address of the conditional branch opcode). Because BRA and BRN instructions are not conditional, these events do not cause change-of-flow information to be stored in the FIFO.

Indirect JMP and JSR instructions use the current contents of the H:X index register pair to determine the destination address, so the debug system stores the run-time destination address for any indirect JMP or JSR. For interrupts, RTI, or RTS, the destination address is stored in the FIFO as change-of-flow information.

# 16.3.4 Tag vs. Force Breakpoints and Triggers

Tagging is a term that refers to identifying an instruction opcode as it is fetched into the instruction queue, but not taking any other action until and unless that instruction is actually executed by the CPU. This distinction is important because any change-of-flow from a jump, branch, subroutine call, or interrupt causes some instructions that have been fetched into the instruction queue to be thrown away without being executed.

Development Support

### 16.4.1.1 BDC Status and Control Register (BDCSCR)

This register can be read or written by serial BDC commands (READ\_STATUS and WRITE\_CONTROL) but is not accessible to user programs because it is not located in the normal memory map of the MCU.

= Unimplemented or Reserved

### Figure 16-5. BDC Status and Control Register (BDCSCR)

#### Table 16-2. BDCSCR Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ENBDM  | <ul> <li>Enable BDM (Permit Active Background Mode) — Typically, this bit is written to 1 by the debug host shortly after the beginning of a debug session or whenever the debug host resets the target and remains 1 until a normal reset clears it.</li> <li>0 BDM cannot be made active (non-intrusive commands still allowed)</li> <li>1 BDM can be made active to allow active background mode commands</li> </ul>                                                                                                                                                                                                                                                |

| 6<br>BDMACT | <ul> <li>Background Mode Active Status — This is a read-only status bit.</li> <li>0 BDM not active (user application program running)</li> <li>1 BDM active and waiting for serial commands</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5<br>BKPTEN | <ul> <li>BDC Breakpoint Enable — If this bit is clear, the BDC breakpoint is disabled and the FTS (force tag select) control bit and BDCBKPT match register are ignored.</li> <li>0 BDC breakpoint disabled</li> <li>1 BDC breakpoint enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4<br>FTS    | <ul> <li>Force/Tag Select — When FTS = 1, a breakpoint is requested whenever the CPU address bus matches the BDCBKPT match register. When FTS = 0, a match between the CPU address bus and the BDCBKPT register causes the fetched opcode to be tagged. If this tagged opcode ever reaches the end of the instruction queue, the CPU enters active background mode rather than executing the tagged opcode.</li> <li>0 Tag opcode at breakpoint address and enter active background mode if CPU attempts to execute that instruction</li> <li>1 Breakpoint match forces active background mode at next instruction boundary (address need not be an opcode)</li> </ul> |

| 3<br>CLKSW  | Select Source for BDC Communications Clock — CLKSW defaults to 0, which selects the alternate BDC clock source.         0       Alternate BDC clock source         1       MCU bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

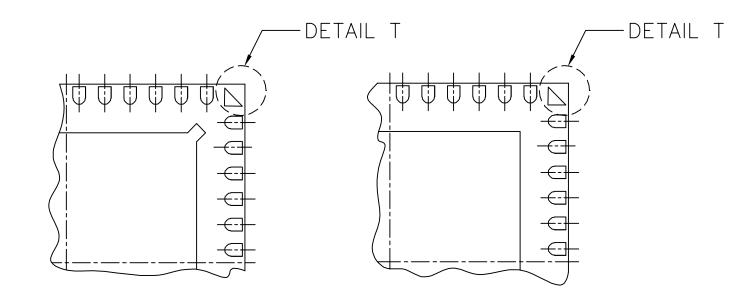

DETAIL M PIN 1 BACKSIDE IDENTIFIER OPTION

DETAIL M PIN 1 BACKSIDE IDENTIFIER OPTION

DETAIL T

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. |                                  |                   | PRINT VERSION NO | T TO SCALE |

|---------------------------------------------------------|----------------------------------|-------------------|------------------|------------|

| TITLE: THERMALLY ENHANCED                               | DOCUMENT NO                      | ): 98ARH99048A    | REV: F           |            |

| FLAT NON-LEADED PACKA                                   | CASE NUMBER: 1314-05 05 DEC 2005 |                   |                  |            |

| 48 TERMINAL, 0.5 PITCH (7                               | STANDARD: JE                     | DEC-MO-220 VKKD-2 | 2                |            |

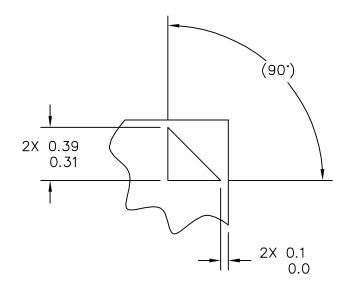

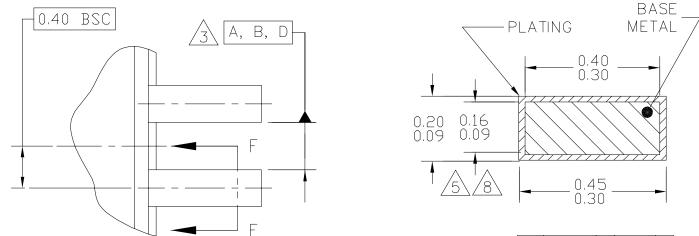

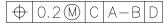

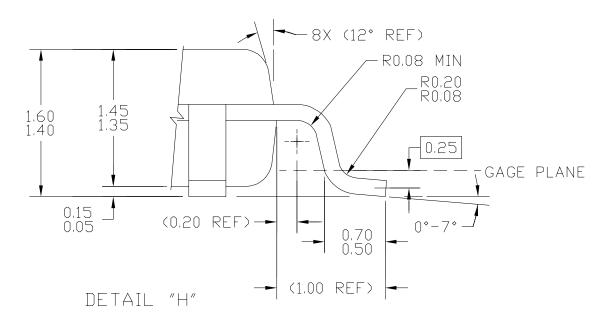

SECTION F-F Rotated 90°CW 32 places

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED.                         | MECHANICAL OUTLINE |                            | PRINT VERSION NOT TO SCALE |             |

|---------------------------------------------------------------------------------|--------------------|----------------------------|----------------------------|-------------|

| TITLE:<br>LOW PROFILE QUAD FLAT PACK (LQFP)<br>32 LEAD, 0.8 PITCH (7 X 7 X 1.4) |                    | DOCUMENT NO: 98ASH70029A   |                            | RE∨: D      |

|                                                                                 |                    | CASE NUMBER: 873A-03       |                            | 19 MAY 2005 |

|                                                                                 |                    | STANDARD: JEDEC MS-026 BBA |                            |             |

DETAIL G