#### NXP USA Inc. - MC9S08AC60CPUER Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S08                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 54                                                                      |

| Program Memory Size        | 60KB (60K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08ac60cpuer |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Section Number**

### Title

### Page

| 10.3.3 ICG Status Register 1 (ICGS1)                            |              |

|-----------------------------------------------------------------|--------------|

| 10.3.4 ICG Status Register 2 (ICGS2)                            |              |

| 10.3.5 ICG Filter Registers (ICGFLTU, ICGFLTL)                  |              |

| 10.3.6 ICG Trim Register (ICGTRM)                               |              |

| 10.4 Functional Description                                     |              |

| 10.4.1 Off Mode (Off)                                           |              |

| 10.4.2 Self-Clocked Mode (SCM)                                  |              |

| 10.4.3 FLL Engaged, Internal Clock (FEI) Mode                   |              |

| 10.4.4 FLL Engaged Internal Unlocked                            |              |

| 10.4.5 FLL Engaged Internal Locked                              |              |

| 10.4.6 FLL Bypassed, External Clock (FBE) Mode                  |              |

| 10.4.7 FLL Engaged, External Clock (FEE) Mode                   |              |

| 10.4.8 FLL Lock and Loss-of-Lock Detection                      |              |

| 10.4.9 FLL Loss-of-Clock Detection                              |              |

| 10.4.10Clock Mode Requirements                                  |              |

| 10.4.11Fixed Frequency Clock                                    |              |

| 10.4.12High Gain Oscillator                                     |              |

| 10.5 Initialization/Application Information                     |              |

| 10.5.1 Introduction                                             |              |

| 10.5.2 Example #1: External Crystal = 32 kHz, Bus Frequency = 4 | .19 MHz185   |

| 10.5.3 Example #2: External Crystal = 4 MHz, Bus Frequency = 2  | 0 MHz187     |

| 10.5.4 Example #3: No External Crystal Connection, 5.4 MHz Bus  | Frequency189 |

| 10.5.5 Example #4: Internal Clock Generator Trim                |              |

## Chapter 11 Inter-Integrated Circuit (S08IICV2)

| 11.1 | Introduction                                 |     |

|------|----------------------------------------------|-----|

|      | 11.1.1 Features                              | 195 |

|      | 11.1.2 Modes of Operation                    |     |

|      | 11.1.3 Block Diagram                         |     |

| 11.2 | External Signal Description                  | 196 |

|      | 11.2.1 SCL — Serial Clock Line               |     |

|      | 11.2.2 SDA — Serial Data Line                | 196 |

| 11.3 | Register Definition                          |     |

|      | 11.3.1 IIC Address Register (IICA)           |     |

|      | 11.3.2 IIC Frequency Divider Register (IICF) | 197 |

|      | 11.3.3 IIC Control Register (IICC1)          |     |

|      | 11.3.4 IIC Status Register (IICS)            |     |

|      | 11.3.5 IIC Data I/O Register (IICD)          | 201 |

|      | 11.3.6 IIC Control Register 2 (IICC2)        |     |

| 11.4 | Functional Description                       | 203 |

|      | 11.4.1 IIC Protocol                          |     |

|      |                                              |     |

| Address           | Register Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|-------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x183B<br>0x183F  | Reserved      | _      | _      | _      | _      | _      | _      | _      | _      |

| 0x1840            | ΡΤΑΡΕ         | PTAPE7 | PTAPE6 | PTAPE5 | PTAPE4 | PTAPE3 | PTAPE2 | PTAPE1 | PTAPE0 |

| 0x1841            | PTASE         | PTASE7 | PTASE6 | PTASE5 | PTASE4 | PTASE3 | PTASE2 | PTASE1 | PTASE0 |

| 0x1842            | PTADS         | PTADS7 | PTADS6 | PTADS5 | PTADS4 | PTADS3 | PTADS2 | PTADS1 | PTADS0 |

| 0x1843            | Reserved      | —      | _      | _      | _      | —      | _      | —      | —      |

| 0x1844            | PTBPE         | PTBPE7 | PTBPE6 | PTBPE5 | PTBPE4 | PTBPE3 | PTBPE2 | PTBPE1 | PTBPE0 |

| 0x1845            | PTBSE         | PTBSE7 | PTBSE6 | PTBSE5 | PTBSE4 | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| 0x1846            | PTBDS         | PTBDS7 | PTBDS6 | PTBDS5 | PTBDS4 | PTBDS3 | PTBDS2 | PTBDS1 | PTBDS0 |

| 0x1847            | Reserved      |        |        |        | _      | —      |        |        |        |

| 0x1848            | PTCPE         | 0      | PTCPE6 | PTCPE5 | PTCPE4 | PTCPE3 | PTCPE2 | PTCPE1 | PTCPE0 |

| 0x1849            | PTCSE         | 0      | PTCSE6 | PTCSE5 | PTCSE4 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| 0x184A            | PTCDS         | 0      | PTCDS6 | PTCDS5 | PTCDS4 | PTCDS3 | PTCDS2 | PTCDS1 | PTCDS0 |

| 0x184B            | Reserved      | —      | _      | _      | -      | —      |        | —      | —      |

| 0x184C            | PTDPE         | PTDPE7 | PTDPE6 | PTDPE5 | PTDPE4 | PTDPE3 | PTDPE2 | PTDPE1 | PTDPE0 |

| 0x184D            | PTDSE         | PTDSE7 | PTDSE6 | PTDSE5 | PTDSE4 | PTDSE3 | PTDSE2 | PTDSE1 | PTDSE0 |

| 0x184E            | PTDDS         | PTDDS7 | PTDDS6 | PTDDS5 | PTDDS4 | PTDDS3 | PTDDS2 | PTDDS1 | PTDDS0 |

| 0x184F            | Reserved      |        |        | _      |        | _      |        | _      |        |

| 0x1850            | PTEPE         | PTEPE7 | PTEPE6 | PTEPE5 | PTEPE4 | PTEPE3 | PTEPE2 | PTEPE1 | PTEPE0 |

| 0x1851            | PTESE         | PTESE7 | PTESE6 | PTESE5 | PTESE4 | PTESE3 | PTESE2 | PTESE1 | PTESE0 |

| 0x1852            | PTEDS         | PTEDS7 | PTEDS6 | PTEDS5 | PTEDS4 | PTEDS3 | PTEDS2 | PTEDS1 | PTEDS0 |

| 0x1853            | Reserved      | —      | _      | —      | _      | —      | _      | —      | —      |

| 0x1854            | PTFPE         | PTFPE7 | PTFPE6 | PTFPE5 | PTFPE4 | PTFPE3 | PTFPE2 | PTFPE1 | PTFPE0 |

| 0x1855            | PTFSE         | PTFSE7 | PTFSE6 | PTFSE5 | PTFSE4 | PTFSE3 | PTFSE2 | PTFSE1 | PTFSE0 |

| 0x1856            | PTFDS         | PTFDS7 | PTFDS6 | PTFDS5 | PTFDS4 | PTFDS3 | PTFDS2 | PTFDS1 | PTFDS0 |

| 0x1857            | Reserved      | —      | _      | —      | _      | —      | _      | —      | —      |

| 0x1858            | PTGPE         | 0      | PTGPE6 | PTGPE5 | PTGPE4 | PTGPE3 | PTGPE2 | PTGPE1 | PTGPE0 |

| 0x1859            | PTGSE         | 0      | PTGSE6 | PTGSE5 | PTGSE4 | PTGSE3 | PTGSE2 | PTGSE1 | PTGSE0 |

| 0x185A            | PTGDS         | 0      | PTGDS6 | PTGDS5 | PTGDS4 | PTGDS3 | PTGDS2 | PTGDS1 | PTGDS0 |

| 0x185B–<br>0x185F | Reserved      | —      |        |        |        | —      |        | —      |        |

Table 4-3. High-Page Register Summary (Sheet 3 of 3)

<sup>1</sup> This reserved bit must always be written to 0.

Nonvolatile FLASH registers, shown in Table 4-4, are located in the FLASH memory. These registers include an 8-byte backdoor key which optionally can be used to gain access to secure memory resources. During reset events, the contents of NVPROT and NVOPT in the nonvolatile register area of the FLASH memory are transferred into corresponding FPROT and FOPT working registers in the high-page registers to control security and block protection options.

Chapter 5 Resets, Interrupts, and System Configuration

## 5.9.2 System Reset Status Register (SRS)

This register includes read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

| _                   | 7   | 6   | 5               | 4            | 3               | 2            | 1    | 0 |

|---------------------|-----|-----|-----------------|--------------|-----------------|--------------|------|---|

| R                   | POR | PIN | COP             | ILOP         | Reserved        | ICG          | LVD  | 0 |

| w                   |     | Wr  | iting any value | to SIMRS add | ress clears COI | vatchdog tim | ner. |   |

| POR                 | 1   | 0   | 0               | 0            | 0               | 0            | 1    | 0 |

| LVR:                | U   | 0   | 0               | 0            | 0               | 0            | 1    | 0 |

| Any other<br>reset: | 0   | (1) | (1)             | (1)          | 0               | (1)          | 0    | 0 |

.....

U = Unaffected by reset

<sup>1</sup> Any of these reset sources that are active at the time of reset will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset will be cleared.

#### Figure 5-3. System Reset Status (SRS)

#### Table 5-4. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVR) status bit is also set to indicate that the reset occurred while the internal supply was below the LVR threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul>                                                           |

| 6<br>PIN  | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                                                                                   |

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source may be blocked by COPE = 0.</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                                                       |

| 4<br>ILOP | Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.         0       Reset not caused by an illegal opcode.         1       Reset caused by an illegal opcode. |

#### Chapter 5 Resets, Interrupts, and System Configuration

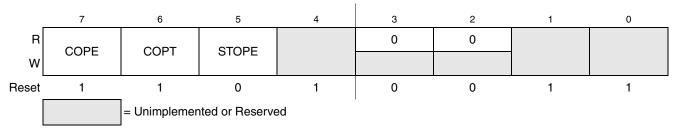

#### Figure 5-5. System Options Register (SOPT)

#### Table 5-6. SOPT Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COPE  | <ul> <li>COP Watchdog Enable — This write-once bit defaults to 1 after reset.</li> <li>0 COP watchdog timer disabled.</li> <li>1 COP watchdog timer enabled (force reset on timeout).</li> </ul>                                                                                                    |

| 6<br>COPT  | <ul> <li>COP Watchdog Timeout — This write-once bit defaults to 1 after reset.</li> <li>0 Short timeout period selected.</li> <li>1 Long timeout period selected.</li> </ul>                                                                                                                        |

| 5<br>STOPE | <ul> <li>Stop Mode Enable — This write-once bit defaults to 0 after reset, which disables stop mode. If stop mode is disabled and a user program attempts to execute a STOP instruction, an illegal opcode reset is forced.</li> <li>0 Stop mode disabled.</li> <li>1 Stop mode enabled.</li> </ul> |

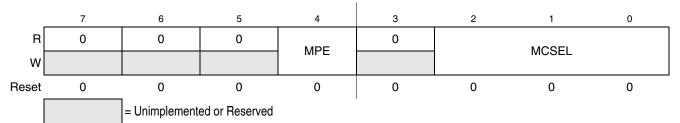

### 5.9.5 System MCLK Control Register (SMCLK)

This register is used to control the MCLK clock output.

#### Figure 5-6. System MCLK Control Register (SMCLK)

#### Table 5-7. SMCLK Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MPE     | <ul> <li>MCLK Pin Enable — This bit is used to enable the MCLK function.</li> <li>0 MCLK output disabled.</li> <li>1 MCLK output enabled on PTC2 pin.</li> </ul>                                                                                                                     |

| 2:0<br>MCSEL | <b>MCLK Divide Select</b> — These bits are used to select the divide ratio for the MCLK output according to the formula below when the MCSEL bits are not equal to all zeroes. In the case that the MCSEL bits are all zero and MPE is set, the pin is driven low. See Equation 5-1. |

#### MCLK frequency = Bus Clock frequency ÷ (2 \* MCSEL)

Eqn. 5-1

MC9S08AC60 Series Data Sheet, Rev. 3

**Chapter 6 Parallel Input/Output**

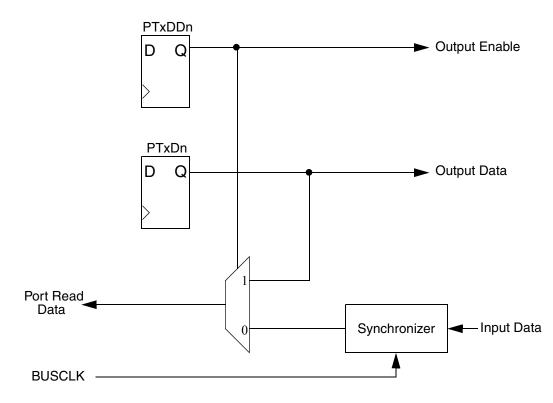

Figure 6-1. Parallel I/O Block Diagram

The data direction control bits determine whether the pin output driver is enabled, and they control what is read for port data register reads. Each port pin has a data direction register bit. When PTxDDn = 0, the corresponding pin is an input and reads of PTxD return the pin value. When PTxDDn = 1, the corresponding pin is an output and reads of PTxD return the last value written to the port data register. When a peripheral module or system function is in control of a port pin, the data direction register bit still controls what is returned for reads of the port data register, even though the peripheral system has overriding control of the actual pin direction.

When a shared analog function is enabled for a pin, all digital pin functions are disabled. A read of the port data register returns a value of 0 for any bits which have shared analog functions enabled. In general, whenever a pin is shared with both an alternate digital function and an analog function, the analog function has priority such that if both the digital and analog functions are enabled, the analog function controls the pin.

It is a good programming practice to write to the port data register before changing the direction of a port pin to become an output. This ensures that the pin will not be driven momentarily with an old data value that happened to be in the port data register.

## 6.4 Pin Control

The pin control registers are located in the high page register block of the memory. These registers are used to control pullups, slew rate, and drive strength for the I/O pins. The pin control registers operate independently of the parallel I/O registers.

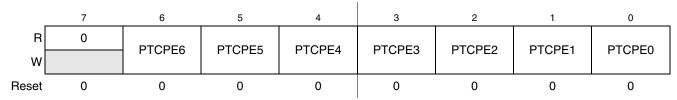

## 6.6.6 Port C Pin Control Registers (PTCPE, PTCSE, PTCDS)

In addition to the I/O control, port C pins are controlled by the registers listed below.

Figure 6-14. Internal Pullup Enable for Port C (PTCPE)

| Table 6-13. PTCPE Register Field Descriptions |

|-----------------------------------------------|

|-----------------------------------------------|

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTCPE[6:0] | <ul> <li>Internal Pullup Enable for Port C Bits — Each of these control bits determines if the internal pullup device is enabled for the associated PTC pin. For port C pins that are configured as outputs, these bits have no effect and the internal pullup devices are disabled.</li> <li>0 Internal pullup device disabled for port C bit n.</li> <li>1 Internal pullup device enabled for port C bit n.</li> </ul> |

|       | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| R     | 0 | PTCSE6 | PTCSE5 | PTCSE4 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| w     |   | FICSED | FICSES | F10324 | FTCSE3 | FTUSEZ | FICSET | FICSED |

| Reset | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-15. Output Slew Rate Control Enable for Port C (PTCSE)

#### Table 6-14. PTCSE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTCSE[6:0] | <ul> <li>Output Slew Rate Control Enable for Port C Bits — Each of these control bits determine whether output slew rate control is enabled for the associated PTC pin. For port C pins that are configured as inputs, these bits have no effect.</li> <li>O Output slew rate control disabled for port C bit n.</li> <li>1 Output slew rate control enabled for port C bit n.</li> </ul> |

Chapter 6 Parallel Input/Output

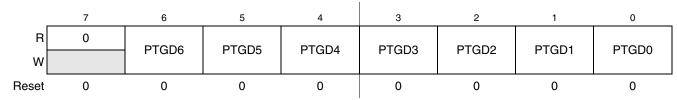

# 6.6.13 Port G I/O Registers (PTGD and PTGDD)

Port G parallel I/O function is controlled by the registers listed below.

#### Figure 6-32. Port G Data Register (PTGD)

#### Table 6-31. PTGD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTGD[6:0] | Port G Data Register Bits — For port G pins that are inputs, reads return the logic level on the pin. For port G pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port G pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTGD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

|       | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| R     | 0 | PTGDD6 | PTGDD5 | PTGDD4 | PTGDD3 | PTGDD2 | PTGDD1 | PTGDD0 |

| W     |   | FIGDDo | FIGDD5 | FIGDD4 | FIGDD3 | FIGDD2 | FIGDDI | FIGDDU |

| Reset | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-33. Data Direction for Port G (PTGDD)

#### Table 6-32. PTGDD Register Field Descriptions

| Field      | Description                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------|

| 6:0        | Data Direction for Port G Bits — These read/write bits control the direction of port G pins and what is read for |

| PTGDD[6:0] | PTGD reads.                                                                                                      |

|            | 0 Input (output driver disabled) and reads return the pin value.                                                 |

|            | 1 Output driver enabled for port G bit n and PTGD reads return the contents of PTGDn.                            |

Chapter 6 Parallel Input/Output

|       | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|---|--------|--------|--------|--------|--------|--------|--------|

| R     | 0 | PTGDS6 | PTGDS5 | PTGDS4 | PTGDS3 | PTGDS2 | PTGDS1 | PTGDS0 |

| w     |   | FIGD30 | FTGD35 | FTGD34 | FIGD33 | FIGD32 | FIGDST | FTGD30 |

| Reset | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

ī.

#### Figure 6-36. Output Drive Strength Selection for Port G (PTGDS)

#### Table 6-35. PTGDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>PTGDS[6:0] | <ul> <li>Output Drive Strength Selection for Port G Bits — Each of these control bits selects between low and high output drive for the associated PTG pin.</li> <li>0 Low output drive enabled for port G bit n.</li> <li>1 High output drive enabled for port G bit n.</li> </ul> |

of an operand for a test and then use relative addressing mode to specify the branch destination address when the tested condition is true. For BRCLR, BRSET, CBEQ, and DBNZ, the addressing mode listed in the instruction set tables is the addressing mode needed to access the operand to be tested, and relative addressing mode is implied for the branch destination.

## 7.3.1 Inherent Addressing Mode (INH)

In this addressing mode, operands needed to complete the instruction (if any) are located within CPU registers so the CPU does not need to access memory to get any operands.

## 7.3.2 Relative Addressing Mode (REL)

Relative addressing mode is used to specify the destination location for branch instructions. A signed 8-bit offset value is located in the memory location immediately following the opcode. During execution, if the branch condition is true, the signed offset is sign-extended to a 16-bit value and is added to the current contents of the program counter, which causes program execution to continue at the branch destination address.

### 7.3.3 Immediate Addressing Mode (IMM)

In immediate addressing mode, the operand needed to complete the instruction is included in the object code immediately following the instruction opcode in memory. In the case of a 16-bit immediate operand, the high-order byte is located in the next memory location after the opcode, and the low-order byte is located in the next memory location after that.

## 7.3.4 Direct Addressing Mode (DIR)

In direct addressing mode, the instruction includes the low-order eight bits of an address in the direct page (0x0000-0x00FF). During execution a 16-bit address is formed by concatenating an implied 0x00 for the high-order half of the address and the direct address from the instruction to get the 16-bit address where the desired operand is located. This is faster and more memory efficient than specifying a complete 16-bit address for the operand.

## 7.3.5 Extended Addressing Mode (EXT)

In extended addressing mode, the full 16-bit address of the operand is located in the next two bytes of program memory after the opcode (high byte first).

## 7.3.6 Indexed Addressing Mode

Indexed addressing mode has seven variations including five that use the 16-bit H:X index register pair and two that use the stack pointer as the base reference.

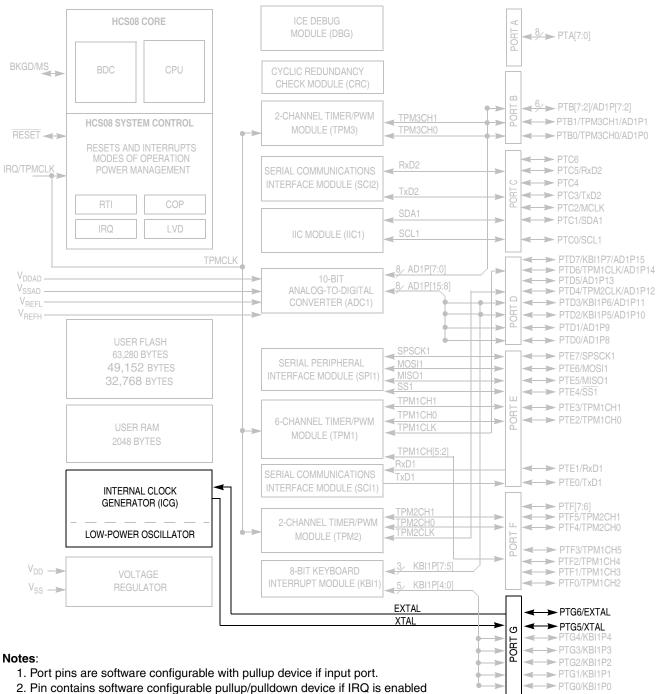

Chapter 10 Internal Clock Generator (S08ICGV4)

- (IRQPE = 1). Pulldown is enabled if rising edge detect is selected (IRQEDG = 1) 3. Pin contains integrated pullup device.

- 3. Pin contains integrated pullup device.

- 4. PTD3, PTD2, PTD7, and PTG4 contain both pullup and pulldown devices. Pulldown enabled when KBI is enabled (KBIPEn = 1) and rising edge is selected (KBEDGn = 1).

- 5. TPMCLK, TPM1CLK, and TPM2CLK options are configured via software; out of reset, TPM1CLK, TPM2CLK, and TPMCLK are available to TPM1, TPM2, and TPM3 respectively.

#### Figure 10-2. Block Diagram Highlighting ICG Module

MC9S08AC60 Series Data Sheet, Rev. 3

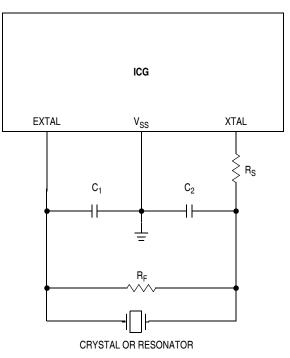

Figure 10-5. External Frequency Reference Connection

## 10.3 Register Definition

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all ICG registers. This section refers to registers and control bits only by their names.

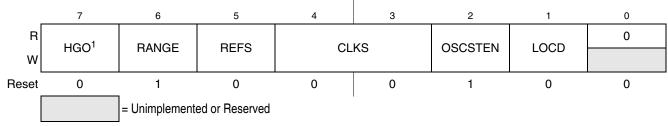

### 10.3.1 ICG Control Register 1 (ICGC1)

#### Figure 10-6. ICG Control Register 1 (ICGC1)

<sup>1</sup> This bit can be written only once after reset. Additional writes are ignored.

Internal Clock Generator (S08ICGV4)

### 10.4.10 Clock Mode Requirements

A clock mode is requested by writing to CLKS1:CLKS0 and the actual clock mode is indicated by CLKST1:CLKST0. Provided minimum conditions are met, the status shown in CLKST1:CLKST0 should be the same as the requested mode in CLKS1:CLKS0. Table 10-9 shows the relationship between CLKS, CLKST, and ICGOUT. It also shows the conditions for CLKS = CLKST or the reason CLKS  $\neq$  CLKST.

#### NOTE

If a crystal will be used before the next reset, then be sure to set REFS = 1 and CLKS = 1x on the first write to the ICGC1 register. Failure to do so will result in "locking" REFS = 0 which will prevent the oscillator amplifier from being enabled until the next reset occurs.

| Actual<br>Mode<br>(CLKST) | Desired<br>Mode<br>(CLKS) | Range | Reference<br>Frequency<br>(f <sub>REFERENCE</sub> ) | Comparison<br>Cycle Time  | ICGOUT                   | Conditions <sup>1</sup> for<br>CLKS = CLKST | Reason<br>CLKS1 ≠<br>CLKST |

|---------------------------|---------------------------|-------|-----------------------------------------------------|---------------------------|--------------------------|---------------------------------------------|----------------------------|

| Off                       | Off<br>(XX)               | х     | 0                                                   | _                         | 0                        | _                                           | _                          |

| (XX)                      | FBE<br>(10)               | х     | 0                                                   |                           | 0                        | _                                           | ERCS = 0                   |

|                           | SCM<br>(00)               | х     | ficgirclk/7 <sup>2</sup>                            | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | Not switching<br>from FBE to<br>SCM         | _                          |

| SCM<br>(00)               | FEI<br>(01)               | 0     | ficgirclk/7 <sup>(1)</sup>                          | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | _                                           | DCOS = 0                   |

| (00)                      | FBE<br>(10)               | х     | f <sub>ICGIRCLK</sub> /7 <sup>(1)</sup>             | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | —                                           | ERCS = 0                   |

|                           | FEE<br>(11)               | х     | ficgirclk/7 <sup>(1)</sup>                          | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | _                                           | DCOS = 0 or<br>ERCS = 0    |

| FEI                       | FEI<br>(01)               | 0     | f <sub>ICGIRCLK</sub> /7                            | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | DCOS = 1                                    | _                          |

| (01)                      | FEE<br>(11)               | х     | f <sub>ICGIRCLK</sub> /7                            | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | —                                           | ERCS = 0                   |

| FBE                       | FBE<br>(10)               | х     | 0                                                   | _                         | ICGERCLK/R               | ERCS = 1                                    | _                          |

| (10)                      | FEE<br>(11)               | х     | 0                                                   | _                         | ICGERCLK/R               | _                                           | LOCS = 1 &<br>ERCS = 1     |

| FEE                       | FEE                       | 0     | f <sub>ICGERCLK</sub>                               | 2/f <sub>ICGERCLK</sub>   | ICGDCLK/R <sup>3</sup>   | ERCS = 1 and<br>DCOS = 1                    | _                          |

| (11)                      | (11)                      | 1     | ficgerclk                                           | 128/f <sub>ICGERCLK</sub> | ICGDCLK/R <sup>(2)</sup> | ERCS = 1 and<br>DCOS = 1                    | _                          |

#### Table 10-9. ICG State Table

<sup>1</sup> CLKST will not update immediately after a write to CLKS. Several bus cycles are required before CLKST updates to the new value.

<sup>2</sup> The reference frequency has no effect on ICGOUT in SCM, but the reference frequency is still used in making the comparisons that determine the DCOS bit

<sup>3</sup> After initial LOCK; will be ICGDCLK/2R during initial locking process and while FLL is re-locking after the MFD bits are changed.

# Chapter 11 Inter-Integrated Circuit (S08IICV2)

## 11.1 Introduction

The inter-integrated circuit (IIC) provides a method of communication between a number of devices. The interface is designed to operate up to 100 kbps with maximum bus loading and timing. The device is capable of operating at higher baud rates, up to a maximum of clock/20, with reduced bus loading. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400 pF.

For additional detail, please refer to volume 1 of the *HCS08 Reference Manual*, (Freescale Semiconductor document order number HCS08RMv1/D).

The MC9S08AC60 series of microcontrollers has an inter-integrated circuit (IIC) module for communication with other integrated circuits.

# 14.3 Modes of Operation

### 14.3.1 SPI in Stop Modes

The SPI is disabled in all stop modes, regardless of the settings before executing the STOP instruction. During either stop1 or stop2 mode, the SPI module will be fully powered down. Upon wake-up from stop1 or stop2 mode, the SPI module will be in the reset state. During stop3 mode, clocks to the SPI module are halted. No registers are affected. If stop3 is exited with a reset, the SPI will be put into its reset state. If stop3 is exited with an interrupt, the SPI continues from the state it was in when stop3 was entered.

## 14.4 Register Definition

The SPI has five 8-bit registers to select SPI options, control baud rate, report SPI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SPI registers. This section refers to registers and control bits only by their names, and a Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

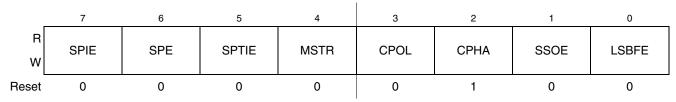

### 14.4.1 SPI Control Register 1 (SPIC1)

This read/write register includes the SPI enable control, interrupt enables, and configuration options.

Figure 14-5. SPI Control Register 1 (SPIC1)

| Field      | Description                                                                                                                                                                                                                                                                                                  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable (for SPRF and MODF) — This is the interrupt enable for SPI receive buffer full (SPRF) and mode fault (MODF) events.</li> <li>Interrupts from SPRF and MODF inhibited (use polling)</li> <li>When SPRF or MODF is 1, request a hardware interrupt</li> </ul>                    |

| 6<br>SPE   | <ul> <li>SPI System Enable — Disabling the SPI halts any transfer that is in progress, clears data buffers, and initializes internal state machines. SPRF is cleared and SPTEF is set to indicate the SPI transmit data buffer is empty.</li> <li>SPI system inactive</li> <li>SPI system enabled</li> </ul> |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This is the interrupt enable bit for SPI transmit buffer empty (SPTEF).</li> <li>Interrupts from SPTEF inhibited (use polling)</li> <li>When SPTEF is 1, hardware interrupt requested</li> </ul>                                                                    |

#### Timer/PWM Module (S08TPMV3)

All TPM interrupts are listed in Table 15-10 which shows the interrupt name, the name of any local enable that can block the interrupt request from leaving the TPM and getting recognized by the separate interrupt processing logic.

| Interrupt | Local<br>Enable | Source           | Description                                                                                                            |

|-----------|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------|

| TOF       | TOIE            | Counter overflow | Set each time the timer counter reaches its terminal count (at transition to next count value which is usually 0x0000) |

| CHnF      | CHnIE           | Channel event    | An input capture or output compare event took place on channel n                                                       |

| Table 15-10. | Interrupt | Summary |

|--------------|-----------|---------|

|--------------|-----------|---------|

The TPM module will provide a high-true interrupt signal. Vectors and priorities are determined at chip integration time in the interrupt module so refer to the user's guide for the interrupt module or to the chip's complete documentation for details.

### 15.8.2 Description of Interrupt Operation

For each interrupt source in the TPM, a flag bit is set upon recognition of the interrupt condition such as timer overflow, channel-input capture, or output-compare events. This flag may be read (polled) by software to determine that the action has occurred, or an associated enable bit (TOIE or CHnIE) can be set to enable hardware interrupt generation. While the interrupt enable bit is set, a static interrupt will generate whenever the associated interrupt flag equals one. The user's software must perform a sequence of steps to clear the interrupt flag before returning from the interrupt-service routine.

TPM interrupt flags are cleared by a two-step process including a read of the flag bit while it is set (1) followed by a write of zero (0) to the bit. If a new event is detected between these two steps, the sequence is reset and the interrupt flag remains set after the second step to avoid the possibility of missing the new event.

#### 15.8.2.1 Timer Overflow Interrupt (TOF) Description

The meaning and details of operation for TOF interrupts varies slightly depending upon the mode of operation of the TPM system (general purpose timing functions versus center-aligned PWM operation). The flag is cleared by the two step sequence described above.

#### 15.8.2.1.1 Normal Case

Normally TOF is set when the timer counter changes from 0xFFFF to 0x0000. When the TPM is not configured for center-aligned PWM (CPWMS=0), TOF gets set when the timer counter changes from the terminal count (the value in the modulo register) to 0x0000. This case corresponds to the normal meaning of counter overflow.

— TPMxCnVH:L = (TPMxMODH:L - 1) [SE110-TPM case 2]

In this case, the TPM v3 produces almost 100% duty cycle. Instead, the TPM v2 produces 0% duty cycle.

- TPMxCnVH:L is changed from 0x0000 to a non-zero value [SE110-TPM case 3 and 5]

In this case, the TPM v3 waits for the start of a new PWM period to begin using the new duty cycle setting. Instead, the TPM v2 changes the channel output at the middle of the current PWM period (when the count reaches 0x0000).

- TPMxCnVH:L is changed from a non-zero value to 0x0000 [SE110-TPM case 4]

In this case, the TPM v3 finishes the current PWM period using the old duty cycle setting. Instead, the TPM v2 finishes the current PWM period using the new duty cycle setting.

- 6. Write to TPMxMODH:L registers in BDM mode (Section 15.5.3, "TPM Counter Modulo Registers (TPMxMODH:TPMxMODL))

In the TPM v3 a write to TPMxSC register in BDM mode clears the write coherency mechanism of TPMxMODH:L registers. Instead, in the TPM v2 this coherency mechanism is not cleared when there is a write to TPMxSC register.

#### Development Support

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

## 16.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

Development Support

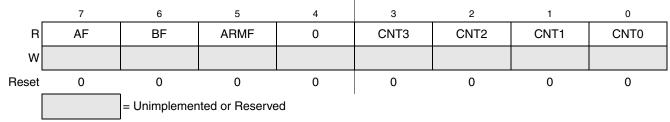

### 16.4.3.9 Debug Status Register (DBGS)

This is a read-only status register.

#### Figure 16-9. Debug Status Register (DBGS)

#### Table 16-6. DBGS Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>AF         | <ul> <li>Trigger Match A Flag — AF is cleared at the start of a debug run and indicates whether a trigger match A condition was met since arming.</li> <li>0 Comparator A has not matched</li> <li>1 Comparator A match</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6<br>BF         | <ul> <li>Trigger Match B Flag — BF is cleared at the start of a debug run and indicates whether a trigger match B condition was met since arming.</li> <li>0 Comparator B has not matched</li> <li>1 Comparator B match</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5<br>ARMF       | Arm Flag — While DBGEN = 1, this status bit is a read-only image of ARM in DBGC. This bit is set by writing 1 to the ARM control bit in DBGC (while DBGEN = 1) and is automatically cleared at the end of a debug run. A debug run is completed when the FIFO is full (begin trace) or when a trigger event is detected (end trace). A debug run can also be ended manually by writing 0 to ARM or DBGEN in DBGC.<br>0 Debugger not armed<br>1 Debugger armed                                                                                                                                                                                                                                                             |

| 3:0<br>CNT[3:0] | FIFO Valid Count — These bits are cleared at the start of a debug run and indicate the number of words of valid data in the FIFO at the end of a debug run. The value in CNT does not decrement as data is read out of the FIFO. The external debug host is responsible for keeping track of the count as information is read out of the FIFO. 0000 Number of valid words in FIFO = No valid data 0001 Number of valid words in FIFO = 1 0010 Number of valid words in FIFO = 2 0011 Number of valid words in FIFO = 3 0100 Number of valid words in FIFO = 4 0101 Number of valid words in FIFO = 5 0110 Number of valid words in FIFO = 6 0111 Number of valid words in FIFO = 7 1000 Number of valid words in FIFO = 8 |

Appendix A Electrical Characteristics and Timing Specifications

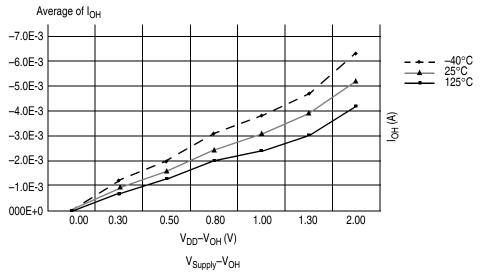

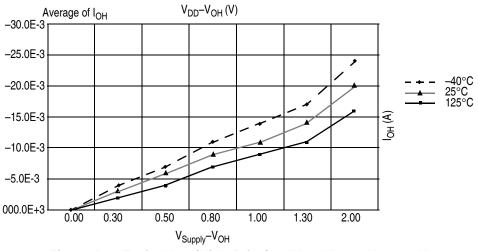

Figure A-4. Typical I<sub>OH</sub> (High Drive) vs V<sub>DD</sub>–V<sub>OH</sub> at V<sub>DD</sub> = 5 V

Appendix A Electrical Characteristics and Timing Specifications

# A.7 Supply Current Characteristics

Table A-7. Supply Current Characteristics

| Num | С                                               | Parameter                                          | Symbol                | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max <sup>2</sup>        | Unit | Temp<br>(°C)                |

|-----|-------------------------------------------------|----------------------------------------------------|-----------------------|------------------------|------------------|-------------------------|------|-----------------------------|

|     | 1 C Run supply current <sup>3</sup> measured at |                                                    |                       | 5                      | 1.0              | 1.3 <sup>4</sup>        |      |                             |

| 1   | С                                               | (CPU clock = 2 MHz, $f_{Bus} = 1$ MHz)             | RI <sub>DD</sub>      | 3                      | 0.9              | 1.1                     | mA   | –40 to 125°C                |

|     |                                                 | Run supply current <sup>5</sup> measured at        |                       | 5                      | 6.5              | 8.0 <sup>6</sup>        |      |                             |

| 2   | С                                               | (CPU clock = 16 MHz, f <sub>Bus</sub> = 8 MHz)     | RI <sub>DD</sub>      | 3                      | 5.5              | 6.5                     | mA   | –40 to 125°C                |

|     |                                                 |                                                    |                       | 5                      | 0.900            | 18.0<br>60 <sup>4</sup> | μA   | –40 to 85°C<br>–40 to 125°C |

| 3   | Р                                               | Stop2 mode supply current                          | S2I <sub>DD</sub>     | 5                      | 0.900            |                         |      |                             |

|     |                                                 |                                                    | טט                    | 3                      | 0.720            | 17.0<br>50              | μA   | −40 to 85°C −40 to 125°C    |

|     |                                                 | Stop3 mode supply current                          | S3I <sub>DD</sub>     |                        |                  | 20.0                    | μΑ   | –40 to 85°C                 |

| 4   | Р                                               |                                                    |                       | 5                      | 0.975            | 90 <sup>4</sup>         |      | –40 to 125°C                |

|     |                                                 |                                                    |                       |                        |                  | 19.0                    | μA   | –40 to 85°C                 |

|     |                                                 |                                                    |                       | 3                      | 0.825            | 85                      | port | –40 to 125°C                |

|     |                                                 |                                                    |                       | 5                      | 300              | 500                     | nA   | -40 to 85°C                 |

| 5   | С                                               | RTI adder to stop2 or stop3 <sup>7</sup>           | S23I <sub>ddrti</sub> |                        |                  | 500                     |      | –40 to 125°C                |

|     |                                                 |                                                    |                       | 3                      | 300              | 500                     | nA   | -40 to 85°C                 |

|     |                                                 |                                                    |                       |                        |                  | 500                     |      | -40 to 125°C                |

|     |                                                 | C LVD adder to stop3 (LVDE = LVDSE = 1)            | 601                   | 5                      | 110              | 180                     | μA   | –40 to 85°C<br>–40 to 125°C |

| 6   | C                                               |                                                    | S3I <sub>DDLVD</sub>  | 3                      | 90               |                         | μA   | –40 to 85°C                 |

|     |                                                 |                                                    |                       | 5                      | 30               | 160                     | μΛ   | –40 to 125°C                |

| 7   | с                                               | Adder to stop3 for oscillator enabled <sup>8</sup> | S3I <sub>DDOSC</sub>  | 5,3                    | 5                | 8                       | μA   | –40 to 85°C                 |

|     | Ŭ                                               | (OSCSTEN =1)                                       | DDOSC                 | 0,0                    | Ŭ                | č                       | μA   | –40 to 125°C                |

<sup>1</sup> Typical values are based on characterization data at 25°C unless otherwise stated. See Figure A-5 through Figure A-7 for typical curves across voltage/temperature.

<sup>2</sup> Values given here are preliminary estimates prior to completing characterization.

<sup>3</sup> All modules except ADC active, ICG configured for FBE, and does not include any dc loads on port pins

<sup>4</sup> Every unit tested to this parameter. All other values in the Max column are guaranteed by characterization.

<sup>5</sup> All modules except ADC active, ICG configured for FBE, and does not include any dc loads on port pins

<sup>6</sup> Every unit tested to this parameter. All other values in the Max column are guaranteed by characterization.

<sup>7</sup> Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode. Wait mode typical is 560  $\mu$ A at 3 V with f<sub>Bus</sub> = 1 MHz.

<sup>8</sup> Values given under the following conditions: low range operation (RANGE = 0) with a 32.768kHz crystal, low power mode (HGO = 0), clock monitor disabled (LOCD = 1).