Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 29x12b, 2x16b; D/A 2x10b                                                   |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128gc006-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

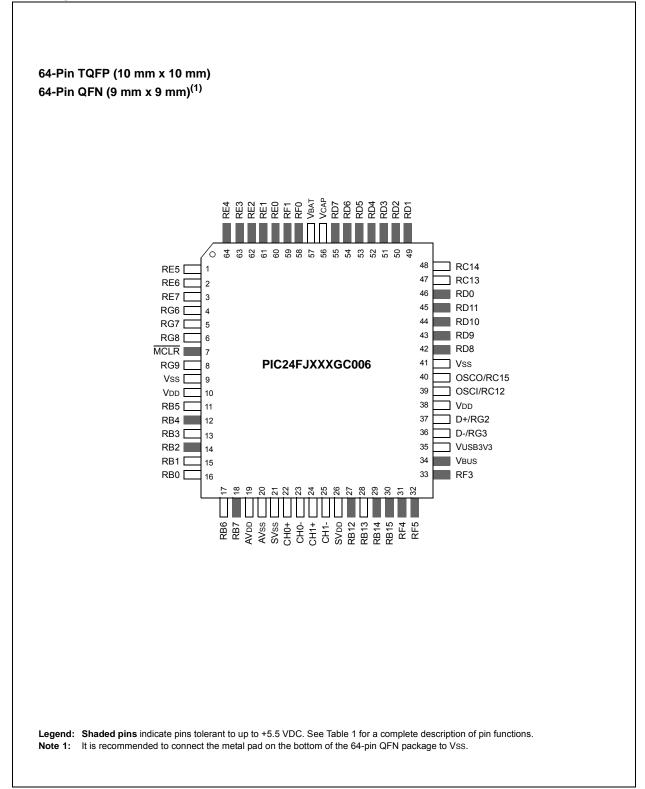

### **Pin Diagrams**

### TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJ128GC010 FAMILY: 64-PIN DEVICES

| Features                                                                 | PIC24FJ64GC006                                                                                                                                                           | PIC24FJ128GC006            |  |  |  |  |  |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|--|

| Operating Frequency                                                      | DC – 3                                                                                                                                                                   | 2 MHz                      |  |  |  |  |  |

| Program Memory (bytes)                                                   | 64K                                                                                                                                                                      | 128K                       |  |  |  |  |  |

| Program Memory (instructions)                                            | 22,016                                                                                                                                                                   | 44,032                     |  |  |  |  |  |

| Data Memory (bytes)                                                      | 8                                                                                                                                                                        | K                          |  |  |  |  |  |

| Interrupt Sources (soft vectors/<br>NMI traps)                           | 65 (61/4)                                                                                                                                                                |                            |  |  |  |  |  |

| I/O Ports                                                                | Ports B, C, D, E, F, G                                                                                                                                                   |                            |  |  |  |  |  |

| Total I/O Pins                                                           | 5                                                                                                                                                                        | 3                          |  |  |  |  |  |

| Remappable Pins                                                          | 30 (29 I/Os,                                                                                                                                                             | 1 input only)              |  |  |  |  |  |

| Timers:                                                                  |                                                                                                                                                                          |                            |  |  |  |  |  |

| Total Number (16-bit)                                                    | 5(                                                                                                                                                                       | 1)                         |  |  |  |  |  |

| 32-Bit (from paired 16-bit timers)                                       | 2                                                                                                                                                                        | 2                          |  |  |  |  |  |

| Input Capture w/Timer Channels                                           | 9(                                                                                                                                                                       | 1)                         |  |  |  |  |  |

| Output Compare/PWM Channels                                              | 9(                                                                                                                                                                       | 1)                         |  |  |  |  |  |

| Input Change Notification Interrupt                                      | 5                                                                                                                                                                        | 2                          |  |  |  |  |  |

| Serial Communications:                                                   |                                                                                                                                                                          |                            |  |  |  |  |  |

| UART                                                                     | 4 <sup>(1)</sup>                                                                                                                                                         |                            |  |  |  |  |  |

| SPI (3-wire/4-wire)                                                      | 2 <sup>(1)</sup>                                                                                                                                                         |                            |  |  |  |  |  |

| I <sup>2</sup> C                                                         | 2                                                                                                                                                                        | 2                          |  |  |  |  |  |

| Digital Signal Modulator                                                 | Ye                                                                                                                                                                       | 28                         |  |  |  |  |  |

| Parallel Communications (EPMP/PSP)                                       | Ye                                                                                                                                                                       | 28                         |  |  |  |  |  |

| JTAG Boundary Scan                                                       | Ye                                                                                                                                                                       | 28                         |  |  |  |  |  |

| 12-Bit Pipeline Analog-to-Digital<br>Converter (A/D) (input channels)    | 2                                                                                                                                                                        | 9                          |  |  |  |  |  |

| Sigma-Delta Analog-to-Digital Converter<br>(A/D) (differential channels) | 2                                                                                                                                                                        | 2                          |  |  |  |  |  |

| Digital-to-Analog Converter (DAC)                                        | 2                                                                                                                                                                        | 2                          |  |  |  |  |  |

| Operational Amplifiers                                                   | 2                                                                                                                                                                        | 2                          |  |  |  |  |  |

| Analog Comparators                                                       | 3                                                                                                                                                                        | }                          |  |  |  |  |  |

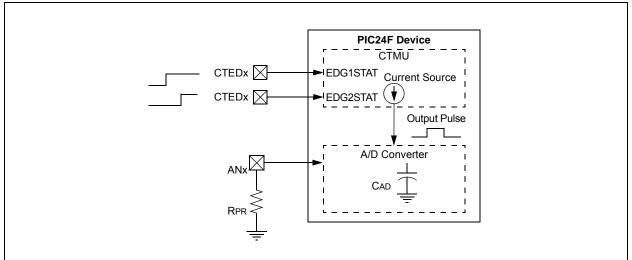

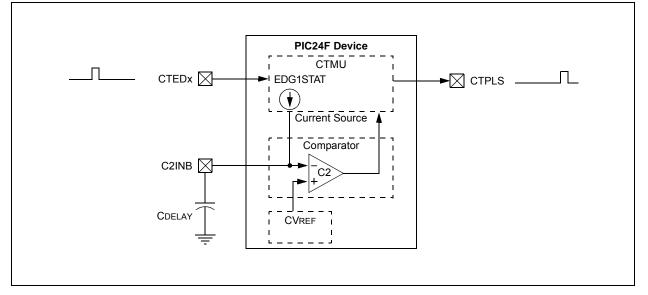

| CTMU Interface                                                           | Ye                                                                                                                                                                       | es                         |  |  |  |  |  |

| LCD Controller (available pixels)                                        | 196 (28 SE                                                                                                                                                               | G x 7 COM)                 |  |  |  |  |  |

| Resets (and delays)                                                      | Core POR, VDD POR, VBAT POR, BOR, RESET Instruction,<br>MCLR, WDT, Illegal Opcode, REPEAT Instruction,<br>Hardware Traps, Configuration Word Mismatch<br>(OST, PLL Lock) |                            |  |  |  |  |  |

| Instruction Set                                                          | 76 Base Instructions, Multiple                                                                                                                                           | Addressing Mode Variations |  |  |  |  |  |

| Packages                                                                 | 64-Pin TQFP and QFN                                                                                                                                                      |                            |  |  |  |  |  |

**Note 1:** Peripherals are accessible through remappable pins.

| Features                                                                 | PIC24FJ64GC010                                                                                             | PIC24FJ128GC010                               |  |  |  |  |  |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|--|--|--|--|

| Operating Frequency                                                      | DC – 32 I                                                                                                  | MHz                                           |  |  |  |  |  |

| Program Memory (bytes)                                                   | 64K                                                                                                        | 128K                                          |  |  |  |  |  |

| Program Memory (instructions)                                            | 22,016                                                                                                     | 44,032                                        |  |  |  |  |  |

| Data Memory (bytes)                                                      | 8K                                                                                                         |                                               |  |  |  |  |  |

| Interrupt Sources (soft vectors/<br>NMI traps)                           | 66 (62/4)                                                                                                  |                                               |  |  |  |  |  |

| I/O Ports                                                                | Ports A, B, C, I                                                                                           | D, E, F, G                                    |  |  |  |  |  |

| Total I/O Pins                                                           | 85                                                                                                         |                                               |  |  |  |  |  |

| Remappable Pins                                                          | 44 (32 l/Os, 12                                                                                            | input only)                                   |  |  |  |  |  |

| Timers:<br>Total Number (16-bit)<br>32-Bit (from paired 16-bit timers)   | 5 <sup>(1)</sup>                                                                                           |                                               |  |  |  |  |  |

| Input Capture w/Timer Channels                                           | 9 <sup>(1)</sup>                                                                                           |                                               |  |  |  |  |  |

| Output Compare/PWM Channels                                              | 9 <sup>(1)</sup>                                                                                           |                                               |  |  |  |  |  |

| Input Change Notification Interrupt                                      | 82                                                                                                         |                                               |  |  |  |  |  |

| Serial Communications:                                                   |                                                                                                            |                                               |  |  |  |  |  |

| UART                                                                     | 4(1)                                                                                                       |                                               |  |  |  |  |  |

| SPI (3-wire/4-wire)                                                      | 2 <sup>(1)</sup>                                                                                           |                                               |  |  |  |  |  |

| I <sup>2</sup> C                                                         | 2                                                                                                          |                                               |  |  |  |  |  |

| Digital Signal Modulator                                                 | Yes                                                                                                        |                                               |  |  |  |  |  |

| Parallel Communications (EPMP/PSP)                                       | Yes                                                                                                        |                                               |  |  |  |  |  |

| JTAG Boundary Scan                                                       | Yes                                                                                                        |                                               |  |  |  |  |  |

| 12-Bit Pipeline Analog-to-Digital<br>Converter (A/D) (input channels)    | 50                                                                                                         |                                               |  |  |  |  |  |

| Sigma-Delta Analog-to-Digital<br>Converter (A/D) (differential channels) | 2                                                                                                          |                                               |  |  |  |  |  |

| Digital-to-Analog Converter (DAC)                                        | 2                                                                                                          |                                               |  |  |  |  |  |

| Operational Amplifiers                                                   | 2                                                                                                          |                                               |  |  |  |  |  |

| Analog Comparators                                                       | 3                                                                                                          |                                               |  |  |  |  |  |

| CTMU Interface                                                           | Yes                                                                                                        |                                               |  |  |  |  |  |

| LCD Controller (available pixels)                                        | 472 (59 SEG >                                                                                              | ( 8 COM)                                      |  |  |  |  |  |

| Resets (and delays)                                                      | Core <u>POR</u> , VDD POR, VBAT POF<br>MCLR, WDT, Illegal Opcode<br>Hardware Traps, Configura<br>(OST, PLL | e, REPEAT Instruction,<br>ation Word Mismatch |  |  |  |  |  |

| Instruction Set                                                          | 76 Base Instructions, Multiple A                                                                           | ddressing Mode Variations                     |  |  |  |  |  |

| Packages                                                                 | 100-Pin TQFP and 121-Pin BGA                                                                               |                                               |  |  |  |  |  |

### TABLE 1-2: DEVICE FEATURES FOR THE PIC24FJ128GC010 FAMILY: 100/121-PIN DEVICES

**Note 1:** Peripherals are accessible through remappable pins.

| Dia             | Pin Num            | ber/Grid L        | ocator              |     | Innert          |                                                             |

|-----------------|--------------------|-------------------|---------------------|-----|-----------------|-------------------------------------------------------------|

| Pin<br>Function | 64-Pin<br>TQFP/QFN | 100-Pin<br>TQFP   | 121-Pin<br>BGA      | I/O | Input<br>Buffer | Description                                                 |

| SOSCI           | 47                 | 73                | C10                 | I   | ANA             | Secondary Oscillator Input.                                 |

| SOSCO           | 48                 | 74                | B11                 | 0   | ANA             | Secondary Oscillator Output.                                |

| SVDD            | 26                 | 37                | J5                  | Р   | _               | Positive Supply for Sigma-Delta A/D Converter.              |

| SVREF+          | 24                 | 35                | K5                  | I   | ANA             | Sigma-Delta A/D Converter Voltage Reference (high).         |

| SVREF-          | 25                 | 36                | L5                  | I   | ANA             | Sigma-Delta A/D Converter Voltage Reference (low).          |

| SVss            | 21                 | 32                | K4                  | Р   | _               | Ground Reference for Sigma-Delta A/D Converter.             |

| T1CK            | 27                 | 41                | J7                  | I   | ST              | External Timer1 Clock Input.                                |

| T2CK            | 30                 | 44                | L8                  | I   | ST              | External Timer2 Clock Input.                                |

| T3CK            | 31                 | 49                | L10                 | I   | ST              | External Timer3 Clock Input.                                |

| T4CK            | 14                 | 23                | J2                  | I   | ST              | External Timer4 Clock Input.                                |

| T5CK            | 4                  | 10                | E3                  | I   | ST              | External Timer5 Clock Input.                                |

| TCK             | 27                 | 38                | J6                  | I   | ST              | JTAG Test Clock/Programming Clock Input.                    |

| TDI             | 28                 | 60                | G11                 | I   | ST              | JTAG Test Data/Programming Data Input.                      |

| TDO             | 29                 | 61                | G9                  | 0   | _               | JTAG Test Data Output.                                      |

| TMS             | 45                 | 17                | G3                  | I   | ST              | JTAG Test Mode Select Input.                                |

| USBID           | 33                 | 51                | K10                 | I   | ST              | USB OTG ID (OTG mode only).                                 |

| USBOE           | 12                 | 21                | H2                  | 0   | —               | USB Output Enable Control (for external transceiver).       |

| VBAT            | 57                 | 86                | A7                  | Р   | —               | Backup Battery (B+) Input.                                  |

| VBUS            | 34                 | 54                | H8                  | Р   | —               | USB VBUS Connection (5V nominal).                           |

| VCAP            | 56                 | 85                | B7                  | Р   | _               | External Filter Capacitor Connection.                       |

| VCMPST1         | 58                 | 87                | B6                  | I   | ST              | USB VBUS External Comparator Input 1.                       |

| VCMPST2         | 59                 | 88                | A6                  | I   | ST              | USB VBUS External Comparator Input 2.                       |

| VCMPST3         | 46                 | 72                | D9                  | I   | ST              | USB VBUS External Comparator Input 3.                       |

| VDD             | 10, 38             | 2, 16,<br>46,62   | C2,G5,<br>K8, F8    | Р   | _               | Positive Supply for Peripheral Digital Logic and I/O Pins.  |

| VLCAP1          | 5                  | 11                | F4                  | Р   | ANA             | LCD Drive Charge Pump Capacitor Pins.                       |

| VLCAP2          | 6                  | 12                | F2                  | Р   | ANA             |                                                             |

| VMIO            | 14                 | 23                | J2                  | I/O | ST              | USB Differential Minus Input/Output (external transceiver). |

| VPIO            | 13                 | 22                | J1                  | I/O | ST              | USB Differential Plus Input/Output (external transceiver).  |

| Vss             | 9, 41              | 15, 45,<br>65, 75 | F5, G7,<br>F10, B10 | Р   | —               | Ground Reference for Logic and I/O Pins.                    |

| VUSB3V3         | 35                 | 55                | H9                  | Р   | _               | USB Transceiver Power Input Voltage (3.3V nominal).         |

| TABLE 1-3: | PIC24FJ128GC010 FAMILY PINOUT DESCRIPTION (CONTINUED) |

|------------|-------------------------------------------------------|

|            |                                                       |

Legend: TTL = TTL input buffer ST = Schmitt Trigger input buffer  $I^2C = I^2C/SMBus$  input buffer

ANA = Analog level input/output

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT       | 0630 | CMIDL  | _      | _      | _      | _      | C3EVT  | C2EVT   | C1EVT   | _      | —      | —     | _     | _     | C3OUT | C2OUT | C10UT | 0000          |

| CVRCON       | 0632 | _      | -      |        | -      |        | CVREFP | CVREFM1 | CVREFM0 | CVREN  | CVROE  | CVRSS | CVR4  | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON       | 0634 | CON    | COE    | CPOL   | -      |        | —      | CEVT    | COUT    | EVPOL1 | EVPOL0 | —     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

| CM2CON       | 0636 | CON    | COE    | CPOL   | -      |        | —      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | _     |       | CCH1  | CCH0  | 0000          |

| CM3CON       | 0638 | CON    | COE    | CPOL   | -      |        | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | _     |       | CCH1  | CCH0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-33: CRC REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                           | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8      | Bit 7      | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|----------------------------------|--------|---------|---------|---------|---------|------------|------------|--------|---------|-------|---------|-------|-------|-------|---------------|

| CRCCON1      | 0640 | CRCEN  | _                                | CSIDL  | VWORD4  | VWORD3  | VWORD2  | VWORD1  | VWORD0     | CRCFUL     | CRCMPT | CRCISEL | CRCGO | LENDIAN |       | _     | _     | 0040          |

| CRCCON2      | 0642 | —      | —                                | —      | DWIDTH4 | DWIDTH3 | DWIDTH2 | DWIDTH1 | DWIDTH0    |            |        | _       | PLEN4 | PLEN3   | PLEN2 | PLEN1 | PLEN0 | 0000          |

| CRCXORL      | 0644 |        |                                  |        |         |         |         |         | X<15:1>    |            |        |         |       |         |       |       | —     | 0000          |

| CRCXORH      | 0646 |        |                                  |        |         |         |         |         | X<31:      | 16>        |        |         |       |         |       |       |       | 0000          |

| CRCDATL      | 0648 |        |                                  |        |         |         |         | CRC     | Data Input | Register L | W      |         |       |         |       |       |       | 0000          |

| CRCDATH      | 064A |        | CRC Data Input Register High 000 |        |         |         |         |         |            |            |        | 0000    |       |         |       |       |       |               |

| CRCWDATL     | 064C |        | CRC Result Register Low 000      |        |         |         |         |         |            |            |        | 0000    |       |         |       |       |       |               |

| CRCWDATH     | 064E |        | CRC Result Register High 000     |        |         |         |         |         |            |            |        | 0000    |       |         |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-34: BAND GAP BUFFER INTERFACE REGISTER MAP

|   | File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   | All<br>Resets |

|---|--------------|------|--------|--------|---------|--------|--------|--------|-------|-------|-------|---------|-------|-------|-------|-------|---------|---------|---------------|

| Ī | BUFCON0      | 0670 | BUFEN  |        | BUFSIDL | BUFSLP | _      | _      | _     |       |       | BUFSTBY |       | _     | _     | —     | BUFREF1 | BUFREF0 | 0000          |

|   | BUFCON1      | 0672 | BUFEN  | —      | BUFSIDL | BUFSLP | _      | _      | _     | _     | BUFOE | BUFSTBY | —     |       | _     | _     | BUFREF1 | BUFREF0 | 0000          |

|   | BUFCON2      | 0674 | BUFEN  | —      | BUFSIDL | BUFSLP | _      | _      | _     | _     | BUFOE | BUFSTBY | —     |       | _     | _     | BUFREF1 | BUFREF0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|                  | R/W-1                                                                        | R/W-0                                                                                                 | R/W-0                                                        | U-0              | R/W-1            | R/W-0           | R/W-0   |

|------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------|------------------|-----------------|---------|

| —                | U3TXIP2                                                                      | U3TXIP1                                                                                               | U3TXIP0                                                      | _                | U3RXIP2          | U3RXIP1         | U3RXIP0 |

| bit 15           | ·                                                                            |                                                                                                       |                                                              |                  |                  |                 | bit     |

| U-0              | R/W-1                                                                        | R/W-0                                                                                                 | R/W-0                                                        | U-0              | U-0              | U-0             | U-0     |

| _                | U3ERIP2                                                                      | U3ERIP1                                                                                               | U3ERIP0                                                      | _                | _                | _               | _       |

| bit 7            |                                                                              |                                                                                                       |                                                              |                  |                  |                 | bit     |

| Legend:          |                                                                              |                                                                                                       |                                                              |                  |                  |                 |         |

| R = Readab       | ole bit                                                                      | W = Writable                                                                                          | bit                                                          | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value a     | at POR                                                                       | '1' = Bit is set                                                                                      |                                                              | '0' = Bit is cle |                  | x = Bit is unkr | nown    |

|                  |                                                                              |                                                                                                       |                                                              |                  |                  |                 |         |

| bit 15           | Unimplemen                                                                   | ted: Read as '                                                                                        | ז'                                                           |                  |                  |                 |         |

| bit 14-12        | -                                                                            | : UART3 Trans                                                                                         |                                                              | ot Priority bits |                  |                 |         |

|                  |                                                                              | pt is Priority 7 (                                                                                    | =                                                            | -                |                  |                 |         |

|                  | •                                                                            | prist nonty / (                                                                                       | nightest phone                                               | y interrupt)     |                  |                 |         |

|                  | •                                                                            |                                                                                                       |                                                              |                  |                  |                 |         |

|                  | •                                                                            |                                                                                                       |                                                              |                  |                  |                 |         |

|                  | 001 = Interru<br>000 = Interru                                               | pt is Priority 1<br>pt source is dis                                                                  | abled                                                        |                  |                  |                 |         |

| bit 11           | Unimplemen                                                                   | ted: Read as '                                                                                        | כי                                                           |                  |                  |                 |         |

| bit 10-8         | U3RXIP<2:0>                                                                  | : UART3 Rece                                                                                          | iver Interrupt I                                             | Priority bits    |                  |                 |         |

|                  | 111 = Interru                                                                |                                                                                                       |                                                              | •                |                  |                 |         |

|                  |                                                                              | dt is priority 7 (                                                                                    | highest priority                                             | v interrupt)     |                  |                 |         |

|                  | •                                                                            | pt is priority 7 (                                                                                    | highest priority                                             | y interrupt)     |                  |                 |         |

|                  | •                                                                            | pt is Priority 7 (                                                                                    | highest priority                                             | y interrupt)     |                  |                 |         |

|                  | •                                                                            |                                                                                                       | highest priority                                             | y interrupt)     |                  |                 |         |

|                  | •<br>•<br>• 001 = Interru                                                    | pt is Priority 1                                                                                      |                                                              | y interrupt)     |                  |                 |         |

| h.i# 7           | 000 = Interru                                                                | pt is Priority 1<br>pt source is dis                                                                  | abled                                                        | y interrupt)     |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen                                                  | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '                                         | abled                                                        |                  |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                                   | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: UART3 Error                       | abled<br>)'<br>Interrupt Prior                               | rity bits        |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                                   | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '                                         | abled<br>)'<br>Interrupt Prior                               | rity bits        |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                                   | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: UART3 Error                       | abled<br>)'<br>Interrupt Prior                               | rity bits        |                  |                 |         |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                                   | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: UART3 Error                       | abled<br>)'<br>Interrupt Prior                               | rity bits        |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0>                                   | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: UART3 Error<br>pt is Priority 7 ( | abled<br>)'<br>Interrupt Prior                               | rity bits        |                  |                 |         |

|                  | 000 = Interru<br>Unimplemen<br>U3ERIP<2:0><br>111 = Interru<br>001 = Interru | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: UART3 Error<br>pt is Priority 7 ( | abled<br><sup>)'</sup><br>Interrupt Prio<br>highest priority | rity bits        |                  |                 |         |

### REGISTER 8-39: IPC20: INTERRUPT PRIORITY CONTROL REGISTER 20

### 11.4.6 PERIPHERAL PIN SELECT REGISTERS

The PIC24FJ128GC010 family of devices implements a total of 35 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (19)

- Output Remappable Peripheral Registers (16)

Note: Input and output register values can only be changed if IOLOCK (OSCCON<6>) = 0. See Section 11.4.4.1 "Control Register Lock" for a specific command sequence.

### REGISTER 11-9: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | INT1R5 | INT1R4 | INT1R3 | INT1R2 | INT1R1 | INT1R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | _   | —   | —   |     | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                           |

|-----------|--------------------------------------------------------------------------------------|

| bit 13-8  | INT1R<5:0>: Assign External Interrupt 1 (INT1) to Corresponding RPn or RPIn Pin bits |

| bit 7-0   | Unimplemented: Read as '0'                                                           |

#### REGISTER 11-10: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | INT3R5 | INT3R4 | INT3R3 | INT3R2 | INT3R1 | INT3R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | INT2R5 | INT2R4 | INT2R3 | INT2R2 | INT2R1 | INT2R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                           |

|-----------|--------------------------------------------------------------------------------------|

| bit 13-8  | INT3R<5:0>: Assign External Interrupt 3 (INT3) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                           |

| bit 5-0   | INT2R<5:0>: Assign External Interrupt 2 (INT2) to Corresponding RPn or RPIn Pin bits |

| R/W-0                       | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                        | U-0                                                                                                                                             | U-0                                                                                       | U-0                                                    | R/W-0                                                         | R/W-0                        |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|------------------------------|

| TON                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TSIDL                                                                                                                                                                        | —                                                                                                                                               |                                                                                           | —                                                      | TIECS1(2)                                                     | TIECS0(2)                    |

| bit 15                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                              |                                                                                                                                                 |                                                                                           |                                                        |                                                               | bit 8                        |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>D</b> 444 0                                                                                                                                                               | DAMA                                                                                                                                            | <b>DMU</b> O                                                                              |                                                        | <b>D</b> 11 1                                                 |                              |

| U-0                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                        | R/W-0                                                                                                                                           | R/W-0                                                                                     | U-0                                                    | R/W-0                                                         | U-0                          |

|                             | TGATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TCKPS1                                                                                                                                                                       | TCKPS0                                                                                                                                          | T32 <sup>(3)</sup>                                                                        | _                                                      | TCS <sup>(2)</sup>                                            |                              |

| bit 7                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                              |                                                                                                                                                 |                                                                                           |                                                        |                                                               | bit (                        |

| Legend:                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                              |                                                                                                                                                 |                                                                                           |                                                        |                                                               |                              |

| R = Read                    | able bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | W = Writable                                                                                                                                                                 | bit                                                                                                                                             | U = Unimplem                                                                              | nented bit, rea                                        | d as '0'                                                      |                              |

| -n = Value                  | e at POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                                             |                                                                                                                                                 | '0' = Bit is clea                                                                         | ared                                                   | x = Bit is unkn                                               | iown                         |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                              |                                                                                                                                                 |                                                                                           |                                                        |                                                               |                              |