Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                 |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                               |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 29x12b, 2x16b; D/A 2x10b                                                  |

| Oscillator Type            | Internal                                                                      |

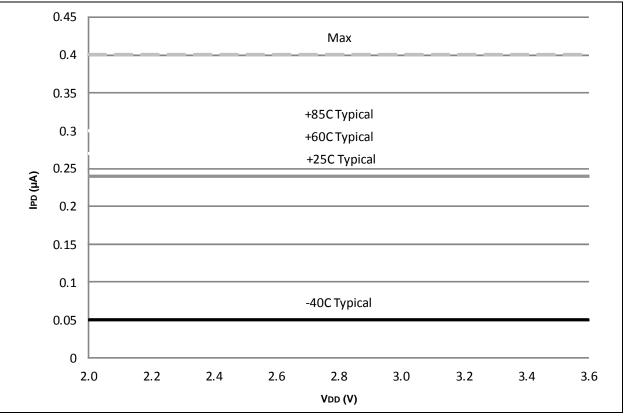

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gc006-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Universal Serial Bus Features**

- USB v2.0 On-The-Go (OTG) Compliant

- USB Device mode Operation from FRC Oscillator No Crystal Oscillator Required

- Dual Role Capable Can Act as Either Host or Peripheral

- Low-Speed (1.5 Mb/s) and Full-Speed (12 Mb/s) USB Operation in Host mode

- Full-Speed USB Operation in Device mode

- Low Jitter PLL for USB

- Supports up to 32 Endpoints (16 bidirectional):

- USB module can use any RAM location on the device as USB endpoint buffers

- On-Chip USB Transceiver with Interface for Off-Chip USB Transceiver

- Supports Control, Interrupt, Isochronous and Bulk Transfers

- On-Chip Pull-up and Pull-Down Resistors

# **Peripheral Features**

- LCD Display Controller:

- Up to 59 segments by 8 commons

- Internal charge pump and low-power, internal resistor biasing

- Operation in Sleep mode

- Up to Five External Interrupt Sources

- Peripheral Pin Select (PPS); Allows Independent I/O Mapping of Many Peripherals

- Five 16-Bit Timers/Counters with Prescaler:

- Can be paired as 32-bit timers/counters

- Six-Channel DMA Supports All Peripheral modules:

Minimizes CPU overhead, increases data throughput and lowers power consumption

- Nine Input Capture modules, each with a Dedicated 16-Bit Timer

- Nine Output Compare/PWM modules, each with a Dedicated 16-Bit Timer

- Enhanced Parallel Master/Slave Port (EPMP/EPSP)

- Hardware Real-Time Clock and Calendar (RTCC):

Run, Sleep, Deep Sleep and VBAT modes

- Two 3-Wire/4-Wire SPI modules (support 4 Frame modes) with 8-Level FIFO Buffer

- Two I<sup>2</sup>C modules Support Multi-Master/Slave mode and 7-Bit/10-Bit Addressing

- Four UART modules:

- Support RS-485, RS-232 and LIN/J2602

- On-chip hardware encoder/decoder for IrDA®

- Auto-wake-up on Auto-Baud Detect (ABD)

- 4-level deep FIFO buffer

- Programmable, 32-Bit Cyclic Redundancy Check (CRC) Generator

- Digital Signal Modulator (DSM) Provides On-Chip FSK and PSK Modulation for a Digital Signal Stream

- High-Current Sink/Source (18 mA/18 mA) on All I/O Pins

- Configurable Open-Drain Outputs on Digital I/O Pins

- · 5.5V Tolerant Inputs on Select Pins

# High-Performance CPU

- Modified Harvard Architecture

- Up to 16 MIPS Operation @ 32 MHz

- C Compiler Optimized Instruction Set Architecture (ISA)

- 8 MHz Internal Oscillator:

- 96 MHz PLL option for USB clocking

- Multiple clock divide options

- Run-time self-calibration capability for maintaining better than  $\pm 0.20\%$  accuracy

- Fast start-up

- 17-Bit x 17-Bit Single-Cycle Hardware Fractional/Integer Multiplier

- · 32-Bit by 16-Bit Hardware Divider

- 16 x 16-Bit Working Register Array

- Two Address Generation Units (AGUs) for Separate Read and Write Addressing of Data Memory

### **Special Microcontroller Features**

- Supply Voltage Range of 2.0V to 3.6V

- Two On-Chip Voltage Regulators (1.8V and 1.2V) for Regular and eXtreme Low-Power Operation

- 20,000 Erase/Write Cycle Endurance Flash Program Memory, Typical

- Flash Data Retention: 20 Years Minimum

- · Self-Programmable under Software Control

- Programmable Reference Clock Output

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and In-Circuit Emulation (ICE) via 2 Pins

- JTAG Boundary Scan Support

- Fail-Safe Clock Monitor Operation:

Detects clock failure and switches to on-

- Detects clock failure and switches to on-chip, low-power RC Oscillator

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Separate Brown-out Reset (BOR) and Deep Sleep

Brown-out Reset (DSBOR) Circuits

- Programmable High/Low-Voltage Detect (HLVD)

- Flexible Watchdog Timer (WDT) with its Own RC Oscillator for Reliable Operation

- Standard and Ultra Low-Power Watchdog Timers for Reliable Operation in Standard and Deep Sleep modes

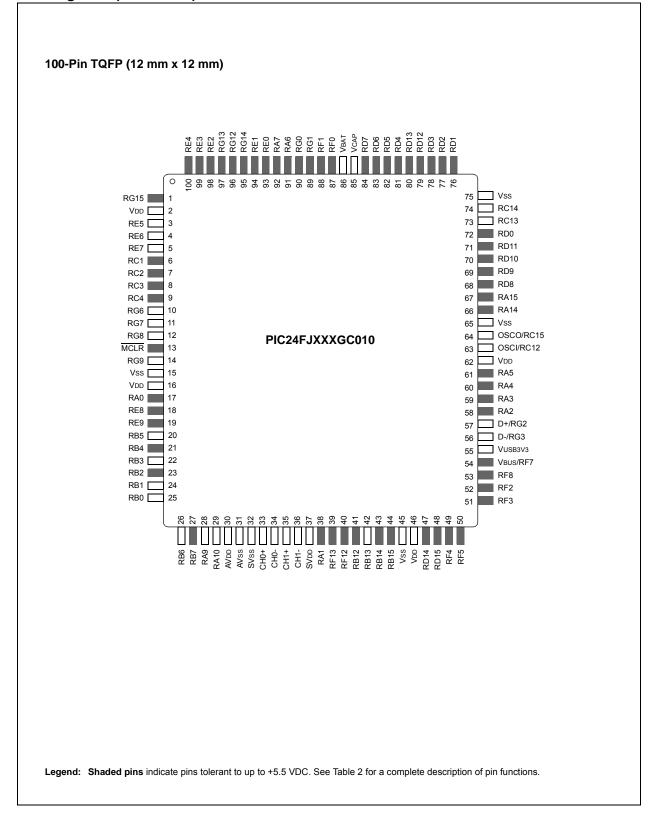

### **Pin Diagrams (Continued)**

### 2.7 Configuration of Analog and Digital Pins During ICSP Operations

If an ICSP compliant emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins. Depending on the particular device, this is done by setting all bits in the ADxPCFG register(s) or clearing all bits in the ANSx registers.

All PIC24F devices will have either one or more ADxPCFG registers or several ANSx registers (one for each port); no device will have both. Refer to **Section 11.2 "Configuring Analog Port Pins** (ANSx)" for more specific information.

The bits in these registers that correspond to the A/D pins that initialized the emulator must not be changed by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must modify the appropriate bits during initialization of the A/D module, as follows:

- For devices with an ADxPCFG register, clear the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGECx/PGEDx pair, at any time.

- For devices with ANSx registers, set the bits corresponding to the pin(s) to be configured as analog. Do not change any other bits, particularly those corresponding to the PGECx/PGEDx pair, at any time.

When a Microchip debugger/emulator is used as a programmer, the user application firmware must correctly configure the ADxPCFG or ANSx registers. Automatic initialization of these registers is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.8 Sigma-Delta A/D Connections

The Sigma-Delta A/D Converter has input and power connections that are independent from the rest of the microcontroller. These connections are required to use the converter, and are in addition to the connection and layout connections provided in Section 2.1 "Basic Connection Requirements" and Section 2.2 "Power Supply Pins".

#### 2.8.1 VOLTAGE AND GROUND CONNECTIONS

To minimize noise interference, the Sigma-Delta A/D Converter has independent voltage pins. Converter circuits are supplied through the SVDD pin. Independent ground return is provided through the SVss pin.

As with the microcontroller's VDD/VSS and AVDD/AVSS pins, bypass capacitors are required on SVDD and SVSS. Requirements for these capacitors are identical to those for the VDD/VSS and AVDD/AVSS pins.

It is recommended that designs using the Sigma-Delta A/D Converter incorporate a separate ground return path for analog circuits. The analog and digital grounds may be tied to a single point at the power source. Analog pins that require grounding should be tied to this analog return. SVss can be tied to the digital ground, along with Vss and AVss.

### 2.8.2 ANALOG INPUTS

The analog signals to be converted are connected to the pins of CH0 and/or CH1. Each channel has inverting and non-inverting inputs (CHx- and CHx+, respectively), and is fully differential.

If not used for conversion, CH1+ and CH1- can be used to supply an external voltage reference to the converter. If an external reference is not used and CH1 is not needed as a conversion input, both pins should be connected to the analog ground return.

### 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### TABLE 4-27: USB OTG REGISTER MAP

| File<br>Name         | Addr                | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                 | Bit 6                   | Bit 5            | Bit 4          | Bit 3          | Bit 2        | Bit 1                | Bit 0                   | All<br>Resets |

|----------------------|---------------------|--------|--------|--------|--------|--------|--------|-------|-------|-----------------------|-------------------------|------------------|----------------|----------------|--------------|----------------------|-------------------------|---------------|

| U10TGIR              | 0480                | _      | —      | —      | —      | _      | —      | _     | —     | IDIF                  | T1MSECIF                | LSTATEIF         | ACTVIF         | SESVDIF        | SESENDIF     | _                    | VBUSVDIF                | 0000          |

| U10TGIE              | 0482                | _      | _      | -      | _      |        | _      | _     | —     | IDIE                  | T1MSECIE                | LSTATEIE         | ACTVIE         | SESVDIE        | SESENDIE     | _                    | VBUSVDIE                | 0000          |

| U1OTGSTAT            | 0484                |        |        | —      | —      | _      | -      |       | —     | ID                    | _                       | LSTATE           | -              | SESVD          | SESEND       |                      | VBUSVD                  | 0000          |

| U10TGCON             | 0486                |        |        | _      | _      | _      | _      |       | —     | DPPULUP               | DMPULUP                 | DPPULDWN         | DMPULDWN       | r              | OTGEN        | r                    | VBUSDIS                 | 0000          |

| U1PWRC               | 0488                | _      |        | —      | —      |        | —      | _     | —     | UACTPND               | —                       | —                | USLPGRD        | _              | —            | USUSPND              | USBPWR                  | 00x0          |

| U1IR                 | 048A <sup>(1)</sup> | _      | —      | —      | —      | —      | —      | _     | —     | STALLIF               | —                       | RESUMEIF         | IDLEIF         | TRNIF          | SOFIF        | UERRIF               | URSTIF                  | 0000          |

|                      |                     | _      | —      | —      | —      | —      | —      | _     | —     | STALLIF               | ATTACHIF <sup>(1)</sup> | RESUMEIF         | IDLEIF         | TRNIF          | SOFIF        | UERRIF               | DETACHIF <sup>(1)</sup> | 0000          |

| U1IE                 | 048C <sup>(1)</sup> | _      | _      | —      | _      | _      | —      | _     | —     | STALLIE               | —                       | RESUMEIE         | IDLEIE         | TRNIE          | SOFIE        | UERRIE               | URSTIE                  | 0000          |

|                      |                     | _      | —      | —      | —      | —      | —      | _     | —     | STALLIE               | ATTACHIE <sup>(1)</sup> | RESUMEIE         | IDLEIE         | TRNIE          | SOFIE        | UERRIE               | DETACHIE <sup>(1)</sup> | 0000          |

| U1EIR                | 048E <sup>(1)</sup> | _      | —      | —      | —      | —      | —      | _     |       | BTSEF                 | —                       | DMAEF            | BTOEF          | DFN8EF         | CRC16EF      | CRC5EF               | PIDEF                   | 0000          |

|                      |                     | _      | _      | —      | _      | _      | —      | _     | —     | BTSEF                 | —                       | DMAEF            | BTOEF          | DFN8EF         | CRC16EF      | EOFEF <sup>(1)</sup> | PIDEF                   | 0000          |

| U1EIE                | 0490 <sup>(1)</sup> | _      | —      | —      | —      | —      | —      | _     | —     | BTSEE                 | —                       | DMAEE            | BTOEE          | DFN8EE         | CRC16EE      | CRC5EE               | PIDEE                   | 0000          |

|                      |                     | _      | _      | —      | _      | _      | —      | _     | —     | BTSEE                 | —                       | DMAEE            | BTOEE          | DFN8EE         | CRC16EE      | EOFEE <sup>(1)</sup> | PIDEE                   | 0000          |

| U1STAT               | 0492                | _      | _      | —      | _      | _      | —      | _     | —     | ENDPT3                | ENDPT2                  | ENDPT1           | ENDPT0         | DIR            | PPBI         | _                    |                         | 0000          |

| U1CON                | 0494(1)             | _      |        | —      | —      |        | —      | _     | —     |                       | SE0                     | PKTDIS           | _              | HOSTEN         | RESUME       | PPBRST               | USBEN                   | 0000          |

|                      |                     | _      | _      | —      | _      | _      | —      | _     | —     | JSTATE <sup>(1)</sup> | SE0                     | TOKBUSY          | USBRST         | HOSTEN         | RESUME       | PPBRST               | SOFEN <sup>(1)</sup>    | 0000          |

| U1ADDR               | 0496                | _      | —      | —      | —      | —      | —      | _     | —     | LSPDEN <sup>(1)</sup> |                         |                  | USB Device A   | ddress (ADD    | OR) Register |                      |                         | 0000          |

| U1BDTP1              | 0498                | _      |        | —      | —      |        | —      | _     | —     |                       | Bi                      | uffer Descriptor | Table Base Ad  | dress Regist   | er           |                      | —                       | 0000          |

| U1FRML               | 049A                | _      | —      | —      | —      | —      | —      | _     | —     |                       |                         | Fra              | ame Count Reg  | gister Low By  | /te          |                      |                         | 0000          |

| U1FRMH               | 049C                | _      | —      | —      | —      | —      | —      | _     |       |                       |                         | Fra              | ame Count Reg  | jister High By | /te          | -                    | 1                       | 0000          |

| U1TOK <sup>(2)</sup> | 049E                | —      | —      | —      | —      | —      | —      | —     | —     | PID3                  | PID2                    | PID1             | PID0           | EP3            | EP2          | EP1                  | EP0                     | 0000          |

| U1SOF <sup>(2)</sup> | 04A0                | _      | _      | —      | _      | _      | —      | _     | —     |                       |                         |                  | Start-of-Frame | Size Register  | r            |                      |                         | 0000          |

| U1CNFG1              | 04A6                | _      | —      | —      | —      | —      | —      | _     |       | UTEYE                 | UOEMON                  | —                | USBSIDL        | _              | —            | PPB1                 | PPB0                    | 0000          |

| U1CNFG2              | 04A8                | _      |        | —      | —      |        | —      | _     | —     |                       | —                       | UVCMPSEL         | PUVBUS         | EXTI2CEN       | —            | UVCMPDIS             | UTRDIS                  | 0000          |

| U1EP0                | 04AA                | _      | —      | —      | —      | —      | —      | _     | —     | LSPD <sup>(1)</sup>   | RETRYDIS <sup>(1)</sup> | —                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

| U1EP1                | 04AC                | _      | —      | —      | —      | —      | —      | _     | —     | —                     | _                       | —                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

| U1EP2                | 04AE                | _      | —      | —      | —      | —      | —      | _     |       | —                     | —                       | _                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

| U1EP3                | 04B0                | _      | —      | —      | —      | —      | —      | _     | —     |                       | —                       | —                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

| U1EP4                | 04B2                | _      | —      | —      | —      | —      | —      | _     |       |                       | —                       | —                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

| U1EP5                | 04B4                | _      | —      | —      | —      | —      | —      | _     | —     | -                     | —                       | —                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

| U1EP6                | 04B6                | _      |        |        |        |        | —      | -     | _     |                       | _                       | _                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

| U1EP7                | 04B8                | _      |        |        |        |        | —      | _     | _     |                       | _                       | _                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

| U1EP8                | 04BA                | _      | _      | —      | —      | —      | —      | _     | _     | —                     | —                       | —                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

| U1EP9                | 04BC                | —      | _      | —      | —      | _      | —      | _     | —     | _                     | _                       | _                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

| U1EP10               | 04BE                | —      | —      | —      | —      | —      | —      | —     | —     | -                     | _                       | —                | EPCONDIS       | EPRXEN         | EPTXEN       | EPSTALL              | EPHSHK                  | 0000          |

Legend: — = unimplemented, read as '0'; r = reserved, do not modify. Reset values are shown in hexadecimal.

Note 1: Alternate register or bit definitions when the module is operating in Host mode.

2: This register is available in Host mode only.

#### CICTED 0 10 .... ----NTRAL DECISTED 5

| U-0                               | U-0                                                                                                           | R/W-0                                                                                              | R/W-0           | U-0               | U-0             | R/W-0           | R/W-0  |  |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|--------|--|--|--|--|--|

| _                                 | _                                                                                                             | IC9IE                                                                                              | OC9IE           |                   | _               | U4TXIE          | U4RXIE |  |  |  |  |  |

| bit 15                            |                                                                                                               |                                                                                                    |                 |                   |                 |                 | bit    |  |  |  |  |  |

| DAMO                              |                                                                                                               |                                                                                                    |                 | DAVA              | DAMO            | DAMO            |        |  |  |  |  |  |

| R/W-0<br>U4ERIE                   | R/W-0<br>USB1IE                                                                                               | U-0                                                                                                | U-0             | R/W-0             | R/W-0<br>U3RXIE | R/W-0           | U-0    |  |  |  |  |  |

| bit 7                             | USBIIE                                                                                                        |                                                                                                    | _               | U3TXIE            | USRAIE          | U3ERIE          |        |  |  |  |  |  |

|                                   |                                                                                                               |                                                                                                    |                 |                   |                 |                 | bit    |  |  |  |  |  |

| Legend:                           |                                                                                                               |                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

| R = Readab                        | le bit                                                                                                        | W = Writable                                                                                       | bit             | U = Unimplem      | ented bit, rea  | d as '0'        |        |  |  |  |  |  |

| n = Value at POR '1' = Bit is set |                                                                                                               |                                                                                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkn | iown   |  |  |  |  |  |

| hit 15 11                         | Unimploment                                                                                                   | ted. Dood oo '                                                                                     | o'              |                   |                 |                 |        |  |  |  |  |  |

| bit 15-14<br>bit 13               | -                                                                                                             | i <b>ted:</b> Read as '<br>Capture Chann                                                           |                 | nable bit         |                 |                 |        |  |  |  |  |  |

|                                   | •                                                                                                             | request is enal                                                                                    | •               |                   |                 |                 |        |  |  |  |  |  |

|                                   |                                                                                                               | request is not                                                                                     |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 12                            | OC9IE: Outp                                                                                                   | ut Compare Ch                                                                                      | annel 9 Enabl   | e Status bit      |                 |                 |        |  |  |  |  |  |

|                                   |                                                                                                               | request is enal                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

|                                   | -                                                                                                             | request is not                                                                                     |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 11-10                         | Unimplemented: Read as '0' U4TXIE: UART4 Transmitter Interrupt Enable bit                                     |                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 9                             |                                                                                                               |                                                                                                    | =               | ble bit           |                 |                 |        |  |  |  |  |  |

|                                   |                                                                                                               | request is enal                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 8                             | <ul> <li>0 = Interrupt request is not enabled</li> <li>U4RXIE: UART4 Receiver Interrupt Enable bit</li> </ul> |                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

|                                   |                                                                                                               | 1 = Interrupt request is enabled                                                                   |                 |                   |                 |                 |        |  |  |  |  |  |

|                                   | 0 = Interrupt                                                                                                 | request is not                                                                                     | enabled         |                   |                 |                 |        |  |  |  |  |  |

| bit 7                             | U4ERIE: UART4 Error Interrupt Enable bit                                                                      |                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

|                                   | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul>            |                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 6                             | •                                                                                                             | •                                                                                                  |                 | la hit            |                 |                 |        |  |  |  |  |  |

|                                   |                                                                                                               | B1 (USB OTG)<br>request is enal                                                                    | =               | ne bit            |                 |                 |        |  |  |  |  |  |

|                                   |                                                                                                               | request is not                                                                                     |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 5-4                           | Unimplemen                                                                                                    | ted: Read as '                                                                                     | 0'              |                   |                 |                 |        |  |  |  |  |  |

| bit 3                             | U3TXIE: UAF                                                                                                   | RT3 Transmitte                                                                                     | r Interrupt Ena | ble bit           |                 |                 |        |  |  |  |  |  |

|                                   | 1 = Interrupt                                                                                                 | request is enal                                                                                    | bled            |                   |                 |                 |        |  |  |  |  |  |

|                                   | -                                                                                                             | request is not                                                                                     |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 2                             |                                                                                                               | RT3 Receiver I                                                                                     | -               | e bit             |                 |                 |        |  |  |  |  |  |

|                                   |                                                                                                               | request is enal<br>request is not                                                                  |                 |                   |                 |                 |        |  |  |  |  |  |

| bit 1                             | -                                                                                                             | RT3 Error Inter                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

| <b>NIL I</b>                      |                                                                                                               |                                                                                                    | -               |                   |                 |                 |        |  |  |  |  |  |

|                                   |                                                                                                               | <ul> <li>1 = Interrupt request is enabled</li> <li>0 = Interrupt request is not enabled</li> </ul> |                 |                   |                 |                 |        |  |  |  |  |  |

|                                   |                                                                                                               |                                                                                                    |                 |                   |                 |                 |        |  |  |  |  |  |

| U-0                 | U-0                                   | U-0                                        | R/W-0                                 | R/W-0                      | R/W-0                 | R/W-0              | R/W-0              |  |  |  |

|---------------------|---------------------------------------|--------------------------------------------|---------------------------------------|----------------------------|-----------------------|--------------------|--------------------|--|--|--|

| _                   |                                       |                                            | DISSCK <sup>(1)</sup>                 | DISSDO <sup>(2)</sup>      | MODE16                | SMP                | CKE <sup>(3)</sup> |  |  |  |

| bit 15              |                                       |                                            |                                       |                            |                       |                    | bit 8              |  |  |  |

| R/W-0               | R/W-0                                 | R/W-0                                      | R/W-0                                 | R/W-0                      | R/W-0                 | R/W-0              | R/W-0              |  |  |  |

| SSEN <sup>(4)</sup> | -                                     | MSTEN                                      | SPRE2                                 | SPRE1                      | SPRE0                 | PPRE1              | PPRE0              |  |  |  |

| bit 7               |                                       | MISTEN                                     | SFREZ                                 | JFRE1                      | SFREU                 | FFNEI              | bit (              |  |  |  |

|                     |                                       |                                            |                                       |                            |                       |                    |                    |  |  |  |

| Legend:             |                                       |                                            | L:4                                   |                            | anted bit wood        | aa (0)             |                    |  |  |  |

| R = Reada           |                                       | W = Writable                               |                                       | -                          | ented bit, read       |                    |                    |  |  |  |

| -n = Value          | at POR                                | '1' = Bit is set                           |                                       | '0' = Bit is clea          | ared                  | x = Bit is unkn    | own                |  |  |  |

| bit 15-13           | Unimplemen                            | ted: Read as '                             | 0'                                    |                            |                       |                    |                    |  |  |  |

| bit 12              | DISSCK: Disa                          | able SCKx Pin                              | bit (SPI Master                       | modes only) <sup>(1)</sup> | )                     |                    |                    |  |  |  |

|                     | 1 = Internal S                        | SPI clock is dis                           | abled; pin funct                      |                            |                       |                    |                    |  |  |  |

|                     |                                       | SPI clock is ena                           |                                       |                            |                       |                    |                    |  |  |  |

| bit 11              |                                       | able SDOx Pin                              |                                       |                            |                       |                    |                    |  |  |  |

|                     |                                       | n is not used by<br>n is controlled l      |                                       | in functions as            | I/O                   |                    |                    |  |  |  |

| bit 10              | •                                     | MODE16: Word/Byte Communication Select bit |                                       |                            |                       |                    |                    |  |  |  |

|                     |                                       | 1 = Communication is word-wide (16 bits)   |                                       |                            |                       |                    |                    |  |  |  |

|                     | 0 = Commun                            | ication is byte-                           | wide (8 bits)                         |                            |                       |                    |                    |  |  |  |

| bit 9               | SMP: SPIx D                           | ata Input Sam                              | ole Phase bit                         |                            |                       |                    |                    |  |  |  |

|                     | Master mode:                          |                                            | t the end of dot                      | o outout timo              |                       |                    |                    |  |  |  |

|                     |                                       |                                            | t the end of dat<br>t the middle of ( | data output time           | 9                     |                    |                    |  |  |  |

|                     | Slave mode:                           | -                                          |                                       | -                          |                       |                    |                    |  |  |  |

| 1.1.0               |                                       |                                            | SPIx is used in                       | Slave mode.                |                       |                    |                    |  |  |  |

| bit 8               |                                       | lock Edge Sele                             |                                       | n from active cl           | ock state to Idl      | o clock stato (s   | oo hit 6)          |  |  |  |

|                     |                                       |                                            |                                       | n from Idle cloc           |                       |                    |                    |  |  |  |

| bit 7               |                                       |                                            | (Slave mode) I                        |                            |                       |                    | /                  |  |  |  |

|                     | $1 = \overline{SSx}$ pin i            | s used for Slav                            | ve mode                               | is controlled by           | , the port functi     | on                 |                    |  |  |  |

| bit 6               |                                       | olarity Select I                           |                                       | is controlled by           |                       |                    |                    |  |  |  |

|                     |                                       |                                            |                                       | ctive state is a           | low level             |                    |                    |  |  |  |

|                     |                                       |                                            |                                       | ctive state is a h         |                       |                    |                    |  |  |  |

| bit 5               | MSTEN: SPI)                           | K Master Mode                              | Enable bit                            |                            |                       |                    |                    |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo          |                                            |                                       |                            |                       |                    |                    |  |  |  |

| Note 1:             | If DISSCK = 0, S                      |                                            | onfigured to an                       | available RPn              | pin See <b>Sectio</b> | on 11.4 "Perin     | heral Pin          |  |  |  |

|                     | Select (PPS)" for                     |                                            |                                       |                            |                       | ·····              |                    |  |  |  |

| 2:                  | If DISSDO = 0, S<br>Select (PPS)" for |                                            |                                       | available RPn              | pin. See Secti        | on 11.4 "Perip     | oheral Pin         |  |  |  |

| 3:                  | The CKE bit is no<br>SPI modes (FRM   |                                            | ramed SPI mod                         | des. The user s            | hould program         | this bit to '0' fo | r the Framed       |  |  |  |

|                     | If SSEN = 1, $\overline{SSx}$         | -                                          |                                       |                            |                       |                    |                    |  |  |  |

### REGISTER 16-2: SPIxCON1: SPIx CONTROL REGISTER 1

#### REGISTER 17-1: **I2CxCON: I2Cx CONTROL REGISTER** R/W-0 U-0 R/W-0 R/W-1, HC R/W-0 R/W-0 R/W-0 R/W-0 **I2CSIDL I2CEN** SCLREL **IPMIEN** A10M DISSLW SMEN bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0, HC R/W-0, HC R/W-0, HC R/W-0, HC R/W-0, HC GCEN STREN ACKDT ACKEN RCEN PEN RSEN SEN bit 7 bit 0 HC = Hardware Clearable bit Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' '1' = Bit is set '0' = Bit is cleared -n = Value at POR x = Bit is unknown bit 15 I2CEN: I2Cx Enable bit 1 = Enables the I2Cx module and configures the SDAx and SCLx pins as serial port pins 0 = Disables the I2Cx module; all I<sup>2</sup>C pins are controlled by port functions Unimplemented: Read as '0' bit 14 bit 13 I2CSIDL: I2Cx Stop in Idle Mode bit 1 = Discontinues module operation when device enters an Idle mode 0 = Continues module operation in Idle mode SCLREL: SCLx Release Control bit (when operating as I<sup>2</sup>C slave) bit 12 1 = Releases SCLx clock 0 = Holds SCLx clock low (clock stretch) If STREN = 1: Bit is R/W (i.e., software may write '0' to initiate stretch and write '1' to release clock). Hardware is clear at the beginning of slave transmission. Hardware is clear at the end of slave reception. If STREN = 0: Bit is R/S (i.e., software may only write '1' to release clock). Hardware is clear at the beginning of slave transmission. bit 11 IPMIEN: Intelligent Platform Management Interface (IPMI) Enable bit 1 = IPMI Support mode is enabled; all addresses are Acknowledged 0 = IPMI Support mode is disabled bit 10 A10M: 10-Bit Slave Addressing bit 1 = I2CxADD is a 10-bit slave address 0 = I2CxADD is a 7-bit slave address **DISSLW:** Disable Slew Rate Control bit bit 9 1 = Slew rate control is disabled 0 = Slew rate control is enabled bit 8 SMEN: SMBus Input Levels bit 1 = Enables I/O pin thresholds compliant with SMBus specifications 0 = Disables the SMBus input thresholds bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave) 1 = Enables interrupt when a general call address is received in the I2CxRSR (module is enabled for reception) 0 = General call address is disabled STREN: SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave) bit 6 Used in conjunction with the SCLREL bit. 1 = Enables software or receives clock stretching 0 = Disables software or receives clock stretching

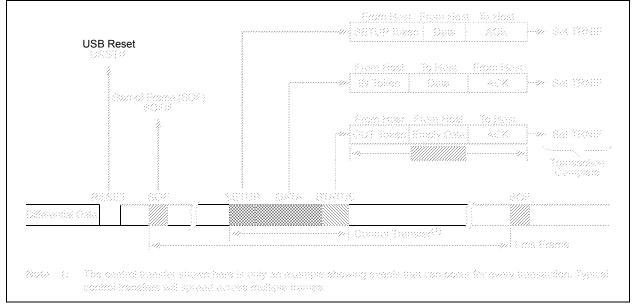

### 19.3.1 CLEARING USB OTG INTERRUPTS

Unlike device-level interrupts, the USB OTG interrupt status flags are not freely writable in software. All USB OTG flag bits are implemented as hardware settable only bits. Additionally, these bits can only be cleared in software by writing a '1' to their locations (i.e., performing a MOV type instruction). Writing a '0' to a flag bit (i.e., a BCLR instruction) has no effect.

Note: Throughout this data sheet, a bit that can only be cleared by writing a '1' to its location is referred to as "Write 1 to clear". In register descriptions, this function is indicated by the descriptor, "K".

# 19.4 Device Mode Operation

The following section describes how to perform a common Device mode task. In Device mode, USB transfers are performed at the transfer level. The USB module automatically performs the status phase of the transfer.

#### 19.4.1 ENABLING DEVICE MODE

- Reset the Ping-Pong Buffer Pointers by setting, then clearing, the Ping-Pong Buffer Reset bit, PPBRST (U1CON<1>).

- 2. Disable all interrupts (U1IE and U1EIE = 00h).

- 3. Clear any existing interrupt flags by writing FFh to U1IR and U1EIR.

- 4. Verify that VBUS is present (non-OTG devices only).

- 5. Enable the USB module by setting the USBEN bit (U1CON<0>).

- Set the OTGEN bit (U1OTGCON<2>) to enable OTG operation.

- Enable the Endpoint 0 buffer to receive the first setup packet by setting the EPRXEN and EPHSHK bits for Endpoint 0 (U1EP0<3,0> = 1).

- 8. Power up the USB module by setting the USBPWR bit (U1PWRC<0>).

- Enable the D+ pull-up resistor to signal an attach by setting the DPPULUP bit (U10TGCON<7>).

|                | U-0                                                                                                                                                                                                                                                        | U-0                                                    | U-0                                                             | U-0            | U-0                  | U-0           | U-0                    |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------|----------------|----------------------|---------------|------------------------|--|--|

| —              | —                                                                                                                                                                                                                                                          | —                                                      | _                                                               | _              | —                    |               | —                      |  |  |

| bit 15         |                                                                                                                                                                                                                                                            |                                                        |                                                                 |                |                      |               | bit 8                  |  |  |

|                |                                                                                                                                                                                                                                                            |                                                        |                                                                 |                |                      |               |                        |  |  |

| R/W-0          | R/W-0                                                                                                                                                                                                                                                      | R/W-0                                                  | R/W-0                                                           | r-0            | R/W-0                | r-0           | R/W-0                  |  |  |

| DPPULUP        | DMPULUP                                                                                                                                                                                                                                                    | DPPULDWN <sup>(1)</sup>                                | DMPULDWN <sup>(1)</sup>                                         |                | OTGEN <sup>(1)</sup> |               | VBUSDIS <sup>(1)</sup> |  |  |

| bit 7          |                                                                                                                                                                                                                                                            |                                                        |                                                                 |                |                      |               | bit 0                  |  |  |

| Legend:        |                                                                                                                                                                                                                                                            | r = Reserved bit                                       |                                                                 |                |                      |               |                        |  |  |

| R = Readal     | ble bit                                                                                                                                                                                                                                                    | W = Writable bit                                       |                                                                 | U = Unimpl     | emented bit, rea     | ad as 'O'     |                        |  |  |

| -n = Value a   |                                                                                                                                                                                                                                                            | '1' = Bit is set                                       |                                                                 | '0' = Bit is c |                      | x = Bit is un | known                  |  |  |

|                |                                                                                                                                                                                                                                                            |                                                        |                                                                 |                |                      |               |                        |  |  |

| bit 15-8       | Unimpleme                                                                                                                                                                                                                                                  | nted: Read as '0'                                      |                                                                 |                |                      |               |                        |  |  |

| oit 7          | DPPULUP:                                                                                                                                                                                                                                                   | DPPULUP: D+ Pull-up Enable bit                         |                                                                 |                |                      |               |                        |  |  |

|                |                                                                                                                                                                                                                                                            | line pull-up resist                                    |                                                                 |                |                      |               |                        |  |  |

|                |                                                                                                                                                                                                                                                            | line pull-up resist                                    |                                                                 |                |                      |               |                        |  |  |

| bit 6          |                                                                                                                                                                                                                                                            | D- Pull-up Enable                                      |                                                                 |                |                      |               |                        |  |  |

|                |                                                                                                                                                                                                                                                            | line pull-up resiste<br>line pull-up resiste           |                                                                 |                |                      |               |                        |  |  |

| bit 5          |                                                                                                                                                                                                                                                            | I: D+ Pull-Down E                                      |                                                                 |                |                      |               |                        |  |  |

|                |                                                                                                                                                                                                                                                            | line pull-down res                                     |                                                                 |                |                      |               |                        |  |  |

|                |                                                                                                                                                                                                                                                            | line pull-down re                                      |                                                                 |                |                      |               |                        |  |  |

| bit 4          | DMPULDWI                                                                                                                                                                                                                                                   | N: D- Pull-Down E                                      | nable bit <sup>(1)</sup>                                        |                |                      |               |                        |  |  |

|                |                                                                                                                                                                                                                                                            | line pull-down res                                     |                                                                 |                |                      |               |                        |  |  |

|                |                                                                                                                                                                                                                                                            | line pull-down res                                     | istor is disabled                                               |                |                      |               |                        |  |  |

| bit 3          |                                                                                                                                                                                                                                                            | /laintain as '0'                                       |                                                                 |                |                      |               |                        |  |  |

|                |                                                                                                                                                                                                                                                            | G Features Enab                                        |                                                                 |                |                      |               |                        |  |  |

| bit 2          | <ul> <li>1 = USB OTG is enabled; all D+/D- pull-up and pull-down bits are enabled</li> <li>0 = USB OTG is disabled; D+/D- pull-up and pull-down bits are controlled in hardware by the settings of the HOSTEN and USBEN (U1CON&lt;3,0&gt;) bits</li> </ul> |                                                        |                                                                 |                |                      |               |                        |  |  |

| bit 2          | 0 = USB OT                                                                                                                                                                                                                                                 | G is disabled; D-                                      | ⊦/D- pull-up and p                                              |                | s are controlled     | in hardware   | by the settings        |  |  |

| bit 2<br>bit 1 | 0 = USB OT<br>of the H                                                                                                                                                                                                                                     | G is disabled; D-                                      | ⊦/D- pull-up and p                                              |                | s are controlled     | in hardware   | by the settings        |  |  |

|                | 0 = USB OT<br>of the H<br>Reserved: M                                                                                                                                                                                                                      | G is disabled; D-<br>OSTEN and USB<br>/laintain as '0' | -/D- pull-up and μ<br>EN (U1CON<3,0                             |                | s are controlled     | in hardware   | by the settings        |  |  |

| bit 1          | 0 = USB OT<br>of the H<br><b>Reserved:</b> N<br><b>VBUSDIS:</b> N                                                                                                                                                                                          | G is disabled; D-<br>OSTEN and USB                     | ⊦/D- pull-up and p<br>EN (U1CON<3,0<br>nable bit <sup>(1)</sup> |                | s are controlled     | in hardware   | by the settings        |  |  |

#### Note 1: These bits are only used in Host mode; do not use them in Device mode.

#### 19.7.2 USB INTERRUPT REGISTERS

#### REGISTER 19-14: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER (HOST MODE ONLY)

| U-0    | U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |  |  |

|--------|--------------|-----|-----|-----|-----|-----|-----|--|--|--|

| —      | —            | —   | —   | _   | —   | —   | —   |  |  |  |

| bit 15 | bit 15 bit 8 |     |     |     |     |     |     |  |  |  |

| R/K-0, HS | U-0 | R/K-0, HS |

|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----------|

| IDIF      | T1MSECIF  | LSTATEIF  | ACTVIF    | SESVDIF   | SESENDIF  | —   | VBUSVDIF  |

| bit 7     |           |           |           |           |           |     | bit 0     |

| Legend:           | HS = Hardware Settable bit                                    | HS = Hardware Settable bit |                    |  |  |  |  |

|-------------------|---------------------------------------------------------------|----------------------------|--------------------|--|--|--|--|

| R = Readable bit  | K = Write '1' to Clear bit U = Unimplemented bit, read as '0' |                            |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                              | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                              |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | IDIF: ID State Change Indicator bit                                                                                                                     |

|          | 1 = Change in ID state is detected                                                                                                                      |

|          | 0 = No ID state change is detected                                                                                                                      |

| bit 6    | T1MSECIF: 1 Millisecond Timer bit                                                                                                                       |

|          | 1 = The 1 millisecond timer has expired                                                                                                                 |

|          | 0 = The 1 millisecond timer has not expired                                                                                                             |

| bit 5    | LSTATEIF: Line State Stable Indicator bit                                                                                                               |

|          | <ul> <li>1 = USB line state (as defined by the SE0 and JSTATE bits) has been stable for 1 ms, but different from<br/>the last time</li> </ul>           |

|          | 0 = USB line state has not been stable for 1 ms                                                                                                         |

| bit 4    | ACTVIF: Bus Activity Indicator bit                                                                                                                      |

|          | 1 = Activity on the D+/D- lines or VBUS is detected                                                                                                     |

|          | 0 = No activity on the D+/D- lines or VBUS is detected                                                                                                  |

| bit 3    | SESVDIF: Session Valid Change Indicator bit                                                                                                             |

|          | 1 = VBUS has crossed VA_SESS_END (as defined in the <i>"USB 2.0 OTG Specification"</i> ) <sup>(1)</sup>                                                 |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                                                    |

| bit 2    | SESENDIF: B-Device VBUS Change Indicator bit                                                                                                            |

|          | <ul> <li>1 = VBUS change on B-device is detected; VBUS has crossed VB_SESS_END (as defined in the "USB 2.0 OTG Specification")<sup>(1)</sup></li> </ul> |

|          | 0 = VBUS has not crossed VA_SESS_END                                                                                                                    |

| bit 1    | Unimplemented: Read as '0'                                                                                                                              |

| bit 0    | VBUSVDIF: A-Device VBUS Change Indicator bit                                                                                                            |

|          | 1 = VBUS change on A-device is detected; VBUS has crossed VA_VBUS_VLD (as defined in the "USB<br>2.0 OTG Specification") <sup>(1)</sup>                 |

|          | 0 = No VBUS change on A-device is detected                                                                                                              |

| Note 1:  | VBUS threshold crossings may either be rising or falling.                                                                                               |

| Note:    | Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the                                       |

**Note:** Individual bits can only be cleared by writing a '1' to the bit position as part of a word write operation on the entire register. Using Boolean instructions or bitwise operations to write to a single bit position will cause all set bits, at the moment of the write, to become cleared.

| R/W-0        | U-0                                                                                                                                                  | R/W-0                                                | U-0                           | U-0              | U-0              | U-0                | U-0                  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------|------------------|------------------|--------------------|----------------------|--|

| MDEN         |                                                                                                                                                      | MSIDL                                                |                               |                  |                  | —                  | _                    |  |

| bit 15       |                                                                                                                                                      |                                                      |                               |                  |                  |                    | bit 8                |  |

| U-0          | R/W-0                                                                                                                                                | R/W-0                                                | R/W-0                         | U-0              | U-0              | U-0                | R/W-0                |  |

|              | MDOE                                                                                                                                                 | MDSLR                                                | MDOPOL                        |                  |                  |                    | MDBIT <sup>(1)</sup> |  |

| bit 7        |                                                                                                                                                      | MBOLI                                                |                               |                  |                  |                    | bit                  |  |

| Legend:      |                                                                                                                                                      |                                                      |                               |                  |                  |                    |                      |  |

| R = Readal   | ole bit                                                                                                                                              | W = Writable                                         | bit                           | U = Unimplen     | nented bit, read | as '0'             |                      |  |

| -n = Value a | at POR                                                                                                                                               | '1' = Bit is set                                     |                               | '0' = Bit is cle |                  | x = Bit is unknown |                      |  |

|              | 0 = DSM mo                                                                                                                                           | dule is enabled<br>dule is disable                   | d and has no o                |                  |                  |                    |                      |  |

|              |                                                                                                                                                      |                                                      |                               |                  |                  |                    |                      |  |

| bit 14       | Unimplemer                                                                                                                                           | ted: Read as '                                       | 0'                            |                  |                  |                    |                      |  |

| bit 13       | MSIDL: DSM                                                                                                                                           | 1 Stop in Idle M                                     | ode bit                       |                  |                  |                    |                      |  |

|              |                                                                                                                                                      | nues module op<br>es module oper                     |                               |                  | lle mode         |                    |                      |  |

| bit 12-7     | Unimplemer                                                                                                                                           | ted: Read as '                                       | 0'                            |                  |                  |                    |                      |  |

| bit 6        | 1 = DSM pin                                                                                                                                          | Module Pin Ou<br>output is enab<br>output is disat   | led                           | t                |                  |                    |                      |  |

| bit 5        | 1 = MDOUT                                                                                                                                            | OUT Pin Slew<br>pin slew rate li<br>pin slew rate li | miting is enable              | ed               |                  |                    |                      |  |

| bit 4        | <ul> <li>MDOPOL: DSM Output Polarity Select bit</li> <li>1 = DSM output signal is inverted</li> <li>0 = DSM output signal is not inverted</li> </ul> |                                                      |                               |                  |                  |                    |                      |  |

| bit 3-1      | Unimplemer                                                                                                                                           | ted: Read as '                                       | 0'                            |                  |                  |                    |                      |  |

| bit 0        | MDBIT: DSM                                                                                                                                           | l Manual Modul                                       | ation Input bit <sup>(1</sup> | 1)               |                  |                    |                      |  |