Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 29x12b, 2x16b; D/A 2x10b                                                   |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gc006t-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

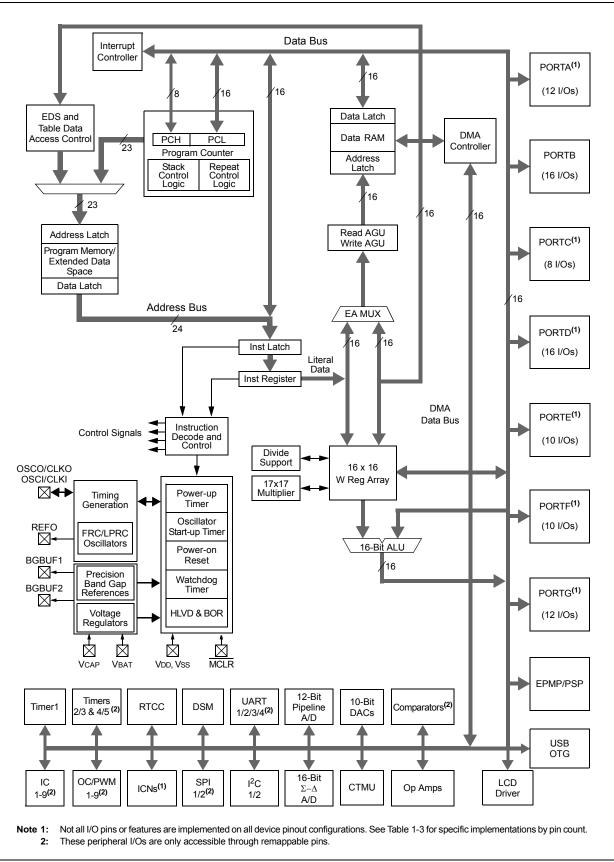

### FIGURE 1-1: PIC24FJ128GC010 FAMILY GENERAL BLOCK DIAGRAM

## TABLE 4-3: CPU CORE REGISTERS MAP

| File<br>Name | Addr | Bit 15                                                | Bit 14                       | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8       | Bit 7        | Bit 6     | Bit 5      | Bit 4       | Bit 3        | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|-------------------------------------------------------|------------------------------|--------|--------|--------|--------|---------|-------------|--------------|-----------|------------|-------------|--------------|----------|-------|-------|---------------|

| WREG0        | 0000 |                                                       |                              |        |        |        |        |         | Working R   | egister 0    |           |            |             |              |          |       |       | 0000          |

| WREG1        | 0002 |                                                       | Working Register 1           |        |        |        |        |         |             |              |           |            |             |              |          | 0000  |       |               |

| WREG2        | 0004 |                                                       |                              |        |        |        |        |         | Working R   | egister 2    |           |            |             |              |          |       |       | 0000          |

| WREG3        | 0006 |                                                       | Working Register 3           |        |        |        |        |         |             |              |           |            |             |              | 0000     |       |       |               |

| WREG4        | 0008 |                                                       |                              |        |        |        |        |         | Working R   | egister 4    |           |            |             |              |          |       |       | 0000          |

| WREG5        | 000A |                                                       |                              |        |        |        |        |         | Working R   | egister 5    |           |            |             |              |          |       |       | 0000          |

| WREG6        | 000C |                                                       |                              |        |        |        |        |         | Working R   | egister 6    |           |            |             |              |          |       |       | 0000          |

| WREG7        | 000E |                                                       |                              |        |        |        |        |         | Working R   | egister 7    |           |            |             |              |          |       |       | 0000          |

| WREG8        | 0010 |                                                       |                              |        |        |        |        |         | Working R   | egister 8    |           |            |             |              |          |       |       | 0000          |

| WREG9        | 0012 |                                                       |                              |        |        |        |        |         | Working R   | egister 9    |           |            |             |              |          |       |       | 0000          |

| WREG10       | 0014 |                                                       | Working Register 10          |        |        |        |        |         |             |              |           |            | 0000        |              |          |       |       |               |

| WREG11       | 0016 |                                                       | Working Register 11          |        |        |        |        |         |             |              |           |            | 0000        |              |          |       |       |               |

| WREG12       | 0018 |                                                       |                              |        |        |        |        |         | Working Re  | egister 12   |           |            |             |              |          |       |       | 0000          |

| WREG13       | 001A |                                                       |                              |        |        |        |        |         | Working Re  | egister 13   |           |            |             |              |          |       |       | 0000          |

| WREG14       | 001C |                                                       |                              |        |        |        |        |         | Working Re  | egister 14   |           |            |             |              |          |       |       | 0000          |

| WREG15       | 001E |                                                       |                              |        |        |        |        |         | Working Re  | egister 15   |           |            |             |              |          |       |       | 0800          |

| SPLIM        | 0020 |                                                       |                              |        |        |        |        | Stack   | Pointer Lim | it Value Reg | gister    |            |             |              |          |       |       | xxxx          |

| PCL          | 002E |                                                       |                              |        |        |        |        | Progran | n Counter L | ow Word R    | egister   |            |             |              |          |       |       | 0000          |

| PCH          | 0030 | _                                                     | _                            | _      | _      | _      | _      | _       | _           |              |           | Progran    | n Counter F | Register Hig | h Byte   |       |       | 0000          |

| DSRPAG       | 0032 | _                                                     | _                            | _      | _      | _      | _      |         |             | Exte         | nded Data | Space Rea  | d Page Ado  | dress Regis  | ter      |       |       | 0000          |

| DSWPAG       | 0034 | _                                                     | _                            | _      | _      | _      | _      | _       |             |              | Extended  | Data Space | e Write Pag | e Address    | Register |       |       | 0000          |

| RCOUNT       | 0036 |                                                       | REPEAT Loop Counter Register |        |        |        |        |         |             |              |           |            | xxxx        |              |          |       |       |               |

| SR           | 0042 | _                                                     | _                            | _      | _      | _      | _      | _       | DC          | IPL2         | IPL1      | IPL0       | RA          | Ν            | OV       | Z     | С     | 0000          |

| CORCON       | 0044 | _                                                     | _                            | —      | —      | _      | —      | —       |             | _            | —         | —          | _           | IPL3         | r        | —     | —     | 0004          |

| DISICNT      | 0052 | —     —     Disable Interrupts Counter Register     x |                              |        |        |        |        |         |             |              |           | xxxx       |             |              |          |       |       |               |

| TBLPAG       | 0054 | _                                                     | _                            | _      | _      | _      |        | —       | _           |              |           | Table Me   | emory Page  | Address R    | legister |       |       | 0000          |

Legend: - = unimplemented, read as '0'; x = unknown value on Reset; r = reserved, do not modify. Reset values are shown in hexadecimal.

### TABLE 4-7: INPUT CAPTURE REGISTER MAP

| IADEE        |      |        |                        |        |         |         |         |       |              |                |          |       |          |          |          |          |          |               |

|--------------|------|--------|------------------------|--------|---------|---------|---------|-------|--------------|----------------|----------|-------|----------|----------|----------|----------|----------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14                 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9 | Bit 8        | Bit 7          | Bit 6    | Bit 5 | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

| IC1CON1      | 0140 | _      | _                      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _            | _              | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC1CON2      | 0142 | _      | —                      | —      | _       | _       | —       | _     | IC32         | ICTRIG         | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC1BUF       | 0144 |        |                        | •      |         |         |         | I     | nput Capture | e 1 Buffer Reg | gister   |       |          |          | •        |          |          | 0000          |

| IC1TMR       | 0146 |        |                        |        |         |         |         |       | Timer Va     | lue 1 Registe  | r        |       |          |          |          |          |          | xxxx          |

| IC2CON1      | 0148 | _      | _                      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | -            | —              | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC2CON2      | 014A | _      | —                      | —      | _       |         | —       | —     | IC32         | ICTRIG         | TRIGSTAT | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC2BUF       | 014C |        |                        |        |         |         |         |       |              |                |          |       |          |          | 0000     |          |          |               |

| IC2TMR       | 014E |        | Timer Value 2 Register |        |         |         |         |       |              |                |          |       |          | xxxx     |          |          |          |               |

| IC3CON1      | 0150 | _      | _                      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _            | _              | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC3CON2      | 0152 | —      | —                      | —      | —       | —       | —       | _     | IC32         | ICTRIG         | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC3BUF       | 0154 |        |                        |        |         |         |         | I     | nput Capture | e 3 Buffer Reg | gister   |       |          |          |          |          |          | 0000          |

| IC3TMR       | 0156 |        |                        |        |         |         |         |       | Timer Va     | lue 3 Registe  | r        |       | -        |          |          |          |          | xxxx          |

| IC4CON1      | 0158 | _      | _                      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _            | _              | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC4CON2      | 015A | —      | _                      | —      | —       | —       | —       | _     | IC32         | ICTRIG         | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC4BUF       | 015C |        |                        |        |         |         |         | I     | nput Capture | e 4 Buffer Reg | gister   |       |          |          |          |          |          | 0000          |

| IC4TMR       | 015E |        |                        | 1      | 1       |         |         |       | Timer Va     | lue 4 Registe  | r        |       | 1        | -        | 1        | 1        |          | xxxx          |

| IC5CON1      | 0160 | —      | —                      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —            | —              | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC5CON2      | 0162 | —      | —                      | —      | —       | —       | —       | —     | IC32         | ICTRIG         | TRIGSTAT | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC5BUF       | 0164 |        |                        |        |         |         |         | I     | nput Capture | e 5 Buffer Reg | gister   |       |          |          |          |          |          | 0000          |

| IC5TMR       | 0166 |        |                        |        |         |         |         |       | Timer Va     | lue 5 Registe  |          |       |          |          | 1        | 1        |          | xxxx          |

| IC6CON1      | 0168 | _      | —                      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | —     | —            | —              | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC6CON2      | 016A | —      | —                      | —      | —       | —       | —       |       | IC32         | ICTRIG         | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC6BUF       | 016C |        |                        |        |         |         |         | I     |              | e 6 Buffer Reg | •        |       |          |          |          |          |          | 0000          |

| IC6TMR       | 016E |        |                        |        |         |         |         |       | Timer Va     | lue 6 Registe  | r        |       |          |          | 1        | 1        |          | xxxx          |

| IC7CON1      | 0170 | _      | _                      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | —            |                | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC7CON2      | 0172 | —      | _                      | _      | —       | —       | —       | _     | IC32         | ICTRIG         | TRIGSTAT | _     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC7BUF       | 0174 |        |                        |        |         |         |         | I     |              | e 7 Buffer Reg |          |       |          |          |          |          |          | 0000          |

| IC7TMR       | 0176 |        |                        | 1      | 1       | -       |         |       | Timer Va     | lue 7 Registe  | r        |       | r        | r        | 1        | 1        | r        | XXXX          |

| IC8CON1      | 0178 | _      | _                      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | _            |                | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC8CON2      | 018A | —      | —                      | —      | —       | —       | —       | —     | IC32         | ICTRIG         | TRIGSTAT | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC8BUF       | 018C |        |                        |        |         |         |         | I     |              | e 8 Buffer Reg | •        |       |          |          |          |          |          | 0000          |

| IC8TMR       | 018E |        |                        | 1      | 1       |         | I I     |       | Timer Va     | lue 8 Registe  |          |       | r        | r        | 1        | 1        | r        | xxxx          |

| IC9CON1      | 0180 | _      | _                      | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _     | —            | —              | ICI1     | ICI0  | ICOV     | ICBNE    | ICM2     | ICM1     | ICM0     | 0000          |

| IC9CON2      | 0182 | —      | —                      | —      | —       | —       | —       | —     | IC32         | ICTRIG         | TRIGSTAT | —     | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 | 000D          |

| IC9BUF       | 0184 |        |                        |        |         |         |         |       |              |                |          | 0000  |          |          |          |          |          |               |

| IC9TMR       | 0186 |        |                        |        |         |         |         |       | Timer Va     | lue 9 Registe  | r        |       |          |          |          |          |          | xxxx          |

Legend: — = unimplemented, read as '0'; x = unknown value on Reset. Reset values are shown in hexadecimal.

| U-0          | U-0           | U-0              | U-0             | U-0              | R/W-0           | R/W-0           | R/W-0  |

|--------------|---------------|------------------|-----------------|------------------|-----------------|-----------------|--------|

|              |               |                  | _               |                  | FSTIE           | SDA1IE          | AMP2IE |

| bit 15       |               |                  |                 |                  |                 |                 | bit 8  |

|              |               |                  |                 |                  |                 |                 |        |

| R/W-0        | U-0           | U-0              | R/W-0           | U-0              | U-0             | U-0             | U-0    |

| AMP1IE       | —             | —                | LCDIE           | _                |                 | —               |        |

| bit 7        |               |                  |                 |                  |                 |                 | bit 0  |

|              |               |                  |                 |                  |                 |                 |        |

| Legend:      |               |                  |                 |                  |                 |                 |        |

| R = Readab   |               | W = Writable     |                 |                  | mented bit, rea |                 |        |

| -n = Value a | at POR        | '1' = Bit is set | t               | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |               |                  |                 |                  |                 |                 |        |

| bit 15-11    | Unimplement   |                  |                 |                  |                 |                 |        |

| bit 10       |               |                  | rupt Enable bit | t                |                 |                 |        |

|              | 1 = Interrupt |                  |                 |                  |                 |                 |        |

| bit 9        | 0 = Interrupt | •                |                 | rupt Enable bit  |                 |                 |        |

| DIL          | 1 = Interrupt |                  |                 |                  |                 |                 |        |

|              | 0 = Interrupt |                  |                 |                  |                 |                 |        |

| bit 8        | AMP2IE: Op /  | Amp 2 Interrup   | ot Enable bit   |                  |                 |                 |        |

|              | 1 = Interrupt | request is ena   | bled            |                  |                 |                 |        |

|              | 0 = Interrupt | •                |                 |                  |                 |                 |        |

| bit 7        | AMP1IE: Op /  |                  |                 |                  |                 |                 |        |

|              | 1 = Interrupt |                  |                 |                  |                 |                 |        |

|              | 0 = Interrupt | •                |                 |                  |                 |                 |        |

| bit 6-5      |               |                  |                 |                  |                 |                 |        |

| bit 4        |               |                  | rrupt Enable bi | t                |                 |                 |        |

|              | 1 = Interrupt | •                |                 |                  |                 |                 |        |

| bit 3-0      | Unimplement   | •                |                 |                  |                 |                 |        |

|              |               |                  | •               |                  |                 |                 |        |

## REGISTER 8-19: IEC6: INTERRUPT ENABLE CONTROL REGISTER 6

### REGISTER 8-42: IPC23: INTERRUPT PRIORITY CONTROL REGISTER 23

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     |     |     |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1  | R/W-0  | R/W-0  |

|-------|--------|--------|--------|-----|--------|--------|--------|

| —     | IC9IP2 | IC9IP1 | IC9IP0 | —   | OC9IP2 | OC9IP1 | OC9IP0 |

| bit 7 |        |        |        |     |        |        | bit 0  |

| Legend:    |         |                                                                          |                       |                    |

|------------|---------|--------------------------------------------------------------------------|-----------------------|--------------------|

| R = Reada  | ble bit | W = Writable bit                                                         | U = Unimplemented bit | , read as '0'      |

| -n = Value | at POR  | '1' = Bit is set                                                         | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7   | Unimple | mented: Read as '0'                                                      |                       |                    |

| bit 6-4    |         | <b>0&gt;:</b> Input Capture Channel 9<br>errupt is Priority 7 (highest p | 1 ,                   |                    |

|         | •                                                                   |

|---------|---------------------------------------------------------------------|

|         | •                                                                   |

|         | •                                                                   |

|         | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |

| L:1.0   |                                                                     |

| bit 3   | Unimplemented: Read as '0'                                          |

| bit 2-0 | OC9IP<2:0>: Output Compare Channel 9 Interrupt Priority bits        |

|         | 111 = Interrupt is Priority 7 (highest priority interrupt)          |

|         | •                                                                   |

|         | •                                                                   |

|         | •                                                                   |

|         | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |

## 10.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of this group of PIC24 devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Power-Saving Features with Deep Sleep" (DS39727) which is available from the Microchip web site (www.microchip.com). The information in this data sheet supersedes the information in the FRM.

The PIC24FJ128GC010 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked reduces consumed power.

PIC24FJ128GC010 family devices manage power consumption with five strategies:

- Instruction-Based Power Reduction modes

- Hardware-Based Power Reduction Features

- Clock Frequency Control

- Software Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

## 10.1 Overview of Power-Saving Modes

In addition to full-power operation, otherwise known as Run mode, the PIC24FJ128GC010 family of devices offers three instruction-based power-saving modes and one hardware-based mode:

- Idle/Doze

- Sleep (Sleep and Low-Voltage Sleep)

- Deep Sleep (with and without retention)

- VBAT (with and without RTCC)

These four power modes offer different current consumption levels and have different degrees of functionality. Table 10-1 lists all of the operating modes in order of increasing power savings. Table 10-2 summarizes how the microcontroller exits the different modes. Specific information is provided in the following sections.

|                         |                                          |      |                  | Active Systems        | 5                   |                                |

|-------------------------|------------------------------------------|------|------------------|-----------------------|---------------------|--------------------------------|

| Mode                    | Entry                                    | Core | Peripherals      | Data RAM<br>Retention | RTCC <sup>(1)</sup> | DSGPR0/<br>DSGPR1<br>Retention |

| Run (default)           | N/A                                      | Y    | Y                | Y                     | Y                   | Y                              |

| Idle                    | Instruction                              | Ν    | Y                | Y                     | Y                   | Y                              |

| Sleep:                  |                                          |      |                  |                       |                     |                                |

| Sleep                   | Instruction                              | Ν    | S <sup>(2)</sup> | Y                     | Y                   | Y                              |

| Low-Voltage Sleep       | Instruction +<br>RETEN bit               | Ν    | S <sup>(2)</sup> | Y                     | Y                   | Y                              |

| Deep Sleep:             |                                          |      |                  |                       |                     |                                |

| Retention Deep<br>Sleep | Instruction +<br>DSEN bit +<br>RETEN bit | Ν    | N                | Y                     | Y                   | Y                              |

| Deep Sleep              | Instruction +<br>DSEN bit                | Ν    | Ν                | Ν                     | Y                   | Y                              |

| VBAT:                   | ·                                        |      |                  |                       |                     |                                |

| with RTCC               | Hardware                                 | Ν    | N                | Ν                     | Y                   | Y                              |

| w/o RTCC                | Hardware +<br>RTCBAT<br>Config. bit      | Ν    | N                | N                     | Ν                   | Y                              |

## TABLE 10-1: OPERATING MODES FOR PIC24FJ128GC010 FAMILY DEVICES

Note 1: If RTCC is otherwise enabled in firmware.

2: A select peripheral can operate during this mode from LPRC or some external clock.

## REGISTER 10-1: DSCON: DEEP SLEEP CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| DSEN   | —   | —   | —   | —   | —   | _   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | r-0 | R/W-0                | R/C-0, HS |

|-------|-----|-----|-----|-----|-----|----------------------|-----------|

| —     | —   | —   | —   | —   | —   | DSBOR <sup>(2)</sup> | RELEASE   |

| bit 7 |     |     |     |     |     |                      | bit 0     |

| Legend:           | C = Clearable bit | U = Unimplemented bit, read | as '0'             |

|-------------------|-------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | HS = Hardware Settable bit  | r = Reserved bit   |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 <b>DSEN:</b> Deep Sleep Enable bit |  |

|-------------------------------------------|--|

|-------------------------------------------|--|

- 1 = Enters Deep Sleep on execution of PWRSAV #0

- 0 = Enters normal Sleep on execution of PWRSAV #0

- bit 14-3 Unimplemented: Read as '0'

- bit 2 Reserved: Maintain as '0'

- bit 1 DSBOR: Deep Sleep BOR Event bit<sup>(2)</sup>

- 1 = The DSBOR was active and a BOR event was detected during Deep Sleep

- 0 = The DSBOR was not active or was active but did not detect a BOR event during Deep Sleep

### bit 0 RELEASE: I/O Pin State Release bit

- 1 = Upon waking from Deep Sleep, I/O pins maintain their states previous to Deep Sleep entry

- 0 = Releases I/O pins from their state previous to Deep Sleep entry, and allows their respective TRISx and LATx bits to control their states

- Note 1: All register bits are reset only in the case of a POR event outside of Deep Sleep mode.

- **2:** Unlike all other events, a Deep Sleep BOR event will NOT cause a wake-up from Deep Sleep; this re-arms the POR.

## REGISTER 10-2: DSWAKE: DEEP SLEEP WAKE-UP SOURCE REGISTER<sup>(1)</sup>

|              |                    |                                                                                                                                                                                                                                  | -               |                   |                  |                |               |  |  |

|--------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|----------------|---------------|--|--|

| U-0          | U-0                | U-0                                                                                                                                                                                                                              | U-0             | U-0               | U-0              | U-0            | R/W-0, HS     |  |  |

| —            | —                  | —                                                                                                                                                                                                                                | —               | —                 | —                | —              | DSINT0        |  |  |

| bit 15       |                    |                                                                                                                                                                                                                                  |                 |                   |                  |                | bit 8         |  |  |

|              |                    |                                                                                                                                                                                                                                  |                 |                   |                  |                |               |  |  |

| R/W-0, HS    | U-0                | U-0                                                                                                                                                                                                                              | R/W-0, HS       | R/W-0, HS         | R/W-0, HS        | U-0            | U-0           |  |  |

| DSFLT        | —                  | —                                                                                                                                                                                                                                | DSWDT           | DSRTCC            | DSMCLR           | —              | —             |  |  |

| bit 7        |                    |                                                                                                                                                                                                                                  |                 |                   |                  |                | bit 0         |  |  |

| Logondi      |                    |                                                                                                                                                                                                                                  | re Settable bit |                   |                  |                |               |  |  |

| Legend:      | I                  |                                                                                                                                                                                                                                  |                 |                   |                  | L = = (O)      |               |  |  |

| R = Readab   |                    | W = Writable                                                                                                                                                                                                                     |                 | •                 | nented bit, read |                |               |  |  |

| -n = Value a | t POR              | '1' = Bit is set                                                                                                                                                                                                                 |                 | '0' = Bit is clea | ared             | x = Bit is unk | nown          |  |  |

|              |                    |                                                                                                                                                                                                                                  |                 |                   |                  |                |               |  |  |

| bit 15-9     | •                  | ted: Read as '                                                                                                                                                                                                                   |                 |                   |                  |                |               |  |  |

| bit 8        |                    | ep Sleep Interru                                                                                                                                                                                                                 |                 |                   |                  |                |               |  |  |

|              |                    | on-change was<br>on-change was                                                                                                                                                                                                   |                 |                   |                  |                |               |  |  |

| bit 7        | -                  | o Sleep Fault D                                                                                                                                                                                                                  |                 | iuning Deep Sie   | eeh              |                |               |  |  |

|              |                    | occurred during                                                                                                                                                                                                                  |                 | nd some Deep      | Sleep configura  | ation settings | may have beer |  |  |

|              | 0 = No Fault       | was detected                                                                                                                                                                                                                     | during Deep Sle | еер               |                  |                |               |  |  |

| bit 6-5      | Unimplemer         | nted: Read as '                                                                                                                                                                                                                  | 0'              |                   |                  |                |               |  |  |

| bit 4        | DSWDT: Dee         | ep Sleep Watch                                                                                                                                                                                                                   | dog Timer Time  | e-out bit         |                  |                |               |  |  |

|              |                    | o Sleep Watcho<br>o Sleep Watcho                                                                                                                                                                                                 |                 |                   |                  | )              |               |  |  |

| bit 3        | DSRTCC: De         | eep Sleep Real                                                                                                                                                                                                                   | -Time Clock an  | d Calendar Ala    | ırm bit          |                |               |  |  |

|              |                    | <b>DSRTCC:</b> Deep Sleep Real-Time Clock and Calendar Alarm bit<br>1 = The Real-Time Clock and Calendar triggered an alarm during Deep Sleep<br>0 = The Real-Time Clock and Calendar did not trigger an alarm during Deep Sleep |                 |                   |                  |                |               |  |  |

| bit 2        | DSMCLR: De         | eep Sleep MCL                                                                                                                                                                                                                    | R Event bit     |                   |                  |                |               |  |  |

|              |                    | .R pin was activ<br>R pin was not a                                                                                                                                                                                              |                 |                   |                  | Deep Sleep     |               |  |  |

| bit 1-0      |                    | nted: Read as '                                                                                                                                                                                                                  |                 |                   | U U              | •••            |               |  |  |

| Note 1. A    | Il register bite e | ro alcorod when                                                                                                                                                                                                                  |                 |                   | t is set         |                |               |  |  |

Note 1: All register bits are cleared when the DSEN (DSCON<15>) bit is set.

### REGISTER 11-1: ANSA: PORTA ANALOG FUNCTION SELECTION REGISTER

|                                         | R/W-1                                                                                                                                                                                                  | U-0                                                                                                                                                                                                                                  | U-0                                                                                                                                                             | U-0                                                                                                                           | R/W-1                          | R/W-1                 | U-0   |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|-------|

| ANSA                                    | <15:14> <sup>(1)</sup>                                                                                                                                                                                 | —                                                                                                                                                                                                                                    | —                                                                                                                                                               | —                                                                                                                             | ANSA                           | <10:9> <sup>(1)</sup> | _     |

| bit 15                                  |                                                                                                                                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                 |                                                                                                                               |                                |                       | bit 8 |

|                                         |                                                                                                                                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                 |                                                                                                                               |                                |                       |       |

| R/W-1                                   | R/W-1                                                                                                                                                                                                  | R/W-1                                                                                                                                                                                                                                | R/W-1                                                                                                                                                           | U-0                                                                                                                           | U-0                            | R/W-1                 | U-0   |

|                                         | ANSA                                                                                                                                                                                                   | <7:4> <sup>(1)</sup>                                                                                                                                                                                                                 |                                                                                                                                                                 | —                                                                                                                             | _                              | ANSA1 <sup>(1)</sup>  | —     |

| bit 7                                   |                                                                                                                                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                 |                                                                                                                               |                                |                       | bit ( |

|                                         |                                                                                                                                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                 |                                                                                                                               |                                |                       |       |

| Legend:                                 |                                                                                                                                                                                                        |                                                                                                                                                                                                                                      |                                                                                                                                                                 |                                                                                                                               |                                |                       |       |

| R = Readab                              | ole bit                                                                                                                                                                                                | W = Writable                                                                                                                                                                                                                         | bit                                                                                                                                                             | U = Unimplem                                                                                                                  | nented bit, rea                | ıd as '0'             |       |

| -n = Value a                            | it POR                                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                                                                                                     |                                                                                                                                                                 | '0' = Bit is clea                                                                                                             | ared                           | x = Bit is unkno      | wn    |

|                                         | $\pm - 1 1113 001$                                                                                                                                                                                     | iliyuleu ili Alla                                                                                                                                                                                                                    | log mode; I/O                                                                                                                                                   | port read is disa                                                                                                             | abled                          |                       |       |

| bit 13-11<br>bit 10-9                   | 0 = Pin is cor<br>Unimplemen<br>ANSA<10:9><br>1 = Pin is cor                                                                                                                                           | nfigured in Digit<br>ted: Read as '(<br>: Analog Functi<br>nfigured in Anal                                                                                                                                                          | tal mode; I/O  <br>o'<br>ion Selection I<br>log mode; I/O                                                                                                       | port read is enab                                                                                                             | abled                          |                       |       |

|                                         | 0 = Pin is cor<br>Unimplemen<br>ANSA<10:9><br>1 = Pin is cor<br>0 = Pin is cor<br>Unimplemen                                                                                                           | nfigured in Digit<br>ted: Read as '(<br>: Analog Functi<br>nfigured in Anal<br>nfigured in Digit<br>ted: Read as '(                                                                                                                  | tal mode; I/O j<br>o'<br>ion Selection I<br>log mode; I/O<br>tal mode; I/O j<br>o'                                                                              | port read is enab<br>bits <sup>(1)</sup><br>port read is disa<br>port read is enab                                            | abled                          |                       |       |

| bit 10-9                                | 0 = Pin is cor<br>Unimplemen<br>ANSA<10:9><br>1 = Pin is cor<br>0 = Pin is cor<br>Unimplemen<br>ANSA<7:4>:                                                                                             | nfigured in Digit<br>ted: Read as '(<br>: Analog Functin<br>figured in Anal<br>nfigured in Digit<br>ted: Read as '(<br>Analog Functic                                                                                                | tal mode; I/O  <br>o'<br>log mode; I/O<br>tal mode; I/O  <br>o'<br>Selection bi                                                                                 | port read is enal<br>bits <sup>(1)</sup><br>port read is disa<br>port read is enal<br>its <sup>(1)</sup>                      | bled<br>abled<br>bled          |                       |       |

| bit 10-9                                | <ul> <li>0 = Pin is cor</li> <li>Unimplemen</li> <li>ANSA&lt;10:9&gt;</li> <li>1 = Pin is cor</li> <li>0 = Pin is cor</li> <li>Unimplemen</li> <li>ANSA&lt;7:4&gt;:</li> <li>1 = Pin is cor</li> </ul> | nfigured in Digit<br>ted: Read as '(<br>: Analog Functin<br>figured in Anal<br>nfigured in Digit<br>ted: Read as '(<br>Analog Functio<br>nfigured in Anal                                                                            | tal mode; I/O p<br>ion Selection I<br>log mode; I/O<br>tal mode; I/O p<br>on Selection bi<br>log mode; I/O                                                      | port read is enab<br>bits <sup>(1)</sup><br>port read is disa<br>port read is enab                                            | abled<br>abled<br>bled         |                       |       |

| bit 10-9                                | 0 = Pin is cor<br>Unimplemen<br>ANSA<10:9><br>1 = Pin is cor<br>0 = Pin is cor<br>Unimplemen<br>ANSA<7:4>:<br>1 = Pin is cor<br>0 = Pin is cor                                                         | nfigured in Digit<br>ted: Read as '(<br>: Analog Functin<br>figured in Anal<br>nfigured in Digit<br>ted: Read as '(<br>Analog Functio<br>nfigured in Anal                                                                            | tal mode; I/O p<br>ion Selection I<br>log mode; I/O<br>tal mode; I/O p<br>or Selection bi<br>log mode; I/O<br>tal mode; I/O p                                   | port read is enab<br>bits <sup>(1)</sup><br>port read is disa<br>port read is enab<br>its <sup>(1)</sup><br>port read is disa | abled<br>abled<br>bled         |                       |       |

| bit 10-9<br>bit 8<br>bit 7-4            | 0 = Pin is cor<br>Unimplemen<br>ANSA<10:9><br>1 = Pin is cor<br>0 = Pin is cor<br>Unimplemen<br>ANSA<7:4>:<br>1 = Pin is cor<br>0 = Pin is cor<br>Unimplemen                                           | nfigured in Digit<br>ted: Read as '(<br>: Analog Functin<br>figured in Anal<br>figured in Digit<br>ted: Read as '(<br>Analog Function<br>figured in Anal<br>figured in Digit                                                         | tal mode; I/O j<br>o'<br>log mode; I/O<br>tal mode; I/O j<br>o'<br>on Selection bi<br>log mode; I/O<br>tal mode; I/O j<br>o'                                    | port read is enab<br>bits <sup>(1)</sup><br>port read is disa<br>port read is enab<br>its <sup>(1)</sup><br>port read is disa | abled<br>abled<br>bled         |                       |       |

| bit 10-9<br>bit 8<br>bit 7-4<br>bit 3-2 | 0 = Pin is cor<br>Unimplemen<br>ANSA<10:9><br>1 = Pin is cor<br>0 = Pin is cor<br>Unimplemen<br>ANSA<7:4>:<br>1 = Pin is cor<br>0 = Pin is cor<br>Unimplemen<br>ANSA1: Anal<br>1 = Pin is cor          | nfigured in Digit<br>ted: Read as '(<br>: Analog Functin<br>figured in Anal<br>figured in Digit<br>ted: Read as '(<br>Analog Function<br>figured in Anal<br>figured in Digit<br>ted: Read as '(<br>og Function Se<br>figured in Anal | tal mode; I/O p<br>ion Selection I<br>log mode; I/O p<br>tal mode; I/O p<br>on Selection bit<br>log mode; I/O p<br>election bit <sup>(1)</sup><br>log mode; I/O | port read is enab<br>bits <sup>(1)</sup><br>port read is disa<br>port read is enab<br>its <sup>(1)</sup><br>port read is disa | abled<br>bled<br>abled<br>bled |                       |       |

**Note 1:** These bits are not available in 64-pin devices.

**REGISTER 11-4: ANSD: PORTD ANALOG FUNCTION SELECTION REGISTER**

|              | -             | -                                   |                 |                       |                 | -                  |       |

|--------------|---------------|-------------------------------------|-----------------|-----------------------|-----------------|--------------------|-------|

| R/W-1        | R/W-1         | R/W-1                               | R/W-1           | R/W-1                 | R/W-1           | R/W-1              | R/W-1 |

|              |               |                                     | ANSD            | <15:8> <sup>(1)</sup> |                 |                    |       |

| bit 15       |               |                                     |                 |                       |                 |                    | bit 8 |

|              |               |                                     |                 |                       |                 |                    |       |

| R/W-1        | R/W-1         | R/W-1                               | R/W-1           | R/W-1                 | R/W-1           | U-0                | R/W-1 |

|              |               | ANSE                                | )<7:2>          |                       |                 | —                  | ANSD0 |

| bit 7        |               |                                     |                 |                       |                 |                    | bit 0 |

|              |               |                                     |                 |                       |                 |                    |       |

| Legend:      |               |                                     |                 |                       |                 |                    |       |

| R = Readab   | le bit        | W = Writable                        | bit             | U = Unimplen          | nented bit, rea | d as '0'           |       |

| -n = Value a | t POR         | '1' = Bit is set                    |                 | '0' = Bit is cleared  |                 | x = Bit is unknown |       |

|              |               |                                     |                 |                       |                 |                    |       |

| bit 15-2     | ANSD<15:2     | >: Analog Funct                     | ion Selection I | bits <sup>(1)</sup>   |                 |                    |       |

|              |               | onfigured in Anal                   |                 |                       |                 |                    |       |

| bit 1        | Unimpleme     | nted: Read as '                     | כ'              |                       |                 |                    |       |

| bit 0        | ANSD0: An     | alog Function Se                    | election bit    |                       |                 |                    |       |

|              | 1 = Pin is co | onfigured in Analonfigured in Digit | og mode; I/O j  |                       |                 |                    |       |

| Note 1: T    | he ANSD<15:   | 12> bits are not a                  | available in 64 | -pin devices.         |                 |                    |       |

|              |               |                                     |                 |                       |                 |                    |       |

## **REGISTER 11-5:** ANSE: PORTE ANALOG FUNCTION SELECTION REGISTER<sup>(1)</sup>

| U-0          | U-0                | U-0               | U-0             | U-0                                   | U-0             | R/W-1           | U-0   |

|--------------|--------------------|-------------------|-----------------|---------------------------------------|-----------------|-----------------|-------|

|              | —                  | —                 | —               | —                                     | —               | ANSE9           | _     |

| bit 15       |                    |                   |                 |                                       |                 |                 | bit 8 |

|              |                    |                   |                 |                                       |                 |                 |       |

| R/W-1        | R/W-1              | R/W-1             | R/W-1           | U-0                                   | U-0             | U-0             | U-0   |

| ANSE<7:4>    |                    |                   |                 | <u> </u>                              |                 | —               | _     |

| bit 7        |                    |                   |                 |                                       |                 |                 | bit 0 |

|              |                    |                   |                 |                                       |                 |                 |       |

| Legend:      |                    |                   |                 |                                       |                 |                 |       |

| R = Readab   | le bit             | W = Writable      | bit             | U = Unimplem                          | ented bit, read | d as '0'        |       |

| -n = Value a | t POR              | '1' = Bit is set  |                 | '0' = Bit is clea                     | ared            | x = Bit is unkn | own   |

|              |                    |                   |                 |                                       |                 |                 |       |

| bit 15-10    | Unimplemen         | ted: Read as '    | כי              |                                       |                 |                 |       |

| bit 9        | ANSE9: Anal        | og Function Se    | lection bit     |                                       |                 |                 |       |

|              |                    |                   |                 | port read is disa<br>ort read is enat |                 |                 |       |

| bit 8        | Unimplemen         | ted: Read as '    | כי              |                                       |                 |                 |       |

| bit 7-4      | ANSE<7:4>:         | Analog Functio    | n Selection bit | S                                     |                 |                 |       |

|              |                    |                   |                 | port read is disa<br>ort read is enat |                 |                 |       |

| bit 3-0      | Unimplemen         | ted: Read as '    | כ'              |                                       |                 |                 |       |

| Note 1: ⊺    | his register is no | ot available in 6 | 4-pin devices.  |                                       |                 |                 |       |

**Note 1:** This register is not available in 64-pin devices.

## REGISTER 19-2: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER PROTOTYPE, CPU MODE (BD0STAT THROUGH BD63STAT)

| R/W-x  | R/W-x              | r-0 | r-0 | R/W-x | R/W-x  | R/W-x, HSC | R/W-x, HSC |

|--------|--------------------|-----|-----|-------|--------|------------|------------|

| UOWN   | DTS <sup>(1)</sup> | —   | —   | DTSEN | BSTALL | BC9        | BC8        |

| bit 15 |                    |     |     |       |        |            | bit 8      |

| R/W-x, HSC |

|------------|------------|------------|------------|------------|------------|------------|------------|

| BC7        | BC6        | BC5        | BC4        | BC3        | BC2        | BC1        | BC0        |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:           | r = Reserved bit | HSC = Hardware Setta  | HSC = Hardware Settable/Clearable bit |  |  |

|-------------------|------------------|-----------------------|---------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0'    |  |  |

| -n = Value at POR | '1' = Bit is set | 'r' = Reserved bit    | x = Bit is unknown                    |  |  |

| bit 15    | UOWN: USB Own bit                                                                                                                                                                                                                                                                                     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>0 = The microcontroller core owns the BD and its corresponding buffer; the USB module ignores all<br/>other fields in the BD</li> </ul>                                                                                                                                                      |

| bit 14    | DTS: Data Toggle Packet bit <sup>(1)</sup>                                                                                                                                                                                                                                                            |

|           | 1 = Data 1 packet                                                                                                                                                                                                                                                                                     |

|           | 0 = Data 0 packet                                                                                                                                                                                                                                                                                     |

| bit 13-12 | Reserved: Maintain as '0'                                                                                                                                                                                                                                                                             |

| bit 11    | DTSEN: Data Toggle Synchronization Enable bit                                                                                                                                                                                                                                                         |

|           | <ul> <li>1 = Data toggle synchronization is enabled; data packets with incorrect Sync value will be ignored</li> <li>0 = No data toggle synchronization is performed</li> </ul>                                                                                                                       |

| bit 10    | BSTALL: Buffer STALL Enable bit                                                                                                                                                                                                                                                                       |

|           | <ul> <li>1 = Buffer STALL is enabled; STALL handshake issued if a token is received that would use the BD in<br/>the given location (UOWN bit remains set, BD value is unchanged); corresponding EPSTALL bit<br/>will get set on any STALL handshake</li> <li>0 = Buffer STALL is disabled</li> </ul> |

| bit 9-0   | BC<9:0>: Byte Count bits                                                                                                                                                                                                                                                                              |

|           | This represents the number of bytes to be transmitted or the maximum number of bytes to be received during a transfer. Upon completion, the byte count is updated by the USB module with the actual number of bytes transmitted or received.                                                          |

| Note 1: ⊤ | his bit is ignored unless DTSEN = 1.                                                                                                                                                                                                                                                                  |

## REGISTER 19-6: U1STAT: USB STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R-0, HSC            | U-0 | U-0   |

|----------|----------|----------|----------|----------|---------------------|-----|-------|

| ENDPT3   | ENDPT2   | ENDPT1   | ENDPT0   | DIR      | PPBI <sup>(1)</sup> | _   | —     |

| bit 7    |          |          |          |          |                     |     | bit 0 |

| Legend:           | U = Unimplemented bit, read as '0' |                                       |                    |  |  |

|-------------------|------------------------------------|---------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                   | HSC = Hardware Settable/Clearable bit |                    |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                  | x = Bit is unknown |  |  |

### bit 15-8 Unimplemented: Read as '0'

| bit 7-4 | <b>ENDPT&lt;3:0&gt;:</b> Number of the Last Endpoint Activity bits (Represents the number of the BDT updated by the last USB transfer.) |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------|

|         | 1111 = Endpoint 15                                                                                                                      |

|         | 1110 = Endpoint 14                                                                                                                      |

|         | •                                                                                                                                       |

|         | •                                                                                                                                       |

|         | •                                                                                                                                       |

|         | 0001 = Endpoint 1                                                                                                                       |

|         | 0000 = Endpoint 0                                                                                                                       |

| bit 3   | DIR: Last BD Direction Indicator bit                                                                                                    |

|         | 1 = The last transaction was a transmit transfer (TX)                                                                                   |

|         | 0 = The last transaction was a receive transfer (RX)                                                                                    |

| bit 2   | PPBI: Ping-Pong BD Pointer Indicator bit <sup>(1)</sup>                                                                                 |

|         | 1 = The last transaction was to the odd BD bank                                                                                         |

|         | 0 = The last transaction was to the even BD bank                                                                                        |

| bit 1-0 | Unimplemented: Read as '0'                                                                                                              |

|         |                                                                                                                                         |

**Note 1:** This bit is only valid for endpoints with available even and odd BD registers.

NOTES:

## REGISTER 22-3: LCDPS: LCD PHASE REGISTER

| U-0           | U-0                        | U-0                                   | U-0      | U-0                              | U-0              | U-0            | U-0   |  |  |

|---------------|----------------------------|---------------------------------------|----------|----------------------------------|------------------|----------------|-------|--|--|

| _             | —                          | —                                     | _        | —                                | —                | —              | —     |  |  |