Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                 |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                               |

| Number of I/O              | 85                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 50x12b, 2x16b; D/A 2x10b                                                  |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 121-TFBGA                                                                     |

| Supplier Device Package    | 121-TFBGA (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64gc010-i-bg |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GC006

PIC24FJ128GC006

- PIC24FJ64GC010 PIC24FJ128GC010

The PIC24FJ128GC010 family expands the capabilities of the PIC24F family by adding a complete selection of advanced analog peripherals to its existing digital features. This combination, along with its ultra low-power features, Direct Memory Access (DMA) for peripherals, USB On-The-Go (OTG) and a built-in LCD controller and driver, makes this family the new standard for mixed-signal PIC<sup>®</sup> microcontrollers in one economical and power-saving package.

#### 1.1 Core Features

#### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers (DSCs). The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear Addressing of up to 12 Mbytes (program space) and 32 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- Operational performance up to 16 MIPS

#### 1.1.2 XLP POWER-SAVING TECHNOLOGY

The PIC24FJ128GC010 family of devices introduces a greatly expanded range of power-saving operating modes for the ultimate in power conservation. The new modes include:

- Retention Sleep with essential circuits being powered from a separate low-voltage regulator

- Retention Deep Sleep, a lower power mode that maintains data RAM for fast start-up

- Deep Sleep without RTCC for the lowest possible power consumption under software control

- VBAT mode (with or without RTCC) to continue limited operation from a backup battery when VDD is removed

Many of these new low-power modes also support the continuous operation of the low-power, on-chip Real-Time Clock and Calendar (RTCC), making it possible for an application to keep time while the device is otherwise asleep.

Aside from these new features, PIC24FJ128GC010 family devices also include all of the legacy power-saving features of previous PIC24F microcontrollers, such as:

- On-the-Fly Clock Switching, allowing the selection of a lower power clock during run time

- Doze Mode Operation, for maintaining peripheral clock speed while slowing the CPU clock

- Instruction-Based Power-Saving modes, for quick invocation of Idle and the many Sleep modes

# 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC24FJ128GC010 family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes

- Two External Clock modes

- A Phase-Locked Loop (PLL) frequency multiplier, which allows clock speeds of up to 32 MHz

- A Fast Internal Oscillator (FRC) nominal 8 MHz output, with multiple frequency divider options and automatic frequency self-calibration during run time

- A separate Low-Power Internal RC Oscillator (LPRC) – 31 kHz nominal, for low-power, timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

### 1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve. This extends the ability of applications to grow from the relatively simple, to the powerful and complex, while still selecting a Microchip device.

### 1.6 Other Special Features

- Peripheral Pin Select (PPS): The Peripheral Pin Select feature allows most digital peripherals to be mapped over a fixed set of digital I/O pins. Users may independently map the input and/or output of any one of the many digital peripherals to any one of the I/O pins.

- **Communications:** The PIC24FJ128GC010 family incorporates several different serial communication peripherals to handle a range of application requirements. There are two independent I<sup>2</sup>C modules that support both Master and Slave modes of operation. Devices also have, through the PPS feature, four independent UARTs with built-in IrDA<sup>®</sup> encoders/decoders and two SPI modules.

- **CTMU Interface:** In addition to their other analog features, members of the PIC24FJ128GC010 family include the CTMU interface module. This provides a convenient method for precision time measurement and pulse generation, and can serve as an interface for capacitive sensors.

- Enhanced Parallel Master/Parallel Slave Port: This module allows rapid and transparent access to the microcontroller data bus, and enables the CPU to directly address external data memory. The parallel port can function in Master or Slave mode, accommodating data widths of 4, 8 or 16 bits, and address widths of up to 23 bits in Master modes.

- Real-Time Clock and Calendar (RTCC): This module implements a full-featured clock and calendar with alarm functions in hardware, freeing up timer resources and program memory space for use of the core application.

- Data Signal Modulator (DSM): The Data Signal Modulator (DSM) allows the user to mix a digital data stream (the "modulator signal") with a carrier signal to produce a modulated output.

### 1.7 Details on Individual Family Members

Devices in the PIC24FJ128GC010 family are available in 64-pin and 100/121-pin packages. The general block diagram for all devices is shown in Figure 1-1.

The devices are differentiated from each other in six ways:

- Flash program memory (64 Kbytes for PIC24FJ64GC0XX devices and 128 Kbytes for PIC24FJ128GC0XX devices).

- Available I/O pins and ports (53 pins on 6 ports for 64-pin devices and 85 pins on 7 ports for 100/121-pin devices).

- 3. Available Interrupt-on-Change Notification (ICN) inputs (52 on 64-pin devices and 82 on 100/121-pin devices).

- 4. Available remappable pins (29 pins on 64-pin devices and 44 pins on 100/121-pin devices).

- 5. Maximum available drivable LCD pixels (248 for 64-pin devices and 472 on 100/121-pin devices.)

- Analog input channels for the Pipeline A/D Converter (29 channels for 64-pin devices and 50 channels for 100/121-pin devices).

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

A list of pin features available on the PIC24FJ128GC010 family devices, sorted by function, is shown in Table 1-3. Note that this table shows the pin location of individual peripheral features and not how they are multiplexed on the same pin. This information is provided in the pinout diagrams in the beginning of the data sheet. Multiplexed features are sorted by the priority given to a feature, with the highest priority peripheral being listed first.

#### TABLE 1-1: DEVICE FEATURES FOR THE PIC24FJ128GC010 FAMILY: 64-PIN DEVICES

| Features                                                                 | PIC24FJ64GC006                                                                                                                                                          | PIC24FJ128GC006 |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| Operating Frequency                                                      | DC – 3                                                                                                                                                                  | 2 MHz           |  |  |  |

| Program Memory (bytes)                                                   | 64K                                                                                                                                                                     | 128K            |  |  |  |

| Program Memory (instructions)                                            | 22,016                                                                                                                                                                  | 44,032          |  |  |  |

| Data Memory (bytes)                                                      | 8                                                                                                                                                                       | K               |  |  |  |

| Interrupt Sources (soft vectors/<br>NMI traps)                           | 65 (6                                                                                                                                                                   | 31/4)           |  |  |  |

| I/O Ports                                                                | Ports B, C,                                                                                                                                                             | D, E, F, G      |  |  |  |

| Total I/O Pins                                                           | 5                                                                                                                                                                       | 3               |  |  |  |

| Remappable Pins                                                          | 30 (29 I/Os,                                                                                                                                                            | 1 input only)   |  |  |  |

| Timers:                                                                  |                                                                                                                                                                         |                 |  |  |  |

| Total Number (16-bit)                                                    | 5(                                                                                                                                                                      | 1)              |  |  |  |

| 32-Bit (from paired 16-bit timers)                                       | 2                                                                                                                                                                       | 2               |  |  |  |

| Input Capture w/Timer Channels                                           | 9(                                                                                                                                                                      | 1)              |  |  |  |

| Output Compare/PWM Channels                                              | 9(                                                                                                                                                                      | 1)              |  |  |  |

| Input Change Notification Interrupt                                      | 52                                                                                                                                                                      |                 |  |  |  |

| Serial Communications:                                                   |                                                                                                                                                                         |                 |  |  |  |

| UART                                                                     | 4 <sup>(1)</sup>                                                                                                                                                        |                 |  |  |  |

| SPI (3-wire/4-wire)                                                      | 2(                                                                                                                                                                      | 1)              |  |  |  |

| I <sup>2</sup> C                                                         | 2                                                                                                                                                                       | 2               |  |  |  |

| Digital Signal Modulator                                                 | Ye                                                                                                                                                                      | 28              |  |  |  |

| Parallel Communications (EPMP/PSP)                                       | Ye                                                                                                                                                                      | 28              |  |  |  |

| JTAG Boundary Scan                                                       | Ye                                                                                                                                                                      | 28              |  |  |  |

| 12-Bit Pipeline Analog-to-Digital<br>Converter (A/D) (input channels)    | 29                                                                                                                                                                      |                 |  |  |  |

| Sigma-Delta Analog-to-Digital Converter<br>(A/D) (differential channels) | 2                                                                                                                                                                       | 2               |  |  |  |

| Digital-to-Analog Converter (DAC)                                        | 2                                                                                                                                                                       | 2               |  |  |  |

| Operational Amplifiers                                                   | 2                                                                                                                                                                       | 2               |  |  |  |

| Analog Comparators                                                       | 3                                                                                                                                                                       | }               |  |  |  |

| CTMU Interface                                                           | Ye                                                                                                                                                                      | es              |  |  |  |

| LCD Controller (available pixels)                                        | 196 (28 SE                                                                                                                                                              | G x 7 COM)      |  |  |  |

| Resets (and delays)                                                      | Core POR, VDD POR, VBAT POR, BOR, RESET Instruction<br>MCLR, WDT, Illegal Opcode, REPEAT Instruction,<br>Hardware Traps, Configuration Word Mismatch<br>(OST, PLL Lock) |                 |  |  |  |

| Instruction Set                                                          | 76 Base Instructions, Multiple Addressing Mode Variations                                                                                                               |                 |  |  |  |

| Packages                                                                 | 64-Pin TQFP and QFN                                                                                                                                                     |                 |  |  |  |

**Note 1:** Peripherals are accessible through remappable pins.

| File<br>Name | Addr | Bit 15 | Bit 14                                            | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9      | Bit 8       | Bit 7        | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|---------------------------------------------------|---------|---------|---------|---------|------------|-------------|--------------|------------|--------|--------|--------|--------|--------|--------|---------------|

| ACCONH       | 050E | _      | _                                                 | _       | _       | _       |         | _          |             | ACEN         | ACIE       | _      | _      | _      | _      | _      | _      | 0000          |

| ACCONL       | 050C | —      | _                                                 | TBLSEL5 | TBLSEL4 | TBLSEL3 | TBLSEL2 | TBLSEL1    | TBLSEL0     | COUNT7       | COUNT6     | COUNT5 | COUNT4 | COUNT3 | COUNT2 | COUNT1 | COUNT0 | 0000          |

| ACRESH       | 0512 |        |                                                   |         |         |         | A/D     | Accumulati | on High Res | ult Register | (bits<31-1 | 6>)    |        |        | •      |        |        | 0000          |

| ACRESL       | 0510 |        | A/D Accumulation Low Result Register (bits<15-0>) |         |         |         |         |            |             |              |            | 0000   |        |        |        |        |        |               |

| ADCHITH      | 0516 |        | CHH<31:16>                                        |         |         |         |         |            |             |              |            | 0000   |        |        |        |        |        |               |

| ADCHITL      | 0514 |        |                                                   |         |         |         |         |            | CHH<1       | 5:0>         |            |        |        |        |        |        |        | 0000          |

| ADTH0H       | 0526 |        |                                                   |         |         |         |         |            | TH<1        | 5:0>         |            |        |        |        |        |        |        | 0000          |

| ADTH0L       | 0524 |        |                                                   |         |         |         |         |            | TH<1        | 5:0>         |            |        |        |        |        |        |        | 0000          |

| ADTH1H       | 0542 |        |                                                   |         |         |         |         |            | TH<1        | 5:0>         |            |        |        |        |        |        |        | 0000          |

| ADTH1L       | 0540 |        | TH<15:0>                                          |         |         |         |         |            |             |              |            | 0000   |        |        |        |        |        |               |

| ADTH2H       | 055E |        | TH<15:0>                                          |         |         |         |         |            |             |              |            | 0000   |        |        |        |        |        |               |

| ADTH2L       | 055C |        | TH<15:0>                                          |         |         |         |         |            |             |              |            | 0000   |        |        |        |        |        |               |

| ADTH3H       | 040A |        | TH<15:0>                                          |         |         |         |         |            |             |              |            | 0000   |        |        |        |        |        |               |

| ADTH3L       | 0408 |        | TH<15:0>                                          |         |         |         |         |            |             |              | 0000       |        |        |        |        |        |        |               |

| ADL0MSEL3    | 052E | —      | _                                                 | _       | —       | _       | _       | —          | _           | —            | —          | _      | —      | _      | _      | MSEL<  | 49:48> | 0000          |

| ADL0MSEL2    | 052C |        |                                                   |         |         |         |         |            | MSEL<4      | 7:32>        |            |        |        |        |        |        |        | 0000          |

| ADL0MSEL1    | 052A |        |                                                   |         |         |         |         |            | MSEL<3      | 1:16>        |            |        |        |        |        |        |        | 0000          |

| ADL0MSEL0    | 0528 | MSEL15 | _                                                 | _       | _       | —       | _       |            |             | _            | _          | _      |        | _      | _      | _      | —      | 0000          |

| ADL1MSEL3    | 054A | —      | _                                                 | —       | —       | —       | _       | —          | _           | _            | —          | _      | —      | —      | —      | MSEL<  | 49:48> | 0000          |

| ADL1MSEL2    | 0548 |        |                                                   |         |         |         |         |            | MSEL<4      | 7:32>        |            |        |        |        |        |        |        | 0000          |

| ADL1MSEL1    | 0546 |        |                                                   |         |         |         |         |            | MSEL<3      | 31:16>       |            |        |        |        |        |        |        | 0000          |

| ADL1MSEL0    | 0544 | MSEL15 | _                                                 | _       | _       | —       | _       | _          | _           | _            | _          | _      | _      | —      | _      | _      | —      | 0000          |

| ADL2MSEL3    | 0566 | —      | _                                                 | —       | —       | —       | _       | —          | _           | _            | —          | _      | —      | —      | —      | MSEL<  | 49:48> | 0000          |

| ADL2MSEL2    | 0564 |        |                                                   |         |         |         |         |            | MSEL<4      | 7:32>        |            |        |        |        |        |        |        | 0000          |

| ADL2MSEL1    | 0562 |        |                                                   |         |         |         |         |            | MSEL<3      | 1:16>        |            |        |        |        |        |        |        | 0000          |

| ADL2MSEL0    | 0560 | MSEL15 | —                                                 | —       | —       | —       | _       | —          | —           | —            | —          | —      | —      | —      | —      | —      | —      | 0000          |

| ADL3MSEL3    |      | —      | —                                                 | _       | —       | —       | —       | —          | —           | —            | —          | _      | —      | —      | —      | MSEL<  | 49:48> | 0000          |

| ADL3MSEL2    | 0410 |        |                                                   |         |         |         |         |            | MSEL<4      | 7:32>        |            |        |        |        |        |        |        | 0000          |

| ADL3MSEL1    | 040E |        |                                                   |         |         |         |         |            | MSEL<3      | 31:16>       |            |        |        |        |        |        |        | 0000          |

| ADL3MSEL0    | 040C | MSEL15 | _                                                 | _       | _       | —       | _       | _          | _           | _            | —          | _      | —      | _      | _      | —      | —      | 0000          |

#### TABLE 4-25: 12-BIT PIPELINE A/D CONVERTER REGISTER MAP (CONTINUED)

Legend: — = unimplemented, read as '0'; r = reserved, do not modify. Reset values are shown in hexadecimal.

#### TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS (CONTINUED)

|                                      | Vector | IVT     | ΑΙΥΤ    | Inte     | errupt Bit Locat | ions         |

|--------------------------------------|--------|---------|---------|----------|------------------|--------------|

| Interrupt Source                     | Number | Address | Address | Flag     | Enable           | Priority     |

| Enhanced Parallel Master Port (EPMP) | 45     | 00006Eh | 00016Eh | IFS2<13> | IEC2<13>         | IPC11<6:4>   |

| Real-Time Clock and Calendar (RTCC)  | 62     | 000090h | 000190h | IFS3<14> | IEC3<14>         | IPC15<10:8>  |

| SPI1 Error                           | 9      | 000026h | 000126h | IFS0<9>  | IEC0<9>          | IPC2<6:4>    |

| SPI1 Event                           | 10     | 000028h | 000128h | IFS0<10> | IEC0<10>         | IPC2<10:8>   |

| SPI2 Error                           | 32     | 000054h | 000154h | IFS2<0>  | IEC2<0>          | IPC8<2:0>    |

| SPI2 Event                           | 33     | 000056h | 000156h | IFS2<1>  | IEC2<1>          | IPC8<6:4>    |

| Timer1                               | 3      | 00001Ah | 00011Ah | IFS0<3>  | IEC0<3>          | IPC0<14:12>  |

| Timer2                               | 7      | 000022h | 000122h | IFS0<7>  | IEC0<7>          | IPC1<14:12>  |

| Timer3                               | 8      | 000024h | 000124h | IFS0<8>  | IEC0<8>          | IPC2<2:0>    |

| Timer4                               | 27     | 00004Ah | 00014Ah | IFS1<11> | IEC1<11>         | IPC6<14:12>  |

| Timer5                               | 28     | 00004Ch | 00014Ch | IFS1<12> | IEC1<12>         | IPC7<2:0>    |

| UART1 Error                          | 65     | 000096h | 000196h | IFS4<1>  | IEC4<1>          | IPC16<6:4>   |

| UART1 Receiver                       | 11     | 00002Ah | 00012Ah | IFS0<11> | IEC0<11>         | IPC2<14:12>  |

| UART1 Transmitter                    | 12     | 00002Ch | 00012Ch | IFS0<12> | IEC0<12>         | IPC3<2:0>    |

| UART2 Error                          | 66     | 000098h | 000198h | IFS4<2>  | IEC4<2>          | IPC16<10:8>  |

| UART2 Receiver                       | 30     | 000050h | 000150h | IFS1<14> | IEC1<14>         | IPC7<10:8>   |

| UART2 Transmitter                    | 31     | 000052h | 000152h | IFS1<15> | IEC1<15>         | IPC7<14:12>  |

| UART3 Error                          | 81     | 0000B6h | 0001B6h | IFS5<1>  | IEC5<1>          | IPC20<6:4>   |

| UART3 Receiver                       | 82     | 0000B8h | 0001B8h | IFS5<2>  | IEC5<2>          | IPC20<10:8>  |

| UART3 Transmitter                    | 83     | 0000BAh | 0001BAh | IFS5<3>  | IEC5<3>          | IPC20<14:12> |

| UART4 Error                          | 87     | 0000C2h | 0001C2h | IFS5<7>  | IEC5<7>          | IPC21<14:12> |

| UART4 Receiver                       | 88     | 0000C4h | 0001C4h | IFS5<8>  | IEC5<8>          | IPC22<2:0>   |

| UART4 Transmitter                    | 89     | 0000C6h | 0001C6h | IFS5<9>  | IEC5<9>          | IPC22<6:4>   |

| USB                                  | 86     | 0000C0h | 0001C0h | IFS5<6>  | IEC5<6>          | IPC21<10:8>  |

#### REGISTER 8-42: IPC23: INTERRUPT PRIORITY CONTROL REGISTER 23

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     |     |     |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-1  | R/W-0  | R/W-0  | U-0 | R/W-1  | R/W-0  | R/W-0  |

|-------|--------|--------|--------|-----|--------|--------|--------|

| —     | IC9IP2 | IC9IP1 | IC9IP0 | —   | OC9IP2 | OC9IP1 | OC9IP0 |

| bit 7 |        |        |        |     |        |        | bit 0  |

| Legend:    |         |                                                                          |                       |                    |

|------------|---------|--------------------------------------------------------------------------|-----------------------|--------------------|

| R = Reada  | ble bit | W = Writable bit                                                         | U = Unimplemented bit | , read as '0'      |

| -n = Value | at POR  | '1' = Bit is set                                                         | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-7   | Unimple | mented: Read as '0'                                                      |                       |                    |

| bit 6-4    |         | <b>0&gt;:</b> Input Capture Channel 9<br>errupt is Priority 7 (highest p | 1 ,                   |                    |

|         | •                                                                   |

|---------|---------------------------------------------------------------------|

|         | •                                                                   |

|         | •                                                                   |

|         | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |

| 1.1.0   |                                                                     |

| bit 3   | Unimplemented: Read as '0'                                          |

| bit 2-0 | OC9IP<2:0>: Output Compare Channel 9 Interrupt Priority bits        |

|         | 111 = Interrupt is Priority 7 (highest priority interrupt)          |

|         | •                                                                   |

|         | •                                                                   |

|         | •                                                                   |

|         | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled |

| U-0                               | R/W-1                                                     | R/W-0                                                                                                 | R/W-0            | U-0                                     | U-0              | U-0      | U-0    |  |  |

|-----------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|------------------|----------|--------|--|--|

|                                   | AMP1IP2                                                   | AMP1IP1                                                                                               | AMP1IP0          |                                         | _                | _        |        |  |  |

| pit 15                            |                                                           |                                                                                                       |                  |                                         |                  |          | bit 8  |  |  |

| U-0                               | U-0                                                       | U-0                                                                                                   | U-0              | U-0                                     | R/W-1            | R/W-0    | R/W-0  |  |  |

|                                   | _                                                         | _                                                                                                     |                  | _                                       | LCDIP2           | LCDIP1   | LCDIP0 |  |  |

| pit 7                             | L                                                         |                                                                                                       |                  | •                                       |                  | 1        | bit C  |  |  |

| _egend:                           |                                                           |                                                                                                       |                  |                                         |                  |          |        |  |  |

| R = Readable bit W = Writable bit |                                                           |                                                                                                       |                  | U = Unimpler                            | nented bit, read | l as '0' |        |  |  |

| n = Value a                       | at POR                                                    | '1' = Bit is set                                                                                      |                  | '0' = Bit is cleared x = Bit is unknown |                  |          |        |  |  |

| oit 14-12<br>Dit 11-3             | 111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru | >: Op Amp 1 In<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as ' | highest priority |                                         |                  |          |        |  |  |

| bit 2-0                           |                                                           | LCD Controlle<br>pt is Priority 7 (                                                                   |                  | •                                       |                  |          |        |  |  |

#### REGISTER 11-11: RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   |     |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | INT4R5 | INT4R4 | INT4R3 | INT4R2 | INT4R1 | INT4R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 INT4R<5:0>: Assign External Interrupt 4 (INT4) to Corresponding RPn or RPIn Pin bits

#### REGISTER 11-12: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

| U-0                               | U-0 | R/W-1            | R/W-1 | R/W-1                              | R/W-1  | R/W-1              | R/W-1 |

|-----------------------------------|-----|------------------|-------|------------------------------------|--------|--------------------|-------|

|                                   |     | IC2R5            | IC2R4 | IC2R3                              | IC2R2  | IC2R1              | IC2R0 |

| bit 15                            | ·   |                  |       |                                    | -<br>- | •                  | bit 8 |

|                                   |     |                  |       |                                    |        |                    |       |

| U-0                               | U-0 | R/W-1            | R/W-1 | R/W-1                              | R/W-1  | R/W-1              | R/W-1 |

| —                                 | —   | IC1R5            | IC1R4 | IC1R3                              | IC1R2  | IC1R1              | IC1R0 |

| bit 7                             |     |                  |       |                                    | bit 0  |                    |       |

|                                   |     |                  |       |                                    |        |                    |       |

| Legend:                           |     |                  |       |                                    |        |                    |       |

| R = Readable bit W = Writable bit |     |                  | bit   | U = Unimplemented bit, read as '0' |        |                    |       |

| -n = Value at POR                 |     | '1' = Bit is set |       | '0' = Bit is cleared               |        | x = Bit is unknown |       |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 IC2R<5:0>: Assign Input Capture 2 (IC2) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IC1R<5:0>: Assign Input Capture 1 (IC1) to Corresponding RPn or RPIn Pin bits

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     | —   | —   | —   |     | IC32  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0     | R/W-0, HS | U-0 | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-1    |

|-----------|-----------|-----|----------|----------|----------|----------|----------|

| ICTRIG    | TRIGSTAT  | —   | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7 bit |           |     |          |          |          |          |          |

| Legend:      |                                                                                                                                                                                                       | HS = Hardware Settab                                                                                                                                                                                                                                                                                                                   | le bit                                                        |                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------|

| R = Readab   | ole bit                                                                                                                                                                                               | W = Writable bit                                                                                                                                                                                                                                                                                                                       | U = Unimplemented bit                                         | t, read as '0'              |

| -n = Value a | at POR                                                                                                                                                                                                | '1' = Bit is set                                                                                                                                                                                                                                                                                                                       | '0' = Bit is cleared                                          | x = Bit is unknown          |

|              |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                        |                                                               |                             |

| bit 15-9     | Unimplem                                                                                                                                                                                              | ented: Read as '0'                                                                                                                                                                                                                                                                                                                     |                                                               |                             |

| bit 8        | IC32: Case                                                                                                                                                                                            | cade Two IC Modules Enab                                                                                                                                                                                                                                                                                                               | le bit (32-bit operation)                                     |                             |

|              |                                                                                                                                                                                                       | nd ICy operate in cascade a<br>nctions independently as a                                                                                                                                                                                                                                                                              | as a 32-bit module (this bit mu<br>16-bit module              | st be set in both modules)  |

| bit 7        | ICTRIG: In                                                                                                                                                                                            | put Capture x Sync/Trigger                                                                                                                                                                                                                                                                                                             | <sup>-</sup> Select bit                                       |                             |

|              |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                        | ignated by the SYNCSELx bit<br>e designated by the SYNCSEL    |                             |

| bit 6        | TRIGSTAT                                                                                                                                                                                              | : Timer Trigger Status bit                                                                                                                                                                                                                                                                                                             |                                                               |                             |

|              |                                                                                                                                                                                                       | source has been triggered source has not been trigge                                                                                                                                                                                                                                                                                   | and is running (set in hardwar<br>red and is being held clear | re, can be set in software) |

| bit 5        | Unimplem                                                                                                                                                                                              | ented: Read as '0'                                                                                                                                                                                                                                                                                                                     |                                                               |                             |

| bit 4-0      | SYNCSEL                                                                                                                                                                                               | <4:0>: Synchronization/Trig                                                                                                                                                                                                                                                                                                            | gger Source Selection bits                                    |                             |

|              | 11010 = C<br>11001 = C<br>11000 = C<br>10111 = Ir<br>10100 = Ir<br>10010 = Ir<br>10010 = Ir<br>10000 = Ir<br>10000 = Ir<br>01111 = T<br>01100 = T<br>01101 = T<br>01011 = T<br>01011 = T<br>01001 = C | teserved<br>TMU(1)<br>ipeline A/D(1)<br>comparator 3(1)<br>comparator 2(1)<br>comparator 1(1)<br>nput Capture 8(2)<br>nput Capture 7(2)<br>nput Capture 6(2)<br>nput Capture 5(2)<br>nput Capture 3(2)<br>nput Capture 3(2)<br>nput Capture 1(2)<br>imer5<br>imer4<br>imer3<br>imer2<br>imer1<br>nput Capture 9(2)<br>Output Compare 9 |                                                               |                             |

|              | 00010 <b>=</b> C                                                                                                                                                                                      | output Compare 2                                                                                                                                                                                                                                                                                                                       |                                                               |                             |

|              |                                                                                                                                                                                                       | Output Compare 1                                                                                                                                                                                                                                                                                                                       |                                                               |                             |

|              |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                        |                                                               |                             |

00000 = Not synchronized to any other module

Note 1: Use these inputs as trigger sources only and never as sync sources.

2: Never use an IC module as its own trigger source by selecting this mode.

# 15.0 OUTPUT COMPARE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Output Compare with Dedicated Timer" (DS70005159) which is available from the Microchip web site (www.microchip.com).. The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ128GC010 family all feature seven independent output compare modules. Each of these modules offers a wide range of configuration and operating options for generating pulse trains on internal device events, and can produce Pulse-Width Modulated (PWM) waveforms for driving power applications.

Key features of the output compare module include:

- Hardware-Configurable for 32-Bit Operation in All modes by Cascading Two Adjacent modules

- Synchronous and Trigger modes of Output Compare Operation, with up to 31 User-Selectable Trigger/Sync Sources Available

- Two Separate Period Registers (a main register, OCxR, and a secondary register, OCxRS) for Greater Flexibility in Generating Pulses of Varying Widths

- Configurable for Single Pulse or Continuous Pulse Generation on an Output Event, or Continuous PWM Waveform Generation

- Up to 6 Clock Sources Available for Each module, Driving a Separate Internal 16-Bit Counter

### 15.1 General Operating Modes

#### 15.1.1 SYNCHRONOUS AND TRIGGER MODES

When the output compare module operates in a Free-Running mode, the internal 16-bit counter, OCxTMR, runs counts up continuously, wrapping around from 0xFFFF to 0x0000 on each overflow. Its period is synchronized to the selected external clock source. Compare or PWM events are generated each time a match between the internal counter and one of the Period registers occurs.

In Synchronous mode, the module begins performing its compare or PWM operation as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the module's internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the counter to run.

Free-Running mode is selected by default or any time that the SYNCSEL<4:0> bits (OCxCON2<4:0>) are set to '00000'. Synchronous or Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The OCTRIG bit (OCxCON2<7>) selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

### 15.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own set of 16-bit Timer and Duty Cycle registers. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module (OCx) provides the Least Significant 16 bits of the 32-bit register pairs and the even numbered module (OCy) provides the Most Significant 16 bits. Wrap-arounds of the OCx registers cause an increment of their corresponding OCy registers.

Cascaded operation is configured in hardware by setting the OC32 bit (OCxCON2<8>) for both modules. For more details on cascading, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Output Compare with Dedicated Timer"** (DS70005159).

### 19.1 Hardware Configuration

#### 19.1.1 DEVICE MODE

#### 19.1.1.1 D+ Pull-up Resistor

PIC24FJ128GC010 family devices have a built-in 1.5 kΩ resistor on the D+ line that is available when the microcontroller is operating in Device mode. This is used to signal an external host that the device is operating in Full-Speed Device mode. It is engaged by setting the USBEN bit (U1CON<0>) and powering up the USB module (USBPWR = 1). If the OTGEN bit (U1OTGCON<2>) is set, then the D+ pull-up is enabled through the DPPULUP bit (U1OTGCON<7>).

#### 19.1.1.2 The VBUS Pin

In order to meet the USB 2.0 specification requirement relating to the back drive voltage on the D+/D- pins, the USB module incorporates VBUS-level sensing comparators. When the comparators detect the VBUS level below the VA\_SESS\_VLD level, the hardware will automatically disable the D+ pull-up resistor described in **Section 19.1.1.1** "D+ Pull-up Resistor". This allows the device to automatically meet the back drive requirement for D+ and D-, even if the application firmware does not explicitly monitor the VBUS level. Therefore, the VBUS microcontroller pin should not be left floating in USB Device mode application designs and should normally be connected to the VBUS pin on the USB connector/cable (either directly or through a small resistance  $\leq$  100 ohms).

#### 19.1.1.3 Power Modes

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are:

- Bus Power Only mode

- · Self-Power Only mode

- Dual Power with Self-Power Dominance

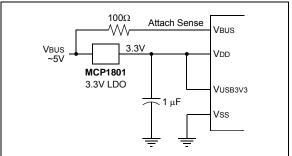

Bus Power Only mode (Figure 19-2) is effectively the simplest method. All power for the application is drawn from the USB.

To meet the inrush current requirements of the *"USB 2.0 OTG Specification"*, the total effective capacitance, appearing across VBUS and ground, must be no more than 10  $\mu$ F.

In the USB Suspend mode, devices must consume no more than 2.5 mA from the 5V VBUS line of the USB cable. During the USB Suspend mode, the D+ or Dpull-up resistor must remain active, which will consume some of the allowed suspend current.

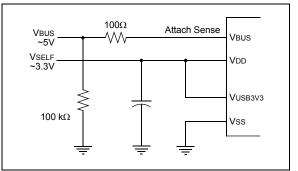

In Self-Power Only mode (Figure 19-3), the USB application provides its own power, with very little power being pulled from the USB. Note that an attach indication is added to indicate when the USB has been connected and the host is actively powering VBUS.

To meet compliance specifications, the USB module (and the D+ or D- pull-up resistor) should not be enabled until the host actively drives VBUS high. One of the 5.5V tolerant I/O pins may be used for this purpose.

The application should never source any current onto the 5V VBUS pin of the USB cable when the USB module is operated in USB Device mode.

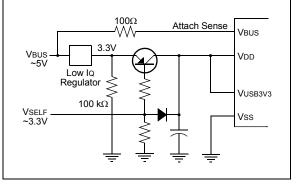

The Dual Power mode with Self-Power Dominance (Figure 19-4) allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. Dual power devices must also meet all of the special requirements for inrush current and Suspend mode current previously described, and must not enable the USB module until VBUS is driven high.

#### FIGURE 19-2: BUS POWER ONLY INTERFACE EXAMPLE

FIGURE 19-3: SELF-POWER ONLY

FIGURE 19-4:

DUAL POWER EXAMPLE

### REGISTER 19-16: U1IR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0                                                                            | U-0                                                                                                                                                        | U-0                                                                                                        | U-0             | U-0                  | U-0                 | U-0                                    | U-0               |  |  |  |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------|----------------------|---------------------|----------------------------------------|-------------------|--|--|--|

| _                                                                              | _                                                                                                                                                          |                                                                                                            | _               |                      | _                   |                                        |                   |  |  |  |

| bit 15                                                                         |                                                                                                                                                            |                                                                                                            |                 |                      |                     |                                        | bit 8             |  |  |  |

|                                                                                |                                                                                                                                                            |                                                                                                            |                 |                      |                     |                                        |                   |  |  |  |

| R/K-0, HS                                                                      | U-0                                                                                                                                                        | R/K-0, HS                                                                                                  | R/K-0, HS       | R/K-0, HS            | R/K-0, HS           | R/K-0, HS                              | R/K-0, HS         |  |  |  |

| STALLIF                                                                        |                                                                                                                                                            | RESUMEIF                                                                                                   | IDLEIF          | TRNIF                | SOFIF               | UERRIF                                 | URSTIF            |  |  |  |

| bit 7                                                                          |                                                                                                                                                            |                                                                                                            |                 |                      |                     |                                        | bit 0             |  |  |  |

|                                                                                |                                                                                                                                                            |                                                                                                            |                 |                      |                     |                                        |                   |  |  |  |

| Legend:                                                                        |                                                                                                                                                            | HS = Hardwar                                                                                               | e Settable bit  |                      |                     |                                        |                   |  |  |  |

| R = Readable bit K = Write '1' to Clear bit U = Unimplemented bit, read as '0' |                                                                                                                                                            |                                                                                                            |                 |                      |                     |                                        |                   |  |  |  |

| -n = Value at                                                                  | POR                                                                                                                                                        | '1' = Bit is set                                                                                           |                 | '0' = Bit is clea    | ared                | x = Bit is unkn                        | own               |  |  |  |

|                                                                                |                                                                                                                                                            |                                                                                                            |                 |                      |                     |                                        |                   |  |  |  |

| bit 15-8                                                                       | Unimplemer                                                                                                                                                 | nted: Read as '0                                                                                           | ,               |                      |                     |                                        |                   |  |  |  |

| bit 7                                                                          |                                                                                                                                                            | ALL Handshake                                                                                              | •               |                      |                     |                                        |                   |  |  |  |

|                                                                                |                                                                                                                                                            | handshake wa                                                                                               | s sent by the p | eripheral during     | g the handshak      | e phase of the                         | transaction in    |  |  |  |

|                                                                                | Device r                                                                                                                                                   | hode<br>- handshake has                                                                                    | s not been sen  | t                    |                     |                                        |                   |  |  |  |

| bit 6                                                                          |                                                                                                                                                            | nted: Read as '0                                                                                           |                 |                      |                     |                                        |                   |  |  |  |

| bit 5                                                                          | -                                                                                                                                                          | Resume Interru                                                                                             |                 |                      |                     |                                        |                   |  |  |  |

| Sit 0                                                                          |                                                                                                                                                            | e is observed on                                                                                           |                 | bin for 2.5 us (d    | ifferential '1' for | low speed, dif                         | ferential '0' for |  |  |  |

|                                                                                | full spee                                                                                                                                                  |                                                                                                            | r               | p= (=                |                     | ···· • • • • • • • • • • • • • • • • • |                   |  |  |  |

|                                                                                | 0 = No K-sta                                                                                                                                               | ate is observed                                                                                            |                 |                      |                     |                                        |                   |  |  |  |

| bit 4                                                                          |                                                                                                                                                            | Detect Interrupt                                                                                           |                 |                      |                     |                                        |                   |  |  |  |

|                                                                                |                                                                                                                                                            | dition is detected<br>condition is deter                                                                   | •               | e state of 3 ms      | or more)            |                                        |                   |  |  |  |

| bit 3                                                                          | TRNIF: Toke                                                                                                                                                | n Processing Co                                                                                            | omplete Interru | ıpt bit              |                     |                                        |                   |  |  |  |

|                                                                                | 1 = Processing of the current token is complete; read the U1STAT register for endpoint information                                                         |                                                                                                            |                 |                      |                     |                                        |                   |  |  |  |

|                                                                                |                                                                                                                                                            | ing of the curren<br>AT (clearing this                                                                     |                 |                      |                     | egister or load                        | the next token    |  |  |  |

| bit 2                                                                          | SOFIF: Start                                                                                                                                               | -of-Frame Toker                                                                                            | Interrupt bit   |                      |                     |                                        |                   |  |  |  |

|                                                                                | 1 = A Start-of-Frame token is received by the peripheral or the Start-of-Frame threshold is reached by                                                     |                                                                                                            |                 |                      |                     |                                        |                   |  |  |  |

|                                                                                | the host                                                                                                                                                   | -of-Frame token                                                                                            | is reasized or  | thrashold rass       | had                 |                                        |                   |  |  |  |

| hit 1                                                                          |                                                                                                                                                            |                                                                                                            |                 | the shou reac        | neu                 |                                        |                   |  |  |  |

| bit 1                                                                          | <b>UERRIF</b> : USB Error Condition Interrupt bit<br>1 = An unmasked error condition has occurred; only error states enabled in the U1EIE register can set |                                                                                                            |                 |                      |                     |                                        |                   |  |  |  |

|                                                                                | this bit                                                                                                                                                   |                                                                                                            | 100111105 0000  | fred, only end       | states enabled      |                                        | egister can set   |  |  |  |

|                                                                                | 0 = No unma                                                                                                                                                | asked error cond                                                                                           | lition has occu | irred                |                     |                                        |                   |  |  |  |

| bit 0                                                                          | URSTIF: US                                                                                                                                                 | B Reset Interrup                                                                                           | ot bit          |                      |                     |                                        |                   |  |  |  |

|                                                                                |                                                                                                                                                            | 1 = Valid USB Reset has occurred for at least 2.5 $\mu$ s; Reset state must be cleared before this bit can |                 |                      |                     |                                        |                   |  |  |  |

|                                                                                |                                                                                                                                                            | serted<br>Reset has occu                                                                                   | rrod: individuo | hite can anly        | he cleared by       | writing o '1' to t                     | he hit position   |  |  |  |

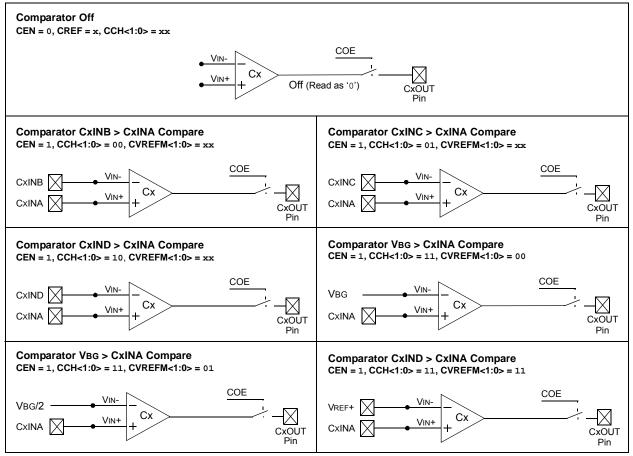

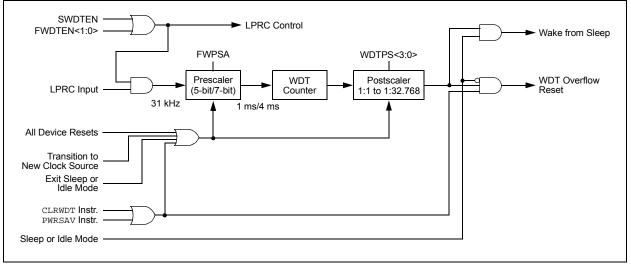

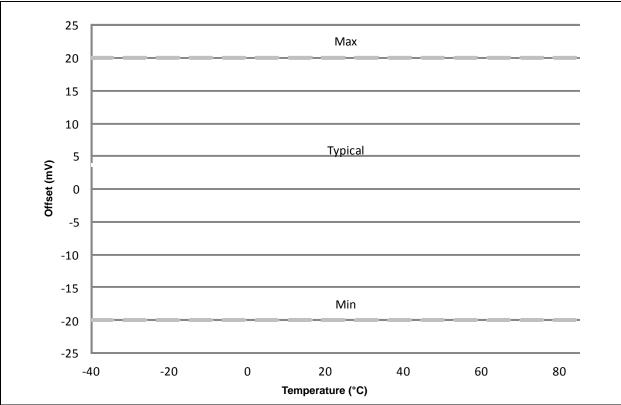

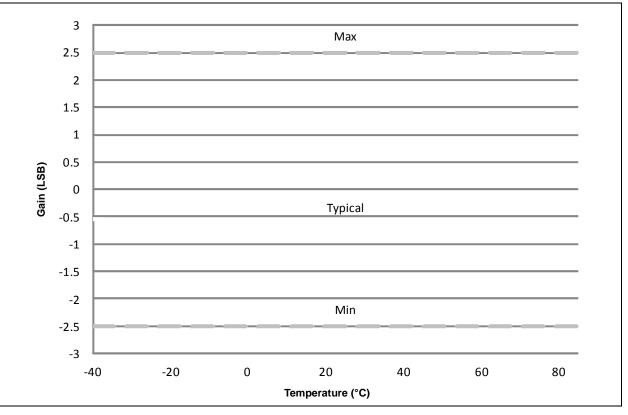

|                                                                                |                                                                                                                                                            | of a word write of                                                                                         |                 | •                    | •                   | •                                      |                   |  |  |  |