Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 11                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 512 x 8                                                               |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 4x12b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 14-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l011d4p6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

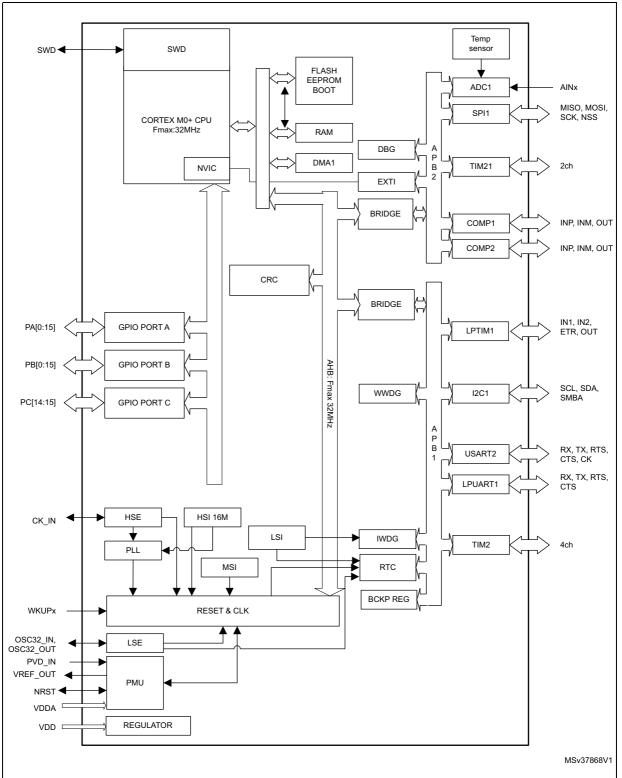

| Figure 1.  | STM32L011x3/4 block diagram                                                                                 | . 12 |

|------------|-------------------------------------------------------------------------------------------------------------|------|

| Figure 2.  | Clock tree                                                                                                  | . 23 |

| Figure 3.  | STM32L011x3/4 LQFP32 pinout                                                                                 | . 33 |

| Figure 4.  | STM32L011x3/4 UFQFPN32 pinout                                                                               | . 33 |

| Figure 5.  | STM32L011x3/4 WLCSP25 pinout                                                                                |      |

| Figure 6.  | STM32L011x3/4 UFQFPN28 pinout                                                                               | . 34 |

| Figure 7.  | STM32L011x3/4 UFQFPN20 pinout                                                                               | . 35 |

| Figure 8.  | STM32L011x3/4 TSSOP20 pinout                                                                                | . 35 |

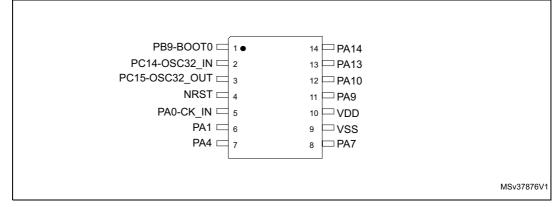

| Figure 9.  | STM32L011x3/4 TSSOP14 pinout                                                                                | . 36 |

| Figure 10. | Memory map                                                                                                  | . 43 |

| Figure 11. | Pin loading conditions.                                                                                     | . 44 |

| Figure 12. | Pin input voltage                                                                                           | . 44 |

| Figure 13. | Power supply scheme.                                                                                        |      |

| Figure 14. | Current consumption measurement scheme                                                                      |      |

| Figure 15. | IDD vs VDD, at TA= 25 °C, Run mode, code running from                                                       |      |

| U          | Flash memory, Range 2, 16 MHz HSE, 1WS.                                                                     | . 54 |

| Figure 16. | IDD vs VDD, at TA= 25 °C, Run mode, code running from                                                       |      |

| U          | Flash memory, Range 2, HSI16, 1WS                                                                           | . 54 |

| Figure 17. | IDD vs VDD, at TA= -40/25/55/ 85/105/125 °C, Low-power run mode,                                            |      |

| U          | code running from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS                                               | . 58 |

| Figure 18. | IDD vs VDD, at TA= -40/25/55/ 85/105/125 °C, Stop mode with RTC enabled                                     |      |

| 0          | and running on LSE Low drive                                                                                | . 59 |

| Figure 19. | IDD vs VDD, at TA= -40/25/55/85/105/125 °C, Stop mode with RTC disabled,                                    |      |

| 0          | all clocks OFF                                                                                              | . 59 |

| Figure 20. | High-speed external clock source AC timing diagram                                                          |      |

| Figure 21. | Low-speed external clock source AC timing diagram                                                           |      |

| Figure 22. | Typical application with a 32.768 kHz crystal                                                               |      |

| Figure 23. | HSI16 minimum and maximum value versus temperature                                                          |      |

| Figure 24. | VIH/VIL versus VDD (CMOS I/Os)                                                                              |      |

| Figure 25. | VIH/VIL versus VDD (TTL I/Os)                                                                               |      |

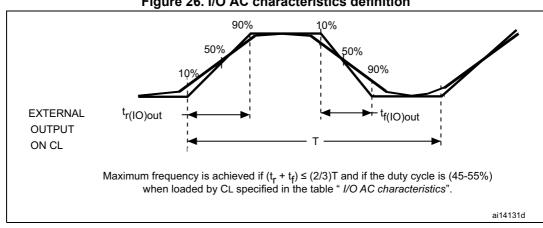

| Figure 26. | I/O AC characteristics definition                                                                           |      |

| Figure 27. | Recommended NRST pin protection                                                                             |      |

| Figure 28. | ADC accuracy characteristics                                                                                |      |

| Figure 29. | Typical connection diagram using the ADC                                                                    | . 84 |

| Figure 30. | SPI timing diagram - slave mode and CPHA = 0                                                                | . 91 |

| Figure 31. | SPI timing diagram - slave mode and CPHA = 0<br>SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup> | . 92 |

| Figure 32. | SPI timing diagram - master mode <sup>(1)</sup>                                                             | . 92 |

| Figure 33. | LQFP32, 7 x 7 mm, 32-pin low-profile quad flat package outline                                              |      |

| Figure 34. | LQFP32 recommended footprint                                                                                |      |

| Figure 35. | Example of LQFP32 marking (package top view)                                                                |      |

| Figure 36. | UFQFPN32, 5 x 5 mm, 32-pin package outline                                                                  |      |

| Figure 37. | UFQFPN32 recommended footprint                                                                              |      |

| Figure 38. | Example of UFQFPN32 marking (package top view)                                                              |      |

| Figure 39. | WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale                                    |      |

| ga. 0 00.  | package outline.                                                                                            | . 98 |

| Figure 40. | WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale                                    |      |

| ga.o .o.   | package recommended footprint                                                                               | 99   |

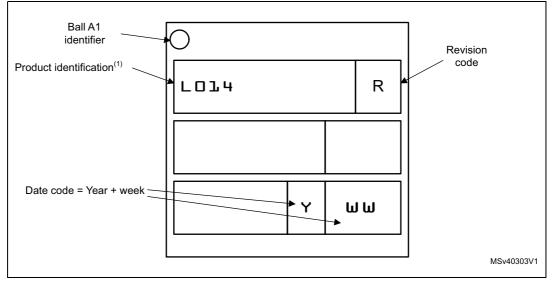

| Figure 41. | Example of WLCSP25 marking (package top view)                                                               | 100  |

|            |                                                                                                             |      |

Figure 1. STM32L011x3/4 block diagram

DocID027973 Rev 4

|                                           |            |       | Low-         | Low-           |                  | Stop                 | 5 | Standby              |

|-------------------------------------------|------------|-------|--------------|----------------|------------------|----------------------|---|----------------------|

| IPs                                       | Run/Active | Sleep | power<br>run | power<br>sleep |                  | Wakeup<br>capability |   | Wakeup<br>capability |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | ο     | 0            | 0              | 0                | 0                    | - | -                    |

| Power-on/down<br>reset (POR/PDR)          | Y          | Y     | Y            | Y              | Y                | Y                    | Y | Y                    |

| High Speed<br>Internal (HSI)              | 0          | Ο     | -            | -              | (3)              | -                    | - | -                    |

| High Speed<br>External (HSE)              | 0          | 0     | 0            | 0              | -                | -                    | - | -                    |

| Low Speed Internal<br>(LSI)               | 0          | Ο     | 0            | 0              | 0                | -                    | 0 | -                    |

| Low Speed<br>External (LSE)               | 0          | 0     | 0            | 0              | 0                | -                    | 0 | -                    |

| Multi-Speed<br>Internal (MSI)             | 0          | 0     | Y            | Y              | -                | -                    | - | -                    |

| Inter-Connect<br>Controller               | Y          | Y     | Y            | Y              | Y                | -                    | - | -                    |

| RTC                                       | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | -                    |

| RTC Tamper                                | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                    |

| Auto WakeUp<br>(AWU)                      | 0          | О     | 0            | 0              | 0                | -                    | 0 | 0                    |

| USART                                     | 0          | 0     | 0            | 0              | O <sup>(4)</sup> | 0                    | - | -                    |

| LPUART                                    | 0          | 0     | 0            | 0              | O <sup>(4)</sup> | 0                    | - | -                    |

| SPI                                       | 0          | 0     | 0            | 0              | -                |                      | - | -                    |

| 12C                                       | 0          | 0     | 0            | 0              | O <sup>(5)</sup> | 0                    | - | -                    |

| ADC                                       | 0          | 0     | -            | -              | -                | -                    | - | -                    |

| Temperature<br>sensor                     | 0          | 0     | 0            | 0              | 0                | -                    | - | -                    |

| Comparators                               | 0          | 0     | 0            | 0              | 0                | 0                    | - | -                    |

| 16-bit timers                             | 0          | 0     | 0            | 0              | -                | -                    | - | -                    |

| LPTIM                                     | 0          | 0     | 0            | 0              | 0                | 0                    | - | -                    |

| IWDG                                      | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                    |

| WWDG                                      | 0          | 0     | 0            | 0              | -                | -                    | - | -                    |

| SysTick Timer                             | 0          | 0     | 0            | 0              | -                | -                    | - | -                    |

| GPIOs                                     | 0          | 0     | 0            | 0              | 0                | 0                    | - | 2 pins               |

Table 5. Functionalities depending on the working mode (from Run/active down to standby) (continued)<sup>(1)(2)</sup>

### 3.10 Analog-to-digital converter (ADC)

A native 12-bit, extended to 16-bit through hardware oversampling, analog-to-digital converter is embedded into STM32L011x3/4 devices. It has up to 10 external channels and 2 internal channels (temperature sensor, voltage reference). Three channels, PA0, PA4 and PA5, are fast channels, while the others are standard channels.

The ADC performs conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC frequency is independent from the CPU frequency, allowing maximum sampling rate of 1.14 MSPS even with a low CPU speed. The ADC consumption is low at all frequencies (~25  $\mu$ A at 10 kSPS, ~200  $\mu$ A at 1MSPS). An auto-shutdown function guarantees that the ADC is powered off except during the active conversion phase.

The ADC can be served by the DMA controller. It can operate from a supply voltage down to 1.65 V.

The ADC features a hardware oversampler up to 256 samples, this improves the resolution to 16 bits (see AN2668).

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers.

### 3.11 Temperature sensor

The temperature sensor (T<sub>SENSE</sub>) generates a voltage V<sub>SENSE</sub> that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode (see *Table 57: Temperature sensor calibration values*).

#### 3.11.1 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (since no external voltage,  $V_{REF+}$ , is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area (see *Table 20: Embedded internal reference voltage calibration values*). It is accessible in read-only mode.

DocID027973 Rev 4

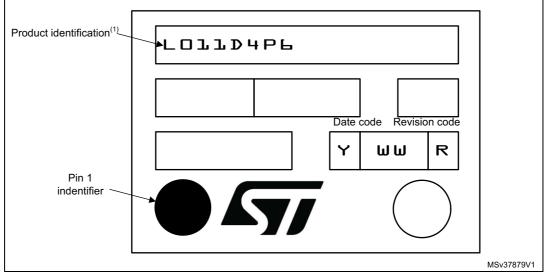

1. The above figure shows the package top view.

| Table 12. Legend/abbreviations used in the pinout | table |

|---------------------------------------------------|-------|

|---------------------------------------------------|-------|

| Nar           | ne                     | Abbreviation                                                                                      | Definition                                                                           |  |  |

|---------------|------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Pin n         | ame                    |                                                                                                   | ed in brackets below the pin name, the pin function during ne as the actual pin name |  |  |

|               |                        | S                                                                                                 | Supply pin                                                                           |  |  |

| Pin t         | уре                    | I                                                                                                 | Input only pin                                                                       |  |  |

|               |                        | I/O                                                                                               | Input / output pin                                                                   |  |  |

|               |                        | FT                                                                                                | 5 V tolerant I/O                                                                     |  |  |

|               |                        | FTf 5 V tolerant I/O, FM+ capable                                                                 |                                                                                      |  |  |

| I/O stru      | ioturo                 | TTa                                                                                               | 3.3 V tolerant I/O directly connected to the ADC                                     |  |  |

| 1/0 501       | loure                  | TC Standard 3.3V I/O                                                                              |                                                                                      |  |  |

|               |                        | B Dedicated BOOT0 pin                                                                             |                                                                                      |  |  |

|               |                        | RST                                                                                               | Bidirectional reset pin with embedded weak pull-up resistor                          |  |  |

| Not           | es                     | Unless otherwise specified by a note, all I/Os are set as floating inputs during and after reset. |                                                                                      |  |  |

| Pin functions | Alternate<br>functions | Functions selected through GPIOx_AFR registers                                                    |                                                                                      |  |  |

|               | Additional functions   | Functions directly selected/enabled through peripheral registers                                  |                                                                                      |  |  |

|         |          | Pin     | num      | ber    |                         |         |                                       |          |               |        | Pin functions                                                                                               |                                                                  |  |

|---------|----------|---------|----------|--------|-------------------------|---------|---------------------------------------|----------|---------------|--------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| TSSOP14 | UFQFPN20 | TSSOP20 | UFQFPN28 | LQFP32 | UFQFPN32 <sup>(1)</sup> | WLCSP25 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes  | Alternate functions                                                                                         | Additional<br>functions                                          |  |

| 2       | 1        | 2       | 2        | 2      | 2                       | B5      | PC14-<br>OSC32_IN                     | I/O      | FT            | -      | -                                                                                                           | OSC32_IN                                                         |  |

| 3       | 2        | 3       | 3        | 3      | 3                       | C5      | PC15-<br>OSC32_OUT                    | I/O      | тс            | -      | -                                                                                                           | OSC32_OUT                                                        |  |

| 4       | 3        | 4       | 4        | 4      | 4                       | D5      | NRST                                  | I/O      | RST           | (2)    | -                                                                                                           | -                                                                |  |

| 10      | 4        | 5       | 5        | 5      | 5                       | C4      | VDDA                                  | S        | -             | (3)(4) | -                                                                                                           | -                                                                |  |

| 5       | 5        | 6       | 6        | 6      | 6                       | E5      | PA0-CK_IN                             | I/O      | ТТа           | -      | USART2_RX,<br>LPTIM1_IN1,<br>TIM2_CH1,<br>USART2_CTS,<br>TIM2_ETR,<br>LPUART1_RX,<br>COMP1_OUT              | COMP1_INM,<br>ADC_IN0,<br>RTC_TAMP2/WKU<br>P1/CK_IN              |  |

| 6       | 6        | 7       | 7        | 7      | 7                       | B4      | PA1                                   | I/O      | FT            | -      | EVENTOUT,<br>LPTIM1_IN2,<br>TIM2_CH2,<br>I2C1_SMBA,<br>USART2_RTS,<br>TIM21_ETR,<br>LPUART1_TX              | COMP1_INP,<br>ADC_IN1                                            |  |

| -       | -        | 8       | 8        | 8      | 8                       | D4      | PA2                                   | I/O      | ТТа           | -      | TIM21_CH1,<br>TIM2_CH3,<br>USART2_TX,<br>LPUART1_TX,<br>COMP2_OUT                                           | COMP2_INM,<br>ADC_IN2,<br>RTC_TAMP3/RTC_<br>TS/RTC_OUT/WKU<br>P3 |  |

| -       | -        | 9       | 9        | 9      | 9                       | E4      | PA3                                   | I/O      | FT            | -      | TIM21_CH2,<br>TIM2_CH4,<br>USART2_RX,<br>LPUART1_RX                                                         | COMP2_INP,<br>ADC_IN3                                            |  |

| 7       | 7        | 10      | 10       | 10     | 10                      | В3      | PA4                                   | I/O      | ТТа           | -      | SPI1_NSS,<br>LPTIM1_IN1,<br>LPTIM1_ETR,<br>I2C1_SCL,<br>USART2_CK,<br>TIM2_ETR,<br>LPUART1_TX,<br>COMP2_OUT | COMP1_INM,<br>COMP2_INM,<br>ADC_IN4                              |  |

### 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 15: Voltage characteristics*, *Table 16: Current characteristics*, and *Table 17: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                                                                 | Ratings                                                                                                                         | Min                  | Мах                  | Unit |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                                                                       | V <sub>DD</sub> –V <sub>SS</sub> External main supply voltage<br>(including V <sub>DDA</sub> , V <sub>DD</sub> ) <sup>(1)</sup> |                      | 4.0                  |      |

|                                                                                                        | Input voltage on FT and FTf pins                                                                                                | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +4.0 |      |

| V <sub>IN</sub> <sup>(2)</sup>                                                                         | Input voltage on TC pins                                                                                                        | V <sub>SS</sub> -0.3 | 4.0                  | V    |

| VIN <sup>(-)</sup>                                                                                     | Input voltage on BOOT0                                                                                                          | V <sub>SS</sub>      | V <sub>DD</sub> +4.0 |      |

|                                                                                                        | Input voltage on any other pin                                                                                                  | V <sub>SS</sub> -0.3 | 4.0                  |      |

| $ \Delta V_{DD} $                                                                                      | Variations between different $V_{DDx}$ power pins                                                                               | -                    | 50                   |      |

| V <sub>DDA</sub> -V <sub>DDx</sub>                                                                     | Variations between any $V_{DDx}$ and $V_{DDA}$ power $pins^{(3)}$                                                               | -                    | 300                  | mV   |

| $ \Delta V_{SS} $                                                                                      | Variations between all different ground pins                                                                                    | -                    | 50                   |      |

| V <sub>ESD(HBM)</sub> Electrostatic discharge voltage<br>(human body model)         see Section 6.3.11 |                                                                                                                                 | ion 6.3.11           |                      |      |

| Table 15 | Voltage | characteristics |

|----------|---------|-----------------|

|----------|---------|-----------------|

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 16* for maximum allowed injected current values.

3. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and device operation. its value does not need to respect this rule.

| Symbol                               | Ratings                                                                     | Max.                 | Unit |

|--------------------------------------|-----------------------------------------------------------------------------|----------------------|------|

| $\Sigma I_{VDD}^{(2)}$               | Total current into sum of all $V_{DD}$ power lines (source) <sup>(1)</sup>  | 105                  |      |

| $\Sigma I_{VSS}^{(2)}$               | Total current out of sum of all $V_{SS}$ ground lines (sink) <sup>(1)</sup> | 105                  |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each V <sub>DD</sub> power pin (source) <sup>(1)</sup> | 100                  |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each $V_{SS}$ ground pin (sink) <sup>(1)</sup>       | 100                  |      |

|                                      | Output current sunk by any I/O and control pin except FTf pins              | 16                   |      |

| Ι <sub>ΙΟ</sub>                      | Output current sunk by FTf pins                                             | 22                   |      |

|                                      | Output current sourced by any I/O and control pin                           | -16                  |      |

| SI (3)                               | Total output current sunk by sum of all IOs and control pins <sup>(4)</sup> | 45                   | mA   |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub> <sup>(3)</sup> | Total output current sourced by sum of all IOs and control pins             | -45                  |      |

| 71                                   | Total output current sunk by sum of all IOs and control pins <sup>(2)</sup> | 90                   |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all IOs and control $pins^{(2)}$     | -90                  |      |

| 1                                    | Injected current on FT, FFf, RST and B pins                                 | -5/+0 <sup>(5)</sup> |      |

| I <sub>INJ(PIN)</sub>                | Injected current on TC pin                                                  | ± 5 <sup>(6)</sup>   | 1    |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(7)</sup>     | ± 25                 | 1    |

| Table 16. C | urrent char | acteristics |

|-------------|-------------|-------------|

|-------------|-------------|-------------|

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

- 3. These values apply only to STM32L011GxUx part number (UFQFPN28 package).

- 4. This current consumption must be correctly distributed over all I/Os and control pins. In particular, it must be located the closest possible to the couple of supply and ground, and distributed on both sides.

- Positive current injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 15* for maximum allowed input voltage values.

- A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 15: Voltage characteristics* for the maximum allowed input voltage values.

- 7. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Table 17. Thermal | characteristics |

|-------------------|-----------------|

|-------------------|-----------------|

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

| Typical consumption, V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C |                      |                                                       |                                                       |                                                       |                               |                                |

|----------------------------------------------------------------------|----------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|--------------------------------|

| Peripheral                                                           |                      | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                           |

|                                                                      | WWDG                 | 2.5                                                   | 2                                                     | 1.6                                                   | 2                             |                                |

|                                                                      | LPUART1              | 8.3                                                   | 7.2                                                   | 5.4                                                   | 7.2                           |                                |

| APB1                                                                 | I2C1                 | 11                                                    | 8.2                                                   | 6.8                                                   | 8.9                           | µA/MHz                         |

| AFDI                                                                 | LPTIM1               | 14                                                    | 11                                                    | 8.7                                                   | 11                            | (f <sub>HCLK</sub> )           |

|                                                                      | TIM2                 | 10.5                                                  | 8.5                                                   | 6.4                                                   | 8.5                           |                                |

|                                                                      | USART2               | 8.5                                                   | 6.8                                                   | 5.4                                                   | 7.1                           |                                |

|                                                                      | ADC1 <sup>(2)</sup>  | 5.0                                                   | 3.9                                                   | 3.3                                                   | 4                             | µА/МНz<br>(f <sub>HCLK</sub> ) |

|                                                                      | SPI1                 | 4.5                                                   | 3.5                                                   | 2.9                                                   | 3.6                           |                                |

| APB2                                                                 | TIM21                | 6.8                                                   | 6.1                                                   | 4.5                                                   | 5.6                           |                                |

|                                                                      | DBGMCU               | 1.7                                                   | 1.7                                                   | 1.1                                                   | 1.4                           |                                |

|                                                                      | SYSCFG/<br>COMP      | 2.5                                                   | 2.4                                                   | 1.6                                                   | 2.3                           |                                |

| Cortex-                                                              | GPIOA                | 7.6                                                   | 6.3                                                   | 4.9                                                   | 6.5                           |                                |

| M0+ core                                                             | GPIOB                | 5.1                                                   | 4.1                                                   | 3.2                                                   | 4                             | µA/MHz<br>(f <sub>HCLK</sub> ) |

| I/O port                                                             | GPIOC                | 1.1                                                   | 0.7                                                   | 0.6                                                   | 0.8                           | (Inclk)                        |

|                                                                      | CRC                  | 1.5                                                   | 1.1                                                   | 1                                                     | 1.2                           |                                |

|                                                                      | FLASH <sup>(3)</sup> | 10                                                    | 8.5                                                   | 7                                                     | 8.5                           |                                |

| AHB                                                                  | DMA1                 | 5.3                                                   | 4.2                                                   | 3.5                                                   | 4.8                           | µA/MHz<br>(f <sub>HCLK</sub> ) |

| All enabled                                                          | 1                    | 96                                                    | 80                                                    | 62                                                    | 88                            | VHULK/                         |

| PWR                                                                  |                      | 2.1                                                   | 1.9                                                   | 1.4                                                   | 1.8                           | µA/MHz<br>(f <sub>HCLK</sub> ) |

Table 32. Peripheral current consumption in run or Sleep mode<sup>(1)</sup>

Data based on differential I<sub>DD</sub> measurement between all peripherals OFF an one peripheral with clock enabled, in the following conditions: f<sub>HCLK</sub> = 32 MHz (range 1), f<sub>HCLK</sub> = 16 MHz (range 2), f<sub>HCLK</sub> = 4 MHz (range 3), f<sub>HCLK</sub> = 64kHz (Low-power run/sleep), f<sub>APB1</sub> = f<sub>HCLK</sub>, f<sub>APB2</sub> = f<sub>HCLK</sub>, default prescaler value for each peripheral. The CPU is in Sleep mode in both cases. No I/O pins toggling. Not tested in production.

2. HSI oscillator is OFF for this measure.

These values correspond to the Flash memory dynamic current consumption. The Flash memory static consumption (Flash memory ON) equals 12 μA and does not depend on the frequency. The Flash memory consumption is already taken into account in all the supply current consumption tables (Flash memory ON cases).

### Low-speed internal (LSI) RC oscillator

| Table | 39. | LSI | oscillator | characteristics |

|-------|-----|-----|------------|-----------------|

| 10010 | ••• |     | 0001110101 |                 |

| Symbol                              | Parameter                                                             | Min | Тур | Max | Unit |

|-------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                         | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \le T_{A} \le 85^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                           | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                      | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design, not tested in production.

#### Multi-speed internal (MSI) RC oscillator

| Symbol                                | Parameter                                                                                            | Condition   | Тур  | Max | Unit  |

|---------------------------------------|------------------------------------------------------------------------------------------------------|-------------|------|-----|-------|

| Symbol                                | Falameter                                                                                            | Condition   | -    | Wax | Unit  |

|                                       |                                                                                                      | MSI range 0 | 65.5 | -   |       |

|                                       |                                                                                                      | MSI range 1 | 131  | -   | kHz   |

|                                       |                                                                                                      | MSI range 2 | 262  | -   | KI IZ |

| f <sub>MSI</sub>                      | Frequency after factory calibration, done at $V_{DD}$ = 3.3 V and T <sub>A</sub> = 25 °C             | MSI range 3 | 524  | -   |       |

|                                       |                                                                                                      | MSI range 4 | 1.05 | -   |       |

|                                       |                                                                                                      | MSI range 5 | 2.1  | -   | MHz   |

|                                       |                                                                                                      | MSI range 6 | 4.2  | -   |       |

| ACC <sub>MSI</sub>                    | Frequency error after factory calibration                                                            | -           | ±0.5 | -   | %     |

| D <sub>TEMP(MSI)</sub> <sup>(1)</sup> | MSI oscillator frequency drift $0 \text{ °C} \leq T_A \leq 85 \text{ °C}$                            | -           | ±3   | -   | %     |

| D <sub>VOLT(MSI)</sub> <sup>(1)</sup> | MSI oscillator frequency drift<br>1.65 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, T <sub>A</sub> = 25 °C | -           | -    | 2.5 | %/V   |

|                                       |                                                                                                      | MSI range 0 | 0.75 | -   |       |

|                                       |                                                                                                      | MSI range 1 | 1    | -   |       |

|                                       |                                                                                                      | MSI range 2 | 1.5  | -   |       |

| I <sub>DD(MSI)</sub> <sup>(2)</sup>   | MSI oscillator power consumption                                                                     | MSI range 3 | 2.5  | -   | μA    |

|                                       |                                                                                                      | MSI range 4 | 4.5  | -   |       |

|                                       |                                                                                                      | MSI range 5 | 8    | -   |       |

|                                       |                                                                                                      | MSI range 6 | 15   | -   |       |

#### Table 40. MSI oscillator characteristics

#### 6.3.14 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub>, except when it is internally driven low (see Table 53).

Unless otherwise specified, the parameters given in Table 53 are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 18.

| Symbol                                | Parameter                                       | Conditions                                                   | Min                           | Тур                               | Max         | Unit |

|---------------------------------------|-------------------------------------------------|--------------------------------------------------------------|-------------------------------|-----------------------------------|-------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                    | -                                                            | -                             | -                                 | $0.3V_{DD}$ |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high level voltage                   | -                                                            | 0.39V <sub>DD</sub> +<br>0.59 | -                                 | -           |      |

|                                       | NRST output low level voltage                   | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V    | -                             | -                                 | 0.4         | V    |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | INKS I Output low level voltage                 | I <sub>OL</sub> = 1.5 mA<br>1.65 V < V <sub>DD</sub> < 2.7 V | -                             | -                                 | 0.4         |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage<br>hysteresis      | -                                                            | -                             | 10%V <sub>DD</sub> <sup>(2)</sup> | -           | mV   |

| R <sub>PU</sub>                       | Weak pull-up equivalent resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                            | 30                            | 45                                | 60          | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered pulse                       | -                                                            | -                             | -                                 | 50          | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup>  | NRST input not filtered pulse                   | -                                                            | 350                           | -                                 | -           | ns   |

Table 53. NRST pin characteristics

1. Guaranteed by design, not tested in production.

2. 200 mV minimum value

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is around 10%. 3.

#### 6.3.17 Comparators

| Table 59. Comparator 1 characteristics |                                                                                     |                                                                                  |                    |     |                    |           |  |  |  |

|----------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|--|--|--|

| Symbol                                 | Parameter                                                                           | Conditions                                                                       | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |  |  |  |

| $V_{DDA}$                              | Analog supply voltage                                                               | -                                                                                | 1.65               |     | 3.6                | V         |  |  |  |

| R <sub>400K</sub>                      | R <sub>400K</sub> value                                                             | -                                                                                | -                  | 400 | -                  | kΩ        |  |  |  |

| R <sub>10K</sub>                       | R <sub>10K</sub> value                                                              | -                                                                                | -                  | 10  | -                  | K77       |  |  |  |

| V <sub>IN</sub>                        | Comparator 1 input voltage range                                                    | -                                                                                | 0.6                | -   | V <sub>DDA</sub>   | V         |  |  |  |

| t <sub>START</sub>                     | Comparator startup time                                                             | -                                                                                | -                  | 7   | 10                 |           |  |  |  |

| td                                     | Propagation delay <sup>(2)</sup>                                                    | -                                                                                | -                  | 3   | 10                 | μs        |  |  |  |

| V <sub>offset</sub>                    | Comparator offset <sup>(3)</sup>                                                    | -                                                                                | -                  | ±3  | ±10                | mV        |  |  |  |

| d <sub>Voffset</sub> /dt               | Comparator offset<br>variation in worst voltage<br>stress conditions <sup>(3)</sup> | $V_{DDA} = 3.6 V$<br>$V_{IN+} = 0 V$<br>$V_{IN-} = V_{REFINT}$<br>$T_A = 25 ° C$ | 0                  | 1.5 | 10                 | mV/1000 h |  |  |  |

| I <sub>COMP1</sub>                     | Current consumption <sup>(4)</sup>                                                  | -                                                                                | -                  | 160 | 260                | nA        |  |  |  |

Table 59. Comparator 1 characteristics

1. Guaranteed by characterization, not tested in production.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

In TSSOP14 package, where V<sub>DDA</sub> pin is shared with V<sub>DD</sub> pin, I/O toggling should be minimized to reach the values given in the above table. I/O toggling with loaded I/O pins can generate ripple on V<sub>DD</sub>/V<sub>DDA</sub> and degrade the comparator performance.

4. Comparator consumption only. Internal reference voltage not included.

#### Table 60. Comparator 2 characteristics

| Symbol              | Parameter Conditions                          |                                                                                                                             | Min  | Тур | Max <sup>(1)</sup> | Unit       |

|---------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------------|

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                           | 1.65 | -   | 3.6                | V          |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                           | 0    | -   | $V_{DDA}$          | V          |

| +.                  | Comparator startup time                       | Fast mode                                                                                                                   | -    | 15  | 20                 |            |

| t <sub>START</sub>  |                                               | Slow mode                                                                                                                   | -    | 20  | 25                 |            |

| +                   | Propagation delay <sup>(2)</sup> in slow mode | $1.65 \text{ V} \leq \text{V}_{\text{DDA}} \leq 2.7 \text{ V}$                                                              | -    | 1.8 | 3.5                | μs         |

| t <sub>d slow</sub> |                                               | $2.7 \text{ V} \leq \text{V}_{\text{DDA}} \leq 3.6 \text{ V}$                                                               | -    | 2.5 | 6                  |            |

|                     | Propagation delay <sup>(2)</sup> in fast mode | $1.65 \text{ V} \leq \text{V}_{\text{DDA}} \leq 2.7 \text{ V}$                                                              | -    | 0.8 | 2                  |            |

| t <sub>d fast</sub> | Fropagation delay in fast mode                | $2.7 \text{ V} \leq \text{V}_{\text{DDA}} \leq 3.6 \text{ V}$                                                               | -    | 1.2 | 4                  |            |

| V <sub>offset</sub> | Comparator offset error <sup>(3)</sup>        |                                                                                                                             | -    | ±4  | ±20                | mV         |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $V_{DDA} = 3.3V$ $T_{A} = 0 \text{ to } 50 \circ C$ $V = V_{REFINT},$ $3/4 V_{REFINT},$ $1/2 V_{REFINT},$ $1/4 V_{REFINT}.$ | -    | 15  | 30                 | ppm<br>/°C |

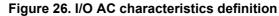

Figure 37. UFQFPN32 recommended footprint

1. Dimensions are expressed in millimeters.

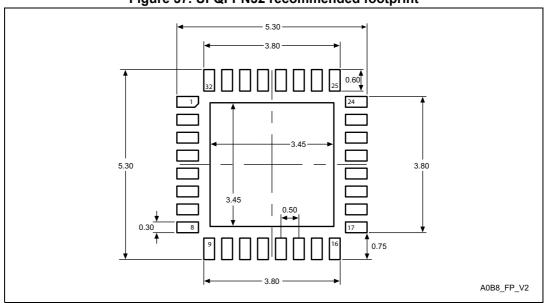

#### **Device marking**

The following figure gives an example of topside marking versus pin 1 position identifier location.

#### Figure 38. Example of UFQFPN32 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### **Device marking**

The following figure gives an example of topside marking versus ball A1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

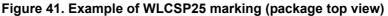

#### **UFQFPN20** device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

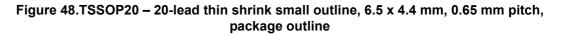

## 7.6 TSSOP20 package information

1. Drawing is not to scale.

| Table 74. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |

|-------------------------------------------------------------------------------------|

| package mechanical data                                                             |

| Cumhal |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |

| А      | -     | -           | 1.200 | -      | -                     | 0.0472 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 0.800 | 1.000       | 1.050 | 0.0315 | 0.0394                | 0.0413 |

| b      | 0.190 | -           | 0.300 | 0.0075 | -                     | 0.0118 |

| с      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |

| D      | 6.400 | 6.500       | 6.600 | 0.2520 | 0.2559                | 0.2598 |

| E      | 6.200 | 6.400       | 6.600 | 0.2441 | 0.2520                | 0.2598 |

| E1     | 4.300 | 4.400       | 4.500 | 0.1693 | 0.1732                | 0.1772 |

| е      | -     | 0.650       | -     | -      | 0.0256                | -      |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |

| Table 74. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |

|-------------------------------------------------------------------------------------|

| package mechanical data (continued)                                                 |

| Symbol | millimeters |      |       | inches <sup>(1)</sup> |      |        |

|--------|-------------|------|-------|-----------------------|------|--------|

| Symbol | Min.        | Тур. | Max.  | Min.                  | Тур. | Max.   |

| k      | 0°          | -    | 8°    | 0°                    | -    | 8°     |

| aaa    | -           | -    | 0.100 | -                     | -    | 0.0039 |

1. Values in inches are converted from mm and rounded to four decimal digits.

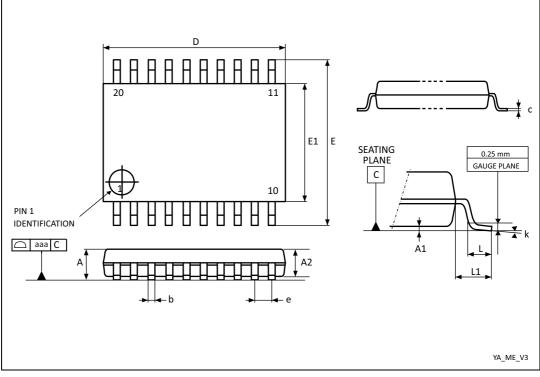

Figure 49. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, package footprint

1. Dimensions are expressed in millimeters.

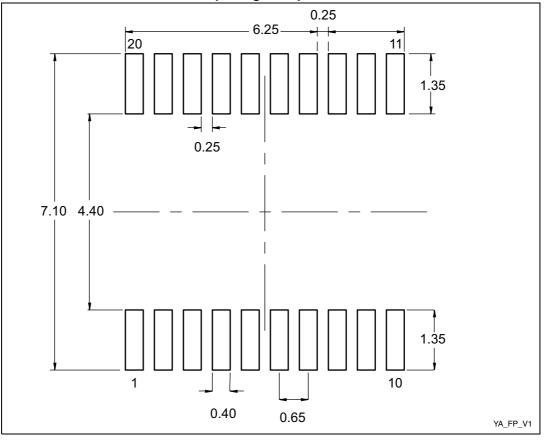

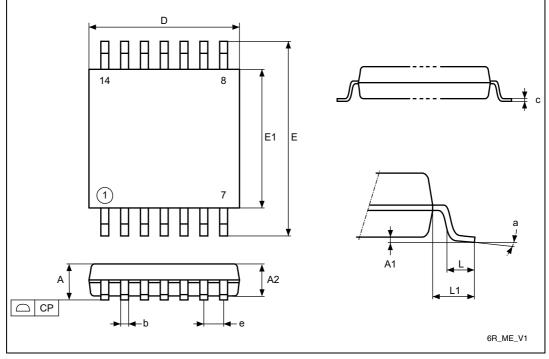

## 7.7 TSSOP14 package information

1. Drawing is not to scale.

| Table 75. TSSOP14 – 14-lead thin shrink small outline, 5.0 x 4.4 mm, 0.65 mm pitch, |

|-------------------------------------------------------------------------------------|

| package mechanical data                                                             |

| Symbol |       | millimeters |       | inches        |               |              |  |        |  |

|--------|-------|-------------|-------|---------------|---------------|--------------|--|--------|--|

|        | Min   | Тур         | Max   | Min           | Тур           | Max          |  |        |  |

| A      | -     | -           | 1.200 | -             | -             | 0.0472       |  |        |  |

| A1     | 0.050 | -           | 0.150 | 0.0020        | -             | 0.0059       |  |        |  |

| A2     | 0.800 | 1.000       | 1.050 | 0.0315        | 0.0315 0.0394 |              |  |        |  |

| b      | 0.190 | -           | 0.300 | 0.0075 -      |               | 0.300 0.0075 |  | 0.0118 |  |

| с      | 0.090 | -           | 0.200 | 0.0035 -      |               | 0.0079       |  |        |  |

| CP     | -     | -           | 0.100 |               |               | 0.0039       |  |        |  |

| D      | 4.900 | 5.000       | 5.100 | 0.1929        | 0.1929 0.1969 |              |  |        |  |

| е      | -     | 0.650       | -     | - 0.0256      |               | 0.0          |  | -      |  |

| E      | 6.200 | 6.400       | 6.600 | 0.2441 0.2520 |               | 6.600 0.2441 |  | 0.2598 |  |

| E1     | 4.300 | 4.400       | 4.500 | 0.1693        | 0.1732        | 0.1772       |  |        |  |

| L      | 0.500 | 0.600       | 0.750 | 0.0197 0.0236 |               | 0.0295       |  |        |  |

| L1     | -     | 1.000       | -     | -             | 0.0394        | -            |  |        |  |

| а      | 0°    | -           | 8°    | 0°            | -             | 8°           |  |        |  |

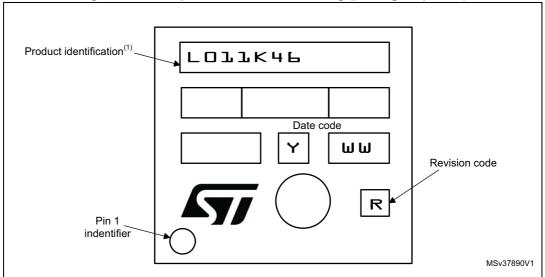

#### **TSSOP14** device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

## 7.8 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$$P_{I/O} \max = \Sigma (V_{OL} \times I_{OL}) + \Sigma ((V_{DD} - V_{OH}) \times I_{OH}),$$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 8 Part numbering

| Table 77. STM32L011x3/4 ordering information scheme |       |       |   |   |   |   |   |     |  |  |  |

|-----------------------------------------------------|-------|-------|---|---|---|---|---|-----|--|--|--|

| Example:                                            | STM32 | L 011 | К | 4 | Т | 6 | D | ххх |  |  |  |

| Device family                                       |       |       |   |   |   |   |   |     |  |  |  |

| STM32 = ARM-based 32-bit microcontroller            |       |       |   |   |   |   |   |     |  |  |  |

|                                                     |       |       |   |   |   |   |   |     |  |  |  |

| Product type                                        |       |       |   |   |   |   |   |     |  |  |  |

| L = Low power                                       |       |       |   |   |   |   |   |     |  |  |  |

| Device subfamily                                    |       |       |   |   |   |   |   |     |  |  |  |

| 011 = Access line                                   |       |       |   |   |   |   |   |     |  |  |  |

|                                                     |       |       |   |   |   |   |   |     |  |  |  |

| Pin count                                           |       |       |   |   |   |   |   |     |  |  |  |

| K = 32 pins                                         |       |       |   |   |   |   |   |     |  |  |  |

| G = 28 pins                                         |       |       |   |   |   |   |   |     |  |  |  |

| E = 25 pins                                         |       |       |   |   |   |   |   |     |  |  |  |

| F = 20 pins                                         |       |       |   |   |   |   |   |     |  |  |  |

| D = 14 pins                                         |       |       |   |   |   |   |   |     |  |  |  |

|                                                     |       |       |   |   |   |   |   |     |  |  |  |

| Flash memory size<br>3 = 8 Kbytes                   |       |       |   |   |   |   |   |     |  |  |  |

| 4 = 16 Kbytes                                       |       |       |   |   |   |   |   |     |  |  |  |

|                                                     |       |       |   |   |   |   |   |     |  |  |  |

| Package                                             |       |       |   |   |   |   |   |     |  |  |  |

| T = LQFP                                            |       |       |   |   |   |   |   |     |  |  |  |

| U = UFQFPN                                          |       |       |   |   |   |   |   |     |  |  |  |

| Y = WLCSP                                           |       |       |   |   |   |   |   |     |  |  |  |

| P = TSSOP                                           |       |       |   |   |   |   |   |     |  |  |  |

| Temperature range                                   |       |       |   |   |   |   |   |     |  |  |  |

| 6 = Industrial temperature range, -40 to 85 °C      |       |       |   |   |   |   |   |     |  |  |  |

| 7 = Industrial temperature range, -40 to 105 °C     |       |       |   |   |   |   |   |     |  |  |  |

| 3 = Industrial temperature range, -40 to 125 °C     |       |       |   |   |   |   |   |     |  |  |  |

|                                                     |       |       |   |   |   |   |   |     |  |  |  |

| Options                                             |       |       |   |   |   |   |   |     |  |  |  |

| No character = $V_{DD}$ range: 1.8 to 3.6 V and BOF |       |       |   |   |   |   |   |     |  |  |  |

| D = $V_{DD}$ range: 1.65 to 3.6 V and BOR disabled  |       |       |   |   |   |   |   |     |  |  |  |

| Packing                                             |       |       |   |   |   |   |   |     |  |  |  |

TR = tape and reel

No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.