Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 11                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 4x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                         |

| Supplier Device Package    | 14-TSSOP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l011d4p6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of figures

| Figure 1.  | STM32L011x3/4 block diagram                                                                                 | . 12 |

|------------|-------------------------------------------------------------------------------------------------------------|------|

| Figure 2.  | Clock tree                                                                                                  | . 23 |

| Figure 3.  | STM32L011x3/4 LQFP32 pinout                                                                                 | . 33 |

| Figure 4.  | STM32L011x3/4 UFQFPN32 pinout                                                                               | . 33 |

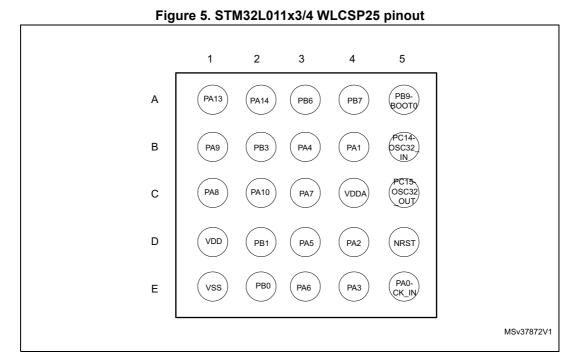

| Figure 5.  | STM32L011x3/4 WLCSP25 pinout                                                                                |      |

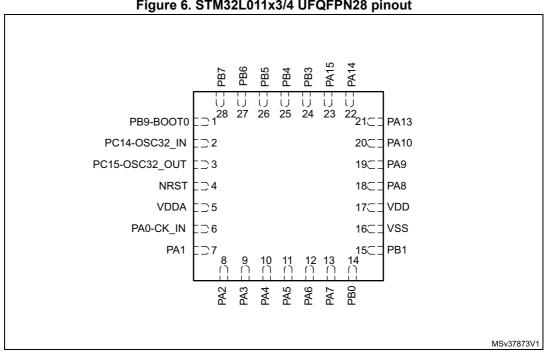

| Figure 6.  | STM32L011x3/4 UFQFPN28 pinout                                                                               | . 34 |

| Figure 7.  | STM32L011x3/4 UFQFPN20 pinout                                                                               | . 35 |

| Figure 8.  | STM32L011x3/4 TSSOP20 pinout                                                                                | . 35 |

| Figure 9.  | STM32L011x3/4 TSSOP14 pinout                                                                                | . 36 |

| Figure 10. | Memory map                                                                                                  | . 43 |

| Figure 11. | Pin loading conditions.                                                                                     | . 44 |

| Figure 12. | Pin input voltage                                                                                           | . 44 |

| Figure 13. | Power supply scheme.                                                                                        |      |

| Figure 14. | Current consumption measurement scheme                                                                      |      |

| Figure 15. | IDD vs VDD, at TA= 25 °C, Run mode, code running from                                                       |      |

| U          | Flash memory, Range 2, 16 MHz HSE, 1WS.                                                                     | . 54 |

| Figure 16. | IDD vs VDD, at TA= 25 °C, Run mode, code running from                                                       |      |

| U          | Flash memory, Range 2, HSI16, 1WS                                                                           | . 54 |

| Figure 17. | IDD vs VDD, at TA= -40/25/55/ 85/105/125 °C, Low-power run mode,                                            |      |

| U          | code running from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS                                               | . 58 |

| Figure 18. | IDD vs VDD, at TA= -40/25/55/ 85/105/125 °C, Stop mode with RTC enabled                                     |      |

| 0          | and running on LSE Low drive                                                                                | . 59 |

| Figure 19. | IDD vs VDD, at TA= -40/25/55/85/105/125 °C, Stop mode with RTC disabled,                                    |      |

| 0          | all clocks OFF                                                                                              | . 59 |

| Figure 20. | High-speed external clock source AC timing diagram                                                          |      |

| Figure 21. | Low-speed external clock source AC timing diagram                                                           |      |

| Figure 22. | Typical application with a 32.768 kHz crystal                                                               |      |

| Figure 23. | HSI16 minimum and maximum value versus temperature                                                          |      |

| Figure 24. | VIH/VIL versus VDD (CMOS I/Os)                                                                              |      |

| Figure 25. | VIH/VIL versus VDD (TTL I/Os)                                                                               |      |

| Figure 26. | I/O AC characteristics definition                                                                           |      |

| Figure 27. | Recommended NRST pin protection                                                                             |      |

| Figure 28. | ADC accuracy characteristics                                                                                |      |

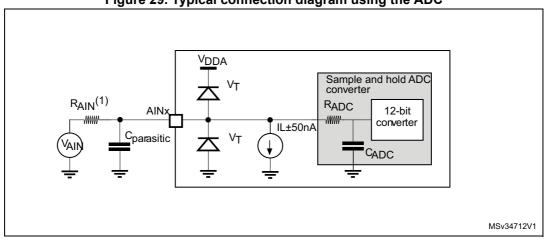

| Figure 29. | Typical connection diagram using the ADC                                                                    | . 84 |

| Figure 30. | SPI timing diagram - slave mode and CPHA = 0                                                                | . 91 |

| Figure 31. | SPI timing diagram - slave mode and CPHA = 0<br>SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup> | . 92 |

| Figure 32. | SPI timing diagram - master mode <sup>(1)</sup>                                                             | . 92 |

| Figure 33. | LQFP32, 7 x 7 mm, 32-pin low-profile quad flat package outline                                              |      |

| Figure 34. | LQFP32 recommended footprint                                                                                |      |

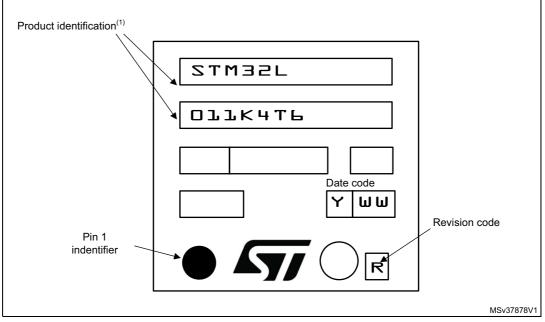

| Figure 35. | Example of LQFP32 marking (package top view)                                                                |      |

| Figure 36. | UFQFPN32, 5 x 5 mm, 32-pin package outline                                                                  |      |

| Figure 37. | UFQFPN32 recommended footprint                                                                              |      |

| Figure 38. | Example of UFQFPN32 marking (package top view)                                                              |      |

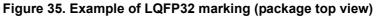

| Figure 39. | WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale                                    |      |

| ga. 0 00.  | package outline.                                                                                            | . 98 |

| Figure 40. | WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale                                    |      |

| ga.o .o.   | package recommended footprint                                                                               | 99   |

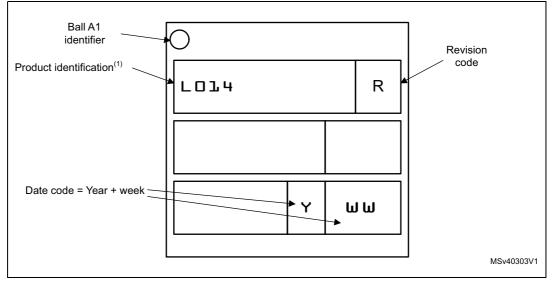

| Figure 41. | Example of WLCSP25 marking (package top view)                                                               | 100  |

|            |                                                                                                             |      |

#### Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L011x3/4 embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.4 Reset and supply management

#### 3.4.1 Power supply schemes

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively. On TSSOP14 package, V<sub>DDA</sub> is internally connected to V<sub>DD</sub>.

#### 3.4.2 Power supply supervisor

The devices feature an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

Two versions are available:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the VDD min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

DocID027973 Rev 4

## 3.15.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock, and can wake up the system from Stop mode, using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

## 3.15.4 Serial peripheral interface (SPI)

The SPI is able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The SPI can be served by the DMA controller.

Refer to *Table 11* for the supported modes and features of SPI interface.

| SPI features <sup>(1)</sup> | SPI1 |

|-----------------------------|------|

| Hardware CRC calculation    | Х    |

| I2S mode                    | -    |

| TI mode                     | Х    |

## Table 11. SPI implementation

1. X = supported.

## 3.16 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

1. The above figure shows the package top view.

Figure 6. STM32L011x3/4 UFQFPN28 pinout

1. The above figure shows the package top view.

| Pin          |  |

|--------------|--|

| descriptions |  |

|              |  |

|        | Table 14. Alternate functions (continued) |                                               |                     |                                                |                         |                                      |              |                        |         |

|--------|-------------------------------------------|-----------------------------------------------|---------------------|------------------------------------------------|-------------------------|--------------------------------------|--------------|------------------------|---------|

|        |                                           | AF0                                           | AF1                 | AF2                                            | AF3                     | AF4                                  | AF5          | AF6                    | AF7     |

| Po     | rts                                       | SPI1/USART2/<br>TIM21/<br>EVENTOUT/<br>SYS_AF | SPI1/I2C1/<br>LPTIM | LPUART1/<br>LPTIM/TIM2/<br>EVENTOUT/<br>SYS_AF | I2C1/LPTIM/<br>EVENTOUT | I2C1/USART2/L<br>PUART1/<br>EVENTOUT | SPI1/TIM2/21 | LPUART1/EVE<br>VENTOUT | COMP1/2 |

|        | PB0                                       | EVENTOUT                                      | SPI1_MISO           | TIM2_CH2                                       | -                       | USART2_RTS                           | TIM2_CH3     | -                      | -       |

|        | PB1                                       | USART2_CK                                     | SPI1_MOSI           | LPTIM1_IN1                                     | -                       | LPUART1_RTS                          | TIM2_CH4     | -                      | -       |

|        | PB2                                       | -                                             | -                   | LPTIM1_OUT                                     | -                       | -                                    | -            | -                      | -       |

|        | PB3                                       | SPI1_SCK                                      | -                   | TIM2_CH2                                       | -                       | EVENTOUT                             | -            | -                      | -       |

| Port B | PB4                                       | SPI1_MISO                                     | -                   | EVENTOUT                                       | -                       | -                                    | -            | -                      | -       |

| TOILD  | PB5                                       | SPI1_MOSI                                     | -                   | LPTIM1_IN1                                     | I2C1_SMBA               | -                                    | TIM21_CH1    | -                      | -       |

|        | PB6                                       | USART2_TX                                     | I2C1_SCL            | LPTIM1_ETR                                     | -                       | -                                    | TIM2_CH3     | LPUART1_TX             | -       |

|        | PB7                                       | USART2_RX                                     | I2C1_SDA            | LPTIM1_IN2                                     | -                       | -                                    | TIM2_CH4     | LPUART1_RX             | -       |

|        | PB8                                       | USART2_TX                                     | -                   | EVENTOUT                                       | -                       | I2C1_SCL                             | SPI1_NSS     | -                      | -       |

|        | PB9                                       | -                                             | -                   | -                                              | -                       | -                                    | -            | -                      | -       |

| Port C | PC14                                      | -                                             | -                   | -                                              | -                       | -                                    | -            | -                      | -       |

|        | PC15                                      | -                                             | -                   | -                                              | -                       | _                                    | -            | -                      | -       |

42/115

| Symbol            | Parameter                     | Conditions                                | Min  | Тур  | Max  | Unit |

|-------------------|-------------------------------|-------------------------------------------|------|------|------|------|

| M                 | Brown-out reset threshold 3   | Falling edge                              | 2.45 | 2.55 | 2.6  |      |

| V <sub>BOR3</sub> | Brown-out reset threshold 5   | Rising edge                               | 2.54 | 2.66 | 2.7  |      |

| M.                | Brown-out reset threshold 4   | Falling edge                              | 2.68 | 2.8  | 2.85 |      |

| V <sub>BOR4</sub> | Brown-out reset threshold 4   | Rising edge                               | 2.78 | 2.9  | 2.95 |      |

| V                 | Programmable voltage detector | Falling edge                              | 1.8  | 1.85 | 1.88 |      |

| V <sub>PVD0</sub> | threshold 0                   | Rising edge                               | 1.88 | 1.94 | 1.99 |      |

| V                 | PVD threshold 1               | Falling edge                              | 1.98 | 2.04 | 2.09 |      |

| V <sub>PVD1</sub> |                               | Rising edge                               | 2.08 | 2.14 | 2.18 |      |

| V                 | PVD threshold 2               | Falling edge                              | 2.20 | 2.24 | 2.28 | v    |

| V <sub>PVD2</sub> |                               | Rising edge                               | 2.28 | 2.34 | 2.38 | v    |

|                   | PVD threshold 3               | Falling edge                              | 2.39 | 2.44 | 2.48 |      |

| V <sub>PVD3</sub> |                               | Rising edge                               | 2.47 | 2.54 | 2.58 |      |

| V                 | PVD threshold 4               | Falling edge                              | 2.57 | 2.64 | 2.69 |      |

| V <sub>PVD4</sub> |                               | Rising edge                               | 2.68 | 2.74 | 2.79 |      |

| V                 | PVD threshold 5               | Falling edge                              | 2.77 | 2.83 | 2.88 |      |

| V <sub>PVD5</sub> |                               | Rising edge                               | 2.87 | 2.94 | 2.99 |      |

| V                 | PVD threshold 6               | Falling edge                              | 2.97 | 3.05 | 3.09 |      |

| V <sub>PVD6</sub> |                               | Rising edge                               | 3.08 | 3.15 | 3.20 |      |

|                   |                               | BOR0 threshold                            | -    | 40   | -    |      |

| V <sub>hyst</sub> | Hysteresis voltage            | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 19. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results, not tested in production.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

| Symbol               | Parameter                                                                          | Conc                                                           | litions                                              | f <sub>HCLK</sub> | Тур   | Max <sup>(1)</sup> | Unit |

|----------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------|-------------------|-------|--------------------|------|

|                      |                                                                                    |                                                                | Range 3,                                             | 1 MHz             | 115   | 140                |      |

|                      |                                                                                    |                                                                | V <sub>CORE</sub> =1.2 V,                            | 2 MHz             | 205   | 240                | μA   |

|                      |                                                                                    |                                                                | VOS[1:0]=11                                          | 4 MHz             | 385   | 420                |      |

|                      |                                                                                    | f <sub>HSE</sub> = f <sub>HCLK</sub> up to 16<br>MHz, included | Range 2,                                             | 4 MHz             | 0.48  | 0.55               |      |

|                      |                                                                                    | $f_{HSE} = f_{HCLK}/2$ above                                   | V <sub>CORE</sub> =1.5 ,V,                           | 8 MHz             | 0.935 | 1.1                |      |

| I <sub>DD</sub> (Run | Supply current in<br>Run mode, code<br>executed from<br>RAM, Flash<br>switched OFF | 16 MHz<br>(PLL ON) <sup>(2)</sup>                              | VOS[1:0]=10                                          | 16 MHz            | 1.8   | 2                  | mA   |

|                      |                                                                                    |                                                                | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 8 MHz             | 1.1   | 1.4                |      |

|                      |                                                                                    |                                                                |                                                      | 16 MHz            | 2.1   | 2.5                |      |

| from<br>RAM)         |                                                                                    |                                                                |                                                      | 32 MHz            | 4.5   | 4.9                |      |

|                      |                                                                                    | MSI clock                                                      | Range 3,<br>V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11 | 65 kHz            | 22    | 38                 |      |

|                      |                                                                                    |                                                                |                                                      | 524 kHz           | 67    | 91                 | μA   |

|                      |                                                                                    |                                                                |                                                      | 4.2 MHz           | 415   | 450                |      |

|                      |                                                                                    | HSI16 clock source<br>(16 MHz)                                 | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10 | 16 MHz            | 1.95  | 2.2                |      |

|                      |                                                                                    |                                                                | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 4.7   | 5.2                | mA   |

#### Table 24. Current consumption in Run mode, code with data processing running from RAM

1. Guaranteed by characterization results at 125 °C, not tested in production, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

# Table 25. Current consumption in Run mode vs code type,code with data processing running from RAM<sup>(1)</sup>

| Symbol       | Parameter                                                | Conditions                                                                      |                                                      |                                                     | f <sub>HCLK</sub> | Тур       | Unit |     |

|--------------|----------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|-------------------|-----------|------|-----|

|              |                                                          |                                                                                 |                                                      | Dhrystone                                           |                   | 385       |      |     |

|              | Supply current in<br>I <sub>DD</sub> (Run Run mode, code | $f_{HSE} = f_{HCLK}$ up to 16<br>MHz, included,<br>$f_{HSE} = f_{HCLK}/2$ above | Range 3,<br>V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11 | CoreMark                                            | 4 MHz             | _(3)      |      |     |

|              |                                                          |                                                                                 |                                                      | Fibonacci                                           |                   | 350       | μA   |     |

|              |                                                          |                                                                                 |                                                      | while(1)                                            |                   | 340       |      |     |

| from<br>RAM) | executed from<br>RAM, Flash                              |                                                                                 | $f_{HSE} = f_{HCLK}/2$ above                         | $f_{\text{LOC}} = f_{\text{LOC}} / 2 \text{ above}$ |                   | Dhrystone |      | 4.5 |

| switched OFF | 16 MHZ (PLL ON)(-)                                       | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01                            | CoreMark                                             | 32 MHz                                              | _(3)              | m 4       |      |     |

|              |                                                          |                                                                                 | Fibonacci                                            |                                                     | 4.2               | mA        |      |     |

|              |                                                          |                                                                                 |                                                      | while(1)                                            |                   | 3         |      |     |

1. Guaranteed by characterization results, not tested in production, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

3. CoreMark code is unable to run from RAM since the RAM size is only 2 Kbytes.

| Symbol          | Parameter                      | Conditions                              |                         | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------|--------------------------------|-----------------------------------------|-------------------------|------|--------------------|------|

|                 |                                |                                         | $T_A$ = -40 °C to 25 °C | 0.8  | 1.6                |      |

|                 |                                |                                         | T <sub>A</sub> = 55 °C  | 0.9  | 1.8                |      |

|                 |                                | Independent watchdog<br>and LSI enabled | T <sub>A</sub> = 85 °C  | 1    | 2                  |      |

|                 | Supply current in Standby mode |                                         | T <sub>A</sub> = 105 °C | 1.25 | 3                  | -μΑ  |

| I <sub>DD</sub> |                                |                                         | T <sub>A</sub> = 125 °C | 2    | 7                  |      |

| (Standby)       |                                | Independent watchdog<br>and LSI OFF     | $T_A$ = -40 °C to 25 °C | 0.23 | 0.6                |      |

|                 |                                |                                         | T <sub>A</sub> = 55 °C  | 0.25 | 0.7                |      |

|                 |                                |                                         | T <sub>A</sub> = 85 °C  | 0.36 | 1                  |      |

|                 |                                |                                         | T <sub>A</sub> = 105 °C | 0.62 | 1.7                |      |

|                 |                                |                                         | T <sub>A</sub> = 125 °C | 1.35 | 5                  |      |

| Table 30. Typical and maximum current of | consumptions in Standby mode |

|------------------------------------------|------------------------------|

|------------------------------------------|------------------------------|

1. Guaranteed by characterization results at 125 °C, not tested in production, unless otherwise specified

| Symbol                            | parameter                                   | System frequency | Current<br>consumption<br>during wakeup | Unit |

|-----------------------------------|---------------------------------------------|------------------|-----------------------------------------|------|

|                                   |                                             | HSI              | 1                                       |      |

|                                   | Supply current during wakeup from Stop mode | HSI/4            | 0,7                                     |      |

| I <sub>DD</sub> (WU from<br>Stop) |                                             | MSI 4,2 MHz      | 0,7                                     |      |

|                                   |                                             | MSI 1,05 MHz     | 0,4                                     |      |

|                                   |                                             | MSI 65 KHz       | 0,1                                     | mA   |

| I <sub>DD</sub> (Reset)           | Reset pin pulled down                       | -                | 0,21                                    |      |

| I <sub>DD</sub> (Power Up)        | BOR ON                                      | -                | 0,23                                    |      |

| I <sub>DD</sub> (WU from          | With Fast wakeup set                        | MSI 2,1 MHz      | 0,5                                     |      |

| StandBy)                          | With Fast wakeup disabled                   | MSI 2,1 MHz      | 0,12                                    |      |

## On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked OFF

- with only one peripheral clocked ON

## Flash memory and data EEPROM

| Symbol                              | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |  |

|-------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|--|

| V <sub>DD</sub>                     | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |  |

| +                                   | Programming time for                                                           | Erasing                                         | -    | 3.28 | 3.94               | 20   |  |

| t <sub>prog</sub> word or half-page |                                                                                | Programming                                     | -    | 3.28 | 3.94               | ms   |  |

|                                     | Average current during<br>the whole programming /<br>erase operation           |                                                 | -    | 500  | 700                | μA   |  |

| I <sub>DD</sub>                     | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |  |

Table 43. Flash memory and data EEPROM characteristics

1. Guaranteed by design, not tested in production.

| Cumhal                          | Deventer                                                                                                   | Conditions                       | Value              | Unit    |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------|---------|--|

| Symbol                          | Parameter                                                                                                  | Conditions                       | Min <sup>(1)</sup> | Unit    |  |

|                                 | Cycling (erase / write)<br>Program memory                                                                  | T <sub>A</sub> = -40°C to 105 °C | 10                 |         |  |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>EEPROM data memory                                                              |                                  | 100                | koveles |  |

| INCYC <sup>1</sup>              | Cycling (erase / write)<br>Program memory                                                                  | T <sub>A</sub> = -40°C to 125 °C | 0.2                | kcycles |  |

|                                 | Cycling (erase / write)<br>EEPROM data memory                                                              |                                  | 2                  |         |  |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C<br>T <sub>RET</sub> = +85 °C |                                  | 30                 |         |  |

|                                 | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 85 \text{ °C}$                             | TRET - 105 C                     | 30                 |         |  |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C                             | T <sub>RFT</sub> = +105 °C       |                    |         |  |

| 'RET` '                         | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 105$ °C                                    | TRET - +103 C                    | 10                 | years   |  |

|                                 | Data retention (program memory) after<br>200 cycles at T <sub>A</sub> = 125 °C                             | T <sub>RET</sub> = +125 °C       |                    |         |  |

|                                 | Data retention (EEPROM data memory) after 2 kcycles at $T_A = 125 ^{\circ}\text{C}$                        | RET - TIZS C                     |                    |         |  |

| Table 44. Flash memor | y and data EEPROM endurance and retention |

|-----------------------|-------------------------------------------|

1. Guaranteed by characterization results, not tested in production.

2. Characterization is done according to JEDEC JESD22-A117.

## 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 45*. They are based on the EMS levels and classes defined in application note AN1709.

| ę | Symbol            | Parameter                                                                                                                         | Conditions                                                                                                    | Level/<br>Class |

|---|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|

| V | / <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP32, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2 | 3B              |

| V | / <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP32, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4 | 4A              |

#### Table 45. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

Figure 29. Typical connection diagram using the ADC

- 1. Refer to Table 54: ADC characteristics for the values of RAIN, RADC and CADC.

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

### 6.3.16 Temperature sensor characteristics

#### Table 57. Temperature sensor calibration values

| Calibration value name | Description                                                                                            | Memory address            |

|------------------------|--------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL2                | TS ADC raw data acquired at<br>temperature of 130 °C $\pm$ 5 °C,<br>V <sub>DDA</sub> = 3 V $\pm$ 10 mV | 0x1FF8 007E - 0x1FF8 007F |

| Symbol                                | Parameter                                      | Min  | Тур  | Мах       | Unit  |  |  |  |

|---------------------------------------|------------------------------------------------|------|------|-----------|-------|--|--|--|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | <u>+2</u> | °C    |  |  |  |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 1.48 | 1.61 | 1.75      | mV/°C |  |  |  |

| V <sub>130</sub>                      | Voltage at 130°C ±5°C <sup>(2)</sup>           | 640  | 670  | 700       | mV    |  |  |  |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                            | -    | 3.4  | 6         | μA    |  |  |  |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                   | -    | -    | 10        |       |  |  |  |

| T <sub>S_temp</sub> <sup>(4)(3)</sup> | ADC sampling time when reading the temperature | 10   | -    | -         | μs    |  |  |  |

Table 58. Temperature sensor characteristics

1. Guaranteed by characterization results, not tested in production.

2. Measured at V<sub>DD</sub> = 3 V  $\pm$ 10 mV. V30 ADC conversion result is stored in the TS\_CAL1 byte.

3. Guaranteed by design, not tested in production.

4. Shortest sampling time can be determined in the application by multiple iterations.

| Symbol | Parameter                          | Conditions | Min | Тур | Max <sup>(1)</sup> | Unit |

|--------|------------------------------------|------------|-----|-----|--------------------|------|

|        | Current consumption <sup>(4)</sup> | Fast mode  | -   | 3.5 | 5                  | uА   |

| ICOMP2 |                                    | Slow mode  | -   | 0.5 | 2                  | μΑ   |

Table 60. Comparator 2 characteristics (continued)

1. Guaranteed by characterization results, not tested in production.

4. Comparator consumption only. Internal reference voltage (necessary for comparator operation) is not included.

### 6.3.18 Timer characteristics

#### **TIM timer characteristics**

The parameters given in the *Table 61* are guaranteed by design.

Refer to Section 6.3.13: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                                                 | Conditions                    | Min    | Мах                     | Unit                 |

|------------------------|---------------------------------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|

| +                      | Timer resolution time                                                     |                               | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  |                                                                           | f <sub>TIMxCLK</sub> = 32 MHz | 31.25  | -                       | ns                   |

| f                      | Timer external clock                                                      |                               | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4                                                   | f <sub>TIMxCLK</sub> = 32 MHz | 0      | 16                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                                                          | -                             |        | 16                      | bit                  |

|                        | 16-bit counter clock                                                      | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t <sub>COUNTER</sub>   | period when internal clock<br>is selected (timer's<br>prescaler disabled) | f <sub>TIMxCLK</sub> = 32 MHz | 0.0312 | 2048                    | μs                   |

| +                      | Maximum possible count                                                    | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT |                                                                           | f <sub>TIMxCLK</sub> = 32 MHz | -      | 134.2                   | S                    |

Table 61. TIMx<sup>(1)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM2 and TIM21 timers.

<sup>2.</sup> The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

In TSSOP14 package, where V<sub>DDA</sub> pin is shared with V<sub>DD</sub> pin, I/O toggling should be minimized to reach the values given in the above table. I/O toggling with loaded I/O pins can generate ripple on V<sub>DD</sub>/V<sub>DDA</sub> and degrade the comparator performance.

### **USART/LPUART** characteristics

The parameters given in the following table are guaranteed by design.

| Symbol               | Parameter                                                                               | Conditions                                                    | Тур | Max  | Unit |

|----------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|------|------|

|                      |                                                                                         | Stop mode with main regulator in<br>Run mode, Range 2 or 3    | -   | 8.7  |      |

| <sup>t</sup> wuusart | calculate the maximum<br>USART/LPUART baudrate<br>allowing to wake up from<br>Stop mode | Stop mode with main regulator in<br>Run mode, Range 1         | -   | 8.1  | μs   |

|                      |                                                                                         | Stop mode with main regulator in low-power mode, Range 2 or 3 | -   | 12   |      |

|                      |                                                                                         | Stop mode with main regulator in low-power mode, Range 1      | -   | 11.4 |      |

| Table 64. USART/LPUART | characteristics |

|------------------------|-----------------|

|                        |                 |

## LQFP32 device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## 7.3 WLCSP25 package information

# Figure 39. WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

| Table 70. WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale |

|------------------------------------------------------------------------------------|

| package mechanical data                                                            |

| Symbol            |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |  |

|-------------------|-------|-------------|-------|--------|-----------------------|--------|--|--|

| Symbol            | Min   | Тур         | Мах   | Min    | Тур                   | Max    |  |  |

| А                 | 0.525 | 0.555       | 0.585 | 0.0207 | 0.0219                | 0.0230 |  |  |

| A1                | -     | 0.175       | -     | -      | 0.0069                | -      |  |  |

| A2                | -     | 0.380       | -     | -      | 0.0150                | -      |  |  |

| A3 <sup>(2)</sup> | -     | 0.025       | -     | -      | 0.0010                | -      |  |  |

| b <sup>(3)</sup>  | 0.220 | 0.250       | 0.280 | 0.0087 | 0.0098                | 0.0110 |  |  |

| D                 | 2.098 | 2.133       | 2.168 | 0.0826 | 0.0840                | 0.0854 |  |  |

| E                 | 2.035 | 2.070       | 2.105 | 0.0801 | 0.0815                | 0.0829 |  |  |

| е                 | -     | 0.400       | -     | -      | 0.0157                | -      |  |  |

| e1                | -     | 1.600       | -     | -      | 0.0630                | -      |  |  |

| e2                | -     | 1.600       | -     | -      | 0.0630                | -      |  |  |

| F                 | -     | 0.2665      | -     | -      | 0.0105                | -      |  |  |

# Table 70. WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale package mechanical data (continued)

|     |   | -     |       | • |        |        |

|-----|---|-------|-------|---|--------|--------|

| G   | - | 0.235 | -     | - | 0.0093 | -      |

| aaa | - | -     | 0.100 | - | -      | 0.0039 |

| bbb | - | -     | 0.100 | - | -      | 0.0039 |

| CCC | - | -     | 0.100 | - | -      | 0.0039 |

| ddd | - | -     | 0.050 | - | -      | 0.0020 |

| eee | - | -     | 0.050 | - | -      | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

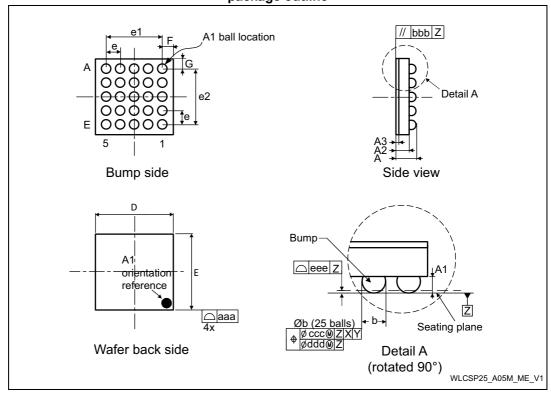

# Figure 40. WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

WLCSP25\_A05M\_FP\_V1

#### Table 71. WLCSP25 recommended PCB design rules (0.4 mm pitch)

| Dimension         | Recommended values                                               |  |  |

|-------------------|------------------------------------------------------------------|--|--|

| Pitch             | 0.4 mm                                                           |  |  |

| Dpad              | 0.225 mm                                                         |  |  |

| Dsm               | 0.290 mm typ. (depends on the soldermask registration tolerance) |  |  |

| Stencil opening   | 0.250 mm                                                         |  |  |

| Stencil thickness | 0.100 mm                                                         |  |  |

#### **Device marking**

The following figure gives an example of topside marking versus ball A1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

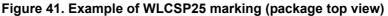

Figure 43. UFQFPN28 recommended footprint

1. Dimensions are expressed in millimeters.

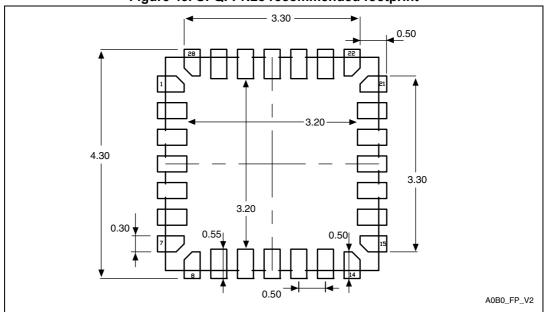

#### **UFQFPN28** device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

Figure 44. Example of UFQFPN28 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

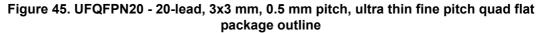

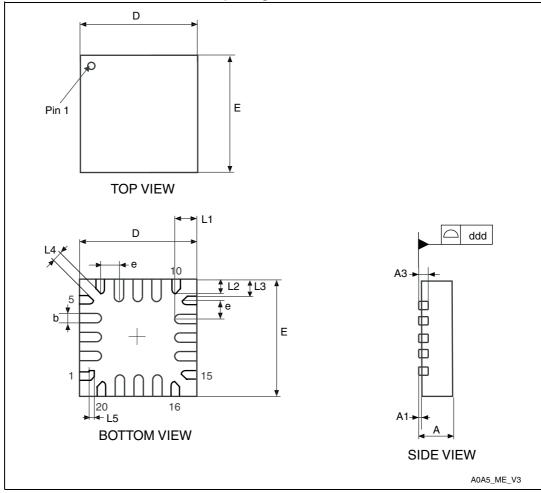

## 7.5 UFQFPN20 package information

1. Drawing is not to scale.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID027973 Rev 4