# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 16                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 512 x 8                                                               |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 9x12b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 20-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l011f4p6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | duction                                                  |

|---|-------|----------------------------------------------------------|

| 2 | Desc  | ription                                                  |

|   | 2.1   | Device overview                                          |

|   | 2.2   | Ultra-low-power device continuum 13                      |

| 3 | Fund  | tional overview                                          |

|   | 3.1   | Low-power modes                                          |

|   | 3.2   | Interconnect matrix                                      |

|   | 3.3   | ARM® Cortex®-M0+ core                                    |

|   | 3.4   | Reset and supply management 20                           |

|   |       | 3.4.1 Power supply schemes                               |

|   |       | 3.4.2 Power supply supervisor                            |

|   |       | 3.4.3 Voltage regulator                                  |

|   |       | 3.4.4 Boot modes                                         |

|   | 3.5   | Clock management                                         |

|   | 3.6   | Low-power real-time clock and backup registers           |

|   | 3.7   | General-purpose inputs/outputs (GPIOs) 24                |

|   | 3.8   | Memories                                                 |

|   | 3.9   | Direct memory access (DMA) 25                            |

|   | 3.10  | Analog-to-digital converter (ADC)                        |

|   | 3.11  | Temperature sensor                                       |

|   |       | 3.11.1 Internal voltage reference (V <sub>RFFINT</sub> ) |

|   | 3.12  | Ultra-low-power comparators and reference voltage        |

|   | 3.13  | System configuration controller 27                       |

|   | 3.14  | Timers and watchdogs                                     |

|   |       | 3.14.1 General-purpose timers (TIM2, TIM21)              |

|   |       | 3.14.2 Low-power Timer (LPTIM)                           |

|   |       | 3.14.3 SysTick timer                                     |

|   |       | 3.14.4 Independent watchdog (IWDG)                       |

|   |       | 3.14.5 Window watchdog (WWDG) 29                         |

|   | 3.15  | Communication interfaces 29                              |

| Table 46. | EMI characteristics                                                       |

|-----------|---------------------------------------------------------------------------|

| Table 47. | ESD absolute maximum ratings                                              |

| Table 48. | Electrical sensitivities                                                  |

| Table 49. | I/O current injection susceptibility                                      |

| Table 50. | I/O static characteristics                                                |

| Table 51. | Output voltage characteristics                                            |

| Table 52. | I/O AC characteristics                                                    |

| Table 53. | NRST pin characteristics                                                  |

| Table 54. | ADC characteristics                                                       |

| Table 55. | $R_{AIN}$ max for $f_{ADC}$ = 16 MHz                                      |

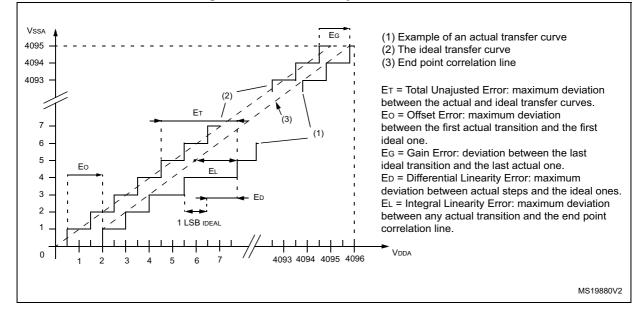

| Table 56. | ADC accuracy                                                              |

| Table 57. | Temperature sensor calibration values                                     |

| Table 58. | Temperature sensor characteristics                                        |

| Table 59. | Comparator 1 characteristics                                              |

| Table 60. | Comparator 2 characteristics                                              |

| Table 61. | TIMx characteristics                                                      |

| Table 62. | I2C analog filter characteristics                                         |

| Table 63. | I2C frequency in all I2C modes                                            |

| Table 64. | USART/LPUART characteristics                                              |

| Table 65. | SPI characteristics in voltage Range 1                                    |

| Table 66. | SPI characteristics in voltage Range 2                                    |

| Table 67. | SPI characteristics in voltage Range 391                                  |

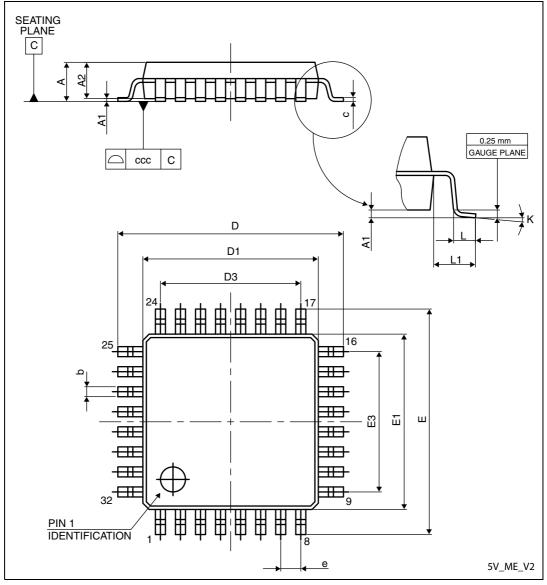

| Table 68. | LQFP32, 7 x 7 mm, 32-pin low-profile quad flat package mechanical data    |

| Table 69. | UFQFPN32, 5 x 5 mm, 32-pin package mechanical data                        |

| Table 70. | WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale  |

|           | package mechanical data                                                   |

| Table 71. | WLCSP25 recommended PCB design rules (0.4 mm pitch)                       |

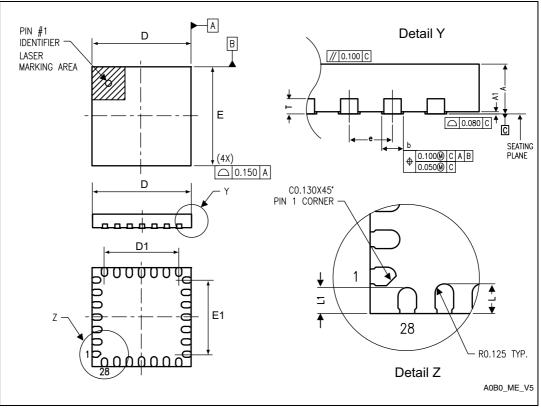

| Table 72. | UFQPN28, 4 x 4 mm, 28-pin package mechanical data                         |

| Table 73. | UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |

|           | package mechanical data                                                   |

| Table 74. | TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |

|           | package mechanical data                                                   |

| Table 75. | TSSOP14 – 14-lead thin shrink small outline, 5.0 x 4.4 mm, 0.65 mm pitch, |

|           | package mechanical data                                                   |

| Table 76. | Thermal characteristics                                                   |

| Table 77. | STM32L011x3/4 ordering information scheme                                 |

| Table 78. | Document revision history                                                 |

| Figure 42. | UFQPN28, 4 x 4 mm, 28-pin package outline                                 | 101 |

|------------|---------------------------------------------------------------------------|-----|

| Figure 43. | UFQFPN28 recommended footprint                                            | 102 |

| Figure 44. | Example of UFQFPN28 marking (package top view)                            | 102 |

| Figure 45. | UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |     |

|            | package outline                                                           | 103 |

| Figure 46. | UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |     |

|            | package recommended footprint                                             | 104 |

| Figure 47. | Example of UFQFPN20 marking (package top view)                            | 105 |

| Figure 48. | TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |     |

| -          | package outline                                                           | 106 |

| Figure 49. | TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |     |

| -          | package footprint                                                         | 107 |

| Figure 50. | Example of TSSOP20 marking (package top view)                             | 108 |

| Figure 51. | TSSOP14 – 14-lead thin shrink small outline, 5.0 x 4.4 mm, 0.65 mm pitch, |     |

| -          | package outline.                                                          | 109 |

| Figure 52. | Example of TSSOP14 marking (package top view)                             |     |

| Figure 53. | Thermal resistance                                                        |     |

(if internal reference voltage is on), it can be the RTC alarm/tamper/timestamp/wakeup events, the USART/I2C/LPUART/LPTIM wakeup events.

#### Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillator are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USART/I2C/LPUART/LPTIM wakeup events.

#### • Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE bypass and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

#### • Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillator are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

|                                                | Functionalities depending on the operating power supply range |                                  |                            |  |

|------------------------------------------------|---------------------------------------------------------------|----------------------------------|----------------------------|--|

| Operating power supply<br>range                | ADC operation                                                 | Dynamic voltage<br>scaling range | I/O operation              |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | ADC only,<br>conversion time up<br>to 570 ksps                | Range 2 or<br>range 3            | Degraded speed performance |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time up<br>to 1.14 Msps               | Range 1, range 2 or<br>range 3   | Degraded speed performance |  |

#### Table 3. Functionalities depending on the operating power supply range

#### Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L011x3/4 embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

# 3.4 Reset and supply management

#### 3.4.1 Power supply schemes

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively. On TSSOP14 package, V<sub>DDA</sub> is internally connected to V<sub>DD</sub>.

#### 3.4.2 Power supply supervisor

The devices feature an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

Two versions are available:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the VDD min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

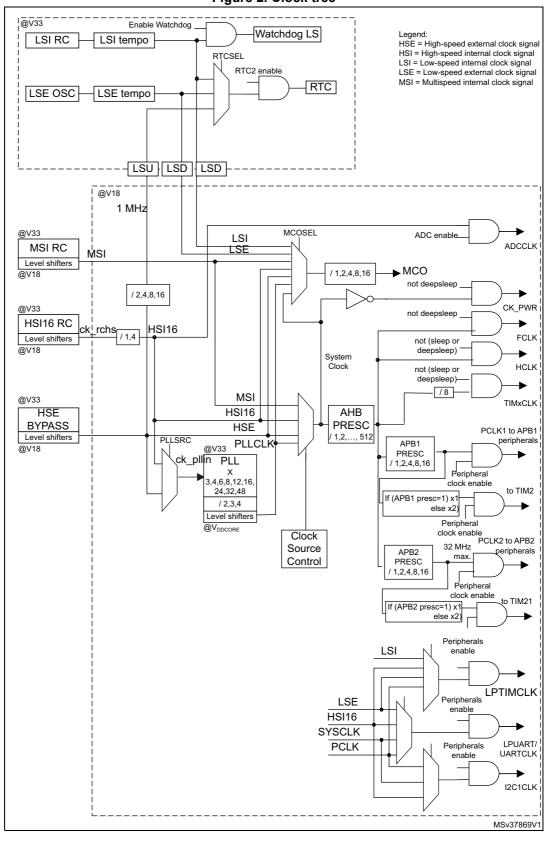

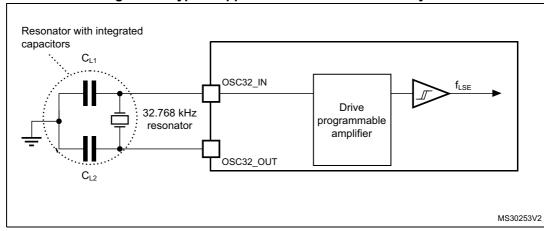

Figure 2. Clock tree

(rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 38 GPIOs can be connected to the 16 configurable interrupt/event lines. The 10 other lines are connected to PVD, RTC, USART, I2C, LPUART, LPTIM or comparator events.

# 3.8 Memories

The STM32L011x3/4 devices have the following features:

- 2 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 8 or 16 Kbytes of embedded Flash program memory

- 512 bytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 4 Kbytes of system memory

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

• Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

## 3.9 Direct memory access (DMA)

The flexible 5-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, LPUART, general-purpose timers, and ADC.

# 3.10 Analog-to-digital converter (ADC)

A native 12-bit, extended to 16-bit through hardware oversampling, analog-to-digital converter is embedded into STM32L011x3/4 devices. It has up to 10 external channels and 2 internal channels (temperature sensor, voltage reference). Three channels, PA0, PA4 and PA5, are fast channels, while the others are standard channels.

The ADC performs conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC frequency is independent from the CPU frequency, allowing maximum sampling rate of 1.14 MSPS even with a low CPU speed. The ADC consumption is low at all frequencies (~25  $\mu$ A at 10 kSPS, ~200  $\mu$ A at 1MSPS). An auto-shutdown function guarantees that the ADC is powered off except during the active conversion phase.

The ADC can be served by the DMA controller. It can operate from a supply voltage down to 1.65 V.

The ADC features a hardware oversampler up to 256 samples, this improves the resolution to 16 bits (see AN2668).

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers.

# 3.11 Temperature sensor

The temperature sensor (T<sub>SENSE</sub>) generates a voltage V<sub>SENSE</sub> that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode (see *Table 57: Temperature sensor calibration values*).

### 3.11.1 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It enables accurate monitoring of the  $V_{DD}$  value (since no external voltage,  $V_{REF+}$ , is available for ADC). The precise voltage of  $V_{REFINT}$  is individually measured for each part by ST during production test and stored in the system memory area (see *Table 20: Embedded internal reference voltage calibration values*). It is accessible in read-only mode.

#### 3.14.1 General-purpose timers (TIM2, TIM21)

There are three synchronizable general-purpose timers embedded in the STM32L011x3/4 devices (see *Table 7* for differences).

#### TIM2

TIM2 is based on 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It features four independent channels each for input capture/output compare, PWM or one-pulse mode output.

The TIM2 general-purpose timers can work together or with the TIM21 general-purpose timer via the Timer Link feature for synchronization or event chaining. Its counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2 has independent DMA request generation.

This timer is capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### TIM21

TIM21 is based on a 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It has two independent channels for input capture/output compare, PWM or one-pulse mode output. It can work together and be synchronized with TIM2 full-featured general-purpose timer.

It can also be used as simple timebase and be clocked by the LSE clock source (32.768 kHz) to provide independent timebase from the main CPU clock.

### 3.14.2 Low-power Timer (LPTIM)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one shot mode

- Selectable software / hardware input trigger

- Selectable clock source

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM1 input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

#### 3.14.3 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit downcounter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches '0'.

### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

### 3.14.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 3.15 Communication interfaces

# 3.15.1 I<sup>2</sup>C bus

One I<sup>2</sup>C interface (I2C1) can operate in multimaster or slave modes. The I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

The I<sup>2</sup>C interface supports 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

| Table 8, Com | parison of I20 | analog and | l digital filters  |

|--------------|----------------|------------|--------------------|

|              |                | analog und | a aigitai iiitoi o |

In addition, I2C1 provides hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C interface can be served by the DMA controller.

Refer to *Table 9* for the supported modes and features of I2C interface.

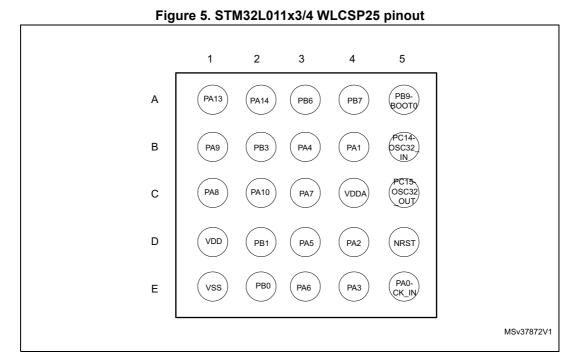

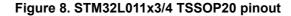

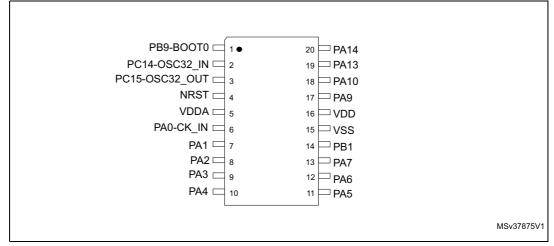

1. The above figure shows the package top view.

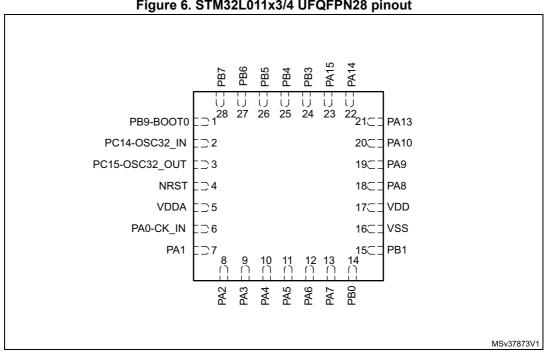

Figure 6. STM32L011x3/4 UFQFPN28 pinout

1. The above figure shows the package top view.

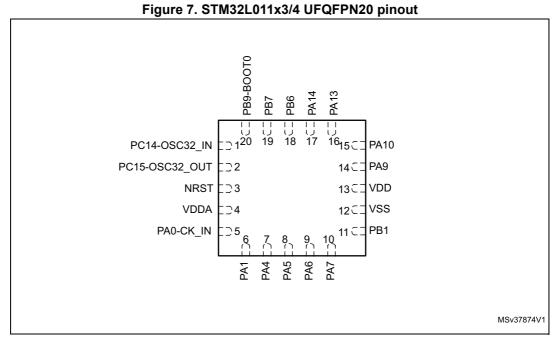

1. The above figure shows the package top view.

1. The above figure shows the package top view.

1. The above figure shows the package top view.

| Table 12. Legend/abbreviations used in the pinout | table |

|---------------------------------------------------|-------|

|---------------------------------------------------|-------|

| Nar           | ne                                            | Abbreviation                                                                                                                          | Definition                                                   |  |

|---------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| Pin n         | ame                                           | Unless otherwise specified in brackets below the pin name, the pin function during and after reset is the same as the actual pin name |                                                              |  |

|               |                                               | S                                                                                                                                     | Supply pin                                                   |  |

| Pin t         | уре                                           | I                                                                                                                                     | Input only pin                                               |  |

|               |                                               | I/O                                                                                                                                   | Input / output pin                                           |  |

|               |                                               | FT                                                                                                                                    | 5 V tolerant I/O                                             |  |

|               |                                               | FTf                                                                                                                                   | Tf 5 V tolerant I/O, FM+ capable                             |  |

| I/O stru      | ioturo                                        | TTa                                                                                                                                   | TTa 3.3 V tolerant I/O directly connected to the ADC         |  |

| 1/0 501       | loure                                         | TC                                                                                                                                    | TC Standard 3.3V I/O                                         |  |

|               |                                               | B Dedicated BOOT0 pin                                                                                                                 |                                                              |  |

|               |                                               | RST                                                                                                                                   | Bidirectional reset pin with embedded weak pull-up resistor  |  |

| Not           | Notes Unless otherwise specified after reset. |                                                                                                                                       | ed by a note, all I/Os are set as floating inputs during and |  |

| Pin functions | Alternate<br>functions                        | Functions selected through                                                                                                            | gh GPIOx_AFR registers                                       |  |

|               | Additional functions                          | Functions directly selected/enabled through peripheral registers                                                                      |                                                              |  |

| S          |  |

|------------|--|

| - <b>H</b> |  |

| Z          |  |

| 5          |  |

| Ň          |  |

|            |  |

| Ó          |  |

|            |  |

| ×          |  |

| ώ          |  |

| 4          |  |

DocID027973 Rev 4

5

|        | Table 14. Alternate functions |                                               |                     |                                                |                         |                                      |              |                        |           |

|--------|-------------------------------|-----------------------------------------------|---------------------|------------------------------------------------|-------------------------|--------------------------------------|--------------|------------------------|-----------|

|        |                               | AF0                                           | AF1                 | AF2                                            | AF3                     | AF4                                  | AF5          | AF6                    | AF7       |

| Po     | orts                          | SPI1/USART2/<br>TIM21/<br>EVENTOUT/<br>SYS_AF | SPI1/I2C1/<br>LPTIM | LPUART1/<br>LPTIM/TIM2/<br>EVENTOUT/<br>SYS_AF | I2C1/LPTIM/<br>EVENTOUT | I2C1/USART2/L<br>PUART1/<br>EVENTOUT | SPI1/TIM2/21 | LPUART1/EVE<br>VENTOUT | COMP1/2   |

|        | PA0                           | USART2_RX                                     | LPTIM1_IN1          | TIM2_CH1                                       | -                       | USART2_CTS                           | TIM2_ETR     | LPUART1_RX             | COMP1_OUT |

|        | PA1                           | EVENTOUT                                      | LPTIM1_IN2          | TIM2_CH2                                       | I2C1_SMBA               | USART2_RTS                           | TIM21_ETR    | LPUART1_TX             | -         |

|        | PA2                           | TIM21_CH1                                     | -                   | TIM2_CH3                                       | -                       | USART2_TX                            | -            | LPUART1_TX             | COMP2_OUT |

|        | PA3                           | TIM21_CH2                                     | -                   | TIM2_CH4                                       | -                       | USART2_RX                            | -            | LPUART1_RX             | -         |

|        | PA4                           | SPI1_NSS                                      | LPTIM1_IN1          | LPTIM1_ETR                                     | I2C1_SCL                | USART2_CK                            | TIM2_ETR     | LPUART1_TX             | COMP2_OUT |

|        | PA5                           | SPI1_SCK                                      | LPTIM1_IN2          | TIM2_ETR                                       | -                       | -                                    | TIM2_CH1     | -                      | -         |

|        | PA6                           | SPI1_MISO                                     | LPTIM1_ETR          | -                                              | -                       | LPUART1_CTS                          | -            | EVENTOUT               | COMP1_OUT |

| Port A | PA7                           | SPI1_MOSI                                     | LPTIM1_OUT          | -                                              | -                       | USART2_CTS                           | TIM21_ETR    | EVENTOUT               | COMP2_OUT |

| FUILA  | PA8                           | MCO                                           | -                   | LPTIM1_IN1                                     | EVENTOUT                | USART2_CK                            | TIM2_CH1     | -                      | -         |

|        | PA9                           | MCO                                           | I2C1_SCL            | LPTIM1_OUT                                     | -                       | USART2_TX                            | TIM21_CH2    | -                      | COMP1_OUT |

|        | PA10                          | TIM21_CH1                                     | I2C1_SDA            | RTC_REFIN                                      | -                       | USART2_RX                            | TIM2_CH3     | -                      | COMP1_OUT |

|        | PA11                          | SPI1_MISO                                     | LPTIM1_OUT          | EVENTOUT                                       | -                       | USART2_CTS                           | TIM21_CH2    | -                      | COMP1_OUT |

|        | PA12                          | SPI1_MOSI                                     | -                   | EVENTOUT                                       | -                       | USART2_RTS                           | -            | -                      | COMP2_OUT |

|        | PA13                          | SWDIO                                         | LPTIM1_ETR          | -                                              | I2C1_SDA                | -                                    | SPI1_SCK     | LPUART1_RX             | COMP1_OUT |

|        | PA14                          | SWCLK                                         | LPTIM1_OUT          | -                                              | I2C1_SMBA               | USART2_TX                            | SPI1_MISO    | LPUART1_TX             | COMP2_OUT |

|        | PA15                          | SPI1_NSS                                      | -                   | TIM2_ETR                                       | EVENTOUT                | USART2_RX                            | TIM2_CH1     | -                      | -         |

41/115

# 6.3 Operating conditions

# 6.3.1 General operating conditions

| Table 18. General operating condition | Table 18 | 18. Genera | I operating | conditions |

|---------------------------------------|----------|------------|-------------|------------|

|---------------------------------------|----------|------------|-------------|------------|

| Symbol             | Parameter                                                                                               | Conditions                                                 | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Max                  | Unit |

|--------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                                            | -                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                   |      |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                                           | -                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                   | MHz  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                                           | -                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                   |      |

|                    |                                                                                                         | BOR detector disabled                                      | 1.65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.6                  |      |

| V <sub>DD</sub>    | Standard operating voltage                                                                              | BOR detector enabled, at power on                          | 1.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.6                  | V    |

|                    |                                                                                                         | BOR detector disabled, after power on                      | 1.65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.6                  |      |

| V <sub>DDA</sub>   | Analog operating voltage<br>(all features)                                                              | Must be the same voltage as $V_{DD}^{(1)}$                 | 1.65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.6                  | V    |

|                    | land tooltone on ET ET( and DOT air (2)                                                                 | $2.0 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.5                  |      |

| N                  | Input voltage on FT, FTf and RST pins <sup>(2)</sup>                                                    | 1.65 V ≤ V <sub>DD</sub> ≤2.0 V                            | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.2                  | V    |

| V <sub>IN</sub>    | Input voltage on BOOT0 pin                                                                              | -                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.5                  | v    |

|                    | Input voltage on TC pin                                                                                 | -                                                          | -0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>DD</sub> +0.3 |      |

|                    |                                                                                                         | LQFP32 package                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 333                  |      |

|                    |                                                                                                         | UFQFPN32 package                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 513                  |      |

|                    |                                                                                                         | UFQFPN28 package                                           | 0<br>0<br>1.65<br>1.8<br>1.65<br>1.65<br>-0.3<br>-0.3<br>0<br>-0.3<br>-0.3<br>3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 206                  |      |

|                    | Power dissipation at $T_A = 85 \degree C$ (range 6)<br>or $T_A = 105 \degree C$ (rage 7) <sup>(3)</sup> | WLCSP25 package                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 286                  |      |

|                    |                                                                                                         | TSSOP20 package                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 270                  |      |

|                    |                                                                                                         | UFQFPN20 package                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 196                  |      |

| Р                  |                                                                                                         | TSSOP14 package                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 210                  | mW   |

| P <sub>D</sub>     |                                                                                                         | LQFP32 package                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83                   | mvv  |

|                    |                                                                                                         | UFQFPN32 package                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 128                  |      |

|                    |                                                                                                         | UFQFPN28 package                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52                   |      |

|                    | Power dissipation at $T_A = 125 \degree C$ (range 3) <sup>(3)</sup>                                     | WLCSP25 package                                            | 0         32           0         32           ad         1.65         3.6           ad,         1.8         3.6           ad,         1.65         3.6           ad,         1.65         3.6           ad,         1.65         3.6           ad,         1.65         3.6           ltage         1.65         3.6           ltage         1.65         3.6           -0.3         5.5         -0.3           -0.3         5.5         -0.3           -0.3         5.5         -0.3           -0.3         5.2         0           -0.3         5.5         -0.3           -0.3         V <sub>DD</sub> +0.3         -0.3           -0.3         V <sub>DD</sub> +0.3         -0.3           -0.3         V <sub>DD</sub> +0.3         -0.3           -10         -1.3         -0.3           -10         -1.3         -0.3           -10         -1.3         -0.3           -10         -1.3         -0.3           -10         -1.3         -0.3           -10         -1.3         -0.3           -10         -1.3         -0.3 </td <td>1</td> | 1                    |      |

|                    | -,                                                                                                      | TSSOP20 package                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67                   |      |

|                    |                                                                                                         | UFQFPN20 package                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49                   |      |

|                    |                                                                                                         | TSSOP14 package                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53                   |      |

| Symbol          | Parameter                 | Conditions                           |                                                                                                                                                                                                                                | Тур                             | Max <sup>(1)</sup> | Unit |

|-----------------|---------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|------|

|                 |                           |                                      | $T_A$ = -40 °C to 25 °C                                                                                                                                                                                                        | 0.8                             | 1.6                |      |

|                 |                           | Independent watchdog and LSI enabled | T <sub>A</sub> = 55 °C                                                                                                                                                                                                         | 0.9                             | 1.8                |      |

|                 |                           |                                      | T <sub>A</sub> = 85 °C                                                                                                                                                                                                         | 1                               | 2                  |      |

|                 |                           |                                      | T <sub>A</sub> = 105 °C                                                                                                                                                                                                        | °C 0.8<br>0.9<br>1<br>1.25<br>2 | ) 1.25             | 3    |

| I <sub>DD</sub> | Supply current in Standby |                                      | T <sub>A</sub> = 125 °C                                                                                                                                                                                                        | 2                               | 7                  |      |

| (Standby)       | mode                      |                                      | $T_A = 55 \degree C$ 0.9 $T_A = 85 \degree C$ 1 $T_A = 105 \degree C$ 1.25 $T_A = 125 \degree C$ 2 $T_A = -40 \degree C$ to $25 \degree C$ 0.23 $T_A = 55 \degree C$ 0.25 $T_A = 85 \degree C$ 0.36 $T_A = 105 \degree C$ 0.62 | 0.6 µ                           | μA                 |      |

|                 |                           |                                      | T <sub>A</sub> = 55 °C                                                                                                                                                                                                         | 0.25                            | 0.7                |      |

|                 |                           | Independent watchdog<br>and LSI OFF  | $T_A = 85 ^{\circ}C$                                                                                                                                                                                                           | 0.36                            | 1                  |      |

|                 |                           |                                      | T <sub>A</sub> = 105 °C                                                                                                                                                                                                        | 0.62                            | 1.7                |      |

|                 |                           |                                      | T <sub>A</sub> = 125 °C                                                                                                                                                                                                        | 1.35                            | 5                  |      |

| Table 30. Typical and maximum current of | consumptions in Standby mode |

|------------------------------------------|------------------------------|

|------------------------------------------|------------------------------|

1. Guaranteed by characterization results at 125 °C, not tested in production, unless otherwise specified

| Table 31. A | Average current | consumption | during wakeup |

|-------------|-----------------|-------------|---------------|

|-------------|-----------------|-------------|---------------|

| Symbol                            | parameter                                   | System frequency | Current<br>consumption<br>during wakeup | Unit |  |

|-----------------------------------|---------------------------------------------|------------------|-----------------------------------------|------|--|

|                                   |                                             | HSI              | 1                                       |      |  |

|                                   |                                             | HSI/4            | 0,7<br>0,7                              |      |  |

| I <sub>DD</sub> (WU from<br>Stop) | Supply current during wakeup from Stop mode | MSI 4,2 MHz      |                                         |      |  |

|                                   |                                             | MSI 1,05 MHz     | 0,4                                     |      |  |

|                                   |                                             | MSI 65 KHz       | MSI 65 KHz 0,1                          |      |  |

| I <sub>DD</sub> (Reset)           | Reset pin pulled down                       | -                | 0,21                                    | mA   |  |

| I <sub>DD</sub> (Power Up)        | BOR ON                                      | -                | 0,23                                    |      |  |

| I <sub>DD</sub> (WU from          | With Fast wakeup set                        | MSI 2,1 MHz      | 0,5                                     |      |  |

| StandBy)                          | With Fast wakeup disabled                   | MSI 2,1 MHz      | 0,12                                    |      |  |

### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)