#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 16                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 7x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 20-UFQFN                                                                |

| Supplier Device Package    | 20-UFQFPN (3x3)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l011f4u6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of tables

| Table 1.               | Device summary                                                                |    |

|------------------------|-------------------------------------------------------------------------------|----|

| Table 2.               | Ultra-low-power STM32L011x3/x4 device features and peripheral counts.         | 11 |

| Table 3.               | Functionalities depending on the operating power supply range                 | 15 |

| Table 4.               | CPU frequency range depending on dynamic voltage scaling                      |    |

| Table 5.               | Functionalities depending on the working mode                                 |    |

|                        | (from Run/active down to standby)                                             | 16 |

| Table 6.               | STM32L011x3/4 peripherals interconnect matrix                                 | 18 |

| Table 7.               | Timer feature comparison                                                      |    |

| Table 8.               | Comparison of I2C analog and digital filters                                  |    |

| Table 9.               | STM32L011x3/4 I <sup>2</sup> C implementation                                 |    |

| Table 10.              | USART implementation                                                          |    |

| Table 11.              | SPI implementation.                                                           |    |

| Table 12.              | Legend/abbreviations used in the pinout table                                 |    |

| Table 13.              | Pin definitions                                                               |    |

| Table 14.              | Alternate functions                                                           |    |

| Table 15.              | Voltage characteristics                                                       |    |

| Table 16.              | Current characteristics                                                       |    |

| Table 10.<br>Table 17. | Thermal characteristics                                                       |    |

| Table 17.<br>Table 18. |                                                                               |    |

|                        | General operating conditions                                                  |    |

| Table 19.              | Embedded reset and power control block characteristics.                       |    |

| Table 20.              | Embedded internal reference voltage calibration values                        |    |

| Table 21.              | Embedded internal reference voltage                                           |    |

| Table 22.              | Current consumption in Run mode, code with data processing running from Flash | 53 |

| Table 23.              | Current consumption in Run mode vs code type,                                 |    |

|                        | code with data processing running from Flash                                  |    |

| Table 24.              | Current consumption in Run mode, code with data processing running from RAM   | 55 |

| Table 25.              | Current consumption in Run mode vs code type,                                 |    |

|                        | code with data processing running from RAM                                    |    |

| Table 26.              | Current consumption in Sleep mode                                             |    |

| Table 27.              | Current consumption in Low-power Run mode                                     |    |

| Table 28.              | Current consumption in Low-power Sleep mode                                   |    |

| Table 29.              | Typical and maximum current consumptions in Stop mode                         |    |

| Table 30.              | Typical and maximum current consumptions in Standby mode                      |    |

| Table 31.              | Average current consumption during wakeup                                     |    |

| Table 32.              | Peripheral current consumption in run or Sleep mode                           | 61 |

| Table 33.              | Peripheral current consumption in Stop and Standby mode                       | 62 |

| Table 34.              | Low-power mode wakeup timings                                                 | 62 |

| Table 35.              | High-speed external user clock characteristics.                               | 64 |

| Table 36.              | Low-speed external user clock characteristics                                 | 65 |

| Table 37.              | LSE oscillator characteristics                                                | 66 |

| Table 38.              | 16 MHz HSI16 oscillator characteristics                                       | 67 |

| Table 39.              | LSI oscillator characteristics                                                | 68 |

| Table 40.              | MSI oscillator characteristics                                                | 68 |

| Table 41.              | PLL characteristics                                                           |    |

| Table 42.              | RAM and hardware registers                                                    |    |

| Table 43.              | Flash memory and data EEPROM characteristics                                  |    |

| Table 44.              | Flash memory and data EEPROM endurance and retention                          | 71 |

| Table 45.              | EMS characteristics                                                           |    |

|                        |                                                                               |    |

## 1 Introduction

The ultra-low-power STM32L011x3/4 family includes devices in 7 different package types from 14 to 32 pins. The description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L011x3/4 microcontrollers suitable for a wide range of applications:

- Gas/water meters and industrial sensors

- Healthcare and fitness equipment

- Remote control and user interface

- PC peripherals, gaming, GPS equipment

- Alarm system, wired and wireless sensors, video intercom

This STM32L011x3/4 datasheet should be read in conjunction with the STM32L0x1 reference manual (RM0377).

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core please refer to the Cortex<sup>®</sup>-M0+ Technical Reference Manual, available from the www.arm.com website.

Figure 1 shows the general block diagram of the device family.

## 2 Description

The access line ultra-low-power STM32L011x3/4 family incorporates the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ 32-bit RISC core operating at a 32 MHz frequency, high-speed embedded memories (up to 16 Kbytes of Flash program memory, 512 bytes of data EEPROM and 2 Kbytes of RAM) plus an extensive range of enhanced I/Os and peripherals.

The STM32L011x3/4 devices provide high power efficiency for a wide range of performance. It is achieved with a large choice of internal and external clock sources, an internal voltage adaptation and several low-power modes.

The STM32L011x3/4 devices offer several analog features, one 12-bit ADC with hardware oversampling, two ultra-low-power comparators, several timers, one low-power timer (LPTIM), three general-purpose 16-bit timers, one RTC and one SysTick which can be used as timebases. They also feature two watchdogs, one watchdog with independent clock and window capability and one window watchdog based on bus clock.

Moreover, the STM32L011x3/4 devices embed standard and advanced communication interfaces: one I2C, one SPI, one USART, and a low-power UART (LPUART).

The STM32L011x3/4 also include a real-time clock and a set of backup registers that remain powered in Standby mode.

The ultra-low-power STM32L011x3/4 devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +125 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The devices feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD/VDDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD/VDDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD/VDDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC\_CSR).

## 3.4.4 Boot modes

At startup, BOOT0 pin and nBOOT0, nBOOT1 and nBOOT\_SEL option bits are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1 (PA4, PA7, PA13 and PA14 on TSSOP14 package or PA4, PA5, PA6 and PA7 on other packages) or USART2 (PA2, PA3 and PA9, PA10). See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

## 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

#### Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

#### • Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

#### Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

#### • System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 0-32 MHz high-speed external (HSE bypass), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

#### • Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

#### • RTC clock sources

The LSI, LSE or HSE sources can be chosen to clock the RTC, whatever the system clock.

#### • Startup clock

After reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

#### • Clock security system (CSS)

This feature can be enabled by software. If an LSE clock failure occurs, it provides an interrupt or wakeup event which is generated assuming it has been previously enabled. This feature is not available on the HSE clock.

#### Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

#### 3.14.1 General-purpose timers (TIM2, TIM21)

There are three synchronizable general-purpose timers embedded in the STM32L011x3/4 devices (see *Table 7* for differences).

#### TIM2

TIM2 is based on 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It features four independent channels each for input capture/output compare, PWM or one-pulse mode output.

The TIM2 general-purpose timers can work together or with the TIM21 general-purpose timer via the Timer Link feature for synchronization or event chaining. Its counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2 has independent DMA request generation.

This timer is capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### TIM21

TIM21 is based on a 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It has two independent channels for input capture/output compare, PWM or one-pulse mode output. It can work together and be synchronized with TIM2 full-featured general-purpose timer.

It can also be used as simple timebase and be clocked by the LSE clock source (32.768 kHz) to provide independent timebase from the main CPU clock.

## 3.14.2 Low-power Timer (LPTIM)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one shot mode

- Selectable software / hardware input trigger

- Selectable clock source

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM1 input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

#### 3.14.3 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit downcounter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches '0'.

DocID027973 Rev 4

## 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

## 3.14.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.15 Communication interfaces

## 3.15.1 I<sup>2</sup>C bus

One I<sup>2</sup>C interface (I2C1) can operate in multimaster or slave modes. The I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

The I<sup>2</sup>C interface supports 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

| Table 8, Com | parison of I20 | analog and | l digital filters  |

|--------------|----------------|------------|--------------------|

|              |                | analog und | a aigitai iiitoi o |

In addition, I2C1 provides hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C interface can be served by the DMA controller.

Refer to *Table 9* for the supported modes and features of I2C interface.

| Table 13. | Pin definitions | (continued) |

|-----------|-----------------|-------------|

|-----------|-----------------|-------------|

|         |          | Pin     | num      | ber    |                         |         |                                       |          |               |       | ,<br>Pin fur                                                                                | octions                 |

|---------|----------|---------|----------|--------|-------------------------|---------|---------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------|-------------------------|

| TSSOP14 | UFQFPN20 | TSSOP20 | UFQFPN28 | LQFP32 | UFQFPN32 <sup>(1)</sup> | WLCSP25 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                         | Additional<br>functions |

| 12      | 15       | 18      | 20       | 20     | 20                      | C2      | PA10                                  | I/O      | FTf           | -     | TIM21_CH1,<br>I2C1_SDA,<br>RTC_REFIN,<br>USART2_RX,<br>TIM2_CH3,<br>COMP1_OUT               | -                       |

| -       | -        | -       | -        | 21     | 21                      | -       | PA11                                  | I/O      | FT            | -     | SPI1_MISO,<br>LPTIM1_OUT,<br>EVENTOUT,<br>USART2_CTS,<br>TIM21_CH2,<br>COMP1_OUT            | -                       |

| -       | -        | -       | -        | 22     | 22                      | -       | PA12                                  | I/O      | FT            | -     | SPI1_MOSI,<br>EVENTOUT,<br>USART2_RTS,<br>COMP2_OUT                                         | -                       |

| 13      | 16       | 19      | 21       | 23     | 23                      | A1      | PA13                                  | I/O      | FTf           | -     | SWDIO,<br>LPTIM1_ETR,<br>I2C1_SDA,<br>SPI1_SCK,<br>LPUART1_RX,<br>COMP1_OUT                 | -                       |

| 14      | 17       | 20      | 22       | 24     | 24                      | A2      | PA14                                  | I/O      | FT            | -     | SWCLK,<br>LPTIM1_OUT,<br>I2C1_SMBA,<br>USART2_TX,<br>SPI1_MISO,<br>LPUART1_TX,<br>COMP2_OUT | -                       |

| -       | -        | -       | 23       | 25     | 25                      | -       | PA15                                  | I/O      | FT            | -     | SPI1_NSS,<br>TIM2_ETR,<br>EVENTOUT,<br>USART2_RX,<br>TIM2_CH1                               | -                       |

| -       | -        | -       | 24       | 26     | 26                      | B2      | PB3                                   | I/O      | FT            | -     | SPI1_SCK,<br>TIM2_CH2,<br>EVENTOUT                                                          | COMP2_INM               |

| -       | -        | -       | 25       | 27     | 27                      | -       | PB4                                   | I/O      | FT            | -     | SPI1_MISO,<br>EVENTOUT                                                                      | COMP2_INP               |

## 6.3.3 Embedded internal reference voltage

The parameters given in *Table 21* are based on characterization results, unless otherwise specified.

| Table 20. Embedde      | ed internal reference voltage                                         | calibration values        |

|------------------------|-----------------------------------------------------------------------|---------------------------|

| Calibration value name | Description                                                           | Memory address            |

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25°C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                   | Parameter                                                             | Conditions                                                     | Min   | Тур   | Max   | Unit                     |

|------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|--------------------------|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                            | – 40 °C < T <sub>J</sub> < +125 °C                             | 1.202 | 1.224 | 1.242 | V                        |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                       | -                                                              | -     | 2     | 3     | ms                       |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> voltage during V <sub>REFINT</sub> factory measure   | -                                                              | 2.99  | 3     | 3.01  | V                        |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured V <sub>REFINT</sub> value <sup>(3)</sup> | Including uncertainties due to ADC and V <sub>DDA</sub> values | -     | -     | ±5    | mV                       |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                               | –40 °C < T <sub>J</sub> < +125 °C                              | -     | 25    | 100   | ppm/°C                   |

| Coeff` ´                                 |                                                                       | 0 °C < T <sub>J</sub> < +50 °C                                 | -     | -     | 20    | ppin/ C                  |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                   | 1000 hours, T= 25 °C                                           | -     | -     | 1000  | ppm                      |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                   | 3.0 V < V <sub>DDA</sub> < 3.6 V                               | -     | -     | 2000  | ppm/V                    |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage   | -                                                              | 5     | 10    | -     | μs                       |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                      | -                                                              | -     | -     | 10    | μs                       |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                       | -                                                              | -     | 13.5  | 25    | μA                       |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                                | -                                                              | -     | -     | 1     | μA                       |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                  | -                                                              | -     | -     | 50    | pF                       |

| I <sub>LPBUF</sub> <sup>(4)</sup>        | Consumption of reference<br>voltage buffer for VREF_OUT<br>and COMP   | -                                                              | -     | 730   | 1200  | nA                       |

| V <sub>REFINT_DIV1</sub> <sup>(4)</sup>  | 1/4 reference voltage                                                 | -                                                              | 24    | 25    | 26    |                          |

| V <sub>REFINT_DIV2</sub> <sup>(4)</sup>  | 1/2 reference voltage                                                 | -                                                              | 49    | 50    | 51    | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(4)</sup>  | 3/4 reference voltage                                                 | -                                                              | 74    | 75    | 76    | KEFINI                   |

### Table 21. Embedded internal reference voltage<sup>(1)</sup>

1. Refer to *Table 33: Peripheral current consumption in Stop and Standby mode* for the value of the internal reference current consumption (I<sub>REFINT</sub>).

2. Guaranteed by test in production.

3. The internal V<sub>REF</sub> value is individually measured in production and stored in dedicated EEPROM bytes.

DocID027973 Rev 4

| Symbol         | Parameter         | Co                                               | f <sub>HCLK</sub>                                  | Тур     | Max <sup>(1)</sup> | Unit |    |

|----------------|-------------------|--------------------------------------------------|----------------------------------------------------|---------|--------------------|------|----|

|                |                   |                                                  |                                                    | 1 MHz   | 140                | 180  |    |

|                |                   |                                                  | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0]=11   | 2 MHz   | 245                | 290  | μA |

|                |                   |                                                  |                                                    | 4 MHz   | 460                | 540  |    |

| · ·            |                   | f <sub>HSE</sub> = f <sub>HCLK</sub> up to       |                                                    | 4 MHz   | 0.56               | 0.65 |    |

|                |                   | 16 MHz included,<br>$f_{HSE} = f_{HCLK}/2$ above | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 8 MHz   | 1.1                | 1.3  |    |

|                |                   | 16 MHz (PLL ON) <sup>(2)</sup>                   |                                                    | 16 MHz  | 2.1                | 2.4  | mA |

|                |                   |                                                  | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01  | 8 MHz   | 1.3                | 1.6  |    |

|                | Run mode,<br>code |                                                  |                                                    | 16 MHz  | 2.6                | 3    |    |

| from<br>Flash) | executed          |                                                  |                                                    | 32 MHz  | 5.3                | 6.5  |    |

|                | from Flash        |                                                  | Range 3, V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11  | 65 kHz  | 34.5               | 54   |    |

|                |                   | MSI clock<br>HSI clock                           |                                                    | 524 kHz | 86                 | 120  | μA |

|                |                   |                                                  |                                                    | 4.2 MHz | 505                | 560  |    |

|                |                   |                                                  | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 16 MHz  | 2.2                | 2.6  |    |

|                |                   |                                                  | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01  | 32 MHz  | 5.4                | 5.9  | mA |

| <b>T</b> 1 1 00 0 1      |                                  |                                  |

|--------------------------|----------------------------------|----------------------------------|

| Table 22. Current consum | ption in Run mode, code with dat | ta processing running from Flash |

1. Guaranteed by characterization results at 125 °C, not tested in production, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Table 23. Current consumption in Run mode vs code type, |

|---------------------------------------------------------|

| code with data processing running from Flash            |

| Symbol                                                                                               | Parameter  |                                                                                                                                                   | Conditions                                           |                           |        |      |    |

|------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------|--------|------|----|

| Supply<br>I <sub>DD</sub> current in<br>(Run Run mode,<br>from code<br>Flash) executed<br>from Flash |            |                                                                                                                                                   |                                                      | Dhrystone                 |        | 460  |    |

|                                                                                                      |            |                                                                                                                                                   |                                                      | CoreMark                  |        | 440  |    |

|                                                                                                      |            | Range 3,<br>V <sub>CORE</sub> =1.2 V,                                                                                                             | Fibonacci                                            | 4 MHz                     | 330    | μA   |    |

|                                                                                                      | Cumple     | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above<br>16 MHz (PLL ON) <sup>(1)</sup> | VOS[1:0]=11                                          | while(1)                  |        | 305  |    |

|                                                                                                      | current in |                                                                                                                                                   |                                                      | while(1), prefetch<br>OFF |        | 320  |    |

|                                                                                                      |            |                                                                                                                                                   |                                                      | Dhrystone                 |        | 5.4  |    |

|                                                                                                      |            |                                                                                                                                                   | CoreMark                                             | 1                         | 4.9    |      |    |

|                                                                                                      |            |                                                                                                                                                   | Range 1,<br>VOS[1:0]=01,<br>V <sub>CORE</sub> =1.8 V | Fibonacci                 | 32 MHz | 5    | mA |

|                                                                                                      |            |                                                                                                                                                   |                                                      | while(1)                  |        | 4.35 |    |

|                                                                                                      |            |                                                                                                                                                   |                                                      | while(1), prefetch<br>OFF |        | 3.7  |    |

1. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

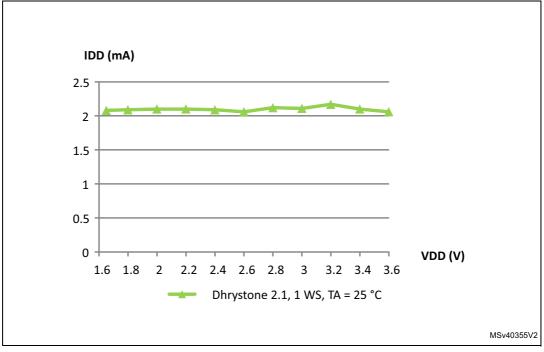

Figure 15.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25 °C, Run mode, code running from Flash memory, Range 2, 16 MHz HSE, 1WS

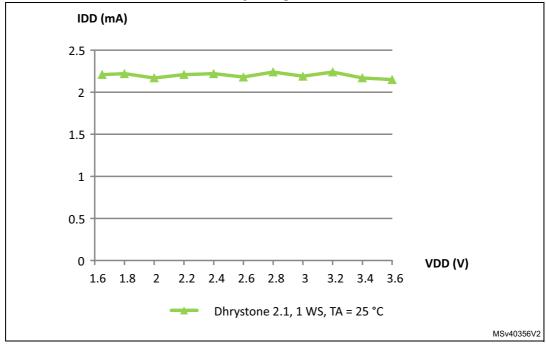

Figure 16. I<sub>DD</sub> vs V<sub>DD</sub>, at T<sub>A</sub>= 25 °C, Run mode, code running from Flash memory, Range 2, HSI16, 1WS

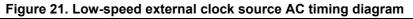

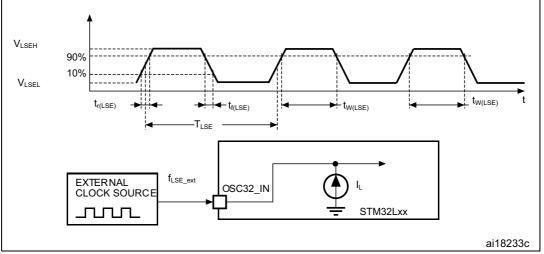

#### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 18*.

| Symbol                                     | Parameter                               | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User external clock source<br>frequency |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level (         |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage    | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                       | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                              | -                                | 45                 | -      | 55                 | %    |

| ١L                                         | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 36. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 37*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization

| Symbol                                | Parameter                          | Condition                                | Тур | Мах | Unit |  |

|---------------------------------------|------------------------------------|------------------------------------------|-----|-----|------|--|

|                                       |                                    | MSI range 0                              | 30  | -   |      |  |

|                                       |                                    | MSI range 1                              | 20  | -   |      |  |

|                                       |                                    | MSI range 2                              | 15  | -   |      |  |

|                                       |                                    | MSI range 3                              | 10  | -   |      |  |

| t                                     | MSI oscillator startup time        | MSI range 4                              | 6   | -   | μs   |  |

| t <sub>SU(MSI)</sub>                  |                                    | MSI range 5                              | 5   | -   | μο   |  |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | 3.5 | -   |      |  |

|                                       |                                    | MSI range 6,<br>Voltage range 3          | 5   | -   |      |  |

|                                       |                                    | MSI range 0                              | -   | 40  |      |  |

|                                       |                                    | MSI range 1                              | -   | 20  |      |  |

|                                       | MSI oscillator stabilization time  | MSI range 2                              | -   | 10  | μs   |  |

|                                       |                                    | MSI range 3                              | i   | 4   |      |  |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> |                                    | MSI range 4                              | -   | 2.5 |      |  |

| STAB(MSI)                             |                                    | MSI range 5                              | I   | 2   | μο   |  |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -   | 2   |      |  |

|                                       |                                    | MSI range 3,<br>Voltage range 3          | -   | 3   |      |  |

| f <sub>over(msi)</sub>                | MSI oscillator frequency overshoot | Any range to range 5                     | -   | 4   | MHz  |  |

|                                       |                                    | Any range to range 6                     | -   | 6   |      |  |

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results, not tested in production.

## 6.3.8 PLL characteristics

The parameters given in *Table 41* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 18*.

| Symbol Parameter    |                                |     | Unit |                    |      |

|---------------------|--------------------------------|-----|------|--------------------|------|

|                     |                                | Min | Тур  | Max <sup>(1)</sup> | Unit |

| f                   | PLL input clock <sup>(2)</sup> | 2   | -    | 24                 | MHz  |

| <sup>T</sup> PLL_IN | PLL input clock duty cycle     | 45  | -    | 55                 | %    |

## 6.3.13 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the conditions summarized in *Table 18*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                         | Conditions                                                                                                                                    | Min                                          | Тур                                | Max                                | Unit |  |

|------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------|------------------------------------|------|--|

| V <sub>IL</sub>  | Input low level voltage                           | TC, FT, FTf, RST<br>I/Os                                                                                                                      | -                                            | -                                  | 0.3V <sub>DD</sub>                 |      |  |

|                  |                                                   | BOOT0 pin                                                                                                                                     | -                                            | -                                  | 0.14V <sub>DD</sub> <sup>(1)</sup> |      |  |

| V                | Input high level voltage                          | All I/Os except<br>BOOT0 pin                                                                                                                  | 0.7 V <sub>DD</sub>                          | -                                  | -                                  | v    |  |

| V <sub>IH</sub>  | input nigh level voltage                          | BOOT0 pin                                                                                                                                     | 0.15<br>V <sub>DD</sub> +0.56 <sup>(1)</sup> | -                                  | -                                  |      |  |

| V                | I/O Schmitt trigger voltage hysteresis            | Standard I/Os                                                                                                                                 | -                                            | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                  |      |  |

| V <sub>hys</sub> | (2)                                               | BOOT0 pin                                                                                                                                     | -                                            | 0.01                               | -                                  |      |  |

|                  |                                                   | $\label{eq:VSS} \begin{array}{l} V_{SS} \leq V_{IN} \leq V_{DD} \\ \mbox{All I/Os except} \\ \mbox{BOOT0 and FTf} \\ \mbox{I/Os} \end{array}$ | -                                            | -                                  | ±50                                | nA   |  |

|                  |                                                   | BOOT0 <sup>(5)</sup><br>V <sub>IN</sub> = V <sub>DD</sub>                                                                                     | -                                            | +2                                 | -                                  |      |  |

| l <sub>lkg</sub> | g Input leakage current <sup>(4)</sup>            | BOOT0<br>V <sub>IN</sub> = V <sub>SS</sub>                                                                                                    | -                                            | 0                                  | -                                  | μA   |  |

|                  |                                                   | $V_{DD} \le V_{IN} \le 5 V$<br>FT I/Os                                                                                                        | -                                            | -                                  | 200                                |      |  |

|                  |                                                   | V <sub>DD</sub> ≤ V <sub>IN</sub> ≤ 5 V<br>FTf I/Os                                                                                           | -                                            | -                                  | 500                                | nA   |  |

|                  |                                                   | $V_{DD} \le V_{IN} \le 5 V$<br>BOOT0                                                                                                          | -                                            | -                                  | 10                                 | μA   |  |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(6)</sup>   | $V_{IN} = V_{SS}$                                                                                                                             | 30                                           | 45                                 | 60                                 | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(6)</sup> | $V_{IN} = V_{DD}$                                                                                                                             | 30                                           | 45                                 | 60                                 | kΩ   |  |

| C <sub>IO</sub>  | I/O pin capacitance                               | -                                                                                                                                             | -                                            | 5                                  | -                                  | pF   |  |

| Table 50. I/O static characteris | stics |

|----------------------------------|-------|

|----------------------------------|-------|

1. Guaranteed by characterization, not tested in production

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results, not tested in production.

3. With a minimum of 200 mV. Guaranteed by characterization results, not tested in production.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

5. BOOT0/PB9 pin limitation: typical input leakage current = 2  $\mu$ A and input frequency limited to 10 kHz (1.65 V < V<sub>DD</sub> < 2.7 V) and 5 MHz (2.7 V < V<sub>DD</sub> < 3.6 V).

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

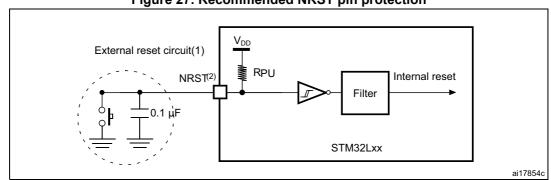

Figure 27. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 53. Otherwise the reset will not be taken into account by the device.

### 6.3.15 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 54* are values derived from tests performed under ambient temperature,  $f_{PCLK}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 18: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                             | Parameter                             | Conditions                                            | Min                 | Тур | Мах              | Unit               |

|------------------------------------|---------------------------------------|-------------------------------------------------------|---------------------|-----|------------------|--------------------|

| V                                  | Analog supply voltage for             | Fast channel                                          | 1.65                | -   | 3.6              | V                  |

| V <sub>DDA</sub>                   | ADC ON                                | Standard channels                                     | 1.75 <sup>(1)</sup> | -   | 3.6              | v                  |

|                                    | Current consumption of the            | 1.14 Msps                                             | -                   | 200 | -                |                    |

|                                    | ADC on V <sub>DDA</sub>               | 10 ksps                                               | -                   | 40  | -                |                    |

| I <sub>DDA</sub> (ADC)             | Current consumption of the            | 1.14 Msps                                             | -                   | 70  | -                | μA                 |

|                                    | ADC on V <sub>DD</sub> <sup>(2)</sup> | 10 ksps                                               | -                   | 1   | -                |                    |

|                                    |                                       | Voltage scaling Range 1                               | 0.14                | -   | 16               |                    |

| f <sub>ADC</sub>                   | ADC clock frequency                   | Voltage scaling Range 2                               | 0.14                | -   | 8                | MHz                |

|                                    |                                       | Voltage scaling Range 3                               | 0.14                | -   | 4                |                    |

| f <sub>S</sub> <sup>(3)</sup>      | Sampling rate                         | -                                                     | 0.05                | -   | 1.14             | MHz                |

| f <sub>TRIG</sub> <sup>(3)</sup>   | External trigger frequency            | f <sub>ADC</sub> = 16 MHz,<br>16-bit resolution       | -                   | -   | 941              | kHz                |

|                                    |                                       | -                                                     | -                   | -   | 17               | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range              | -                                                     | 0                   | -   | V <sub>DDA</sub> | V                  |

| R <sub>AIN</sub> <sup>(3)</sup>    | External input impedance              | See <i>Equation 1</i> and <i>Table 55</i> for details | -                   | -   | 50               | kΩ                 |

| R <sub>ADC</sub> <sup>(3)(4)</sup> | Sampling switch resistance            | -                                                     | -                   | -   | 1                | kΩ                 |

| C <sub>ADC</sub> <sup>(3)</sup>    | Internal sample and hold capacitor    | -                                                     | -                   | -   | 8                | pF                 |

Table 54. ADC characteristics

### **USART/LPUART** characteristics

The parameters given in the following table are guaranteed by design.

| Symbol                                                                              | Parameter                                                     | Conditions                                               | Тур | Max  | Unit |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|-----|------|------|

|                                                                                     |                                                               | Stop mode with main regulator in Run mode, Range 2 or 3  |     | 8.7  |      |

| t <sub>WUUSART</sub> USART/LPUART baudrate<br>allowing to wake up from<br>Stop mode | calculate the maximum                                         | Stop mode with main regulator in<br>Run mode, Range 1    | -   | 8.1  | μs   |

|                                                                                     | Stop mode with main regulator in low-power mode, Range 2 or 3 | -                                                        | 12  |      |      |

|                                                                                     |                                                               | Stop mode with main regulator in low-power mode, Range 1 | -   | 11.4 |      |

| Table 64. USART/LPUART | characteristics |

|------------------------|-----------------|

|                        |                 |

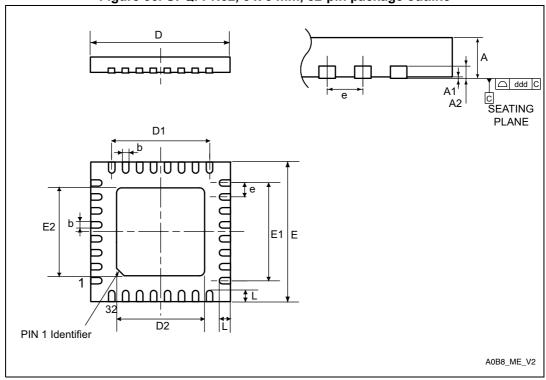

## 7.2 UFQFPN32 package information

#### Figure 36. UFQFPN32, 5 x 5 mm, 32-pin package outline

1. Drawing is not to scale.

#### Table 69. UFQFPN32, 5 x 5 mm, 32-pin package mechanical data

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| A      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |

| A3     | -     | 0.200       | -     | -      | 0.0079                | -      |

| b      | 0.180 | 0.250       | 0.300 | 0.0071 | 0.0098                | 0.0118 |

| D      | 4.900 | 5.000       | 5.100 | 0.1929 | 0.1969                | 0.2008 |

| D2     | 3.200 | 3.450       | 3.700 | 0.1260 | 0.1358                | 0.1457 |

| E      | 4.900 | 5.000       | 5.100 | 0.1929 | 0.1969                | 0.2008 |

| E2     | 3.200 | 3.450       | 3.700 | 0.1260 | 0.1358                | 0.1457 |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197 |

| ddd    | -     | -           | 0.080 | -      | -                     | 0.0031 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

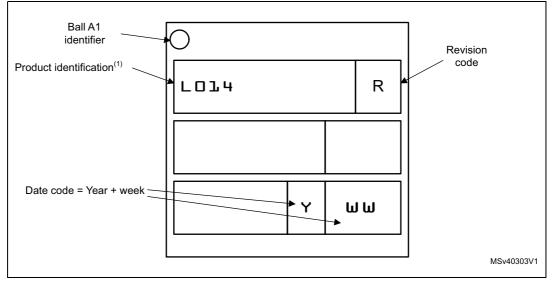

#### **Device marking**

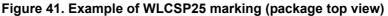

The following figure gives an example of topside marking versus ball A1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Table 74. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |

|-------------------------------------------------------------------------------------|

| package mechanical data (continued)                                                 |

| Symbol | millimeters |      |       | inches <sup>(1)</sup> |      |        |  |

|--------|-------------|------|-------|-----------------------|------|--------|--|

|        | Min.        | Тур. | Max.  | Min.                  | Тур. | Max.   |  |

| k      | 0°          | -    | 8°    | 0°                    | -    | 8°     |  |

| aaa    | -           | -    | 0.100 | -                     | -    | 0.0039 |  |

1. Values in inches are converted from mm and rounded to four decimal digits.

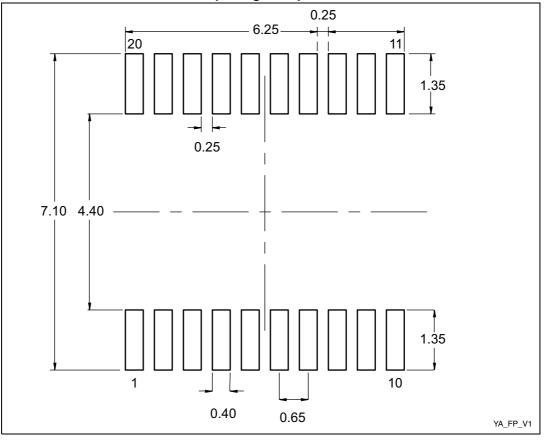

Figure 49. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, package footprint

1. Dimensions are expressed in millimeters.

# 8 Part numbering

| Table 77. STM32L011x3/4 ordering information scheme |           |       |   |   |   |   |   |     |  |  |  |  |

|-----------------------------------------------------|-----------|-------|---|---|---|---|---|-----|--|--|--|--|

| Example:                                            | STM32     | L 011 | К | 4 | Т | 6 | D | ххх |  |  |  |  |

| Device family                                       |           |       |   |   |   |   |   |     |  |  |  |  |

| STM32 = ARM-based 32-bit microcontroller            |           |       |   |   |   |   |   |     |  |  |  |  |

|                                                     |           |       |   |   |   |   |   |     |  |  |  |  |

| Product type                                        |           |       |   |   |   |   |   |     |  |  |  |  |

| L = Low power                                       |           |       |   |   |   |   |   |     |  |  |  |  |

| Device subfamily                                    |           |       |   |   |   |   |   |     |  |  |  |  |

| 011 = Access line                                   |           |       |   |   |   |   |   |     |  |  |  |  |

|                                                     |           |       |   |   |   |   |   |     |  |  |  |  |

| Pin count                                           |           |       |   |   |   |   |   |     |  |  |  |  |

| K = 32 pins                                         |           |       |   |   |   |   |   |     |  |  |  |  |

| G = 28 pins                                         |           |       |   |   |   |   |   |     |  |  |  |  |

| E = 25 pins                                         |           |       |   |   |   |   |   |     |  |  |  |  |

| F = 20 pins                                         |           |       |   |   |   |   |   |     |  |  |  |  |

| D = 14 pins                                         |           |       |   |   |   |   |   |     |  |  |  |  |

|                                                     |           |       |   |   |   |   |   |     |  |  |  |  |

| Flash memory size                                   |           |       |   |   |   |   |   |     |  |  |  |  |

| 3 = 8 Kbytes                                        |           |       |   |   |   |   |   |     |  |  |  |  |

| 4 = 16 Kbytes                                       |           |       |   |   |   |   |   |     |  |  |  |  |

| Package                                             |           |       |   |   |   |   |   |     |  |  |  |  |

| T = LQFP                                            |           |       |   |   |   |   |   |     |  |  |  |  |

| U = UFQFPN                                          |           |       |   |   |   |   |   |     |  |  |  |  |

| Y = WLCSP                                           |           |       |   |   |   |   |   |     |  |  |  |  |

| P = TSSOP                                           |           |       |   |   |   |   |   |     |  |  |  |  |

| Temperature range                                   |           |       |   |   |   |   |   |     |  |  |  |  |

| 6 = Industrial temperature range, -40 to 85 °C      |           |       |   |   |   |   |   |     |  |  |  |  |

| 7 = Industrial temperature range, -40 to 105 °C     |           |       |   |   |   |   |   |     |  |  |  |  |

| 3 = Industrial temperature range, -40 to 125 °C     |           |       |   |   |   |   |   |     |  |  |  |  |

|                                                     |           |       |   |   |   |   |   |     |  |  |  |  |

| Options                                             |           |       |   |   |   |   |   |     |  |  |  |  |

| No character = $V_{DD}$ range: 1.8 to 3.6 V and BOR | R enabled |       |   |   |   |   |   |     |  |  |  |  |

| D = $V_{DD}$ range: 1.65 to 3.6 V and BOR disabled  |           |       |   |   |   |   |   |     |  |  |  |  |

| Packing                                             |           |       |   |   |   |   |   |     |  |  |  |  |

TR = tape and reel

No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.