#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 26                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 512 x 8                                                               |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l011k4t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 46. | EMI characteristics                                                       |

|-----------|---------------------------------------------------------------------------|

| Table 47. | ESD absolute maximum ratings                                              |

| Table 48. | Electrical sensitivities                                                  |

| Table 49. | I/O current injection susceptibility                                      |

| Table 50. | I/O static characteristics                                                |

| Table 51. | Output voltage characteristics                                            |

| Table 52. | I/O AC characteristics                                                    |

| Table 53. | NRST pin characteristics                                                  |

| Table 54. | ADC characteristics                                                       |

| Table 55. | $R_{AIN}$ max for $f_{ADC}$ = 16 MHz                                      |

| Table 56. | ADC accuracy                                                              |

| Table 57. | Temperature sensor calibration values                                     |

| Table 58. | Temperature sensor characteristics                                        |

| Table 59. | Comparator 1 characteristics                                              |

| Table 60. | Comparator 2 characteristics                                              |

| Table 61. | TIMx characteristics                                                      |

| Table 62. | I2C analog filter characteristics                                         |

| Table 63. | I2C frequency in all I2C modes                                            |

| Table 64. | USART/LPUART characteristics                                              |

| Table 65. | SPI characteristics in voltage Range 1                                    |

| Table 66. | SPI characteristics in voltage Range 2                                    |

| Table 67. | SPI characteristics in voltage Range 391                                  |

| Table 68. | LQFP32, 7 x 7 mm, 32-pin low-profile quad flat package mechanical data    |

| Table 69. | UFQFPN32, 5 x 5 mm, 32-pin package mechanical data                        |

| Table 70. | WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale  |

|           | package mechanical data                                                   |

| Table 71. | WLCSP25 recommended PCB design rules (0.4 mm pitch)                       |

| Table 72. | UFQPN28, 4 x 4 mm, 28-pin package mechanical data                         |

| Table 73. | UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |

|           | package mechanical data                                                   |

| Table 74. | TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |

|           | package mechanical data                                                   |

| Table 75. | TSSOP14 – 14-lead thin shrink small outline, 5.0 x 4.4 mm, 0.65 mm pitch, |

|           | package mechanical data                                                   |

| Table 76. | Thermal characteristics                                                   |

| Table 77. | STM32L011x3/4 ordering information scheme                                 |

| Table 78. | Document revision history                                                 |

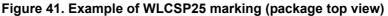

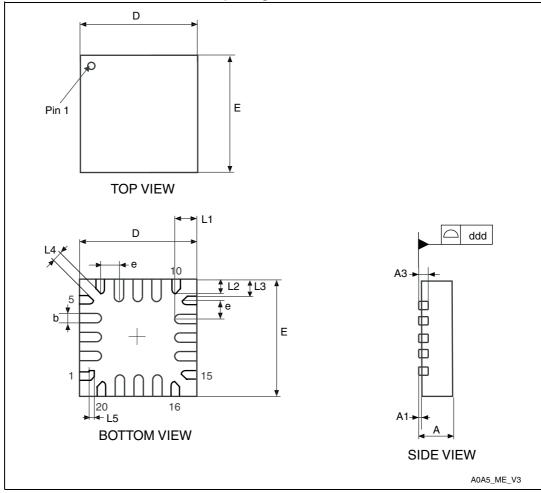

| Figure 42. | UFQPN28, 4 x 4 mm, 28-pin package outline                                 | 101 |

|------------|---------------------------------------------------------------------------|-----|

| Figure 43. | UFQFPN28 recommended footprint                                            | 102 |

| Figure 44. | Example of UFQFPN28 marking (package top view)                            | 102 |

| Figure 45. | UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |     |

|            | package outline                                                           | 103 |

| Figure 46. | UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |     |

|            | package recommended footprint                                             | 104 |

| Figure 47. | Example of UFQFPN20 marking (package top view)                            | 105 |

| Figure 48. | TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |     |

| -          | package outline                                                           | 106 |

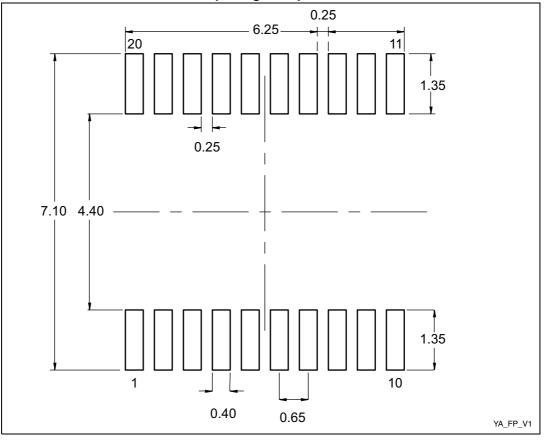

| Figure 49. | TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |     |

| -          | package footprint                                                         | 107 |

| Figure 50. | Example of TSSOP20 marking (package top view)                             | 108 |

| Figure 51. | TSSOP14 – 14-lead thin shrink small outline, 5.0 x 4.4 mm, 0.65 mm pitch, |     |

| -          | package outline.                                                          | 109 |

| Figure 52. | Example of TSSOP14 marking (package top view)                             |     |

| Figure 53. | Thermal resistance                                                        |     |

# 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM<sup>®</sup> Cortex<sup>®</sup>-M4, including ARM<sup>®</sup> Cortex<sup>®</sup>-M3 and ARM<sup>®</sup> Cortex<sup>®</sup>-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 Ultra-low-power series are the best solution for applications such as gas/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power Run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The devices feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD/VDDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD/VDDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD/VDDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC\_CSR).

## 3.4.4 Boot modes

At startup, BOOT0 pin and nBOOT0, nBOOT1 and nBOOT\_SEL option bits are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1 (PA4, PA7, PA13 and PA14 on TSSOP14 package or PA4, PA5, PA6 and PA7 on other packages) or USART2 (PA2, PA3 and PA9, PA10). See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

# 3.6 Low-power real-time clock and backup registers

The real time clock (RTC) and the 5 backup registers are supplied in all modes including standby mode. The backup registers are five 32-bit registers used to store 20 bytes of user application data. They are not reset by a system reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- Automatically correction for 28, 29 (leap year), 30, and 31 day of the month

- Two programmable alarms with wake up from Stop and Standby mode capability

- Periodic wakeup from Stop and Standby with programmable resolution and period

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- 2 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 37 kHz)

- The high-speed external clock

# 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated alternate function registers. All GPIOs are high current capable. Each GPIO output, speed can be slowed (40 MHz, 10 MHz, 2 MHz, 400 kHz). The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to a dedicated IO bus with a toggling speed of up to 32 MHz.

The BOOT0 pin is shared with PB9 GPIO pin. This pin is an input-only pin. If nBOOT\_SEL option bit is reset, sampling this pin on NRST rising edge gives the internal BOOT0 state. This pin then works as PB9 pin. The input voltage characteristics of this pin are specific for BOOT0 pin type (see *Table 50: I/O static characteristics*).

#### Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 26 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event

(rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 38 GPIOs can be connected to the 16 configurable interrupt/event lines. The 10 other lines are connected to PVD, RTC, USART, I2C, LPUART, LPTIM or comparator events.

# 3.8 Memories

The STM32L011x3/4 devices have the following features:

- 2 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 8 or 16 Kbytes of embedded Flash program memory

- 512 bytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 4 Kbytes of system memory

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

• Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

# 3.9 Direct memory access (DMA)

The flexible 5-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: SPI, I<sup>2</sup>C, USART, LPUART, general-purpose timers, and ADC.

|         |          | Pin     | num      | ber    |                         |         |                                       |          |               |        | Pin functions                                                                                               |                                                                  |  |

|---------|----------|---------|----------|--------|-------------------------|---------|---------------------------------------|----------|---------------|--------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| TSSOP14 | UFQFPN20 | TSSOP20 | UFQFPN28 | LQFP32 | UFQFPN32 <sup>(1)</sup> | WLCSP25 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes  | Alternate functions                                                                                         | Additional<br>functions                                          |  |

| 2       | 1        | 2       | 2        | 2      | 2                       | B5      | PC14-<br>OSC32_IN                     | I/O      | FT            | -      | -                                                                                                           | OSC32_IN                                                         |  |

| 3       | 2        | 3       | 3        | 3      | 3                       | C5      | PC15-<br>OSC32_OUT                    | I/O      | тс            | -      | -                                                                                                           | OSC32_OUT                                                        |  |

| 4       | 3        | 4       | 4        | 4      | 4                       | D5      | NRST                                  | I/O      | RST           | (2)    | -                                                                                                           | -                                                                |  |

| 10      | 4        | 5       | 5        | 5      | 5                       | C4      | VDDA                                  | S        | -             | (3)(4) | -                                                                                                           | -                                                                |  |

| 5       | 5        | 6       | 6        | 6      | 6                       | E5      | PA0-CK_IN                             | I/O      | TTa           | -      | USART2_RX,<br>LPTIM1_IN1,<br>TIM2_CH1,<br>USART2_CTS,<br>TIM2_ETR,<br>LPUART1_RX,<br>COMP1_OUT              | COMP1_INM,<br>ADC_IN0,<br>RTC_TAMP2/WKU<br>P1/CK_IN              |  |

| 6       | 6        | 7       | 7        | 7      | 7                       | B4      | PA1                                   | I/O      | FT            | -      | EVENTOUT,<br>LPTIM1_IN2,<br>TIM2_CH2,<br>I2C1_SMBA,<br>USART2_RTS,<br>TIM21_ETR,<br>LPUART1_TX              | COMP1_INP,<br>ADC_IN1                                            |  |

| -       | -        | 8       | 8        | 8      | 8                       | D4      | PA2                                   | I/O      | ТТа           | -      | TIM21_CH1,<br>TIM2_CH3,<br>USART2_TX,<br>LPUART1_TX,<br>COMP2_OUT                                           | COMP2_INM,<br>ADC_IN2,<br>RTC_TAMP3/RTC_<br>TS/RTC_OUT/WKU<br>P3 |  |

| -       | -        | 9       | 9        | 9      | 9                       | E4      | PA3                                   | I/O      | FT            | -      | TIM21_CH2,<br>TIM2_CH4,<br>USART2_RX,<br>LPUART1_RX                                                         | COMP2_INP,<br>ADC_IN3                                            |  |

| 7       | 7        | 10      | 10       | 10     | 10                      | В3      | PA4                                   | I/O      | ТТа           | -      | SPI1_NSS,<br>LPTIM1_IN1,<br>LPTIM1_ETR,<br>I2C1_SCL,<br>USART2_CK,<br>TIM2_ETR,<br>LPUART1_TX,<br>COMP2_OUT | COMP1_INM,<br>COMP2_INM,<br>ADC_IN4                              |  |

# 6.3.3 Embedded internal reference voltage

The parameters given in *Table 21* are based on characterization results, unless otherwise specified.

| Table 20. Embedded internal reference voltage calibration values |                                                                       |                           |  |  |  |

|------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------|--|--|--|

| Calibration value name                                           | Description                                                           | Memory address            |  |  |  |

| VREFINT_CAL                                                      | Raw data acquired at<br>temperature of 25°C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |  |  |  |

| Symbol                                   | Parameter                                                             | Conditions                                                     | Min   | Тур   | Max   | Unit                     |

|------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|--------------------------|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                            | – 40 °C < T <sub>J</sub> < +125 °C                             | 1.202 | 1.224 | 1.242 | V                        |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                       | -                                                              | -     | 2     | 3     | ms                       |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> voltage during V <sub>REFINT</sub> factory measure   | -                                                              | 2.99  | 3     | 3.01  | V                        |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured V <sub>REFINT</sub> value <sup>(3)</sup> | Including uncertainties due to ADC and V <sub>DDA</sub> values | -     | -     | ±5    | mV                       |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                               | –40 °C < T <sub>J</sub> < +125 °C                              | -     | 25    | 100   | ppm/°C                   |

| Coeff` ´                                 |                                                                       | 0 °C < T <sub>J</sub> < +50 °C                                 | -     | -     | 20    | ppin/ C                  |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                   | 1000 hours, T= 25 °C                                           | -     | -     | 1000  | ppm                      |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                   | 3.0 V < V <sub>DDA</sub> < 3.6 V                               | -     | -     | 2000  | ppm/V                    |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage   | -                                                              | 5     | 10    | -     | μs                       |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                      | -                                                              | -     | -     | 10    | μs                       |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                       | -                                                              | -     | 13.5  | 25    | μA                       |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                                | -                                                              | -     | -     | 1     | μA                       |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                  | -                                                              | -     | -     | 50    | pF                       |

| I <sub>LPBUF</sub> <sup>(4)</sup>        | Consumption of reference<br>voltage buffer for VREF_OUT<br>and COMP   | -                                                              | -     | 730   | 1200  | nA                       |

| V <sub>REFINT_DIV1</sub> <sup>(4)</sup>  | 1/4 reference voltage                                                 | -                                                              | 24    | 25    | 26    |                          |

| V <sub>REFINT_DIV2</sub> <sup>(4)</sup>  | 1/2 reference voltage                                                 | -                                                              | 49    | 50    | 51    | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(4)</sup>  | 3/4 reference voltage                                                 | -                                                              | 74    | 75    | 76    | KEFINI                   |

## Table 21. Embedded internal reference voltage<sup>(1)</sup>

1. Refer to *Table 33: Peripheral current consumption in Stop and Standby mode* for the value of the internal reference current consumption (I<sub>REFINT</sub>).

2. Guaranteed by test in production.

3. The internal V<sub>REF</sub> value is individually measured in production and stored in dedicated EEPROM bytes.

DocID027973 Rev 4

- 4. Guaranteed by design, not tested in production.

- 5. Shortest sampling time can be determined in the application by multiple iterations.

- 6. To guarantee less than 1% VREF\_OUT deviation.

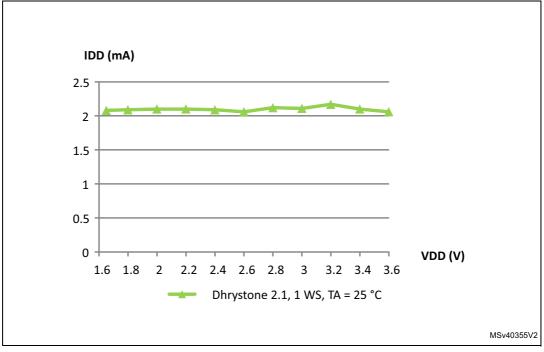

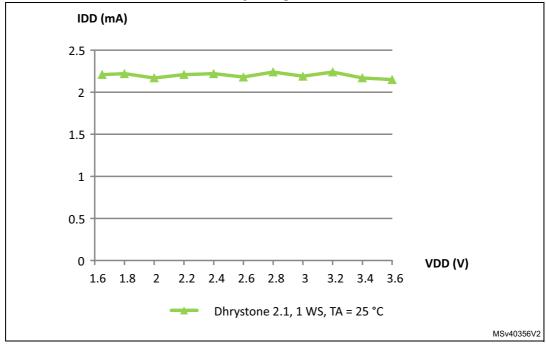

## 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code. The current consumption is measured as described in *Figure 14: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code if not specified otherwise.

The current consumption values are derived from the tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 18: General operating conditions* unless otherwise specified.

The MCU is placed under the following conditions:

- All I/O pins are configured in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time and prefetch is adjusted depending on f<sub>HCLK</sub> frequency and voltage range to provide the best CPU performance unless otherwise specified.

- When the peripherals are enabled f<sub>APB1</sub> = f<sub>APB2</sub> = f<sub>APB</sub>

- When PLL is ON, the PLL inputs are equal to HSI = 16 MHz (if internal clock is used) or HSE = 16 MHz (if HSE bypass mode is used)

- The HSE user clock is applied to CK\_IN. It follows the characteristic specified in Table 35: High-speed external user clock characteristics

- For maximum current consumption  $V_{DD} = V_{DDA} = 3.6$  V is applied to all supply pins

- For typical current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.0 V is applied to all supply pins if not specified otherwise

Figure 15.  $I_{DD}$  vs  $V_{DD}$ , at  $T_A$ = 25 °C, Run mode, code running from Flash memory, Range 2, 16 MHz HSE, 1WS

Figure 16. I<sub>DD</sub> vs V<sub>DD</sub>, at T<sub>A</sub>= 25 °C, Run mode, code running from Flash memory, Range 2, HSI16, 1WS

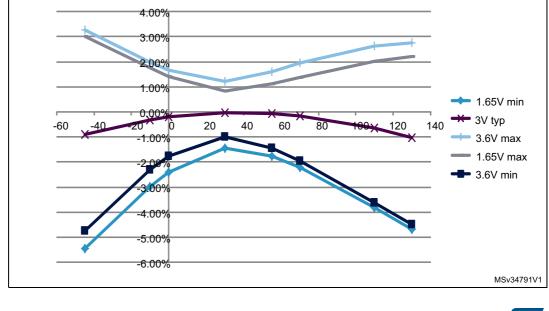

## 6.3.7 Internal clock source characteristics

The parameters given in *Table 38* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 18*.

## High-speed internal 16 MHz (HSI16) RC oscillator

| Symbol                                | Parameter                                           | Conditions                                                           | Min               | Тур  | Max              | Unit |

|---------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI16</sub>                    | Frequency                                           | V <sub>DD</sub> = 3.0 V                                              | -                 | 16   | -                | MHz  |

| TRIM <sup>(1)(2)</sup>                | HSI16 user-                                         | Trimming code is not a multiple of 16                                | -                 | ±0.4 | 0.7              | %    |

|                                       | trimmed resolution                                  | Trimming code is a multiple of 16                                    | -                 | -    | ±1.5             | %    |

|                                       |                                                     | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                     | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

|                                       | Accuracy of the factory-calibrated HSI16 oscillator | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 0 to 55 °C                |                   | -    | 1.5              | %    |

| ACC                                   |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                              | -2                | -    | 2                | %    |

| ACC <sub>HSI16</sub>                  |                                                     | $V_{DDA}$ = 3.0 V, $T_{A}$ = -10 to 85 °C                            | -2.5              | -    | 2                | %    |

|                                       |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 105 °C                             | -4                | -    | 2                | %    |

|                                       |                                                     | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = -40 to 125 °C | -5.45             | -    | 3.25             | %    |

| t <sub>SU(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>startup time                    | -                                                                    | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>power consumption               | -                                                                    | -                 | 100  | 140              | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results, not tested in production.

3. Guaranteed by test in production.

#### Figure 23. HSI16 minimum and maximum value versus temperature

DocID027973 Rev 4

## 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 45*. They are based on the EMS levels and classes defined in application note AN1709.

| ; | Symbol            | Parameter                                                                                                                         | Conditions                                                                                                    | Level/<br>Class |

|---|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|

| ` | / <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP32, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2 | 3B              |

| \ | / <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP32, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4 | 4A              |

#### Table 45. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

|                            |                        |                                                   |                            |                                                   |                            | -                          |                             |                                                            |                                                           |  |  |  |

|----------------------------|------------------------|---------------------------------------------------|----------------------------|---------------------------------------------------|----------------------------|----------------------------|-----------------------------|------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

|                            |                        | R <sub>AIN</sub> max for<br>fast channels<br>(kΩ) |                            | $R_{AIN}$ max for standard channels (k $\Omega$ ) |                            |                            |                             |                                                            |                                                           |  |  |  |

| T <sub>s</sub><br>(cycles) | t <sub>S</sub><br>(μs) |                                                   | V <sub>DD</sub> ><br>2.7 V | V <sub>DD</sub> ><br>2.4 V                        | V <sub>DD</sub> ><br>2.0 V | V <sub>DD</sub> ><br>1.8 V | V <sub>DD</sub> ><br>1.75 V | V <sub>DD</sub> > 1.65 V<br>and<br>T <sub>A</sub> > -10 °C | V <sub>DD</sub> > 1.65 V<br>and<br>T <sub>A</sub> > 25 °C |  |  |  |

| 1.5                        | 0.09                   | 0.5                                               | < 0.1                      | NA                                                | NA                         | NA                         | NA                          | NA                                                         | NA                                                        |  |  |  |

| 3.5                        | 0.22                   | 1                                                 | 0.2                        | < 0.1                                             | NA                         | NA                         | NA                          | NA                                                         | NA                                                        |  |  |  |

| 7.5                        | 0.47                   | 2.5                                               | 1.7                        | 1.5                                               | < 0.1                      | NA                         | NA                          | NA                                                         | NA                                                        |  |  |  |

| 12.5                       | 0.78                   | 4                                                 | 3.2                        | 3                                                 | 1                          | NA                         | NA                          | NA                                                         | NA                                                        |  |  |  |

| 19.5                       | 1.22                   | 6.5                                               | 5.7                        | 5.5                                               | 3.5                        | NA                         | NA                          | NA                                                         | < 0.1                                                     |  |  |  |

| 39.5                       | 2.47                   | 13                                                | 12.2                       | 12                                                | 10                         | NA                         | NA                          | NA                                                         | 5                                                         |  |  |  |

| 79.5                       | 4.97                   | 27                                                | 26.2                       | 26                                                | 24                         | < 0.1                      | NA                          | NA                                                         | 19                                                        |  |  |  |

| 160.5                      | 10.03                  | 50                                                | 49.2                       | 49                                                | 47                         | 32                         | < 0.1                       | < 0.1                                                      | 42                                                        |  |  |  |

Table 55.  $R_{AIN}$  max for  $f_{ADC}$  = 16 MHz<sup>(1)</sup>

1. Guaranteed by design.

# Table 56. ADC $accuracy^{(1)(2)(3)(4)}$

| Symbol                                             | Parameter                                                                          | Conditions                               | Min  | Тур  | Мах   | Unit |

|----------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------|------|------|-------|------|

| ET                                                 | Total unadjusted error                                                             |                                          | -    | 2    | 4     |      |

| EO                                                 | Offset error                                                                       |                                          | -    | 1    | 2.5   |      |

| EG                                                 | Gain error                                                                         |                                          | -    | 1    | 2     | LSB  |

| EL                                                 | Integral linearity error                                                           |                                          | -    | 1.5  | 2.5   |      |

| ED                                                 | Differential linearity error                                                       |                                          | -    | 1    | 1.5   |      |

|                                                    | Effective number of bits                                                           | 1.65 V < V <sub>DDA</sub> < 3.6 V, range | 10.2 | 11   |       |      |

| ENOB                                               | Effective number of bits (16-bit mode oversampling with ratio =256) <sup>(5)</sup> | 1/2/3, except for TSSOP14<br>package     | 11.3 | 12.1 | -     | bits |

| SINAD                                              | Signal-to-noise distortion                                                         |                                          | 62   | 67.8 | -     |      |

|                                                    | Signal-to-noise ratio                                                              |                                          | 63   | 68   | -     |      |

| ET<br>EO<br>EG<br>EL<br>ED<br>ENOB<br>SINAD<br>SNR | Signal-to-noise ratio (16-bit mode oversampling with ratio =256) <sup>(5)</sup>    |                                          | 70   | 76   | -     | dB   |

| THD                                                | Total harmonic distortion                                                          |                                          | -    | -81  | -68.5 |      |

# 6.3.17 Comparators

| Table 59. Comparator 1 characteristics |                                                                                     |                                                                                  |                    |     |                    |           |  |  |

|----------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|--|--|

| Symbol                                 | Parameter                                                                           | Conditions                                                                       | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |  |  |

| $V_{DDA}$                              | Analog supply voltage                                                               | -                                                                                | 1.65               |     | 3.6                | V         |  |  |

| R <sub>400K</sub>                      | R <sub>400K</sub> value                                                             | -                                                                                | -                  | 400 | -                  | kΩ        |  |  |

| R <sub>10K</sub>                       | R <sub>10K</sub> value                                                              | -                                                                                | -                  | 10  | -                  |           |  |  |

| V <sub>IN</sub>                        | Comparator 1 input voltage range                                                    | -                                                                                | 0.6                | -   | V <sub>DDA</sub>   | V         |  |  |

| t <sub>START</sub>                     | Comparator startup time                                                             | -                                                                                | -                  | 7   | 10                 |           |  |  |

| td                                     | Propagation delay <sup>(2)</sup>                                                    | -                                                                                | -                  | 3   | 10                 | μs        |  |  |

| V <sub>offset</sub>                    | Comparator offset <sup>(3)</sup>                                                    | -                                                                                | -                  | ±3  | ±10                | mV        |  |  |

| d <sub>Voffset</sub> /dt               | Comparator offset<br>variation in worst voltage<br>stress conditions <sup>(3)</sup> | $V_{DDA} = 3.6 V$<br>$V_{IN+} = 0 V$<br>$V_{IN-} = V_{REFINT}$<br>$T_A = 25 ° C$ | 0                  | 1.5 | 10                 | mV/1000 h |  |  |

| I <sub>COMP1</sub>                     | Current consumption <sup>(4)</sup>                                                  | -                                                                                | -                  | 160 | 260                | nA        |  |  |

Table 59. Comparator 1 characteristics

1. Guaranteed by characterization, not tested in production.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

In TSSOP14 package, where V<sub>DDA</sub> pin is shared with V<sub>DD</sub> pin, I/O toggling should be minimized to reach the values given in the above table. I/O toggling with loaded I/O pins can generate ripple on V<sub>DD</sub>/V<sub>DDA</sub> and degrade the comparator performance.

4. Comparator consumption only. Internal reference voltage not included.

## Table 60. Comparator 2 characteristics

| Symbol              | Parameter                                     | Conditions                                                                                                                  | Min  | Тур | Max <sup>(1)</sup> | Unit       |  |

|---------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------------|--|

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                           | 1.65 | -   | 3.6                | V          |  |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                           | 0    | -   | V <sub>DDA</sub>   | V          |  |

| t                   | Comparator startup time                       | Fast mode                                                                                                                   | -    | 15  | 20                 |            |  |

| t <sub>START</sub>  |                                               | Slow mode                                                                                                                   | -    | 20  | 25                 |            |  |

| t <sub>d slow</sub> | Propagation delay <sup>(2)</sup> in slow mode | $1.65 \text{ V} \leq \text{V}_{\text{DDA}} \leq 2.7 \text{ V}$                                                              | -    | 1.8 | 3.5                | μs         |  |

|                     | Fropagation delay 7 in slow mode              | $2.7 \text{ V} \leq \text{V}_{\text{DDA}} \leq 3.6 \text{ V}$                                                               | -    | 2.5 | 6                  |            |  |

| 4                   | Propagation delay <sup>(2)</sup> in fast mode | $1.65 \text{ V} \leq \text{V}_{\text{DDA}} \leq 2.7 \text{ V}$                                                              | -    | 0.8 | 2                  |            |  |

| t <sub>d fast</sub> |                                               | $2.7 \text{ V} \leq \text{V}_{\text{DDA}} \leq 3.6 \text{ V}$                                                               | -    | 1.2 | 4                  |            |  |

| V <sub>offset</sub> | Comparator offset error <sup>(3)</sup>        |                                                                                                                             | -    | ±4  | ±20                | mV         |  |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | $V_{DDA} = 3.3V$ $T_{A} = 0 \text{ to } 50 \circ C$ $V = V_{REFINT},$ $3/4 V_{REFINT},$ $1/2 V_{REFINT},$ $1/4 V_{REFINT}.$ | -    | 15  | 30                 | ppm<br>/°C |  |

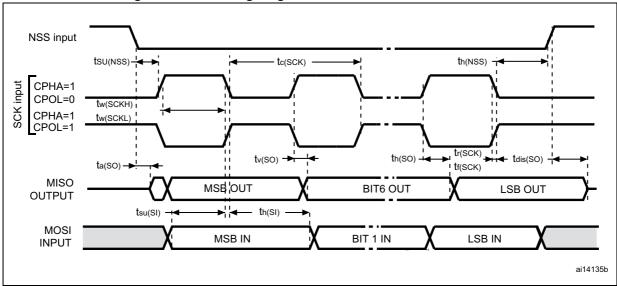

Figure 31. SPI timing diagram - slave mode and CPHA =  $1^{(1)}$

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

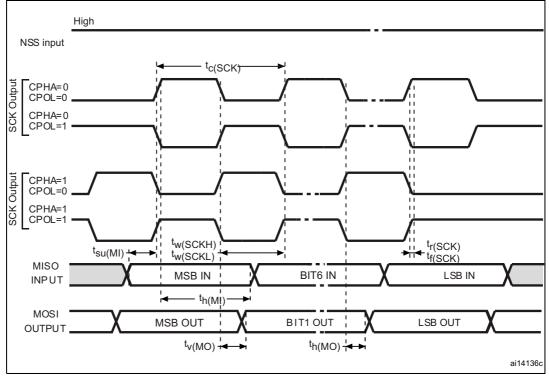

Figure 32. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

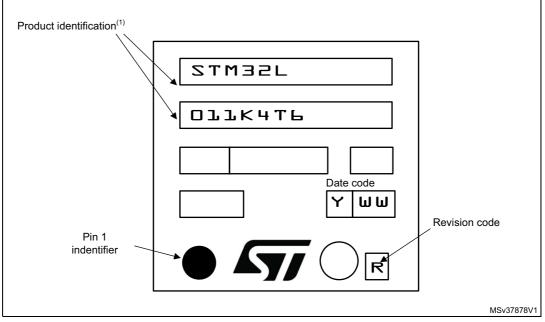

## LQFP32 device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

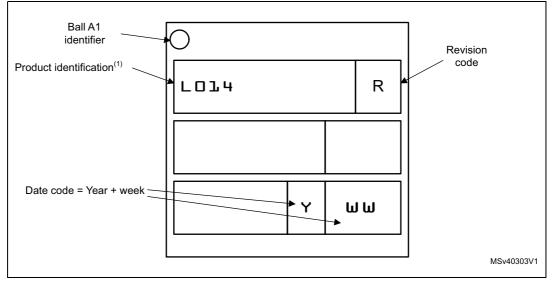

#### **Device marking**

The following figure gives an example of topside marking versus ball A1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 7.4 UFQFPN28 4 x 4 mm package information

Figure 42. UFQPN28, 4 x 4 mm, 28-pin package outline

1. Drawing is not to scale.

| Symbol | millimeters |       |       | inches |        |        |  |

|--------|-------------|-------|-------|--------|--------|--------|--|

|        | Min         | Тур   | Мах   | Min    | Тур    | Мах    |  |

| А      | 0.500       | 0.550 | 0.600 | 0.0197 | 0.0217 | 0.0236 |  |

| A1     | -           | 0.000 | 0.050 | -      | 0.0000 | 0.0020 |  |

| D      | 3.900       | 4.000 | 4.100 | 0.1535 | 0.1575 | 0.1614 |  |

| D1     | 2.900       | 3.000 | 3.100 | 0.1142 | 0.1181 | 0.1220 |  |

| E      | 3.900       | 4.000 | 4.100 | 0.1535 | 0.1575 | 0.1614 |  |

| E1     | 2.900       | 3.000 | 3.100 | 0.1142 | 0.1181 | 0.1220 |  |

| L      | 0.300       | 0.400 | 0.500 | 0.0118 | 0.0157 | 0.0197 |  |

| L1     | 0.250       | 0.350 | 0.450 | 0.0098 | 0.0138 | 0.0177 |  |

| Т      | -           | 0.152 | -     | -      | 0.0060 | -      |  |

| b      | 0.200       | 0.250 | 0.300 | 0.0079 | 0.0098 | 0.0118 |  |

| e      | -           | 0.500 | -     | -      | 0.0197 | -      |  |

### Table 72. UFQPN28, 4 x 4 mm, 28-pin package mechanical data<sup>(1)</sup>

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 7.5 UFQFPN20 package information

1. Drawing is not to scale.

| Table 74. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |

|-------------------------------------------------------------------------------------|

| package mechanical data (continued)                                                 |

| Symbol | millimeters |      |       | inches <sup>(1)</sup> |      |        |  |

|--------|-------------|------|-------|-----------------------|------|--------|--|

|        | Min.        | Тур. | Max.  | Min.                  | Тур. | Max.   |  |

| k      | 0°          | -    | 8°    | 0°                    | -    | 8°     |  |

| aaa    | -           | -    | 0.100 | -                     | -    | 0.0039 |  |

1. Values in inches are converted from mm and rounded to four decimal digits.

Figure 49. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, package footprint

1. Dimensions are expressed in millimeters.