# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                       |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 32MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                             |

| Number of I/O              | 26                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |

| Data Converters            | A/D 10x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l011k4t6d |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of figures

| Figure 1.  | STM32L011x3/4 block diagram                                                                                 | . 12 |

|------------|-------------------------------------------------------------------------------------------------------------|------|

| Figure 2.  | Clock tree                                                                                                  | . 23 |

| Figure 3.  | STM32L011x3/4 LQFP32 pinout                                                                                 | . 33 |

| Figure 4.  | STM32L011x3/4 UFQFPN32 pinout                                                                               | . 33 |

| Figure 5.  | STM32L011x3/4 WLCSP25 pinout                                                                                |      |

| Figure 6.  | STM32L011x3/4 UFQFPN28 pinout                                                                               | . 34 |

| Figure 7.  | STM32L011x3/4 UFQFPN20 pinout                                                                               | . 35 |

| Figure 8.  | STM32L011x3/4 TSSOP20 pinout                                                                                | . 35 |

| Figure 9.  | STM32L011x3/4 TSSOP14 pinout                                                                                | . 36 |

| Figure 10. | Memory map                                                                                                  | . 43 |

| Figure 11. | Pin loading conditions.                                                                                     | . 44 |

| Figure 12. | Pin input voltage                                                                                           | . 44 |

| Figure 13. | Power supply scheme.                                                                                        |      |

| Figure 14. | Current consumption measurement scheme                                                                      |      |

| Figure 15. | IDD vs VDD, at TA= 25 °C, Run mode, code running from                                                       |      |

| U          | Flash memory, Range 2, 16 MHz HSE, 1WS.                                                                     | . 54 |

| Figure 16. | IDD vs VDD, at TA= 25 °C, Run mode, code running from                                                       |      |

| U          | Flash memory, Range 2, HSI16, 1WS                                                                           | . 54 |

| Figure 17. | IDD vs VDD, at TA= -40/25/55/ 85/105/125 °C, Low-power run mode,                                            |      |

| U          | code running from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS                                               | . 58 |

| Figure 18. | IDD vs VDD, at TA= -40/25/55/ 85/105/125 °C, Stop mode with RTC enabled                                     |      |

| 0          | and running on LSE Low drive                                                                                | . 59 |

| Figure 19. | IDD vs VDD, at TA= -40/25/55/85/105/125 °C, Stop mode with RTC disabled,                                    |      |

| 0          | all clocks OFF                                                                                              | . 59 |

| Figure 20. | High-speed external clock source AC timing diagram                                                          |      |

| Figure 21. | Low-speed external clock source AC timing diagram                                                           |      |

| Figure 22. | Typical application with a 32.768 kHz crystal                                                               |      |

| Figure 23. | HSI16 minimum and maximum value versus temperature                                                          |      |

| Figure 24. | VIH/VIL versus VDD (CMOS I/Os)                                                                              |      |

| Figure 25. | VIH/VIL versus VDD (TTL I/Os)                                                                               |      |

| Figure 26. | I/O AC characteristics definition                                                                           |      |

| Figure 27. | Recommended NRST pin protection                                                                             |      |

| Figure 28. | ADC accuracy characteristics                                                                                |      |

| Figure 29. | Typical connection diagram using the ADC                                                                    | . 84 |

| Figure 30. | SPI timing diagram - slave mode and CPHA = 0                                                                | . 91 |

| Figure 31. | SPI timing diagram - slave mode and CPHA = 0<br>SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup> | . 92 |

| Figure 32. | SPI timing diagram - master mode <sup>(1)</sup>                                                             | . 92 |

| Figure 33. | LQFP32, 7 x 7 mm, 32-pin low-profile quad flat package outline                                              |      |

| Figure 34. | LQFP32 recommended footprint                                                                                |      |

| Figure 35. | Example of LQFP32 marking (package top view)                                                                |      |

| Figure 36. | UFQFPN32, 5 x 5 mm, 32-pin package outline                                                                  |      |

| Figure 37. | UFQFPN32 recommended footprint                                                                              |      |

| Figure 38. | Example of UFQFPN32 marking (package top view)                                                              |      |

| Figure 39. | WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale                                    |      |

| ga. 0 00.  | package outline.                                                                                            | . 98 |

| Figure 40. | WLCSP25 - 25-ball, 2.133 x 2.070 mm, 0.4 mm pitch wafer level chip scale                                    |      |

| ga.o .o.   | package recommended footprint                                                                               | 99   |

| Figure 41. | Example of WLCSP25 marking (package top view)                                                               | 100  |

|            |                                                                                                             |      |

## 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM<sup>®</sup> Cortex<sup>®</sup>-M4, including ARM<sup>®</sup> Cortex<sup>®</sup>-M3 and ARM<sup>®</sup> Cortex<sup>®</sup>-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 Ultra-low-power series are the best solution for applications such as gas/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power Run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

## **3** Functional overview

### 3.1 Low-power modes

The ultra-low-power STM32L011x3/4 supports dynamic voltage scaling to optimize its power consumption in Run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply.

There are three power consumption ranges:

- Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), with the CPU running at up to 32 MHz

- Range 2 (full V<sub>DD</sub> range), with a maximum CPU frequency of 16 MHz

- Range 3 (full V<sub>DD</sub> range), with a maximum CPU frequency limited to 4.2 MHz

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs. Sleep mode power consumption at 16 MHz is about 1 mA with all peripherals off.

#### Low-power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the lowspeed clock (max 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In Lowpower run mode, the clock frequency and the number of enabled peripherals are both limited.

#### • Low-power sleep mode

This mode is achieved by entering Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In Low-power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the Run mode with the regulator on.

#### • Stop mode with RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSE and HSI RC oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event

## 3.6 Low-power real-time clock and backup registers

The real time clock (RTC) and the 5 backup registers are supplied in all modes including standby mode. The backup registers are five 32-bit registers used to store 20 bytes of user application data. They are not reset by a system reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- Automatically correction for 28, 29 (leap year), 30, and 31 day of the month

- Two programmable alarms with wake up from Stop and Standby mode capability

- Periodic wakeup from Stop and Standby with programmable resolution and period

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- 2 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 37 kHz)

- The high-speed external clock

## 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated alternate function registers. All GPIOs are high current capable. Each GPIO output, speed can be slowed (40 MHz, 10 MHz, 2 MHz, 400 kHz). The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to a dedicated IO bus with a toggling speed of up to 32 MHz.

The BOOT0 pin is shared with PB9 GPIO pin. This pin is an input-only pin. If nBOOT\_SEL option bit is reset, sampling this pin on NRST rising edge gives the internal BOOT0 state. This pin then works as PB9 pin. The input voltage characteristics of this pin are specific for BOOT0 pin type (see *Table 50: I/O static characteristics*).

#### Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 26 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event

## 3.12 Ultra-low-power comparators and reference voltage

The STM32L011x3/4 embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with ultra low consumption

- One comparator with rail-to-rail inputs, fast or slow mode.

- The threshold can be one of the following:

- External I/O pins

- Internal reference voltage (V<sub>REFINT</sub>)

- submultiple of Internal reference voltage(1/4, 1/2, 3/4) for the rail to rail comparator.

Both comparators can wake up the devices from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

## 3.13 System configuration controller

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM21 and LPTIM1 timer input captures. It also controls the routing of internal analog signals to the ADC, COMP1 and COMP2 and the internal reference voltage  $V_{\text{REFINT}}$ .

## 3.14 Timers and watchdogs

The ultra-low-power STM32L011x3/4 devices include two general-purpose timers, one low-power timer (LPTIM1), two watchdog timers and the SysTick timer.

*Table 7* compares the features of the general-purpose and basic timers.

| Timer | Counter resolution | Counter type         | Prescaler factor                   | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |

|-------|--------------------|----------------------|------------------------------------|------------------------------|-----------------------------|--------------------------|

| TIM2  | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | Yes                          | 4                           | No                       |

| TIM21 | 16-bit             | Up, down,<br>up/down | Any integer between<br>1 and 65536 | No                           | 2                           | No                       |

Table 7. Timer feature comparison

#### 3.14.1 General-purpose timers (TIM2, TIM21)

There are three synchronizable general-purpose timers embedded in the STM32L011x3/4 devices (see *Table 7* for differences).

#### TIM2

TIM2 is based on 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It features four independent channels each for input capture/output compare, PWM or one-pulse mode output.

The TIM2 general-purpose timers can work together or with the TIM21 general-purpose timer via the Timer Link feature for synchronization or event chaining. Its counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2 has independent DMA request generation.

This timer is capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### TIM21

TIM21 is based on a 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It has two independent channels for input capture/output compare, PWM or one-pulse mode output. It can work together and be synchronized with TIM2 full-featured general-purpose timer.

It can also be used as simple timebase and be clocked by the LSE clock source (32.768 kHz) to provide independent timebase from the main CPU clock.

#### 3.14.2 Low-power Timer (LPTIM)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one shot mode

- Selectable software / hardware input trigger

- Selectable clock source

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM1 input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

#### 3.14.3 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit downcounter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches '0'.

DocID027973 Rev 4

| I2C features <sup>(1)</sup>                                  | I2C1             |

|--------------------------------------------------------------|------------------|

| 7-bit addressing mode                                        | Х                |

| 10-bit addressing mode                                       | Х                |

| Standard mode (up to 100 kbit/s)                             | Х                |

| Fast mode (up to 400 kbit/s)                                 | X                |

| Fast Mode Plus with 20 mA output drive I/Os (up to 1 Mbit/s) | X <sup>(2)</sup> |

| Independent clock                                            | Х                |

| SMBus                                                        | X                |

| Wakeup from STOP                                             | X                |

| Tahlo | a  | STM32I   | 011-2/1 | 1 <sup>2</sup> C | implementation |

|-------|----|----------|---------|------------------|----------------|

| lane  | э. | STIVISZL | 01123/4 | 10               | implementation |

1. X = supported.

2. See Table 13: Pin definitions on page 37 for the list of I/Os that feature Fast Mode Plus capability

#### 3.15.2 Universal synchronous/asynchronous receiver transmitter (USART)

The USART interface (USART2) is able to communicate at speeds of up to 4 Mbit/s.

It provides hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode and single-wire half-duplex communication mode. USART2 also supports Smartcard communication (ISO 7816, T=0 protocol) and IrDA SIR ENDEC.

USART2 interface can be served by the DMA controller.

*Table 10* for the supported modes and features of USART interface.

| USART modes/features <sup>(1)</sup>         | USART2 |

|---------------------------------------------|--------|

| Hardware flow control for modem             | Х      |

| Continuous communication using DMA          | Х      |

| Multiprocessor communication                | Х      |

| Synchronous mode                            | -      |

| Smartcard mode                              | Х      |

| Single-wire half-duplex communication       | Х      |

| IrDA SIR ENDEC block                        | Х      |

| LIN mode                                    | -      |

| Dual clock domain and wakeup from Stop mode | -      |

| Receiver timeout interrupt                  | -      |

| Modbus communication                        | -      |

| Auto baud rate detection (4 modes)          | -      |

| Driver Enable                               | Х      |

#### Table 10. USART implementation

1. X = supported.

|         |          | Pin     | num      | ber    |                         |         |                                       |          |               |       | Pin functions                                                     |                                  |  |

|---------|----------|---------|----------|--------|-------------------------|---------|---------------------------------------|----------|---------------|-------|-------------------------------------------------------------------|----------------------------------|--|

| TSSOP14 | UFQFPN20 | TSSOP20 | UFQFPN28 | LQFP32 | UFQFPN32 <sup>(1)</sup> | WLCSP25 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                               | Additional<br>functions          |  |

| -       | -        | -       | 26       | 28     | 28                      | -       | PB5                                   | I/O      | FT            | -     | SPI1_MOSI,<br>LPTIM1_IN1,<br>I2C1_SMBA,<br>TIM21_CH1              | COMP2_INP                        |  |

| -       | 18       | -       | 27       | 29     | 29                      | A3      | PB6                                   | I/O      | FTf           | -     | USART2_TX,<br>I2C1_SCL,<br>LPTIM1_ETR,<br>TIM2_CH3,<br>LPUART1_TX | COMP2_INP                        |  |

| -       | 19       | -       | 28       | 30     | 30                      | A4      | PB7                                   | I/O      | FTf           | -     | USART2_RX,<br>I2C1_SDA,<br>LPTIM1_IN2,<br>TIM2_CH4,<br>LPUART1_RX | COMP2_INP,<br>VREF_PVD_IN        |  |

| 1       | 20       | 1       | 1        | 31     | 31                      | A5      | PB9-BOOT0                             | I        | В             | -     | -                                                                 | BOOT0 (Boot<br>memory selection) |  |

| -       | -        | -       | -        | -      | 32                      | -       | PB8                                   | I/O      | FTf           | -     | USART2_TX,<br>EVENTOUT,<br>I2C1_SCL,<br>SPI1_NSS                  | -                                |  |

| -       | -        | -       | -        | 32     | -                       | -       | VSS                                   | S        | I             | (5)   | -                                                                 | -                                |  |

| -       | -        | -       | -        | 1      | 1                       | -       | VDD                                   | S        | -             | (6)   | -                                                                 | -                                |  |

1. V<sub>SS</sub> pins are connected to the exposed pad (see *Figure 36: UFQFPN32, 5 x 5 mm, 32-pin package outline*).

2. Device reset input/internal reset output (active low).

3. Analog power supply.

4. On TSSOP14 package,  $V_{DDA}$  is internally connected to  $V_{DD}$ .

5. Digital and analog ground.

6. Digital power supply.

| Symbol            | Parameter                     | Conditions                                | Min  | Тур  | Мах  | Unit |

|-------------------|-------------------------------|-------------------------------------------|------|------|------|------|

| M                 | Brown-out reset threshold 3   | Falling edge                              | 2.45 | 2.55 | 2.6  |      |

| V <sub>BOR3</sub> | Brown-out reset threshold 5   | Rising edge                               | 2.54 | 2.66 | 2.7  |      |

| M.                | Brown-out reset threshold 4   | Falling edge                              | 2.68 | 2.8  | 2.85 |      |

| V <sub>BOR4</sub> | Brown-out reset threshold 4   | Rising edge                               | 2.78 | 2.9  | 2.95 |      |

| V                 | Programmable voltage detector | Falling edge                              | 1.8  | 1.85 | 1.88 |      |

| V <sub>PVD0</sub> | threshold 0                   | Rising edge                               | 1.88 | 1.94 | 1.99 |      |

| V                 | PVD threshold 1               | Falling edge                              | 1.98 | 2.04 | 2.09 |      |

| V <sub>PVD1</sub> |                               | Rising edge                               | 2.08 | 2.14 | 2.18 |      |

| N/                | PVD threshold 2               | Falling edge                              | 2.20 | 2.24 | 2.28 | v    |

| V <sub>PVD2</sub> |                               | Rising edge                               | 2.28 | 2.34 | 2.38 | v    |

| V <sub>PVD3</sub> | PVD threshold 3               | Falling edge                              | 2.39 | 2.44 | 2.48 |      |

|                   |                               | Rising edge                               | 2.47 | 2.54 | 2.58 |      |

| V                 | PVD threshold 4               | Falling edge                              | 2.57 | 2.64 | 2.69 |      |

| V <sub>PVD4</sub> |                               | Rising edge                               | 2.68 | 2.74 | 2.79 |      |

| V                 | PVD threshold 5               | Falling edge                              | 2.77 | 2.83 | 2.88 |      |

| V <sub>PVD5</sub> |                               | Rising edge                               | 2.87 | 2.94 | 2.99 |      |

| V                 | PVD threshold 6               | Falling edge                              | 2.97 | 3.05 | 3.09 |      |

| V <sub>PVD6</sub> |                               | Rising edge                               | 3.08 | 3.15 | 3.20 |      |

| V <sub>hyst</sub> |                               | BOR0 threshold                            | -    | 40   | -    |      |

|                   | Hysteresis voltage            | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 19. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results, not tested in production.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

| Symbol                                                                                 | Parameter  | Co                                                    | f <sub>HCLK</sub>                                  | Тур     | Max <sup>(1)</sup> | Unit |    |

|----------------------------------------------------------------------------------------|------------|-------------------------------------------------------|----------------------------------------------------|---------|--------------------|------|----|

|                                                                                        |            |                                                       |                                                    | 1 MHz   | 140                | 180  |    |

|                                                                                        |            |                                                       | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0]=11   | 2 MHz   | 245                | 290  | μA |

|                                                                                        |            |                                                       |                                                    | 4 MHz   | 460                | 540  |    |

|                                                                                        |            | f <sub>HSE</sub> = f <sub>HCLK</sub> up to            |                                                    | 4 MHz   | 0.56               | 0.65 |    |

|                                                                                        |            | 16 MHz included,<br>$f_{HSE} = f_{HCLK}/2$ above      | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 8 MHz   | 1.1                | 1.3  |    |

| Supply<br>I <sub>DD</sub> current in<br>(Run Run mode,<br>from code<br>Flash) executed | Quantu     | Supply<br>Current in<br>Run mode,<br>code<br>executed |                                                    | 16 MHz  | 2.1                | 2.4  | mA |

|                                                                                        |            |                                                       | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01  | 8 MHz   | 1.3                | 1.6  |    |

|                                                                                        |            |                                                       |                                                    | 16 MHz  | 2.6                | 3    |    |

|                                                                                        |            |                                                       |                                                    | 32 MHz  | 5.3                | 6.5  |    |

|                                                                                        | from Flash |                                                       | Range 3, V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11  | 65 kHz  | 34.5               | 54   |    |

|                                                                                        |            |                                                       |                                                    | 524 kHz | 86                 | 120  | μA |

|                                                                                        |            |                                                       |                                                    | 4.2 MHz | 505                | 560  | 7  |

|                                                                                        |            | HSI clock                                             | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 16 MHz  | 2.2                | 2.6  |    |

|                                                                                        |            |                                                       | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01  | 32 MHz  | 5.4                | 5.9  | mA |

| <b>T</b> 1 1 00 0 1      |                                  |                                  |

|--------------------------|----------------------------------|----------------------------------|

| Table 22. Current consum | ption in Run mode, code with dat | ta processing running from Flash |

1. Guaranteed by characterization results at 125 °C, not tested in production, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Table 23. Current consumption in Run mode vs code type, |

|---------------------------------------------------------|

| code with data processing running from Flash            |

| Symbol                                                 | Parameter                             |                                                                                                                | Conditions                            |                           |        |      | Unit     |

|--------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------|--------|------|----------|

|                                                        |                                       |                                                                                                                |                                       | Dhrystone                 |        | 460  | μA<br>mA |

| Supply<br>I <sub>DD</sub> current in<br>(Run Run mode, |                                       |                                                                                                                |                                       | CoreMark                  |        | 440  |          |

|                                                        |                                       |                                                                                                                | Range 3,<br>V <sub>CORE</sub> =1.2 V, | Fibonacci                 | 4 MHz  | 330  |          |

|                                                        | Cumple                                | upply<br>irrent in $f_{HSE} = f_{HCLK}$ up to<br>un mode, 16 MHz included,<br>ode $f_{HSE} = f_{HCLK}/2$ above | VOS[1:0]=11                           | while(1)                  |        | 305  |          |

|                                                        | current in f<br>Run mode, 1<br>code f |                                                                                                                |                                       | while(1), prefetch<br>OFF |        | 320  |          |

| from<br>Flash)                                         |                                       |                                                                                                                |                                       | Dhrystone                 |        | 5.4  |          |

| 1 (4511)                                               |                                       |                                                                                                                |                                       | CoreMark                  | 32 MHz | 4.9  |          |

|                                                        |                                       |                                                                                                                | Range 1,<br>VOS[1:0]=01,              | Fibonacci                 |        | 5    |          |

|                                                        |                                       |                                                                                                                | V <sub>CORE</sub> =1.8 V              | while(1)                  |        | 4.35 |          |

|                                                        |                                       |                                                                                                                |                                       | while(1), prefetch<br>OFF |        | 3.7  |          |

1. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol                  | Parameter               | Conc                                                                                                                | litions                                              | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit         |

|-------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------|------|--------------------|--------------|

|                         |                         |                                                                                                                     | Range 3,                                             | 1 MHz             | 36.5 | 70                 |              |

|                         |                         |                                                                                                                     | V <sub>CORE</sub> =1.2 V,                            | 2 MHz             | 58   | 95                 |              |

|                         |                         |                                                                                                                     | VOS[1:0]=11                                          | 4 MHz             | 100  | 150                |              |

|                         |                         | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,                                                      | Range 2,                                             | 4 MHz             | 125  | 170                |              |

|                         |                         | $f_{HSE} = f_{HCLK}/2$                                                                                              | V <sub>CORE</sub> =1.5 V,                            | 8 MHz             | 230  | 300                |              |

|                         |                         | above 16 MHz<br>(PLL ON) <sup>(2)</sup>                                                                             | VOS[1:0]=10                                          | 16 MHz            | 450  | 540                |              |

|                         |                         |                                                                                                                     | Range 1,                                             | 8 MHz             | 275  | 350                |              |

|                         | Supply current in Sleep |                                                                                                                     | V <sub>CORE</sub> =1.8 V,                            | 16 MHz            | 555  | 650                |              |

|                         | mode, Flash             |                                                                                                                     | VOS[1:0]=01                                          | 32 MHz            | 1350 | 1600               |              |

|                         | OFF                     |                                                                                                                     | Range 3,                                             | 65 kHz            | 15.5 | 32                 |              |

|                         |                         | MSI clock                                                                                                           | V <sub>CORE</sub> =1.2 V,                            | 524 kHz           | 26.5 | 55                 |              |

|                         |                         |                                                                                                                     | VOS[1:0]=11                                          | 4.2 MHz           | 115  | 160                |              |

|                         |                         | HSI16 clock source<br>(16 MHz)                                                                                      | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10 | 16 MHz            | 585  | 670                |              |

|                         |                         |                                                                                                                     | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 1500 | 1700               | - μA<br><br> |

| I <sub>DD</sub> (Sleep) |                         | $f_{HSE} = f_{HCLK}$ up to<br>16 MHz included,<br>$f_{HSE} = f_{HCLK}/2$<br>above 16 MHz (PLL<br>ON) <sup>(2)</sup> | Range 3,<br>V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11 | 1 MHz             | 49   | 88                 |              |

|                         |                         |                                                                                                                     |                                                      | 2 MHz             | 69   | 120                |              |

|                         |                         |                                                                                                                     |                                                      | 4 MHz             | 115  | 190                |              |

|                         |                         |                                                                                                                     | Range 2,<br><sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10   | 4 MHz             | 135  | 200                |              |

|                         |                         |                                                                                                                     |                                                      | 8 MHz             | 240  | 340                |              |

|                         |                         |                                                                                                                     |                                                      | 16 MHz            | 460  | 650                |              |

|                         |                         |                                                                                                                     | Range 1,                                             | 8 MHz             | 290  | 400                |              |

|                         | Supply current          |                                                                                                                     | V <sub>CORE</sub> =1.8 V,                            | 16 MHz            | 565  | 750                | -            |

|                         | in Sleep<br>mode, Flash |                                                                                                                     | VOS[1:0]=01                                          | 32 MHz            | 1350 | 1900               | -            |

|                         | ON                      |                                                                                                                     | Range 3,                                             | 65 kHz            | 26.5 | 46                 | -            |

|                         |                         | MSI clock                                                                                                           | V <sub>CORE</sub> =1.2 V,                            | 524 kHz           | 38.5 | 70                 |              |

|                         |                         |                                                                                                                     | VOS[1:0]=11                                          | 4.2 MHz           | 125  | 190                |              |

|                         |                         | HSI16 clock source                                                                                                  | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10 | 16 MHz            | 600  | 760                |              |

|                         |                         | (16 MHz)                                                                                                            | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 1500 | 1850               |              |

1. Guaranteed by characterization results at 125 °C, not tested in production, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol          | Parameter                                     |                                     | Conditions                                        |                                         | Тур  | Max <sup>(1)</sup> | Unit                       |

|-----------------|-----------------------------------------------|-------------------------------------|---------------------------------------------------|-----------------------------------------|------|--------------------|----------------------------|

|                 |                                               |                                     |                                                   | $T_A$ = -40 °C to 25 °C                 | 5.7  | 8.1                |                            |

|                 |                                               |                                     | MSI clock, 65 kHz                                 | T <sub>A</sub> = 85 °C                  | 6.5  | 9                  |                            |

|                 |                                               |                                     | f <sub>HCLK</sub> = 32 kHz                        | T <sub>A</sub> = 105 °C                 | 8    | 13                 |                            |

|                 |                                               | All                                 |                                                   | T <sub>A</sub> = 125 °C                 | 11.5 | 22                 |                            |

|                 |                                               | peripherals<br>OFF, code            |                                                   | $T_A = -40 \degree C$ to 25 $\degree C$ | 8.7  | 11                 |                            |

|                 |                                               | executed                            | MSI clock, 65 kHz                                 | T <sub>A</sub> = 85 °C                  | 9.5  | 12                 |                            |

|                 |                                               | from RAM,<br>Flash                  | f <sub>HCLK</sub> = 65 kHz                        | T <sub>A</sub> = 105 °C                 | 11   | 15                 |                            |

|                 |                                               | switched                            |                                                   | T <sub>A</sub> = 125 °C                 | 15   | 24                 |                            |

|                 |                                               | OFF, V <sub>DD</sub><br>from 1.65 V |                                                   | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$ | 17   | 19                 |                            |

|                 | Supply<br>current in<br>Low-power<br>run mode | to 3.6 V                            | MSI clock, 131 kHz<br>f <sub>HCLK</sub> = 131 kHz | T <sub>A</sub> = 55 °C                  | 17   | 19.5               | -<br>-<br>-<br>-<br>-<br>- |

|                 |                                               |                                     |                                                   | T <sub>A</sub> = 85 °C                  | 17.5 | 20                 |                            |

|                 |                                               |                                     |                                                   | T <sub>A</sub> = 105 °C                 | 19   | 22                 |                            |

| I <sub>DD</sub> |                                               |                                     |                                                   | T <sub>A</sub> = 125 °C                 | 22.5 | 31                 |                            |

| (LP Run)        |                                               |                                     | MSI clock, 65 kHz<br>f <sub>HCLK</sub> = 32 kHz   | $T_A$ = -40 °C to 25 °C                 | 18   | 22                 |                            |

|                 |                                               |                                     |                                                   | T <sub>A</sub> = 85 °C                  | 20   | 24                 |                            |

|                 |                                               |                                     |                                                   | T <sub>A</sub> = 105 °C                 | 22   | 27                 |                            |

|                 |                                               |                                     |                                                   | T <sub>A</sub> = 125 °C                 | 26.5 | 37                 |                            |

|                 |                                               | All<br>peripherals                  |                                                   | $T_A$ = -40 °C to 25 °C                 | 22   | 25                 | 1                          |

|                 |                                               | OFF, code                           | MSI clock, 65 kHz                                 | T <sub>A</sub> = 85 °C                  | 24   | 27                 |                            |

|                 |                                               | executed from Flash,                | f <sub>HCLK</sub> = 65 kHz                        | T <sub>A</sub> = 105 °C                 | 26   | 30                 | 1                          |

|                 |                                               | V <sub>DD</sub> from                |                                                   | T <sub>A</sub> = 125 °C                 | 30.5 | 39                 |                            |

|                 |                                               | 1.65 V to<br>3.6 V                  |                                                   | $T_A$ = -40 °C to 25 °C                 | 32   | 34                 | -                          |

|                 |                                               |                                     |                                                   | T <sub>A</sub> = 55 °C                  | 32.5 | 35                 |                            |

|                 |                                               |                                     | MSI clock, 131 kHz<br>f <sub>HCLK</sub> = 131 kHz | T <sub>A</sub> = 85 °C                  | 34   | 37                 |                            |

|                 |                                               |                                     | HOEK                                              | T <sub>A</sub> = 105 °C                 | 36   | 39                 |                            |

|                 |                                               |                                     |                                                   | T <sub>A</sub> = 125 °C                 | 40   | 47                 |                            |

| Table 27. Current consumption | n in Low-power Run mode |

|-------------------------------|-------------------------|

|-------------------------------|-------------------------|

1. Guaranteed by characterization results at 125 °C, not tested in production, unless otherwise specified.

| Symbol                     | Peripheral           | Typical consum         | Unit                   |        |  |

|----------------------------|----------------------|------------------------|------------------------|--------|--|

| Symbol                     | Peripheral           | V <sub>DD</sub> =1.8 V | V <sub>DD</sub> =3.0 V | – Unit |  |

| I <sub>DD(PVD / BOR)</sub> | -                    | 0.6                    | 1                      |        |  |

| I <sub>REFINT</sub>        | -                    | 1.25                   | 1.3                    |        |  |

| -                          | LSE Low drive        | 0.11                   | 0.16                   |        |  |

| -                          | LPTIM1, Input 100 Hz | 0.01                   | 0.02                   | μΑ     |  |

| -                          | LPTIM1, Input 1 MHz  | 8                      | 9                      |        |  |

| -                          | LPUART1              | 0.025                  | 0.027                  |        |  |

| -                          | RTC                  | 0.1                    | 0.19                   | 1      |  |

Table 33. Peripheral current consumption in Stop and Standby mode

#### 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 18*.

| Symbol               | Parameter                         | Conditions                                        | Тур | Max | Unit          |

|----------------------|-----------------------------------|---------------------------------------------------|-----|-----|---------------|

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode            | f <sub>HCLK</sub> = 32 MHz                        | 7   | 8   |               |

| twusleep_lp          | Wakeup from Low-power sleep mode, | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled      | 7   | 8   | CPU<br>cvcles |

|                      |                                   | f <sub>HCLK</sub> = 262 kHz<br>Flash switched OFF | 9   | 10  | - <b>,</b>    |

Table 34. Low-power mode wakeup timings

| Symbol               | Parameter                                                                               | Conditions                                                        | Тур  | Мах | Unit |

|----------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|-----|------|

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 5.1  | 8   |      |

|                      | Wakeup from Stop mode, regulator in Run mode                                            | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 5.1  | 7   |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.1  | 11  |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 1 | 5    | 8   |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 2 | 5    | 8   |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 5    | 8   |      |

|                      | Wakeup from Stop mode, regulator in<br>low-power mode                                   | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 7.4  | 13  |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 14   | 23  |      |

| t <sub>WUSTOP</sub>  |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                    | 28   | 38  |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 51   | 65  | μs   |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 99   | 120 |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 65 kHz                     | 196  | 260 | -    |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 5.1  | 7   |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.2  | 11  |      |

|                      | Wakeup from Stop mode, regulator in<br>low-power mode, HSI kept running in<br>Stop mode | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 3.25 | -   |      |

|                      | Wakeup from Stop mode, regulator in                                                     | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9  | 7   |      |

|                      | low-power mode, code running from                                                       | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 7.9  | 10  |      |

|                      | RAM                                                                                     | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 4.8  | 8   |      |

| t                    | Wakeup from Standby mode<br>FWU bit = 1                                                 | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 65   | 130 |      |

| <sup>t</sup> wustdby | Wakeup from Standby mode<br>FWU bit = 0                                                 | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 2.2  | 3   | ms   |

Table 34. Low-power mode wakeup timings (continued)

## Low-speed internal (LSI) RC oscillator

| Table | 39. | LSI | oscillator | characteristics |

|-------|-----|-----|------------|-----------------|

| 10010 |     |     | 0001110101 |                 |

| Symbol                              | Parameter                                                             | Min | Тур | Max | Unit |

|-------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                         | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \le T_{A} \le 85^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                           | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                      | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design, not tested in production.

#### Multi-speed internal (MSI) RC oscillator

| Symbol                                | Parameter                                                                                            | Condition   | Тур  | Max | Unit  |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------|-------------|------|-----|-------|--|

| Symbol                                | Falameter                                                                                            | Condition   | -    | Wax | Unit  |  |

|                                       |                                                                                                      | MSI range 0 | 65.5 | -   |       |  |

|                                       |                                                                                                      | MSI range 1 | 131  | -   | kHz   |  |

|                                       |                                                                                                      | MSI range 2 | 262  | -   | KI IZ |  |

| f <sub>MSI</sub>                      | Frequency after factory calibration, done at $V_{DD}$ = 3.3 V and T <sub>A</sub> = 25 °C             | MSI range 3 | 524  | -   |       |  |

|                                       |                                                                                                      | MSI range 4 | 1.05 | -   |       |  |

|                                       |                                                                                                      | MSI range 5 | 2.1  | -   | MHz   |  |

|                                       |                                                                                                      | MSI range 6 | 4.2  | -   |       |  |

| ACC <sub>MSI</sub>                    | Frequency error after factory calibration                                                            | -           | ±0.5 | -   | %     |  |

| D <sub>TEMP(MSI)</sub> <sup>(1)</sup> | MSI oscillator frequency drift $0 \text{ °C} \leq T_A \leq 85 \text{ °C}$                            | -           | ±3   | -   | %     |  |

| D <sub>VOLT(MSI)</sub> <sup>(1)</sup> | MSI oscillator frequency drift<br>1.65 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, T <sub>A</sub> = 25 °C | -           | -    | 2.5 | %/V   |  |

|                                       |                                                                                                      | MSI range 0 | 0.75 | -   |       |  |

|                                       |                                                                                                      | MSI range 1 | 1    | -   |       |  |

|                                       |                                                                                                      | MSI range 2 | 1.5  | -   |       |  |

| I <sub>DD(MSI)</sub> <sup>(2)</sup>   | MSI oscillator power consumption                                                                     | MSI range 3 | 2.5  | -   | μA    |  |

|                                       |                                                                                                      | MSI range 4 | 4.5  | -   |       |  |

|                                       |                                                                                                      | MSI range 5 | 8    | -   |       |  |

|                                       |                                                                                                      | MSI range 6 | 15   | -   |       |  |

#### Table 40. MSI oscillator characteristics

#### Flash memory and data EEPROM

| Symbol            | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |  |  |

|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|--|--|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |  |  |

| t <sub>prog</sub> | Programming time for                                                           | Erasing                                         | -    | 3.28 | 3.94               |      |  |  |

|                   | word or half-page                                                              | Programming                                     | -    | 3.28 | 3.94               | ms   |  |  |

| I <sub>DD</sub>   | Average current during<br>the whole programming /<br>erase operation           |                                                 | -    | 500  | 700                | μA   |  |  |

|                   | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |  |  |

Table 43. Flash memory and data EEPROM characteristics

1. Guaranteed by design, not tested in production.

| Cumb al                         | Donomotor                                                                      | Conditions                                            | Value              | Unit    |  |

|---------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------|--------------------|---------|--|

| Symbol                          | Parameter                                                                      | Conditions                                            | Min <sup>(1)</sup> |         |  |

|                                 | Cycling (erase / write)<br>Program memory                                      | T <sub>A</sub> = -40°C to 105 °C                      | 10                 | kcycles |  |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>EEPROM data memory                                  |                                                       | 100                |         |  |

| INCYC <sup>1</sup>              | Cycling (erase / write)<br>Program memory                                      | - T <sub>A</sub> = -40°C to 125 °C                    | 0.2                |         |  |

|                                 | Cycling (erase / write)<br>EEPROM data memory                                  | $T_{A} = -40 \ \text{C} \ \text{10} \ 123 \ \text{C}$ | 2                  |         |  |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C  | • T <sub>RET</sub> = +85 °C                           | 30                 | years   |  |

|                                 | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 85 \text{ °C}$ | TRET - 105 C                                          | 30                 |         |  |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C | -Т <sub>вет</sub> = +105 °С                           | - 10               |         |  |

| 'RET` '                         | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 105$ °C        | TRET - +103 C                                         |                    |         |  |

|                                 | Data retention (program memory) after<br>200 cycles at T <sub>A</sub> = 125 °C | -T <sub>RET</sub> = +125 °C                           |                    |         |  |

|                                 | Data retention (EEPROM data memory) after 2 kcycles at $T_A$ = 125 °C          | TRET - TIZS C                                         |                    |         |  |

| Table 44. Flash memor | y and data EEPROM endurance and retention |

|-----------------------|-------------------------------------------|

1. Guaranteed by characterization results, not tested in production.

2. Characterization is done according to JEDEC JESD22-A117.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                             | Monitored<br>frequency band | Max vs. frequency range<br>(32 MHz voltage Range 1) | Unit |  |

|------------------|------------|----------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------|------|--|

|                  |            | $V_{DD} = 3.3 V,$<br>$T_A = 25 °C,$<br>LQFP32 package<br>compliant with IEC<br>61967-2 | 0.1 to 30 MHz               | -22                                                 |      |  |

| 6                | Peak level |                                                                                        | 30 to 130 MHz               | -7                                                  | dBµV |  |

| S <sub>EMI</sub> | FEAKIEVEI  |                                                                                        | 130 MHz to 1GHz             | -12                                                 |      |  |

|                  |            |                                                                                        | SAE EMI Level               | 1                                                   | -    |  |

Table 46. EMI characteristics

#### 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the ANSI/JEDEC standard.

| Table 47. I | ESD absolute | maximum | ratings |

|-------------|--------------|---------|---------|

|-------------|--------------|---------|---------|

| Symbol Ratings        |                                                       | Conditions                                                     | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|----------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/JEDEC JS-001  | 2     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A = +25 \text{ °C},$<br>conforming to<br>ANSI/ESD STM5.3.1. | C4    | 500                             | V    |

1. Guaranteed by characterization results, not tested in production.

#### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latch-up standard.

| Symbol | Parameter             | Conditions                            | Class      |  |  |

|--------|-----------------------|---------------------------------------|------------|--|--|

| LU     | Static latch-up class | $T_A = +125$ °C conforming to JESD78A | II level A |  |  |

#### Table 48. Electrical sensitivities

#### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu$ A/+0  $\mu$ A range), or other functional failure (for example reset occurrence oscillator frequency deviation).

The test results are given in the Table 49.

|                  |                                   | Functional s       |                    |      |  |

|------------------|-----------------------------------|--------------------|--------------------|------|--|

| Symbol           | Description                       | Negative injection | Positive injection | Unit |  |

|                  | Injected current on BOOT0         | -0                 | NA                 |      |  |

| I <sub>INJ</sub> | Injected current on all FT pins   | -5 <sup>(1)</sup>  | NA                 | mA   |  |

|                  | Injected current on any other pin | -5 <sup>(1)</sup>  | +5                 |      |  |

#### Table 49. I/O current injection susceptibility

1. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

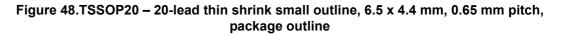

## 7.6 TSSOP20 package information

1. Drawing is not to scale.