Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 26                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-LQFP                                                                 |

| Supplier Device Package    | 32-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l011k4t6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM<sup>®</sup> Cortex<sup>®</sup>-M4, including ARM<sup>®</sup> Cortex<sup>®</sup>-M3 and ARM<sup>®</sup> Cortex<sup>®</sup>-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 Ultra-low-power series are the best solution for applications such as gas/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power Run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

### **3** Functional overview

### 3.1 Low-power modes

The ultra-low-power STM32L011x3/4 supports dynamic voltage scaling to optimize its power consumption in Run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply.

There are three power consumption ranges:

- Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), with the CPU running at up to 32 MHz

- Range 2 (full V<sub>DD</sub> range), with a maximum CPU frequency of 16 MHz

- Range 3 (full V<sub>DD</sub> range), with a maximum CPU frequency limited to 4.2 MHz

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs. Sleep mode power consumption at 16 MHz is about 1 mA with all peripherals off.

#### Low-power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the lowspeed clock (max 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In Lowpower run mode, the clock frequency and the number of enabled peripherals are both limited.

#### • Low-power sleep mode

This mode is achieved by entering Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In Low-power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the Run mode with the regulator on.

#### • Stop mode with RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSE and HSI RC oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event

### 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

#### Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

#### • Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

#### Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

#### • System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 0-32 MHz high-speed external (HSE bypass), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

#### • Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

#### • RTC clock sources

The LSI, LSE or HSE sources can be chosen to clock the RTC, whatever the system clock.

#### • Startup clock

After reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

#### • Clock security system (CSS)

This feature can be enabled by software. If an LSE clock failure occurs, it provides an interrupt or wakeup event which is generated assuming it has been previously enabled. This feature is not available on the HSE clock.

### Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

### 3.14.1 General-purpose timers (TIM2, TIM21)

There are three synchronizable general-purpose timers embedded in the STM32L011x3/4 devices (see *Table 7* for differences).

#### TIM2

TIM2 is based on 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It features four independent channels each for input capture/output compare, PWM or one-pulse mode output.

The TIM2 general-purpose timers can work together or with the TIM21 general-purpose timer via the Timer Link feature for synchronization or event chaining. Its counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2 has independent DMA request generation.

This timer is capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

### TIM21

TIM21 is based on a 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It has two independent channels for input capture/output compare, PWM or one-pulse mode output. It can work together and be synchronized with TIM2 full-featured general-purpose timer.

It can also be used as simple timebase and be clocked by the LSE clock source (32.768 kHz) to provide independent timebase from the main CPU clock.

### 3.14.2 Low-power Timer (LPTIM)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one shot mode

- Selectable software / hardware input trigger

- Selectable clock source

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM1 input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

### 3.14.3 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit downcounter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches '0'.

DocID027973 Rev 4

### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

### 3.14.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 3.15 Communication interfaces

### 3.15.1 I<sup>2</sup>C bus

One I<sup>2</sup>C interface (I2C1) can operate in multimaster or slave modes. The I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

The I<sup>2</sup>C interface supports 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

| Table 8, Com | parison of I20 | analog and | l digital filters  |

|--------------|----------------|------------|--------------------|

|              |                | analog und | a aigitai iiitoi o |

In addition, I2C1 provides hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C interface can be served by the DMA controller.

Refer to *Table 9* for the supported modes and features of I2C interface.

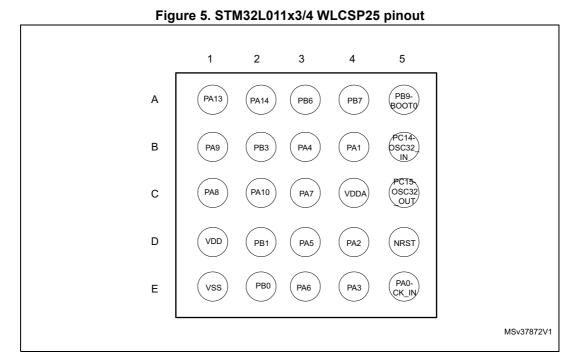

1. The above figure shows the package top view.

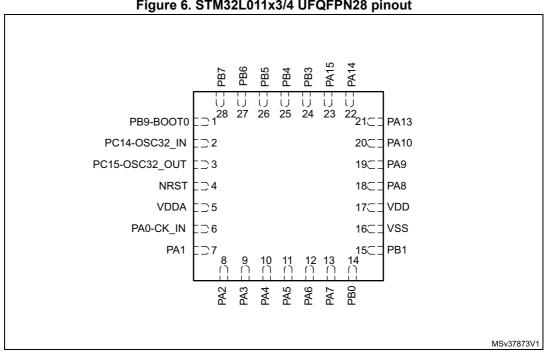

Figure 6. STM32L011x3/4 UFQFPN28 pinout

1. The above figure shows the package top view.

### 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 15: Voltage characteristics*, *Table 16: Current characteristics*, and *Table 17: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                 | Ratings                                                                                                 | Min                  | Мах                  | Unit |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                       | External main supply voltage<br>(including V <sub>DDA</sub> , V <sub>DD</sub> ) <sup>(1)</sup> –0.3 4.0 |                      |                      |      |

|                                                        | Input voltage on FT and FTf pins                                                                        | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +4.0 |      |

| V <sub>IN</sub> <sup>(2)</sup>                         | Input voltage on TC pins                                                                                | V <sub>SS</sub> -0.3 | 4.0                  | V    |

| V <sub>IN</sub> (-)                                    | Input voltage on BOOT0                                                                                  | V <sub>SS</sub>      | V <sub>DD</sub> +4.0 |      |

|                                                        | Input voltage on any other pin                                                                          | V <sub>SS</sub> -0.3 | 4.0                  |      |

| $ \Delta V_{DD} $                                      | Variations between different $V_{DDx}$ power pins                                                       | -                    | 50                   |      |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |                                                                                                         | -                    | 300                  | mV   |

| $ \Delta V_{SS} $                                      | Variations between all different ground pins                                                            | - 50                 |                      |      |

| V <sub>ESD(HBM)</sub>                                  | Electrostatic discharge voltage<br>(human body model)                                                   | see Section 6.3.11   |                      |      |

| Table 15 | Voltage | characteristics |

|----------|---------|-----------------|

|----------|---------|-----------------|

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 16* for maximum allowed injected current values.

3. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and device operation. its value does not need to respect this rule.

# 6.3 Operating conditions

### 6.3.1 General operating conditions

| Table 18. General operating condition | Table 18 | 18. Genera | I operating | conditions |

|---------------------------------------|----------|------------|-------------|------------|

|---------------------------------------|----------|------------|-------------|------------|

| Symbol             | Parameter                                                                                | Conditions                                                 | Min  | Max                  | Unit |  |

|--------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------|------|----------------------|------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                             | -                                                          | 0    | 32                   |      |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                            | -                                                          | 0    | 32                   | MHz  |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                            | -                                                          | 0    | 32                   |      |  |

|                    |                                                                                          | BOR detector disabled                                      | 1.65 | 3.6                  |      |  |

| V <sub>DD</sub>    | Standard operating voltage                                                               | BOR detector enabled, at power on                          | 1.8  | 3.6                  | v    |  |

|                    |                                                                                          | BOR detector disabled, after power on                      | 1.65 | 3.6                  |      |  |

| V <sub>DDA</sub>   | Analog operating voltage<br>(all features)                                               | Must be the same voltage as $V_{DD}^{(1)}$                 | 1.65 | 3.6                  | V    |  |

|                    | Input voltage on FT, FTf and RST pins <sup>(2)</sup>                                     | $2.0 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | -0.3 | 5.5                  |      |  |

| V                  | Input voltage on FT, FTT and RST pins                                                    | 1.65 V ≤ V <sub>DD</sub> ≤2.0 V                            | -0.3 | 5.2                  | V    |  |

| V <sub>IN</sub>    | Input voltage on BOOT0 pin                                                               | -                                                          | 0    | 5.5                  |      |  |

|                    | Input voltage on TC pin                                                                  | -                                                          | -0.3 | V <sub>DD</sub> +0.3 |      |  |

|                    |                                                                                          | LQFP32 package                                             | -    | 333                  |      |  |

|                    |                                                                                          | UFQFPN32 package                                           | -    | 513                  |      |  |

|                    | Power dissipation at $T_A$ = 85 °C (range 6)<br>or $T_A$ =105 °C (rage 7) <sup>(3)</sup> | UFQFPN28 package                                           | -    | 206                  |      |  |

|                    |                                                                                          | WLCSP25 package                                            | -    | 286                  | -    |  |

|                    |                                                                                          | TSSOP20 package                                            | -    | 270                  |      |  |

|                    |                                                                                          | UFQFPN20 package                                           | -    | 196                  |      |  |

| Pp                 |                                                                                          | TSSOP14 package                                            | -    | 210                  | mW   |  |

| PD                 |                                                                                          | LQFP32 package                                             | -    | 83                   | mvv  |  |

|                    |                                                                                          | UFQFPN32 package                                           | -    | 128                  |      |  |

|                    |                                                                                          | UFQFPN28 package                                           | -    | 52                   |      |  |

|                    | Power dissipation at $T_A = 125 \degree C$ (range 3) <sup>(3)</sup>                      | WLCSP25 package                                            | -    | 71                   | 1    |  |

|                    | -,                                                                                       | TSSOP20 package                                            | -    | 67                   |      |  |

|                    |                                                                                          | UFQFPN20 package                                           | -    | 49                   |      |  |

|                    |                                                                                          | TSSOP14 package                                            | -    | 53                   |      |  |

| Symbol                            | Parameter                 | Conditions                              |                         | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------------------------|---------------------------|-----------------------------------------|-------------------------|------|--------------------|------|

| I <sub>DD</sub> Supply current in |                           |                                         | $T_A$ = -40 °C to 25 °C | 0.8  | 1.6                |      |

|                                   |                           |                                         | T <sub>A</sub> = 55 °C  | 0.9  | 1.8                |      |

|                                   |                           | Independent watchdog<br>and LSI enabled | T <sub>A</sub> = 85 °C  | 1    | 2                  |      |

|                                   | Supply current in Standby |                                         | T <sub>A</sub> = 105 °C | 1.25 | 3                  |      |

|                                   |                           |                                         | T <sub>A</sub> = 125 °C | 2    | 7                  |      |

| (Standby)                         | mode                      |                                         | $T_A$ = -40 °C to 25 °C | 0.23 | 0.6                | μA   |

|                                   |                           | Independent watchdog<br>and LSI OFF     | T <sub>A</sub> = 55 °C  | 0.25 | 0.7                |      |

|                                   |                           |                                         | T <sub>A</sub> = 85 °C  | 0.36 | 1                  | 1    |

|                                   |                           |                                         | T <sub>A</sub> = 105 °C | 0.62 | 1.7                |      |

|                                   |                           |                                         | T <sub>A</sub> = 125 °C | 1.35 | 5                  |      |

| Table 30. Typical and maximum current of | consumptions in Standby mode |

|------------------------------------------|------------------------------|

|------------------------------------------|------------------------------|

1. Guaranteed by characterization results at 125 °C, not tested in production, unless otherwise specified

| Symbol                            | parameter                                   | System frequency | Current<br>consumption<br>during wakeup | Unit |

|-----------------------------------|---------------------------------------------|------------------|-----------------------------------------|------|

|                                   |                                             | HSI              | 1                                       |      |

|                                   |                                             | HSI/4            | 0,7                                     |      |

| I <sub>DD</sub> (WU from<br>Stop) | Supply current during wakeup from Stop mode | MSI 4,2 MHz      | 0,7                                     | mA   |

|                                   |                                             | MSI 1,05 MHz     | 0,4                                     |      |

|                                   |                                             | MSI 65 KHz       | 0,1                                     |      |

| I <sub>DD</sub> (Reset)           | Reset pin pulled down                       | -                | 0,21                                    |      |

| I <sub>DD</sub> (Power Up)        | BOR ON                                      | -                | 0,23                                    |      |

| I <sub>DD</sub> (WU from          | With Fast wakeup set                        | MSI 2,1 MHz      | 0,5                                     |      |

| StandBy)                          | With Fast wakeup disabled                   | MSI 2,1 MHz      | 0,12                                    |      |

### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked OFF

- with only one peripheral clocked ON

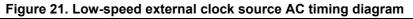

#### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 18*.

| Symbol                                     | Parameter                               | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User external clock source<br>frequency |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage    | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                       | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                              | -                                | 45                 | -      | 55                 | %    |

| ١L                                         | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 36. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 37*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization

### 6.3.7 Internal clock source characteristics

The parameters given in *Table 38* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 18*.

### High-speed internal 16 MHz (HSI16) RC oscillator

| Symbol                                | Parameter                                           | Conditions                                                           | Min               | Тур  | Max              | Unit |

|---------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI16</sub>                    | Frequency                                           | V <sub>DD</sub> = 3.0 V                                              | -                 | 16   | -                | MHz  |

| TRIM <sup>(1)(2)</sup>                | HSI16 user-                                         | Trimming code is not a multiple of 16                                | -                 | ±0.4 | 0.7              | %    |

| TRIM                                  | trimmed resolution                                  | Trimming code is a multiple of 16                                    | -                 | -    | ±1.5             | %    |

| ACC <sub>HSI16</sub>                  |                                                     | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                     | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

|                                       | Accuracy of the factory-calibrated HSI16 oscillator | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 0 to 55 °C                |                   | -    | 1.5              | %    |

|                                       |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                              |                   | -    | 2                | %    |

|                                       |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 85 °C                              |                   | -    | 2                | %    |

|                                       |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 105 °C                             |                   | -    | 2                | %    |

|                                       |                                                     | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = -40 to 125 °C |                   | -    | 3.25             | %    |

| t <sub>SU(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>startup time                    | -                                                                    | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>power consumption               | -                                                                    | -                 | 100  | 140              | μA   |

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results, not tested in production.

3. Guaranteed by test in production.

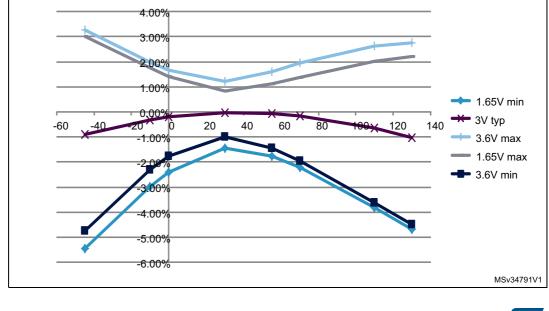

#### Figure 23. HSI16 minimum and maximum value versus temperature

DocID027973 Rev 4

### 6.3.13 I/O port characteristics

### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the conditions summarized in *Table 18*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                         | Conditions                                                                                                                                    | Min                                          | Тур                                | Max                                | Unit |  |

|------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------|------------------------------------|------|--|

| V <sub>IL</sub>  | Input low level voltage                           | TC, FT, FTf, RST<br>I/Os                                                                                                                      | -                                            | -                                  | 0.3V <sub>DD</sub>                 |      |  |

|                  |                                                   | BOOT0 pin                                                                                                                                     | -                                            | -                                  | 0.14V <sub>DD</sub> <sup>(1)</sup> |      |  |

| V                | Input high level voltage                          | All I/Os except<br>BOOT0 pin                                                                                                                  | 0.7 V <sub>DD</sub>                          | -                                  | -                                  | v    |  |

| V <sub>IH</sub>  | input nigh level voltage                          | BOOT0 pin                                                                                                                                     | 0.15<br>V <sub>DD</sub> +0.56 <sup>(1)</sup> | -                                  | -                                  |      |  |

| V                | I/O Schmitt trigger voltage hysteresis            | Standard I/Os                                                                                                                                 | -                                            | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                  |      |  |

| V <sub>hys</sub> | (2)                                               | BOOT0 pin                                                                                                                                     | -                                            | 0.01                               | -                                  |      |  |

| I <sub>lkg</sub> |                                                   | $\label{eq:VSS} \begin{array}{l} V_{SS} \leq V_{IN} \leq V_{DD} \\ \mbox{All I/Os except} \\ \mbox{BOOT0 and FTf} \\ \mbox{I/Os} \end{array}$ | -                                            | -                                  | ±50                                | nA   |  |

|                  |                                                   | BOOT0 <sup>(5)</sup><br>V <sub>IN</sub> = V <sub>DD</sub>                                                                                     | -                                            | +2                                 | -                                  |      |  |

|                  | Input leakage current <sup>(4)</sup>              | BOOT0<br>V <sub>IN</sub> = V <sub>SS</sub>                                                                                                    | -                                            | 0                                  | -                                  | μA   |  |

|                  |                                                   | $V_{DD} \le V_{IN} \le 5 V$<br>FT I/Os                                                                                                        | -                                            | -                                  | 200                                |      |  |

|                  |                                                   | V <sub>DD</sub> ≤ V <sub>IN</sub> ≤ 5 V<br>FTf I/Os                                                                                           | -                                            | -                                  | 500                                | nA   |  |

|                  |                                                   | $V_{DD} \le V_{IN} \le 5 V$<br>BOOT0                                                                                                          | -                                            | -                                  | 10                                 | μA   |  |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(6)</sup>   | $V_{IN} = V_{SS}$                                                                                                                             | 30                                           | 45                                 | 60                                 | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(6)</sup> | $V_{IN} = V_{DD}$                                                                                                                             | 30                                           | 45                                 | 60                                 | kΩ   |  |

| C <sub>IO</sub>  | I/O pin capacitance                               | -                                                                                                                                             | -                                            | 5                                  | -                                  | pF   |  |

| Table 50. I/O static characteris | stics |

|----------------------------------|-------|

|----------------------------------|-------|

1. Guaranteed by characterization, not tested in production

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results, not tested in production.

3. With a minimum of 200 mV. Guaranteed by characterization results, not tested in production.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

5. BOOT0/PB9 pin limitation: typical input leakage current = 2  $\mu$ A and input frequency limited to 10 kHz (1.65 V < V<sub>DD</sub> < 2.7 V) and 5 MHz (2.7 V < V<sub>DD</sub> < 3.6 V).

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

### 6.3.19 Communications interfaces

### I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm) : with a bit rate up to 100 kbit/s

- Fast-mode (Fm) : with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+) : with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timing requirements are guaranteed by design when the I<sup>2</sup>C peripheral is properly configured (refer to the reference manual for details) and when the I2CCLK frequency is greater than the minimum given in *Table 63*. The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and VDDIOx is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement (refer to *Section 6.3.13: I/O port characteristics* for the I2C I/Os characteristics).

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter (see *Table 62* for the analog filter characteristics).

### Table 62. I2C analog filter characteristics<sup>(1)</sup>

| Symbol          | Parameter                                                              | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 100 <sup>(3)</sup> | ns   |

1. Guaranteed by design, not tested in production.

2. Spikes with widths below t<sub>AF(min)</sub> are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

#### Table 63. I2C frequency in all I2C modes

| Symbol  | Parameter           | Co             | Min                                       | Unit |     |

|---------|---------------------|----------------|-------------------------------------------|------|-----|

|         |                     | Standard-mode  |                                           | 2    |     |

|         |                     | Fast-mode      |                                           | 8    |     |

| fi2CCLK | I2C clock frequency | Fast-mode Plus | Analog filter ON,<br>DNF = 0              | 18   | MHz |

|         |                     | Fast-mode Flus | ode Plus<br>Analog filter OFF,<br>DNF = 1 | 16   |     |

### **SPI characteristics**

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 18*.

Refer to Section 6.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                            | Conditions                                               | Min     | Тур   | Max               | Unit |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------|---------|-------|-------------------|------|

|                                              |                                      | Master mode                                              |         | -     | 16                |      |

|                                              |                                      | Slave mode receiver                                      | 1 -     |       | 16                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave mode Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 12 <sup>(2)</sup> | MHz  |

|                                              |                                      | Slave mode Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | -     | 16 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                               | 30      | 50    | 70                | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                | 4Tpclk  | -     | -                 |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                | 2Tpclk  | -     | -                 |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                              | Tpclk-2 | Tpclk | Tpclk+2           |      |

| t <sub>su(MI)</sub>                          | Data input setup time Master mode    |                                                          | 3       | -     | -                 |      |

| t <sub>su(SI)</sub>                          | Data input setup time                | Slave mode                                               |         | -     | -                 |      |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                              | 3.5     | -     | -                 |      |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                                               | 0       | -     | -                 | ns   |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                                               | 15      | -     | 36                |      |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                               | 10      | -     | 30                |      |

| +                                            |                                      | Slave mode 1.71 <v<sub>DD&lt;3.6V</v<sub>                | -       | 14    | 35                |      |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode 2.7 <v<sub>DD&lt;3.6V</v<sub>                 | -       | 14    | 20                |      |

| t <sub>v(MO)</sub>                           |                                      | Master mode                                              | -       | 4     | 6                 |      |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                                               | 10      | -     | -                 |      |

| t <sub>h(MO)</sub>                           |                                      | Master mode                                              | 3       | -     | -                 |      |

| Table 65. SPI characteristics in voltage Range 1 <sup>(1)</sup> | Table 65 | . SPI characte | eristics in | voltage | Range 1 <sup>(1)</sup> |

|-----------------------------------------------------------------|----------|----------------|-------------|---------|------------------------|

|-----------------------------------------------------------------|----------|----------------|-------------|---------|------------------------|

1. Guaranteed by characterization results, not tested in production.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

| Cumhal |       | millimeters | inches <sup>(1)</sup> |        |        |        |  |

|--------|-------|-------------|-----------------------|--------|--------|--------|--|

| Symbol | Min   | Тур         | Мах                   | Min    | Тур    | Мах    |  |

| А      | -     | -           | 1.600                 | -      | -      | 0.0630 |  |

| A1     | 0.050 | -           | 0.150                 | 0.0020 | -      | 0.0059 |  |

| A2     | 1.350 | 1.400       | 1.450                 | 0.0531 | 0.0551 | 0.0571 |  |

| b      | 0.300 | 0.370       | 0.450                 | 0.0118 | 0.0146 | 0.0177 |  |

| С      | 0.090 | -           | 0.200                 | 0.0035 | -      | 0.0079 |  |

| D      | 8.800 | 9.000       | 9.200                 | 0.3465 | 0.3543 | 0.3622 |  |

| D1     | 6.800 | 7.000       | 7.200                 | 0.2677 | 0.2756 | 0.2835 |  |

| D3     | -     | 5.600       | -                     | -      | 0.2205 | -      |  |

| E      | 8.800 | 9.000       | 9.200                 | 0.3465 | 0.3543 | 0.3622 |  |

| E1     | 6.800 | 7.000       | 7.200                 | 0.2677 | 0.2756 | 0.2835 |  |

| E3     | -     | 5.600       | -                     | -      | 0.2205 | -      |  |

| е      | -     | 0.800       | -                     | -      | 0.0315 | -      |  |

| L      | 0.450 | 0.600       | 0.750                 | 0.0177 | 0.0236 | 0.0295 |  |

| L1     | -     | 1.000       | -                     | -      | 0.0394 | -      |  |

| ссс    | -     | -           | 0.100                 | -      | -      | 0.0039 |  |

| А      | -     | -           | 1.600                 | -      | -      | 0.0630 |  |

Table 68. LQFP32, 7 x 7 mm, 32-pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

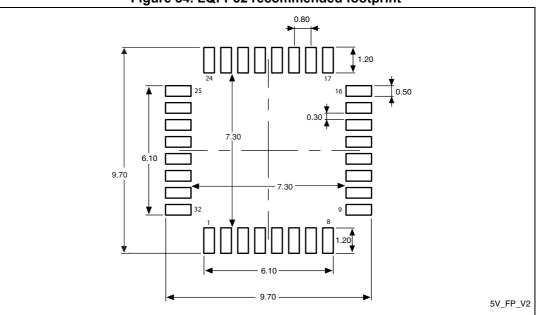

### Figure 34. LQFP32 recommended footprint

1. Dimensions are expressed in millimeters.

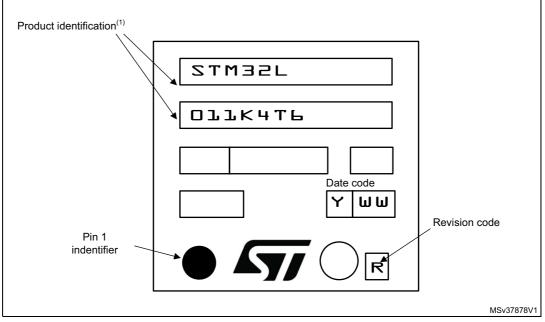

### LQFP32 device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| package mechanical data |       |             |       |                       |        |        |  |

|-------------------------|-------|-------------|-------|-----------------------|--------|--------|--|

| Cumhal                  |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

| Symbol                  | Min   | Тур         | Мах   | Min                   | Тур    | Мах    |  |

| А                       | 0.500 | 0.550       | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |

| A1                      | 0.000 | 0.020       | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |

| A3                      | -     | 0.152       | -     | -                     | 0.060  | -      |  |

| D                       | -     | 3.000       | -     | -                     | 0.1181 | -      |  |

| E                       | -     | 3.000       | -     | -                     | 0.1181 | -      |  |

| L1                      | 0.500 | 0.550       | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |

| L2                      | 0.300 | 0.350       | 0.400 | 0.0118                | 0.0138 | 0.0157 |  |

| L3                      | -     | 0.375       | -     | -                     | 0.0148 | -      |  |

| L4                      | -     | 0.200       | -     | -                     | 0.0079 | -      |  |

| L5                      | -     | 0.150       | -     | -                     | 0.0059 | -      |  |

| b                       | 0.180 | 0.250       | 0.300 | 0.0071                | 0.0098 | 0.0118 |  |

| е                       | -     | 0.500       | -     | -                     | 0.0197 | -      |  |

| ddd                     | -     | -           | 0.050 | -                     | -      | 0.0020 |  |

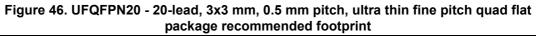

# Table 73. UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

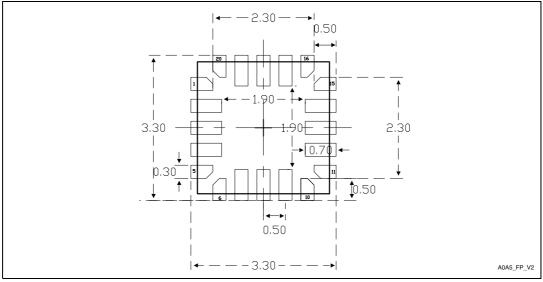

## 7.7 TSSOP14 package information

1. Drawing is not to scale.

| Table 75. TSSOP14 – 14-lead thin shrink small outline, 5.0 x 4.4 mm, 0.65 mm pitch, |

|-------------------------------------------------------------------------------------|

| package mechanical data                                                             |

| Symbol |       | millimeters |       |        | inches |        |

|--------|-------|-------------|-------|--------|--------|--------|

|        | Min   | Тур         | Max   | Min    | Тур    | Max    |

| A      | -     | -           | 1.200 | -      | -      | 0.0472 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -      | 0.0059 |

| A2     | 0.800 | 1.000       | 1.050 | 0.0315 | 0.0394 | 0.0413 |

| b      | 0.190 | -           | 0.300 | 0.0075 | -      | 0.0118 |

| с      | 0.090 | -           | 0.200 | 0.0035 | -      | 0.0079 |

| CP     | -     | -           | 0.100 | -      | -      | 0.0039 |

| D      | 4.900 | 5.000       | 5.100 | 0.1929 | 0.1969 | 0.2008 |

| е      | -     | 0.650       | -     | -      | 0.0256 | -      |

| E      | 6.200 | 6.400       | 6.600 | 0.2441 | 0.2520 | 0.2598 |

| E1     | 4.300 | 4.400       | 4.500 | 0.1693 | 0.1732 | 0.1772 |

| L      | 0.500 | 0.600       | 0.750 | 0.0197 | 0.0236 | 0.0295 |

| L1     | -     | 1.000       | -     | -      | 0.0394 | -      |

| а      | 0°    | -           | 8°    | 0°     | -      | 8°     |

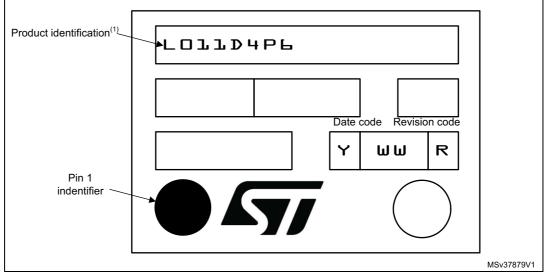

### **TSSOP14** device marking

The following figure gives an example of topside marking versus pin 1 position identifier location.

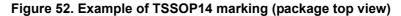

### 7.8 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$$P_{I/O} \max = \Sigma (V_{OL} \times I_{OL}) + \Sigma ((V_{DD} - V_{OH}) \times I_{OH}),$$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Symbol | Parameter                                                                       | Value | Unit |

|--------|---------------------------------------------------------------------------------|-------|------|

| ΘյΑ    | Thermal resistance junction-ambient<br>LQFP32 - 7 x 7 mm / 0.8 mm pitch         | 60    | °C/W |

|        | Thermal resistance junction-ambient<br>UFQFPN32 - 5 x 5 mm / 0.5 mm pitch       | 39    |      |

|        | Thermal resistance junction-ambient<br>WLCSP25 - 2.133 x 2.070 mm, 0.4 mm pitch | 70    |      |

|        | <b>Thermal resistance junction-ambient</b><br>UFQFPN28 - 4 x 4 mm, 0.5 mm pitch | 97    |      |

|        | <b>Thermal resistance junction-ambient</b><br>UFQFPN20 - 3 x 3 mm, 0.5 mm pitch | 102   |      |

|        | Thermal resistance junction-ambient<br>TSSOP20 - 169 mils                       | 74    |      |

|        | Thermal resistance junction-ambient<br>TSSOP14 - 169 mils                       | 95    |      |

Table 76. Thermal characteristics

1. The above curves are valid for range 3.

### 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.