Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 28                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-UFQFN Exposed Pad                                                    |

| Supplier Device Package    | 32-UFQFPN (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l011k4u6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

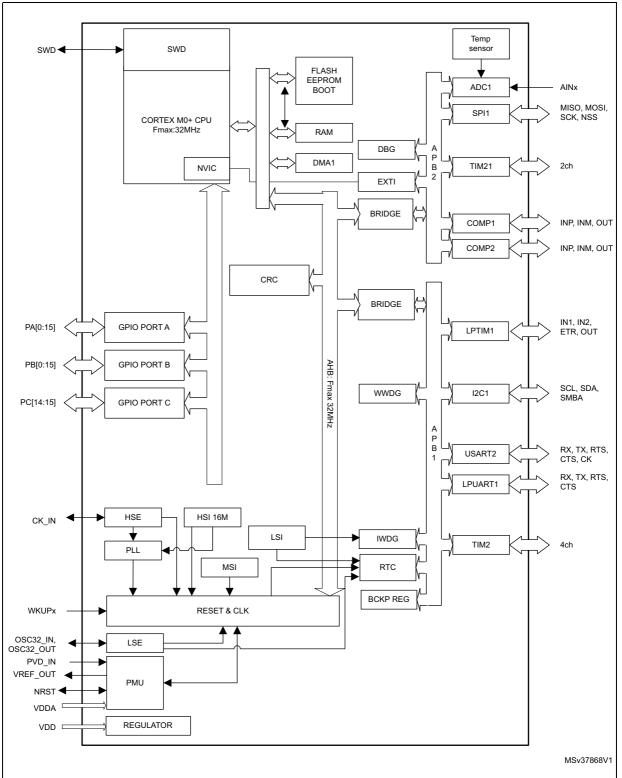

Figure 1. STM32L011x3/4 block diagram

DocID027973 Rev 4

|                                           |            |       | Low-         | Low-           |                  | Stop                 | 5 | Standby              |

|-------------------------------------------|------------|-------|--------------|----------------|------------------|----------------------|---|----------------------|

| IPs                                       | Run/Active | Sleep | power<br>run | power<br>sleep |                  | Wakeup<br>capability |   | Wakeup<br>capability |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | О     | 0            | 0              | 0                | 0                    | - | -                    |

| Power-on/down<br>reset (POR/PDR)          | Y          | Y     | Y            | Y              | Y                | Y                    | Y | Y                    |

| High Speed<br>Internal (HSI)              | 0          | О     | -            | -              | (3)              | -                    | - | -                    |

| High Speed<br>External (HSE)              | 0          | 0     | 0            | 0              | -                | -                    | - | -                    |

| Low Speed Internal<br>(LSI)               | 0          | О     | 0            | 0              | 0                | -                    | 0 | -                    |

| Low Speed<br>External (LSE)               | 0          | 0     | 0            | 0              | 0                | -                    | 0 | -                    |

| Multi-Speed<br>Internal (MSI)             | 0          | 0     | Y            | Y              | -                | -                    | - | -                    |

| Inter-Connect<br>Controller               | Y          | Y     | Y            | Y              | Y                | -                    | - | -                    |

| RTC                                       | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | -                    |

| RTC Tamper                                | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                    |

| Auto WakeUp<br>(AWU)                      | 0          | 0     | 0            | 0              | 0                | -                    | 0 | 0                    |

| USART                                     | 0          | 0     | 0            | 0              | O <sup>(4)</sup> | 0                    | - | -                    |

| LPUART                                    | 0          | 0     | 0            | 0              | O <sup>(4)</sup> | 0                    | - | -                    |

| SPI                                       | 0          | 0     | 0            | 0              | -                |                      | - | -                    |

| I2C                                       | 0          | 0     | 0            | 0              | O <sup>(5)</sup> | 0                    | - | -                    |

| ADC                                       | 0          | 0     | -            | -              | -                | -                    | - | -                    |

| Temperature<br>sensor                     | 0          | 0     | 0            | 0              | 0                | -                    | - | -                    |

| Comparators                               | 0          | 0     | 0            | 0              | 0                | 0                    | - | -                    |

| 16-bit timers                             | 0          | 0     | 0            | 0              | -                | -                    | - | -                    |

| LPTIM                                     | 0          | 0     | 0            | 0              | 0                | 0                    | - | -                    |

| IWDG                                      | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                    |

| WWDG                                      | 0          | 0     | 0            | 0              | -                | -                    | - | -                    |

| SysTick Timer                             | 0          | 0     | 0            | 0              | -                | -                    | - | -                    |

| GPIOs                                     | 0          | 0     | 0            | 0              | 0                | 0                    | - | 2 pins               |

Table 5. Functionalities depending on the working mode (from Run/active down to standby) (continued)<sup>(1)(2)</sup>

## Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L011x3/4 embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.4 Reset and supply management

## 3.4.1 Power supply schemes

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively. On TSSOP14 package, V<sub>DDA</sub> is internally connected to V<sub>DD</sub>.

## 3.4.2 Power supply supervisor

The devices feature an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

Two versions are available:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the VDD min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

DocID027973 Rev 4

## 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

## 3.14.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 3.15 Communication interfaces

## 3.15.1 I<sup>2</sup>C bus

One I<sup>2</sup>C interface (I2C1) can operate in multimaster or slave modes. The I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

The I<sup>2</sup>C interface supports 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask). They also include programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

| Table 8, Com | parison of I20 | analog and | l digital filters  |

|--------------|----------------|------------|--------------------|

|              |                | analog und | a aigitai iiitoi o |

In addition, I2C1 provides hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C interface can be served by the DMA controller.

Refer to *Table 9* for the supported modes and features of I2C interface.

| I2C features <sup>(1)</sup>                                  | I2C1             |

|--------------------------------------------------------------|------------------|

| 7-bit addressing mode                                        | Х                |

| 10-bit addressing mode                                       | X                |

| Standard mode (up to 100 kbit/s)                             | Х                |

| Fast mode (up to 400 kbit/s)                                 | X                |

| Fast Mode Plus with 20 mA output drive I/Os (up to 1 Mbit/s) | X <sup>(2)</sup> |

| Independent clock                                            | Х                |

| SMBus                                                        | X                |

| Wakeup from STOP                                             | X                |

| Tahlo | a  | STM32I   | 011-2/1 | 1 <sup>2</sup> C | implementation |

|-------|----|----------|---------|------------------|----------------|

| lane  | э. | STIVISZL | 01123/4 | 10               | implementation |

1. X = supported.

2. See Table 13: Pin definitions on page 37 for the list of I/Os that feature Fast Mode Plus capability

## 3.15.2 Universal synchronous/asynchronous receiver transmitter (USART)

The USART interface (USART2) is able to communicate at speeds of up to 4 Mbit/s.

It provides hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode and single-wire half-duplex communication mode. USART2 also supports Smartcard communication (ISO 7816, T=0 protocol) and IrDA SIR ENDEC.

USART2 interface can be served by the DMA controller.

*Table 10* for the supported modes and features of USART interface.

| USART modes/features <sup>(1)</sup>         | USART2 |

|---------------------------------------------|--------|

| Hardware flow control for modem             | Х      |

| Continuous communication using DMA          | Х      |

| Multiprocessor communication                | Х      |

| Synchronous mode                            | -      |

| Smartcard mode                              | Х      |

| Single-wire half-duplex communication       | Х      |

| IrDA SIR ENDEC block                        | Х      |

| LIN mode                                    | -      |

| Dual clock domain and wakeup from Stop mode | -      |

| Receiver timeout interrupt                  | -      |

| Modbus communication                        | -      |

| Auto baud rate detection (4 modes)          | -      |

| Driver Enable                               | Х      |

## Table 10. USART implementation

1. X = supported.

| Table 13. | Pin definitions | (continued) |

|-----------|-----------------|-------------|

|-----------|-----------------|-------------|

|         |          | Pin     | num      | ber    |                         |         |                                       |          |               |       | Pin functions                                                                               |                         |  |

|---------|----------|---------|----------|--------|-------------------------|---------|---------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------|-------------------------|--|

| TSSOP14 | UFQFPN20 | TSSOP20 | UFQFPN28 | LQFP32 | UFQFPN32 <sup>(1)</sup> | WLCSP25 | Pin name<br>(function<br>after reset) | Pin type | I/O structure | Notes | Alternate functions                                                                         | Additional<br>functions |  |

| 12      | 15       | 18      | 20       | 20     | 20                      | C2      | PA10                                  | I/O      | FTf           | -     | TIM21_CH1,<br>I2C1_SDA,<br>RTC_REFIN,<br>USART2_RX,<br>TIM2_CH3,<br>COMP1_OUT               | -                       |  |

| -       | -        | -       | -        | 21     | 21                      | -       | PA11                                  | I/O      | FT            | -     | SPI1_MISO,<br>LPTIM1_OUT,<br>EVENTOUT,<br>USART2_CTS,<br>TIM21_CH2,<br>COMP1_OUT            | -                       |  |

| -       | -        | -       | -        | 22     | 22                      | -       | PA12                                  | I/O      | FT            | -     | SPI1_MOSI,<br>EVENTOUT,<br>USART2_RTS,<br>COMP2_OUT                                         | -                       |  |

| 13      | 16       | 19      | 21       | 23     | 23                      | A1      | PA13                                  | I/O      | FTf           | -     | SWDIO,<br>LPTIM1_ETR,<br>I2C1_SDA,<br>SPI1_SCK,<br>LPUART1_RX,<br>COMP1_OUT                 | -                       |  |

| 14      | 17       | 20      | 22       | 24     | 24                      | A2      | PA14                                  | I/O      | FT            | -     | SWCLK,<br>LPTIM1_OUT,<br>I2C1_SMBA,<br>USART2_TX,<br>SPI1_MISO,<br>LPUART1_TX,<br>COMP2_OUT | -                       |  |

| -       | -        | -       | 23       | 25     | 25                      | -       | PA15                                  | I/O      | FT            | -     | SPI1_NSS,<br>TIM2_ETR,<br>EVENTOUT,<br>USART2_RX,<br>TIM2_CH1                               | -                       |  |

| -       | -        | -       | 24       | 26     | 26                      | B2      | PB3                                   | I/O      | FT            | -     | SPI1_SCK,<br>TIM2_CH2,<br>EVENTOUT                                                          | COMP2_INM               |  |

| -       | -        | -       | 25       | 27     | 27                      | -       | PB4                                   | I/O      | FT            | -     | SPI1_MISO,<br>EVENTOUT                                                                      | COMP2_INP               |  |

| Pin          |  |

|--------------|--|

| descriptions |  |

|              |  |

|         | Table 14. Alternate functions (continued) |                                               |                     |                                                |                         |                                      |              |                        |         |  |  |

|---------|-------------------------------------------|-----------------------------------------------|---------------------|------------------------------------------------|-------------------------|--------------------------------------|--------------|------------------------|---------|--|--|

|         |                                           | AF0                                           | AF1                 | AF2                                            | AF3                     | AF4                                  | AF5          | AF6                    | AF7     |  |  |

| Po      | rts                                       | SPI1/USART2/<br>TIM21/<br>EVENTOUT/<br>SYS_AF | SPI1/I2C1/<br>LPTIM | LPUART1/<br>LPTIM/TIM2/<br>EVENTOUT/<br>SYS_AF | I2C1/LPTIM/<br>EVENTOUT | I2C1/USART2/L<br>PUART1/<br>EVENTOUT | SPI1/TIM2/21 | LPUART1/EVE<br>VENTOUT | COMP1/2 |  |  |

|         | PB0                                       | EVENTOUT                                      | SPI1_MISO           | TIM2_CH2                                       | -                       | USART2_RTS                           | TIM2_CH3     | -                      | -       |  |  |

|         | PB1                                       | USART2_CK                                     | SPI1_MOSI           | LPTIM1_IN1                                     | -                       | LPUART1_RTS                          | TIM2_CH4     | -                      | -       |  |  |

|         | PB2                                       | -                                             | -                   | LPTIM1_OUT                                     | -                       | -                                    | -            | -                      | -       |  |  |

|         | PB3                                       | SPI1_SCK                                      | -                   | TIM2_CH2                                       | -                       | EVENTOUT                             | -            | -                      | -       |  |  |

| Port B  | PB4                                       | SPI1_MISO                                     | -                   | EVENTOUT                                       | -                       | -                                    | -            | -                      | -       |  |  |

| I OIL D | PB5                                       | SPI1_MOSI                                     | -                   | LPTIM1_IN1                                     | I2C1_SMBA               | -                                    | TIM21_CH1    | -                      | -       |  |  |

|         | PB6                                       | USART2_TX                                     | I2C1_SCL            | LPTIM1_ETR                                     | -                       | -                                    | TIM2_CH3     | LPUART1_TX             | -       |  |  |

|         | PB7                                       | USART2_RX                                     | I2C1_SDA            | LPTIM1_IN2                                     | -                       | -                                    | TIM2_CH4     | LPUART1_RX             | -       |  |  |

|         | PB8                                       | USART2_TX                                     | -                   | EVENTOUT                                       | -                       | I2C1_SCL                             | SPI1_NSS     | -                      | -       |  |  |

|         | PB9                                       | -                                             | -                   | -                                              | -                       | -                                    | -            | -                      | -       |  |  |

| Port C  | PC14                                      | -                                             | -                   | -                                              | -                       | -                                    | -            | -                      | -       |  |  |

|         | PC15                                      | -                                             | -                   | -                                              | -                       | _                                    | -            | -                      | -       |  |  |

42/115

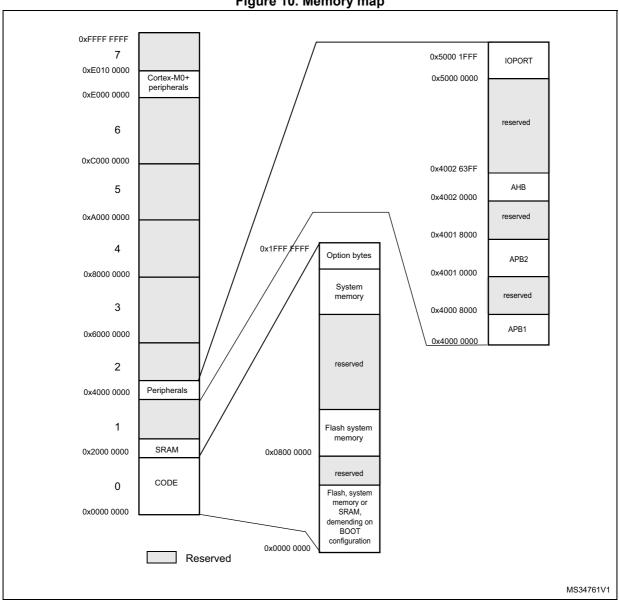

#### Memory mapping 5

Figure 10. Memory map

1. Refer to the STM32L011x3/4 reference manual for details on the Flash memory organization for each memory size.

| Symbol | Parameter                            | Conditions                                 | Min | Max | Unit |

|--------|--------------------------------------|--------------------------------------------|-----|-----|------|

| TA     |                                      | Maximum power<br>dissipation (range 6)     | -40 | 85  |      |

|        | Temperature range                    | Maximum power<br>dissipation (range 7)     | -40 | 105 |      |

|        |                                      | Maximum power<br>dissipation (range 3)     | -40 | 125 | °C   |

|        | Junction temperature range (range 6) | -40 °C $\leq$ T <sub>A</sub> $\leq$ 85 °   | -40 | 105 |      |

| TJ     | Junction temperature range (range 7) | -40 °C $\leq$ T <sub>A</sub> $\leq$ 105 °C | -40 | 125 |      |

|        | Junction temperature range (range 3) | -40 °C $\leq$ T <sub>A</sub> $\leq$ 125 °C | -40 | 130 |      |

Table 18. General operating conditions (continued)

1. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and normal operation.

2. To sustain a voltage higher than  $V_{DD}$ +0.3V, the internal pull-up/pull-down resistors must be disabled.

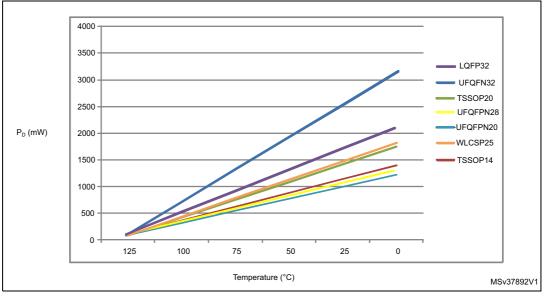

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 17: Thermal characteristics on page 47).

## 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in *Table 18*.

| Symbol                               | Parameter                      | Conditions                                          | Min  | Тур  | Max  | Unit       |  |

|--------------------------------------|--------------------------------|-----------------------------------------------------|------|------|------|------------|--|

|                                      | V <sub>DD</sub> rise time rate | BOR detector enabled                                | 0    | -    | 8    |            |  |

| t <sub>VDD</sub> <sup>(1)</sup>      |                                | BOR detector disabled                               | 0    | -    | 1000 | uo/\/      |  |

| 'VDD`'                               |                                | BOR detector enabled                                | 20   | -    | 8    | μs/V       |  |

|                                      |                                | BOR detector disabled                               | 0    | -    | 1000 |            |  |

| т (1)                                | Reset temporization            | V <sub>DD</sub> rising, BOR enabled                 | -    | 2    | 3.3  | <b>m</b> 0 |  |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> |                                | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6  | ms         |  |

| V                                    | Power on/power down reset      | Falling edge                                        | 1    | 1.5  | 1.65 |            |  |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                                         | 1.3  | 1.5  | 1.65 |            |  |

| V                                    | Brown-out reset threshold 0    | Falling edge                                        | 1.67 | 1.7  | 1.74 |            |  |

| V <sub>BOR0</sub>                    |                                | Rising edge                                         | 1.69 | 1.76 | 1.8  | V          |  |

| V                                    | Drown out report throohold 1   | Falling edge                                        | 1.87 | 1.93 | 1.97 | V          |  |

| V <sub>BOR1</sub>                    | Brown-out reset threshold 1    | Rising edge                                         | 1.96 | 2.03 | 2.07 |            |  |

| N/ -                                 | Brown-out reset threshold 2    | Falling edge                                        | 2.22 | 2.30 | 2.35 |            |  |

| V <sub>BOR2</sub>                    |                                | Rising edge                                         | 2.31 | 2.41 | 2.44 |            |  |

#### Table 19. Embedded reset and power control block characteristics

- 4. Guaranteed by design, not tested in production.

- 5. Shortest sampling time can be determined in the application by multiple iterations.

- 6. To guarantee less than 1% VREF\_OUT deviation.

## 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code. The current consumption is measured as described in *Figure 14: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code if not specified otherwise.

The current consumption values are derived from the tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 18: General operating conditions* unless otherwise specified.

The MCU is placed under the following conditions:

- All I/O pins are configured in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time and prefetch is adjusted depending on f<sub>HCLK</sub> frequency and voltage range to provide the best CPU performance unless otherwise specified.

- When the peripherals are enabled f<sub>APB1</sub> = f<sub>APB2</sub> = f<sub>APB</sub>

- When PLL is ON, the PLL inputs are equal to HSI = 16 MHz (if internal clock is used) or HSE = 16 MHz (if HSE bypass mode is used)

- The HSE user clock is applied to CK\_IN. It follows the characteristic specified in Table 35: High-speed external user clock characteristics

- For maximum current consumption  $V_{DD} = V_{DDA} = 3.6$  V is applied to all supply pins

- For typical current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.0 V is applied to all supply pins if not specified otherwise

| Symbol                  | Parameter               | Conc                                                           | litions                                              | f <sub>HCLK</sub> | Тур   | Max <sup>(1)</sup> | Unit    |

|-------------------------|-------------------------|----------------------------------------------------------------|------------------------------------------------------|-------------------|-------|--------------------|---------|

|                         |                         |                                                                | Range 3,                                             | 1 MHz             | 36.5  | 70                 |         |

|                         |                         |                                                                | V <sub>CORE</sub> =1.2 V,                            | 2 MHz             | 58    | 95                 | -       |

|                         |                         |                                                                | VOS[1:0]=11                                          | 4 MHz             | 100   | 150                |         |

|                         |                         | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included, | Range 2,                                             | 4 MHz             | 125   | 170                |         |

|                         |                         | $f_{HSE} = f_{HCLK}/2$                                         | V <sub>CORE</sub> =1.5 V,                            | 8 MHz             | 230   | 300                |         |

|                         |                         | above 16 MHz<br>(PLL ON) <sup>(2)</sup>                        | VOS[1:0]=10                                          | 16 MHz            | 450   | 540                |         |

|                         |                         |                                                                | Range 1,                                             | 8 MHz             | 275   | 350                |         |

|                         | Supply current in Sleep |                                                                | V <sub>CORE</sub> =1.8 V,                            | 16 MHz            | 555   | 650                |         |

|                         | mode, Flash             |                                                                | VOS[1:0]=01                                          | 32 MHz            | 1350  | 1600               |         |

|                         | OFF                     |                                                                | Range 3,                                             | 65 kHz            | 15.5  | 32                 |         |

|                         |                         | MSI clock                                                      | V <sub>CORE</sub> =1.2 V,                            | 524 kHz           | 26.5  | 55                 |         |

|                         |                         |                                                                | VOS[1:0]=11                                          | 4.2 MHz           | 115   | 160                |         |

|                         |                         | HSI16 clock source<br>(16 MHz)                                 | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10 | 16 MHz            | 585   | 670                | -<br>μΑ |

|                         |                         |                                                                | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 1500  | 1700               |         |

| I <sub>DD</sub> (Sleep) |                         |                                                                | Range 3,<br>V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11 | 1 MHz             | 49    | 88                 |         |

|                         |                         |                                                                |                                                      | 2 MHz             | 69    | 120                |         |

|                         |                         | f <sub>HSE</sub> = f <sub>HCLK</sub> up to                     |                                                      | 4 MHz             | 115   | 190                |         |

|                         |                         |                                                                | $f_{HSE} = f_{HCLK}$ up to                           | Range 2,          | 4 MHz | 135                | 200     |

|                         |                         | $f_{HSE} = f_{HCLK}/2$                                         | -                                                    | 8 MHz             | 240   | 340                | -       |

|                         |                         |                                                                |                                                      | 16 MHz            | 460   | 650                |         |

|                         |                         |                                                                |                                                      | 8 MHz             | 290   | 400                |         |

|                         | Supply current          |                                                                | V <sub>CORE</sub> =1.8 V,                            | 16 MHz            | 565   | 750                | -       |

|                         | in Sleep<br>mode, Flash |                                                                | VOS[1:0]=01                                          | 32 MHz            | 1350  | 1900               | -       |

|                         | ON                      |                                                                | Range 3,                                             | 65 kHz            | 26.5  | 46                 | -       |

|                         | MSI clock               | MSI clock                                                      | V <sub>CORE</sub> =1.2 V,                            | 524 kHz           | 38.5  | 70                 | -       |

|                         |                         |                                                                | VOS[1:0]=11                                          | 4.2 MHz           | 125   | 190                | 1       |

|                         |                         | HSI16 clock source                                             | Range 2,<br>V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10 | 16 MHz            | 600   | 760                |         |

|                         |                         | (16 MHz)                                                       | Range 1,<br>V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | 32 MHz            | 1500  | 1850               |         |

1. Guaranteed by characterization results at 125 °C, not tested in production, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol               | Parameter                                                                               | Conditions                                                        | Тур  | Мах | Unit |

|----------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|-----|------|

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 5.1  | 8   |      |

|                      | Wakeup from Stop mode, regulator in Run mode                                            | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 5.1  | 7   | -    |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.1  | 11  |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 1 | 5    | 8   |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 2 | 5    | 8   |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3 | 5    | 8   |      |

|                      | Wakeup from Stop mode, regulator in<br>low-power mode                                   | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 7.4  | 13  |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                   | 14   | 23  | -    |

| t <sub>WUSTOP</sub>  |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                    | 28   | 38  |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                    | 51   | 65  | μs   |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                    | 99   | 120 |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>MSI</sub> = 65 kHz                     | 196  | 260 |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 5.1  | 7   |      |

|                      |                                                                                         | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 8.2  | 11  | 1    |

|                      | Wakeup from Stop mode, regulator in<br>low-power mode, HSI kept running in<br>Stop mode | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 3.25 | -   |      |

|                      | Wakeup from Stop mode, regulator in                                                     | f <sub>HCLK</sub> = f <sub>HSI</sub> = 16 MHz                     | 4.9  | 7   |      |

|                      | low-power mode, code running from                                                       | f <sub>HCLK</sub> = f <sub>HSI</sub> /4 = 4 MHz                   | 7.9  | 10  |      |

|                      | RAM                                                                                     | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                    | 4.8  | 8   | ]    |

| t                    | Wakeup from Standby mode<br>FWU bit = 1                                                 | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 65   | 130 |      |

| <sup>t</sup> wustdby | Wakeup from Standby mode<br>FWU bit = 0                                                 | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                    | 2.2  | 3   | ms   |

Table 34. Low-power mode wakeup timings (continued)

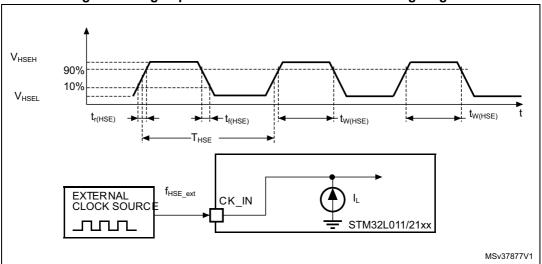

## 6.3.6 External clock source characteristics

## High-speed external user clock generated from an external source

In bypass mode the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.12*. However, the recommended clock input waveform is shown in *Figure 20*.

| Symbol                                     | Parameter                          | Conditions                       | Min         | Тур | Max                | Unit |

|--------------------------------------------|------------------------------------|----------------------------------|-------------|-----|--------------------|------|

| f                                          | User external clock source         | CSS is ON or<br>PLL is used      | 1           | 8   | 32                 | MHz  |

| <sup>f</sup> HSE_ext                       | frequency                          | CSS is OFF,<br>PLL not used      | 0           | 8   | 32                 | MHz  |

| V <sub>HSEH</sub>                          | CK_IN input pin high level voltage |                                  | $0.7V_{DD}$ | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                          | CK_IN input pin low level voltage  |                                  | $V_{SS}$    | -   | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | CK_IN high or low time             | _                                | 12          | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | CK_IN rise or fall time            |                                  | -           | -   | 20                 | 115  |

| C <sub>in(HSE)</sub>                       | CK_IN input capacitance            |                                  | -           | 2.6 | -                  | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                         |                                  | 45          | -   | 55                 | %    |

| ١L                                         | CK_IN Input leakage current        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -           | -   | ±1                 | μA   |

Table 35. High-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

## Figure 20. High-speed external clock source AC timing diagram

time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                  | Parameter Conditions <sup>(2)</sup>          |                                                    |   | Тур    | Max  | Unit |

|-------------------------|----------------------------------------------|----------------------------------------------------|---|--------|------|------|

| f <sub>LSE</sub>        | LSE oscillator frequency                     |                                                    | - | 32.768 | -    | kHz  |

|                         | Maximum critical crystal<br>transconductance | LSEDRV[1:0]=00<br>lower driving capability         | - | -      | 0.5  |      |

| C                       |                                              | LSEDRV[1:0]= 01<br>medium low driving capability   | - | -      | 0.75 | μΑ/V |

| G <sub>m</sub>          |                                              | LSEDRV[1:0] = 10<br>medium high driving capability | - | -      | 1.7  | μΑνν |

|                         |                                              | LSEDRV[1:0]=11<br>higher driving capability        | - | -      | 2.7  |      |

| $t_{\rm SU(LSE)}^{(3)}$ | Startup time                                 | V <sub>DD</sub> is stabilized                      | - | 2      | -    | s    |

1. Guaranteed by design, not tested in production.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. Guaranteed by characterization results, not tested in production. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. To increase speed, address a lower-drive quartz with a high- driver mode.

# *Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>http://www.st.com</u>.

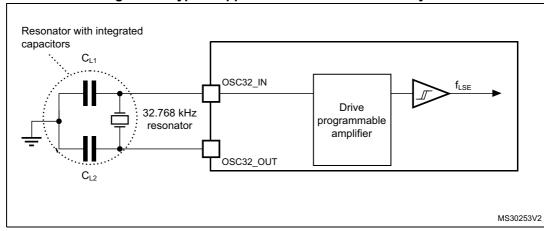

#### Figure 22. Typical application with a 32.768 kHz crystal

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

## Flash memory and data EEPROM

| Symbol            | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |  |  |

|-------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|--|--|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |  |  |

| +                 |                                                                                | Erasing                                         | -    | 3.28 | 3.94               | 20   |  |  |

| t <sub>prog</sub> | word or half-page                                                              | Programming                                     | -    | 3.28 | 3.94               | ms   |  |  |

|                   | Average current during<br>the whole programming /<br>erase operation           | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 500  | 700                | μA   |  |  |

| I <sub>DD</sub>   | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation |                                                 | -    | 1.5  | 2.5                | mA   |  |  |

Table 43. Flash memory and data EEPROM characteristics

1. Guaranteed by design, not tested in production.

| Cumb al                         | Parameter                                                                      | Conditions                                                       | Value              | Unit      |

|---------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------|-----------|

| Symbol                          | Parameter                                                                      | Conditions                                                       | Min <sup>(1)</sup> | Unit      |

|                                 | Cycling (erase / write)<br>Program memory                                      | T 10°C to 105 °C                                                 | 10                 |           |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>EEPROM data memory                                  | $T_A = -40^{\circ}C$ to 105 °C<br>$T_A = -40^{\circ}C$ to 125 °C | 100                | koveles   |

| INCYC <sup>1</sup>              | Cycling (erase / write)<br>Program memory                                      |                                                                  | 0.2                | - kcycles |

|                                 | Cycling (erase / write)<br>EEPROM data memory                                  |                                                                  | 2                  |           |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C  | • T <sub>RET</sub> = +85 °C                                      | 30                 |           |

|                                 | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 85 \text{ °C}$ | TRET - 105 C                                                     | 30                 |           |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 105 °C | -Т <sub>ВЕТ</sub> = +105 °С                                      |                    | Voars     |

| 'RET`                           | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 105$ °C        |                                                                  | 10                 | years     |

|                                 | Data retention (program memory) after<br>200 cycles at T <sub>A</sub> = 125 °C | -T <sub>RET</sub> = +125 °C                                      |                    |           |

|                                 | Data retention (EEPROM data memory) after 2 kcycles at $T_A$ = 125 °C          | TRET - TIZS C                                                    |                    |           |

| Table 44. Flash memor | y and data EEPROM endurance and retention |

|-----------------------|-------------------------------------------|

1. Guaranteed by characterization results, not tested in production.

2. Characterization is done according to JEDEC JESD22-A117.

## 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 45*. They are based on the EMS levels and classes defined in application note AN1709.

| ; | Symbol            | Parameter                                                                                                                         | Conditions                                                                                                    | Level/<br>Class |

|---|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|

| ` | / <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP32, $T_A$ = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2          | 3B              |

| \ | / <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, LQFP32, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4 | 4A              |

#### Table 45. EMS characteristics

## Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

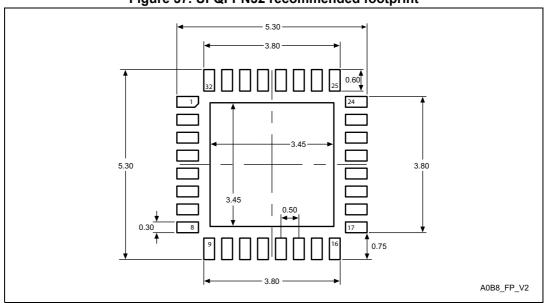

Figure 37. UFQFPN32 recommended footprint

1. Dimensions are expressed in millimeters.

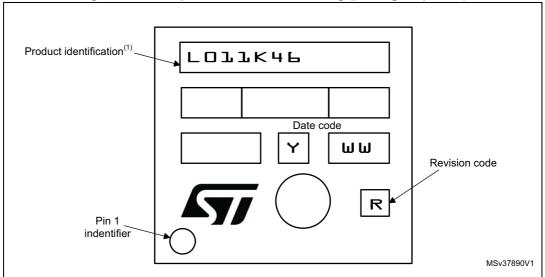

#### **Device marking**

The following figure gives an example of topside marking versus pin 1 position identifier location.

#### Figure 38. Example of UFQFPN32 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

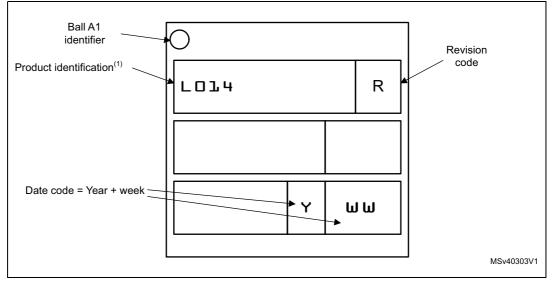

### **Device marking**

The following figure gives an example of topside marking versus ball A1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

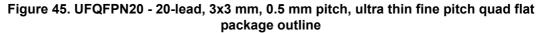

# 7.5 UFQFPN20 package information

1. Drawing is not to scale.

| Symbol        | Parameter                                                                       | Value | Unit |

|---------------|---------------------------------------------------------------------------------|-------|------|

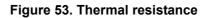

|               | Thermal resistance junction-ambient<br>LQFP32 - 7 x 7 mm / 0.8 mm pitch         | 60    |      |

|               | Thermal resistance junction-ambient<br>UFQFPN32 - 5 x 5 mm / 0.5 mm pitch       | 39    |      |

|               | Thermal resistance junction-ambient<br>WLCSP25 - 2.133 x 2.070 mm, 0.4 mm pitch | 70    |      |

| $\Theta_{JA}$ | <b>Thermal resistance junction-ambient</b><br>UFQFPN28 - 4 x 4 mm, 0.5 mm pitch | 97    | °C/W |

|               | <b>Thermal resistance junction-ambient</b><br>UFQFPN20 - 3 x 3 mm, 0.5 mm pitch | 102   |      |

|               | Thermal resistance junction-ambient<br>TSSOP20 - 169 mils                       | 74    |      |

|               | Thermal resistance junction-ambient<br>TSSOP14 - 169 mils                       | 95    |      |

Table 76. Thermal characteristics

1. The above curves are valid for range 3.

## 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.