#### Zilog - Z8F6081AN024XK Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status Active                                           |         |

|-----------------------------------------------------------------|---------|

|                                                                 |         |

| Core Processor eZ8                                              |         |

| Core Size 8-Bit                                                 |         |

| Speed 24MHz                                                     |         |

| Connectivity DALI, DMX, I <sup>2</sup> C, LINbus, SPI, UART/USA | RT, USB |

| Peripherals DMA, LVD, POR, PWM, WDT                             |         |

| Number of I/O 36                                                |         |

| Program Memory Size 60KB (60K x 8)                              |         |

| Program Memory Type FLASH                                       |         |

| EEPROM Size -                                                   |         |

| RAM Size 3.75K x 8                                              |         |

| Voltage - Supply (Vcc/Vdd) 1.8V ~ 3.6V                          |         |

| Data ConvertersA/D 10x12b; D/A 1x12b                            |         |

| Oscillator Type Internal                                        |         |

| Operating Temperature -40°C ~ 85°C (TA)                         |         |

| Mounting Type Surface Mount                                     |         |

| Package / Case 44-LQFP                                          |         |

|                                                                 |         |

| Supplier Device Package44-LQFP (10x10)                          |         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                   | 9.4.8.<br>9.4.9.<br>9.4.10. | IRQ3 Enable High and Low Bit Registers142Interrupt Edge Select Register145Shared Interrupt Select Register 0146 |

|-------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------|

|                   | 9.4.11.                     | Shared Interrupt Select Register 1 147                                                                          |

|                   | 9.4.12.                     | Interrupt Control Register 148                                                                                  |

| Chapter 10. Time  | rs                          |                                                                                                                 |

| 10.1.             | Timer A                     | rchitecture                                                                                                     |

| 10.2.             | Timer O                     | peration                                                                                                        |

|                   | 10.2.1.                     | Timer Clock Source                                                                                              |

|                   | 10.2.2.                     | Low-Power Modes                                                                                                 |

|                   | 10.2.3.                     | Timer Operating Modes 152                                                                                       |

|                   | 10.2.4.                     | Reading the Timer Count Values                                                                                  |

|                   | 10.2.5.                     | Timer Interrupts and DMA 170                                                                                    |

|                   | 10.2.6.                     | Timer Output Signal Operation                                                                                   |

|                   | 10.2.7.                     | Timer Input Path and Noise Filter 171                                                                           |

| 10.3.             | Timer R                     | egister Definitions                                                                                             |

|                   | 10.3.1.                     | Timer 0–2 High and Low Byte Registers 175                                                                       |

|                   | 10.3.2.                     | Timer Reload High and Low Byte Registers 176                                                                    |

|                   | 10.3.3.                     | Timer 0–2 PWM0 High and Low Byte Registers 177                                                                  |

|                   | 10.3.4.                     | Timer 0–2 PWM1 High and Low Byte Registers 178                                                                  |

|                   | 10.3.5.                     | Timer 0–2 Control Registers 179                                                                                 |

|                   | 10.3.6.                     | Timer 0–2 Status Registers                                                                                      |

|                   | 10.3.7.                     | Timer 0–2 Noise Filter Control Registers 186                                                                    |

| Chapter 11. Multi | -Channel                    | Timer                                                                                                           |

| 11.1.             | Archited                    | ture                                                                                                            |

| 11.2.             | Timer O                     | peration                                                                                                        |

|                   | 11.2.1.                     | Multi-Channel Timer Counter                                                                                     |

|                   | 11.2.2.                     | Inputs and Outputs 188                                                                                          |

|                   | 11.2.3.                     | Clock Source                                                                                                    |

|                   | 11.2.4.                     | Multi-Channel Timer Clock Prescaler                                                                             |

|                   | 11.2.5.                     | Multi-Channel Timer Start                                                                                       |

|                   | 11.2.6.                     | Multi-Channel Timer Mode Control 189                                                                            |

|                   | 11.2.7.                     | Count Modulo Mode 190                                                                                           |

|                   | 11.2.8.                     | Count Up/Down Mode 190                                                                                          |

| 11.3.             | Capture/                    | Compare Channel Operation 191                                                                                   |

|                   | 11.3.1.                     | One-Shot Compare Operation                                                                                      |

|                   | 11.3.2.                     | Continuous Compare Operation                                                                                    |

|                   | 11.3.3.                     | PWM Output Operation 191                                                                                        |

|                   | 11.3.4.                     | Capture Operation 192                                                                                           |

| Timer 1 (ContinuedF0BTimF0CTimF0DTimF0ETimF0FTimF24TimF25TimF26Tim                                                                                                                                    | egister Description<br>P<br>mer 1 Reload Low Byte<br>mer 1 PWM0 High Byte<br>mer 1 PWM0 Low Byte<br>mer 1 Control 0<br>mer 1 Control 1<br>mer 1 PWM1 High Byte<br>mer 1 PWM1 Low Byte<br>mer 1 Control 2<br>mer 1 Status<br>mer 1 Noise Filter Control | Mnemonic<br>T1RL<br>T1PWM0H<br>T1PWM0L<br>T1CTL0<br>T1CTL1<br>T1PWM1H<br>T1PWM1L<br>T1CTL2<br>T1STA | Reset<br>(Hex)           FF           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00 | Page # 176 177 177 179 180 178 178 101                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| F0B         Tim           F0C         Tim           F0D         Tim           F0E         Tim           F0F         Tim           F24         Tim           F25         Tim           F26         Tim | ner 1 Reload Low Byte<br>ner 1 PWM0 High Byte<br>ner 1 PWM0 Low Byte<br>ner 1 Control 0<br>ner 1 Control 1<br>ner 1 PWM1 High Byte<br>ner 1 PWM1 Low Byte<br>ner 1 Control 2<br>ner 1 Status                                                           | T1PWM0H<br>T1PWM0L<br>T1CTL0<br>T1CTL1<br>T1PWM1H<br>T1PWM1L<br>T1CTL2                              | 00<br>00<br>00<br>00<br>00<br>00                                                                                                                                                                                                                                      | 177         177         179         180         178         178 |

| FOC         Tin           F0D         Tin           F0E         Tin           F0F         Tin           F24         Tin           F25         Tin           F26         Tin                           | ner 1 PWM0 High Byte<br>ner 1 PWM0 Low Byte<br>ner 1 Control 0<br>ner 1 Control 1<br>ner 1 PWM1 High Byte<br>ner 1 PWM1 Low Byte<br>ner 1 Control 2<br>ner 1 Status                                                                                    | T1PWM0H<br>T1PWM0L<br>T1CTL0<br>T1CTL1<br>T1PWM1H<br>T1PWM1L<br>T1CTL2                              | 00<br>00<br>00<br>00<br>00<br>00                                                                                                                                                                                                                                      | 177         177         179         180         178         178 |

| F0D         Tin           F0E         Tin           F0F         Tin           F24         Tin           F25         Tin           F26         Tin                                                     | ner 1 PWM0 Low Byte<br>ner 1 Control 0<br>ner 1 Control 1<br>ner 1 PWM1 High Byte<br>ner 1 PWM1 Low Byte<br>ner 1 Control 2<br>ner 1 Status                                                                                                            | T1PWM0L<br>T1CTL0<br>T1CTL1<br>T1PWM1H<br>T1PWM1L<br>T1CTL2                                         | 00<br>00<br>00<br>00<br>00                                                                                                                                                                                                                                            | 177       179       180       178       178                     |

| F0E         Tin           F0F         Tin           F24         Tin           F25         Tin           F26         Tin                                                                               | ner 1 Control 0<br>ner 1 Control 1<br>ner 1 PWM1 High Byte<br>ner 1 PWM1 Low Byte<br>ner 1 Control 2<br>ner 1 Status                                                                                                                                   | T1CTL0<br>T1CTL1<br>T1PWM1H<br>T1PWM1L<br>T1CTL2                                                    | 00<br>00<br>00<br>00                                                                                                                                                                                                                                                  | 179       180       178       178                               |

| F0F         Tin           F24         Tin           F25         Tin           F26         Tin                                                                                                         | ner 1 Control 1<br>ner 1 PWM1 High Byte<br>ner 1 PWM1 Low Byte<br>ner 1 Control 2<br>ner 1 Status                                                                                                                                                      | T1CTL1<br>T1PWM1H<br>T1PWM1L<br>T1CTL2                                                              | 00<br>00<br>00                                                                                                                                                                                                                                                        | <u>180</u><br><u>178</u><br><u>178</u>                          |

| F24         Tin           F25         Tin           F26         Tin                                                                                                                                   | ner 1 PWM1 High Byte<br>ner 1 PWM1 Low Byte<br>ner 1 Control 2<br>ner 1 Status                                                                                                                                                                         | T1PWM1H<br>T1PWM1L<br>T1CTL2                                                                        | 00                                                                                                                                                                                                                                                                    | <u>178</u><br><u>178</u>                                        |

| F25         Tin           F26         Tin                                                                                                                                                             | ner 1 PWM1 Low Byte<br>ner 1 Control 2<br>ner 1 Status                                                                                                                                                                                                 | T1PWM1L<br>T1CTL2                                                                                   | 00                                                                                                                                                                                                                                                                    | <u>178</u>                                                      |

| F26 Tin                                                                                                                                                                                               | ner 1 Control 2<br>ner 1 Status                                                                                                                                                                                                                        | T1CTL2                                                                                              |                                                                                                                                                                                                                                                                       |                                                                 |

|                                                                                                                                                                                                       | ner 1 Status                                                                                                                                                                                                                                           |                                                                                                     | 00                                                                                                                                                                                                                                                                    | 404                                                             |

| F27 Tin                                                                                                                                                                                               |                                                                                                                                                                                                                                                        | T1STA                                                                                               |                                                                                                                                                                                                                                                                       | <u>184</u>                                                      |

|                                                                                                                                                                                                       | ner 1 Noise Filter Control                                                                                                                                                                                                                             |                                                                                                     | 00                                                                                                                                                                                                                                                                    | <u>185</u>                                                      |

| F2D Tin                                                                                                                                                                                               |                                                                                                                                                                                                                                                        | T1NFC                                                                                               | 00                                                                                                                                                                                                                                                                    | <u>186</u>                                                      |

| Timer 2                                                                                                                                                                                               |                                                                                                                                                                                                                                                        |                                                                                                     |                                                                                                                                                                                                                                                                       |                                                                 |

| F10 Tin                                                                                                                                                                                               | ner 2 High Byte                                                                                                                                                                                                                                        | T2H                                                                                                 | 00                                                                                                                                                                                                                                                                    | <u>175</u>                                                      |

| F11 Tin                                                                                                                                                                                               | ner 2 Low Byte                                                                                                                                                                                                                                         | T2L                                                                                                 | 01                                                                                                                                                                                                                                                                    | <u>175</u>                                                      |

| F12 Tin                                                                                                                                                                                               | ner 2 Reload High Byte                                                                                                                                                                                                                                 | T2RH                                                                                                | FF                                                                                                                                                                                                                                                                    | <u>176</u>                                                      |

| F13 Tin                                                                                                                                                                                               | ner 2 Reload Low Byte                                                                                                                                                                                                                                  | T2RL                                                                                                | FF                                                                                                                                                                                                                                                                    | <u>176</u>                                                      |

| F14 Tin                                                                                                                                                                                               | ner 2 PWM0 High Byte                                                                                                                                                                                                                                   | T2PWM0H                                                                                             | 00                                                                                                                                                                                                                                                                    | <u>177</u>                                                      |

| F15 Tin                                                                                                                                                                                               | ner 2 PWM0 Low Byte                                                                                                                                                                                                                                    | T2PWM0L                                                                                             | 00                                                                                                                                                                                                                                                                    | <u>177</u>                                                      |

| F16 Tin                                                                                                                                                                                               | ner 2 Control 0                                                                                                                                                                                                                                        | T2CTL0                                                                                              | 00                                                                                                                                                                                                                                                                    | <u>179</u>                                                      |

| F17 Tin                                                                                                                                                                                               | ner 2 Control 1                                                                                                                                                                                                                                        | T2CTL1                                                                                              | 00                                                                                                                                                                                                                                                                    | <u>180</u>                                                      |

| F18–F1F Re                                                                                                                                                                                            | eserved                                                                                                                                                                                                                                                | _                                                                                                   | XX                                                                                                                                                                                                                                                                    |                                                                 |

| F28 Tin                                                                                                                                                                                               | ner 2 PWM1 High Byte                                                                                                                                                                                                                                   | T2PWM1H                                                                                             | 00                                                                                                                                                                                                                                                                    | <u>180</u>                                                      |

| F29 Tin                                                                                                                                                                                               | ner 2 PWM1 Low Byte                                                                                                                                                                                                                                    | T2PWM1L                                                                                             | 00                                                                                                                                                                                                                                                                    | <u>178</u>                                                      |

| F2A Tin                                                                                                                                                                                               | ner 2 Control 2                                                                                                                                                                                                                                        | T2CTL2                                                                                              | 00                                                                                                                                                                                                                                                                    | <u>184</u>                                                      |

| F2B Tin                                                                                                                                                                                               | ner 2 Status                                                                                                                                                                                                                                           | T2STA                                                                                               | 00                                                                                                                                                                                                                                                                    | <u>185</u>                                                      |

| F2E Tin                                                                                                                                                                                               | ner 2 Noise Filter Control                                                                                                                                                                                                                             | T2NFC                                                                                               | 00                                                                                                                                                                                                                                                                    | <u>186</u>                                                      |

| F2F Re                                                                                                                                                                                                | eserved                                                                                                                                                                                                                                                | _                                                                                                   | XX                                                                                                                                                                                                                                                                    |                                                                 |

| RTC                                                                                                                                                                                                   |                                                                                                                                                                                                                                                        |                                                                                                     |                                                                                                                                                                                                                                                                       |                                                                 |

| F30 Rea                                                                                                                                                                                               | al-Time Clock Seconds                                                                                                                                                                                                                                  | RTC_SEC                                                                                             | XX                                                                                                                                                                                                                                                                    | <u>213</u>                                                      |

| F31 Rea                                                                                                                                                                                               | al-Time Clock Minutes                                                                                                                                                                                                                                  | RTC_MIN                                                                                             | XX                                                                                                                                                                                                                                                                    | <u>214</u>                                                      |

| F32 Re                                                                                                                                                                                                | al-Time Clock Hours                                                                                                                                                                                                                                    | RTC_HRS                                                                                             | XX                                                                                                                                                                                                                                                                    | <u>216</u>                                                      |

| F33 Re                                                                                                                                                                                                | al-Time Clock Day-of-the-Month                                                                                                                                                                                                                         | RTC_DOM                                                                                             | XX                                                                                                                                                                                                                                                                    | 217                                                             |

### Table 8. Register File Address Map (Continued)

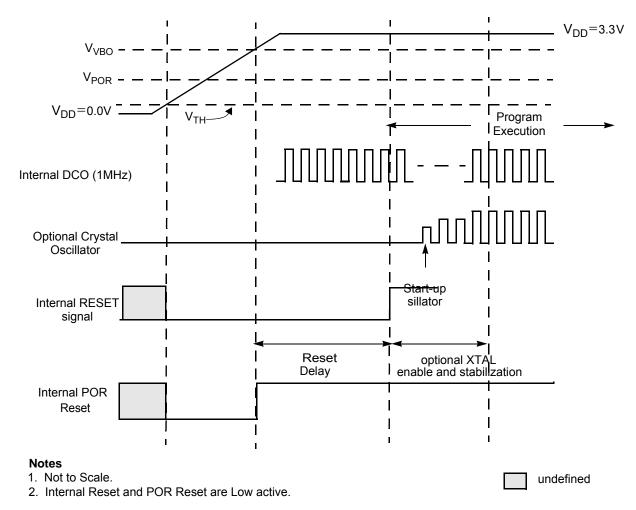

the supply voltage reaches a safe circuit operating level when the device is powered on.  $V_{DD}$  must be greater than both  $V_{POR}$  and  $V_{VBO}$  to exit the Reset state.

After power on, the POR circuit keeps idle until the supply voltage drops below  $V_{TH}$  voltage. <u>Figure 8</u> on page 42 shows this POR behavior.

After the F6482 Series MCU exits the POR state, the eZ8 CPU fetches the Reset vector. Following this POR, the POR/VBO status bit in the Reset Status Register is set to 1.

For the POR threshold voltage ( $V_{POR}$ ) and POR start voltage  $V_{TH}$ , see the <u>Electrical</u> <u>Characteristics</u> chapter on page 598.

Figure 7. Power-On Reset Operation

# **Chapter 7. General-Purpose Input/Output**

The F6482 Series products support a maximum of 67 port pins (ports A–J) for generalpurpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop-Mode Recovery functionality, and alternate pin functions. Each port pin is individually programmable.

# 7.1. GPIO Port Availability by Device

Table 16 lists the port pins available with each device and package type.

|                                                     |                    | 12-Bit | 120              |     | 0.01 |      |     |       |       |       |       |       |       |       |       | Port  | Total |

|-----------------------------------------------------|--------------------|--------|------------------|-----|------|------|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Device                                              | Pkg.               | ADC    | I <sup>2</sup> C | LCD | SPI  | UART | USB | Α     | В     | С     | D     | Е     | F     | G     | н     | J     | I/O   |

| Z8F6481QK,<br>Z8F6081QK,<br>Z8F3281QK,<br>Z8F1681QK | 32-<br>pin<br>QFN  | 9      | 1                | -   | 1    | 1    | 1   | [7:0] | [6:0] | [7:0] | [0]   | [1:0] | -     | -     | -     | _     | 26    |

| Z8F6481AN,<br>Z8F6081AN,<br>Z8F3281AN,<br>Z8F1681AN | 44-<br>pin<br>LQFP | 10     | 1                | _   | 1    | 2    | 1   | [7:0] | [4:0] | [7:0] | [7:0] | [6:0] | -     | _     | _     | _     | 36    |

| Z8F6481QN,<br>Z8F6081QN,<br>Z8F3281QN,<br>Z8F1681QN | 44-<br>pin<br>QFN  | 10     | 1                | -   | 1    | 2    | 1   | [7:0] | [4:0] | [7:0] | [7:0] | [6:0] | -     | -     | -     | -     | 36    |

| Z8F6481AR,<br>Z8F6081AR,<br>Z8F3281AR,<br>Z8F1681AR | 64-<br>pin<br>LQFP | 12     | 1                | -   | 2    | 2    | 1   | [7:0] | [7:0] | [7:0] | [7:0] | [6:0] | [7:0] | [4:0] | -     | _     | 52    |

| Z8F6482AR,<br>Z8F6082AR,<br>Z8F3282AR,<br>Z8F1682AR | 64-<br>pin<br>LQFP | 8      | 1                | 1   | 2    | 1    | 0   | [7:0] | [5:0] | [7:0] | [0]   | -     | [7:0] | [7:0] | [7:0] | [3:0] | 51    |

| Z8F6482AT,<br>Z8F6082AT,<br>Z8F3282AT,<br>Z8F1682AT | 80-<br>pin<br>LQFP | 12     | 1                | 1   | 2    | 2    | 1   | [7:0] | [7:0] | [7:0] | [7:0] | [6:0] | [7:0] | [7:0] | [7:0] | [3:0] | 67    |

Table 16. Port Availability by Device and Package Type

| Port                | Pin | Mnemonic   | Alternate Function Description             | Alternate Function<br>Set Subregisters |

|---------------------|-----|------------|--------------------------------------------|----------------------------------------|

| Port E <sup>1</sup> | PE0 | DP         | USB DP                                     | AFS1[0]: 0                             |

| PE1<br>PE2<br>PE3   |     | T0IN/T0OUT | Timer 0 Input/Timer 0 Output<br>Complement | AFS1[0]: 1                             |

|                     | PE1 | DM         | USB DM                                     | AFS1[1]: 0                             |

|                     |     | TOOUT      | Timer 0 Output                             | AFS1[1]: 1                             |

|                     | PE2 | T4IN       | AFS1[2]: 0                                 |                                        |

|                     |     | Reserved   |                                            | AFS1[2]: 1                             |

|                     | PE3 | T4CHA      | Multi Channel Timer Input/Output A         | AFS1[3]: 0                             |

|                     |     | ESOUT[0]   | Event System Out 0                         | AFS1[3]: 1                             |

|                     | PE4 | T4CHB      | Multi Channel Timer Input/Output B         | AFS1[4]: 0                             |

|                     |     | ESOUT[1]   | Event System Out 1                         | AFS1[4]: 1                             |

|                     | PE5 | T4CHC      | Multi Channel Timer Input/Output C         | AFS1[5]: 0                             |

|                     |     | ESOUT[2]   | Event System Out 2                         | AFS1[5]: 1                             |

|                     | PE6 | T4CHD      | Multi Channel Timer Input/Output D         | AFS1[6]: 0                             |

|                     |     | ESOUT[3]   | Event System Out 3                         | AFS1[6]: 1                             |

#### Table 18. Port Alternate Function Mapping (44-Pin Parts) (Continued)

Notes

Because there are at most two choices of alternate function for some pins of Ports A, B, D and E, the Alternate Function Set register AFS2 is not implemented. Additionally, alternate function selection, as described in the Port A–J Alternate Function Subregisters (see page 88), must also be enabled.

2. The alternate function selection for Port C, as described in the Port A–J Alternate Function Subregisters (see page 88), must also be enabled.

$PLL_{CLK} = \frac{PLL_{CLKIN}}{(PLLRDIV + 1)} \times \frac{(PLLNDIV+1)}{(PLLODIV+1)}$

The operands in the above equation can be defined as:

- PLL<sub>CLKIN</sub> is either HFXO or the External Clock Drive, as selected by the PLLSEL

- PLL<sub>RDIV</sub> + 1 is the PLL reference divider ratio

- PLL<sub>NDIV</sub> + 1 is the PLL feedback divider ratio

- PLL<sub>ODIV</sub> + 1 is the PLL output divider ratio

The PLL should be configured in accordance with the following requirements:

- PLL<sub>CLK</sub>IN: 0.3125 MHz–24 MHz

- Reference divider output frequency (PLL core input clock): 0.3125–24MHz, 1.5MHz – the recommended minimum for when clocking the USB

- PLL VCO frequency (input to output divider): 80MHz–384MHz

- PLL<sub>CLK</sub> (PLL output): 48 MHz max. If PLL<sub>CLK</sub> is >25 MHz and is selected as the source for System Clock, SCKDIV must be configured such that System Clock does not exceed 24 MHz.

Table 37 lists common PLL configurations to generate a 48 MHz PLL<sub>CLK</sub> for the USB that satisfy the 2500 ppm data rate requirement.

| PLL <sub>CLKIN</sub><br>(MHz) | <b>PLL</b> <sub>RDIV</sub> | PLL Core<br>(MHz) | <b>PLL</b> <sub>NDIV</sub> | VCO<br>(MHz) | PLL <sub>ODIV</sub> |

|-------------------------------|----------------------------|-------------------|----------------------------|--------------|---------------------|

| 1.5                           | 0                          | 1.5               | 63                         | 96           | 1                   |

| 1.6                           | 0                          | 1.6               | 59                         | 96           | 1                   |

| 2                             | 0                          | 2                 | 47                         | 96           | 1                   |

| 2.4                           | 0                          | 2.4               | 39                         | 96           | 1                   |

| 3                             | 0                          | 3                 | 31                         | 96           | 1                   |

| 3.2                           | 0                          | 3.2               | 29                         | 96           | 1                   |

| 3.84                          | 0                          | 3.84              | 24                         | 96           | 1                   |

| 4                             | 0                          | 4                 | 23                         | 96           | 1                   |

| 4.5                           | 2                          | 1.5               | 63                         | 96           | 1                   |

| 4.8                           | 1                          | 2.4               | 39                         | 96           | 1                   |

| 5                             | 0                          | 5                 | 47                         | 240          | 4                   |

Table 37. Common PLL Configurations for 48 MHz PLLCLK

| Bit    | Description (Continued)                                                                                                                                                                               |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2:0]  | System Clock Source Select                                                                                                                                                                            |

| SCKSEL | There is a delay from the writing of SCKSEL to the actual switching from the currently active clock source to the new, desired clock source. Reading SCKSEL return the currently active clock source. |

|        | 000: Digitally Controlled Oscillator (DCO).                                                                                                                                                           |

|        | 001: Peripheral Clock (PCLK).                                                                                                                                                                         |

|        | 010: High Frequency Crystal Oscillator (HFXO) or external clock drive, CLKIN on PA0, based on PLL Clock Source Select (PLLSEL).                                                                       |

|        | 011: Phase Locked Loop (PLL).                                                                                                                                                                         |

|        | 100: Watchdog Timer Oscillator (WTO).                                                                                                                                                                 |

|        | 101: Reserved.                                                                                                                                                                                        |

|        | 110: Reserved.                                                                                                                                                                                        |

|        | 111: Reserved.                                                                                                                                                                                        |

# 8.11.2. Clock Control 1 Register

The Clock Control 1 (CLKCTL1) Register, shown in Table 39, enables/disables the IPO and LFXO, selects PCLK Stop Mode behavior, selects the PCLK source, enables/disables WTO failure detection, and contains a ready bit for the IPO. Before writing CLKCTL1, the clock control registers must be unlocked as described in the <u>Clock System Control</u> <u>Register Unlocking/Locking</u> section on page 103.

| Table 39. | Clock | Control | 1 Register | (CLKCTL1) |

|-----------|-------|---------|------------|-----------|

|-----------|-------|---------|------------|-----------|

| Bit     | 7      | 6        | 5      | 4   | 3   | 2     | 1      | 0     |

|---------|--------|----------|--------|-----|-----|-------|--------|-------|

| Field   | IPORDY | Reserved | WTOFEN | PCK | SEL | PCKSM | LFXOEN | IPOEN |

| Reset   | 0      | 0        | 0      | 0   | 0   | 0     | 0      | 1     |

| R/W     | R      | R        | R/W    | R/W | R/W | R/W   | R/W    | R/W   |

| Address |        | F83h     |        |     |     |       |        |       |

| Bit    | Description                                                    |

|--------|----------------------------------------------------------------|

| [7]    | Internal Precision Oscillator (IPO) Ready Flag                 |

| IPORDY | 0: The IPO is not ready.                                       |

|        | 1: The IPO is ready.                                           |

| [6]    | Reserved                                                       |

|        | This bit is reserved and must be programmed to 0.              |

| [5]    | Watchdog Timer Oscillator Failure Detection Enable             |

| WTOFEN | 0: Failure detection of Watchdog Timer Oscillator is disabled. |

|        | 1: Failure detection of Watchdog Timer Oscillator is enabled.  |

If an initial starting value other than 0001h is loaded into the Timer High and Low Byte registers, the One-Shot Mode equation must be used to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is calculated using the following equation:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value - PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is calculated using the following equation:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### 10.1.3.8. Capture Mode

In Capture Mode (TMODE=0100), the current timer count value is recorded when the appropriate external Timer Input 0 transition occurs. The Capture count value is written to the Timer PWM0 High and Low Byte registers. The Timer counts timer clocks up to the 16-bit reload value. The TPOL bit in the Timer Control 1 Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input 0 signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in Timer Control 0 Register is set to indicate the timer interrupt is due to an input capture event.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting. The INPCAP bit in Timer Control 0 Register is cleared to indicate the timer interrupt is not due to an input capture event.

Observe the following steps to configure a timer for Capture Mode and initiate the count:

- 1. Write to the Timer Control 1 Register to:

- Disable the timer

- Configure the timer for Capture Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input 0

- 2. Write to the Timer Control 2 Register to choose the timer clock source.

- 3. Write to the Timer Control 0 Register to set the timer interrupt configuration field TICONFIG.

- 4. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001h).

# 17.3.3. USB Control Register

The USB Control Register, shown in Table 172, selects the USB Module endpoint buffer memory addressing method and the endpoint buffer memory section for the USBSD access.

| Bit     | 7        | 6   | 5   | 4     | 3   | 2        | 1 | 0 |

|---------|----------|-----|-----|-------|-----|----------|---|---|

| Field   | Reserved | AI  |     | EPSEL |     | Reserved |   |   |

| Reset   | 0        | 0   | 0   | 0     | 0   | 0        | 0 | 0 |

| R/W     | R        | R/W | R/W | R/W   | R/W | R        | R | R |

| Address |          |     |     | F5    | Bh  |          |   |   |

#### Table 172. USB Control Register (USBCTL)

| Bit   | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| [7]   | Reserved                                                                                 |

|       | This bit is reserved and must be programmed to 0.                                        |

| [6]   | Addressing Select                                                                        |

| AI    | <ol><li>Accesses to the endpoint buffer selected by EPSEL will auto-increment.</li></ol> |

|       | 1: Accesses to the endpoint buffer selected by EPSEL will not auto-increment.            |

| [5:3] | Endpoint Select                                                                          |

| EPSEL | 000: IN endpoint 0 buffer memory.                                                        |

|       | 001: IN endpoint 1 buffer memory.                                                        |

|       | 010: IN endpoint 2 buffer memory.                                                        |

|       | 011: IN endpoint 3 buffer memory.                                                        |

|       | 100: OUT endpoint 0 buffer memory.                                                       |

|       | 101: OUT endpoint 1 buffer memory.                                                       |

|       | 110: OUT endpoint 2 buffer memory.                                                       |

|       | 111: OUT endpoint 3 buffer memory.                                                       |

| [2:0] | Reserved                                                                                 |

| -     | These bits are reserved and must be programmed to 000.                                   |

## 373

# 17.3.16. USB OUT Interrupt Enable Subregister

The USB OUT Interrupt Enable Subregister, shown in Table 185, controls the enabling of OUT endpoint interrupt requests.

#### Table 185. USB OUT Interrupt Enable Subregister (USBOUTIEN)

| Bit            | 7                                                                                                                                    | 6                                                                                                                                    | 5 | 4       | 3       | 2       | 1       | 0   |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---|---------|---------|---------|---------|-----|

| Field          | Reserved                                                                                                                             |                                                                                                                                      |   | OUT3IEN | OUT2IEN | OUT1IEN | OUT0IEN |     |

| Reset          | 0                                                                                                                                    | 0                                                                                                                                    | 0 | 0       | 0       | 0       | 0       | 0   |

| R/W            | R                                                                                                                                    | R                                                                                                                                    | R | R       | R/W     | R/W     | R/W     | R/W |

| Address        |                                                                                                                                      | If USBSA = 2Dh in the USB Subaddress Register,<br>accessible through the USB Subdata Register                                        |   |         |         |         |         |     |

| Bit            | Descriptio                                                                                                                           | Description                                                                                                                          |   |         |         |         |         |     |

| [7:4]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 0000.                                                           |                                                                                                                                      |   |         |         |         |         |     |

| [3]<br>OUT3IEN | 0: Interrupts                                                                                                                        | OUT Endpoint 3 Interrupt Enable<br>0: Interrupts from OUT endpoint 3 are disabled.<br>1: Interrupts from OUT endpoint 3 are enabled. |   |         |         |         |         |     |

| [2]<br>OUT2IEN | OUT Endpoint 2 Interrupt Enable<br>0: Interrupts from OUT endpoint 2 are disabled.<br>1: Interrupts from OUT endpoint 2 are enabled. |                                                                                                                                      |   |         |         |         |         |     |

| [1]<br>OUT1IEN | OUT Endpoint 1 Interrupt Enable<br>0: Interrupts from OUT endpoint 1 are disabled.<br>1: Interrupts from OUT endpoint 1 are enabled. |                                                                                                                                      |   |         |         |         |         |     |

| [0]<br>OUTOIEN | OUT Endpoint 0 Interrupt Enable<br>0: Interrupts from OUT endpoint 0 are disabled.<br>1: Interrupts from OUT endpoint 0 are enabled. |                                                                                                                                      |   |         |         |         |         |     |

| Bit            | Description (Continued)                                                                                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| [1]<br>CHAIN32 | Chain DMA3and DMA2<br>0: DMA3 and DMA2 are independent of each other.                                                       |

|                | <ol> <li>DMA3 and DMA2 are chained together, as described in the <u>Chain Operation</u> section on<br/>page 393.</li> </ol> |

| [0]            | Chain DMA1 and DMA0                                                                                                         |

| CHAIN10        | 0: DMA1 and DMA0 are independent of each other.                                                                             |

|                | <ol> <li>DMA1 and DMA0 are chained together, as described in the <u>Chain Operation</u> section on<br/>page 393.</li> </ol> |

# 18.3.4. DMA Source Address Subregisters

The DMAxSRCH and DMAxSRCL subregisters, shown in Tables 207 and 208, combine to form the 12-bit source address for the DMA transaction. Upon each byte transfer, the source address is updated based on the SRCCTL configuration in the DMAx Control 0 Subregister. In addition, DMAxSRCH contains transfer in list (TXLIST) control.

| Table 207. DMA Source Address High S | Subregister (DMAxSRCH) |

|--------------------------------------|------------------------|

|--------------------------------------|------------------------|

| Bit     | 7      | 6                                                                                | 5        | 4 | 3   | 2   | 1   | 0   |

|---------|--------|----------------------------------------------------------------------------------|----------|---|-----|-----|-----|-----|

| Field   | TXLIST |                                                                                  | Reserved |   |     | SR  | СН  |     |

| Reset   | 0      | 0                                                                                | 0        | 0 | 0   | 0   | 0   | 0   |

| R/W     | R      | R                                                                                | R        | R | R/W | R/W | R/W | R/W |

| Address | If DMA | If DMASA = 0h in the DMAxSA Register, accessible through the DMA 0–3 Subregister |          |   |     |     |     |     |

| Bit           | Description                                                                                                                                                       |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>TXLIST | <b>Transfer In List</b><br>TXLIST has an effect only during linked list operation, see the <u>Linked List Control Options</u><br>section on page 395 for details. |

| [6:4]         | Reserved<br>These bits are reserved and must be programmed to 000.                                                                                                |

| [3:0]<br>SRCH | Source Address High<br>0–F: Upper 4 bits of the DMA source address.                                                                                               |

output, ESOUT[3:0], that is available for a particular port pin. See the <u>General-Purpose</u> <u>Input/Output</u> chapter on page 55 to learn more regarding alternate function selection.

# 19.4. Timing Considerations

The Event System essentially performs a multiplexing function. Signals sourced to Event System channels do not go through a synchronization process within the Event System. As such, the signals on Event System channels must be sufficient in duration for detection by their corresponding destinations. Any source and destination pair that are using the same clock, one of SYSCLK, PCLK, or the WTO, can be connected to each other via the Event System without concern about source signal duration. When the Event System source and destination pair are using dissimilar clocks, the Event System source signal should be at least 1.5 times the duration of the clock period of the Event System destination to assure that the destination will detect the signal from the source.

# 19.5. Event System Usage Examples

To illustrate the usage of the Event System, let's examine the following two examples.

**Example 1: Triggering Periodic ADC Conversions Using a Timer.** In this example, a timer serves as the signal source to Event System channel 0 and the this channel is selected to trigger ADC conversions.

- Select Timer 0 out as the signal source for Event System channel 0, as follows:

- Write 00h to the ESSSA Register to select the ESCH0SRC Subregister.

- Write 10h to the ESSSD Register. This accesses the ESCH0SRC Subregister to select Timer 0 out as the Event System channel 0 source.

- Configure the ADC conversion parameters. For instance, the ADC could be configured with a window function such that interrupts are generated only when the window is exceeded.

- If a DMA is desired, configure the DMA Controller to transfer the ADC results to memory.

- Configure the ADC to respond to Event System channel 0, as follows:

- Write 04h to the ESDSA Register to select the ESDST04CH Subregister.

- Write 08h to the ESDSD Register. This accesses ESDST04CH Subregister to enable Event System connection to the ADC and to select channel 0 as input to the ADC.

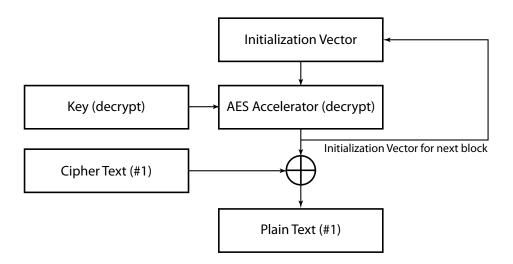

Figure 67. OFB Mode Decryption Flow Diagram

#### 20.2.4.2. OFB Mode Encryption Example

The following steps are required to support OFB Mode encryption operation.

- 1. Write the AESCTRL Register as follows: AES\_EN=1, MODE=01 (OFB), DECRYPT=0, AUTODIS=1.

- 2. Write the AESKEY Register with the encryption key.

- 3. Set the IVEN bit.

- 4. Write the Initialization Vector to the AESIV Register.

- 5. Clear the IVEN bit; DMA and IRQ will not occur while this bit is set.

- 6. Write the plain text data to the AESDATA Register, or use DMA.

- 7. Set the START/BUSY bit in the AESSTAT Register, or use auto-start by setting AUTODIS=0 in <u>Step 1</u>.

- 8. Poll the START/BUSY bit, or use an interrupt.

- 9. Read the cipher text from the AESDATA Register, or use DMA. The Initialization Vector is overwritten in preparation for the next 128-bit data block AES encryption operation, as shown in Figure 66.

464

# Chapter 22. Digital-to-Analog Converter

The F6482 Series MCUs include a high-performance Digital-to-Analog Converter (DAC). This DAC converts a 12-bit digital input code to an analog output signal. The DAC offers the following features:

- 12-bit resolution

- Output driven externally on GPIO; internal connections to comparators and ADC

- Conversion initiated by software or Event System input

- Data buffering option

- Data can be left- or right-justified with either unsigned (binary) or signed (two's-complement) format

- DMA support

- Internal positive voltage reference selections of A<sub>VDD</sub> or the DAC V<sub>REF</sub> from the Reference System (2.5V, 2.0V, 1.5V, 1.25V) which is driven on V<sub>REF</sub>+ for decoupling

- Ability to utilize external reference voltage

- Three power settings providing programmable power vs. settling time; see the <u>Electri-</u> <u>cal Characteristics</u> chapter on page 598 to learn more

# 22.1. Architecture

The DAC architecture, shown in Figure 78, consists of a data register, an internal voltage reference buffer, and a 12-bit DAC.

| Bit     | Description (Continued)                                                              |  |  |  |

|---------|--------------------------------------------------------------------------------------|--|--|--|

| [5]     | Programmable Reference Source Selection                                              |  |  |  |

| PREFSRC | 0: VBIAS is the highest tap of the Programmable Reference.                           |  |  |  |

|         | 1: AV <sub>DD</sub> is the highest tap of the Programmable Reference.                |  |  |  |

| [4:0]   | Programmable Reference Level Selection                                               |  |  |  |

| PREFLVL | 0000 to 1111: Programmable reference level=(PREFSRC selection) * (PREFLVL + 1) ÷ 32. |  |  |  |

# 26.3.3. LCD Clock Register

The LCD Clock Register, shown in Table 269, controls the clocking of the LCD including: clock selection, clock prescale division and frame clock division.

#### Table 269. LCD Clock Register (LCDCLK)

| Bits              | 7                                                                                                                                                                                                                           | 6                                                                                                                                                                              | 5        | 4   | 3   | 2   | 1   | 0   |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-----|-----|-----|-----|

| Field             | CLKSEL                                                                                                                                                                                                                      |                                                                                                                                                                                | PRESCALE |     |     | FC  | DIV |     |

| Reset             | 0                                                                                                                                                                                                                           | 0                                                                                                                                                                              | 0        | 0   | 0   | 0   | 0   | 0   |

| R/W               | R/W                                                                                                                                                                                                                         | R/W                                                                                                                                                                            | R/W      | R/W | R/W | R/W | R/W | R/W |

| Address           |                                                                                                                                                                                                                             |                                                                                                                                                                                |          | FB  | 3h  |     |     |     |

| Bit               | Descriptio                                                                                                                                                                                                                  | n                                                                                                                                                                              |          |     |     |     |     |     |

| [7]<br>CLKSEL     | LCD Clock<br>0: PCLK.<br>1: WTO.                                                                                                                                                                                            |                                                                                                                                                                                |          |     |     |     |     |     |

| [6:4]<br>PRESCALE | LCD Clock Prescale Divider<br>000: Divide by 1.<br>001: Divide by 2.<br>010: Divide by 4.<br>011: Divide by 8.<br>100: Divide by 16.<br>101: Divide by 32.<br>110: Reserved.<br>111: Reserved.                              |                                                                                                                                                                                |          |     |     |     |     |     |

| [3:0]<br>FDIV     | Frame Div<br>0000: Divid<br>0001: Divid<br>0010: Divid<br>0010: Divid<br>0100: Divid<br>0101: Divid<br>0111: Divid<br>1000: Divid<br>1001: Divid<br>1011: Divid<br>1011: Divid<br>1101: Divid<br>1101: Divid<br>1111: Divid | e by 8.<br>e by 9.<br>e by 10.<br>e by 11.<br>e by 12.<br>e by 13.<br>e by 14.<br>e by 16.<br>e by 20.<br>e by 22.<br>e by 22.<br>e by 24.<br>e by 26.<br>e by 28.<br>e by 30. |          |     |     |     |     |     |

## Z8 Encore! XP<sup>®</sup> F6482 Series Product Specification

| 16 KB Flash<br>Program Memory | Addresses<br>3FFFh |  |

|-------------------------------|--------------------|--|

| Page 31                       | 3DFFh              |  |

| Page 30                       | 3BFFh              |  |

| Page 29                       | 39FFh              |  |

| Page 28                       | 37FFh              |  |

| I                             |                    |  |

|                               |                    |  |

| i                             |                    |  |

| Page 3                        | 07FFh              |  |

| Page 2                        | 05FFh              |  |

| Page 1                        | 03FFh              |  |

| Page 0                        | 01FFh              |  |

|                               | 0000h              |  |

| 32 KB Flash<br>Program Memory | Addresses<br>7FFFh |  |

|-------------------------------|--------------------|--|

| Page 63                       | 7DFFh              |  |

| Page 62                       | 7BFFh              |  |

| Page 61                       | 79FFh              |  |

| Page 60                       | 77FFh              |  |

|                               |                    |  |

| Page 3                        | 07FFh              |  |

| Page 2                        | 05FFh              |  |

| Page 1                        | 03FFh              |  |

| Page 0                        | 01FFh              |  |

| Ŭ                             | 0000h              |  |

| 60 KB Flash<br>Program Memory | Addresses<br>′ |

|-------------------------------|----------------|

| Dama 440                      | ] EFFFh        |

| Page 119                      | EDFFh          |

| Page 118                      |                |

| Page 117                      | EBFFh          |

|                               | E9FFh          |

| Page 116                      |                |

|                               | E7FFh          |

I

| 64 KB Flash    | Addresses |

|----------------|-----------|

| Program Memory | /         |

|                |           |

| Page 127 | FFFFh |

|----------|-------|

|          | FDFFh |

| Page 126 | FBFFh |

| Page 125 |       |

| Page 124 | F9FFh |

|          | F7FFh |

1 | | |

T

|        | 07551 |

|--------|-------|

| Page 3 | 07FFh |

| Page 2 | 05FFh |

|        | 03FFh |

| Page 1 | 01FFh |

| Page 0 |       |

|        | 0000h |

|        | 07556 |

|--------|-------|

| Page 3 | 07FFh |

| Page 2 | 05FFh |

| Page 1 | 03FFh |

|        | 01FFh |

| Page 0 | 0000h |