Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 24MHz                                                     |

| Connectivity               | DALI, DMX, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                              |

| Number of I/O              | 67                                                        |

| Program Memory Size        | 60KB (60K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 3.75K x 8                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                               |

| Data Converters            | A/D 12x12b; D/A 1x12b                                     |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 80-LQFP                                                   |

| Supplier Device Package    | 80-LQFP                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6082at024xk |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Z8 Encore! XP<sup>®</sup> F6482 Series Product Specification

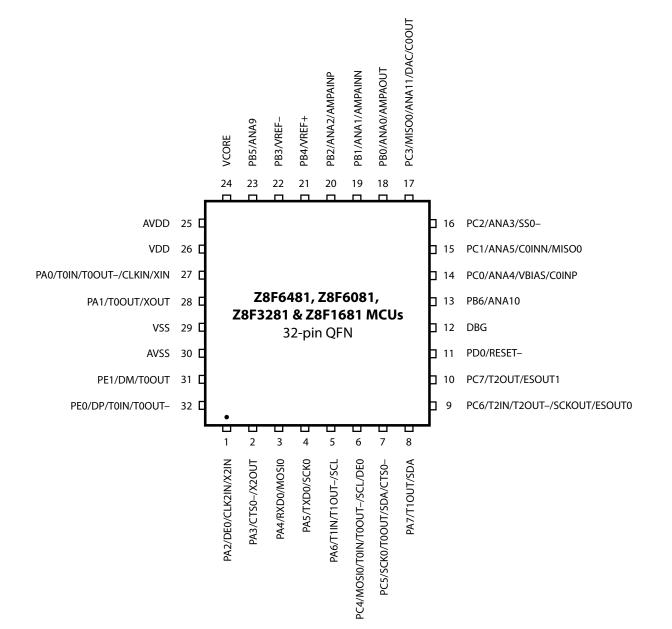

Figure 2. Z8F6481, Z8F6081, Z8F3281 and Z8F1681 MCUs, 32-Pin Quad Flat No Lead (QFN) Package

**Note:** It is recommended to connect the QFN bottom pad to  $V_{SS}$ .

| PCLK Sources                           | Characteristics                                                                                                         | Required Setup                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision Oscillator<br>(IPO) | <ul> <li>32.768kHz nominal</li> <li>± 2% accuracy with factory trim</li> <li>No external components required</li> </ul> | <ul> <li>Unlock the Clock Control registers</li> <li>Enable the IPO</li> <li>Switch System Clock sources as described<br/>in the <u>PCLK Source Switching</u> section on<br/>page 102</li> <li>Select PCLK as the clock source for any<br/>desired peripheral(s) in the appropriate<br/>peripheral control register(s)</li> </ul>                                                                                                                 |

| External Clock 2 Drive                 | <ul> <li>32.768kHz when used as<br/>PCLK source</li> <li>Accuracy dependent on<br/>external clock source</li> </ul>     | <ul> <li>Write GPIO registers to configure PA2 pin<br/>for external clock function, CLK2IN</li> <li>Apply external clock signal to GPIO</li> <li>Unlock the Clock Control registers</li> <li>Switch System Clock sources as described<br/>in the <u>PCLK Source Switching</u> section on<br/>page 102</li> <li>Select PCLK as the clock source for any<br/>desired peripheral(s) in the appropriate<br/>peripheral control register(s)</li> </ul> |

#### Table 36. Peripheral Clock Sources and Usage

#### 8.2.2.1. PCLK Source Switching

PCLK source switching provides glitch free operation in that changing the clock source or prescale setting will not cause clock glitches. In accomplishing glitch free clock switching operation, there is a delay from the writing of PCKSEL to the actual switching from the currently active clock source to the new, desired clock source. To switch from one PCLK source to another, observe the following procedure:

- 1. Unlock the clock control registers.

- 2. Write to the appropriate clock control registers to configure the desired clock source.

- 3. Enable the desired clock source.

- 4. Wait for the newly enabled clock source to stabilize.

- 5. Write CLKCTL1 to select PCLK.

- 6. After the System Clock source has been switched, disable any unnecessary clock sources, if desired.

- 7. The clock control registers can be locked by clearing CSTAT.

### 8.2.3. PLL Clock Selection

The PLL Clock (PLL<sub>CLK</sub>) is driven by the on-chip PLL. The two possible sources for the PLL are the High Frequency Crystal Oscillator (HFXO) and the External Clock Drive.

142

| Bit                       | Description (Continued)                                                                     |

|---------------------------|---------------------------------------------------------------------------------------------|

| [4:1]<br>PAD <i>x</i> ENL | Port Ax or Port Dx Interrupt Request Enable Low Bit x indicates the specific PAD bit (4–1). |

| [0]<br>PA0ENL             | Port A0 Interrupt Request Enable Low Bit                                                    |

### 9.4.8. IRQ3 Enable High and Low Bit Registers

Table 65 describes the priority control for IRQ3. The IRQ3 Enable High and Low Bit registers, shown in Tables 66 and 67, form a priority-encoded enabling for interrupts in the Interrupt Request 3 Register. Priority is generated by setting bits in each register.

| IRQ3ENH[ <i>x</i> ]                       | IRQ3ENL[x] | Priority | Description |  |  |  |  |

|-------------------------------------------|------------|----------|-------------|--|--|--|--|

| 0                                         | 0          | Disabled | Disabled    |  |  |  |  |

| 0                                         | 1          | Level 1  | Low         |  |  |  |  |

| 1                                         | 0          | Level 2  | Nominal     |  |  |  |  |

| 1                                         | 1          | Level 3  | High        |  |  |  |  |

| Note: x indicates register bits from 0–7. |            |          |             |  |  |  |  |

Table 65. IRQ3 Enable and Priority Encoding

#### Table 66. IRQ3 Enable High Bit Register (IRQ3ENH)

| Bit     | 7      | 6      | 5      | 4      | 3                 | 2                 | 1     | 0     |

|---------|--------|--------|--------|--------|-------------------|-------------------|-------|-------|

| Field   | AESENH | MCTENH | U1RENH | U1TENH | C3ENH/<br>DMA3ENH | C2ENH/<br>DMA2ENH | C1ENH | COENH |

| Reset   | 0      | 0      | 0      | 0      | 0                 | 0                 | 0     | 0     |

| R/W     | R/W    | R/W    | R/W    | R/W    | R/W               | R/W               | R/W   | R/W   |

| Address | FCAh   |        |        |        |                   |                   |       |       |

| Bit           | Description                                           |

|---------------|-------------------------------------------------------|

| [7]<br>AESENH | AES Interrupt Request Enable High Bit                 |

| [6]<br>MCTENH | Multi-Channel Timer Interrupt Request Enable High Bit |

| [5]<br>U1RENH | UART1 Receive Interrupt Request Enable High Bit       |

### **10.1.2.** Timer Reload High and Low Byte Registers

The Timer 0–2 Reload High and Low Byte (T*x*RH and T*x*RL) registers, shown in Tables 77 and 78, store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to these Timer Reload High Byte registers are stored in a temporary holding register. When a write to the Timer Reload Low Byte Register occurs, this temporary holding register value is written to the Timer High Byte Register. This operation allows simultaneous updates of the 16-bit timer reload value.

In Compare Mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

| Bit                                         | 7                                             | 6               | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------------------------------------|-----------------------------------------------|-----------------|-----|-----|-----|-----|-----|-----|

| Field                                       | TRH                                           |                 |     |     |     |     |     |     |

| Reset                                       | 1                                             | 1 1 1 1 1 1 1 1 |     |     |     |     |     |     |

| R/W                                         | R/W                                           | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |

| Address                                     | Address T0RH @ F02h, T1RH @ F0Ah, T2RH @ F12h |                 |     |     |     |     |     |     |

| Note: x references bits in the range [2:0]. |                                               |                 |     |     |     |     |     |     |

#### Table 77. Timer 0–2 Reload High Byte Registers (TxRH)

#### Table 78. Timer 0–2 Reload Low Byte Registers (TxRL)

| Bit          | 7                                            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|--------------|----------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Field        | TRL                                          |     |     |     |     |     |     |     |  |

| Reset        | 1                                            | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W          | R/W                                          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address      | ddress T0RL @ F03h, T1RL @ F0Bh, T2RL @ F13h |     |     |     |     |     |     |     |  |

| Note: x refe | Note: x references bits in the range [2:0].  |     |     |     |     |     |     |     |  |

| Bit   | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| [7:0] | Timer Reload Register High and Low                                                            |

| TRH,  | These two bytes form the 16-bit reload value, {TRH[7:0], TRL[7:0]}. This value is used to set |

| TRL   | the maximum count value which initiates a timer reload to 0001h. In Compare Mode, these two   |

|       | bytes form the 16-bit Compare value.                                                          |

| Bit                     | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6]<br>TPOL<br>(cont'd) | <ul> <li>PWM Dual Output Mode</li> <li>0: Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in Timer Control 0 Register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).</li> <li>1: Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon PWM count match and forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in Timer Control 0 Register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).</li> </ul> |

|                         | <b>Capture Restart Mode</b><br>0: Count is captured on the rising edge of the Timer Input 0 signal.<br>1: Count is captured on the falling edge of the Timer Input 0 signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                         | <ul> <li>Comparator Counter Mode</li> <li>When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer reload.</li> <li>Triggered One-Shot Mode and Dual Input Triggered One-Shot Mode</li> <li>OUTCTL = 0</li> <li>0: Timer counting is triggered on the rising edge of the Timer Input 0 signal.</li> <li>1: Timer counting is triggered on the falling edge of the Timer Input 0 signal.</li> <li>OUTCTL = 1</li> <li>0: Timer counting is triggered on the rising edge of the Timer Input 0 signal.</li> <li>1: Reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         | <ul> <li>Demodulation Mode This functionality applies only if TPOLHI bit in Timer Control 2 Register is 0. If TPOLHI bit is 1 then timer counting is triggered on any edge of the Timer Input 0 signal and the current count is captured on both edges. The current count is captured into PWM0 registers on rising edges and PWM1 registers on falling edges of the Timer Input 0 signal. 0: Timer counting is triggered on the rising edge of the Timer Input 0 signal. The current count is captured into PWM0 High and Low byte registers on subsequent rising edges of the Timer Input 0 signal. </li> <li>1: Timer counting is triggered on the falling edge of the Timer Input 0 signal. The current count is captured into PWM1 High and Low byte registers on subsequent falling edges of the Timer Input 0 signal. </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Subaddress Register, USB Control Register and USB Subdata Register combine to provide write access to all USB Module controls and buffer memory.

This register contains an address in the USB Module memory space selected by the USBCTL Register. For access to endpoint buffer spaces (64 bytes maximum each), bits 7 and 6 of this register are forced to 0 by hardware.

| Bit            | 7                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                        | 5    | 4   | 3     | 2    | 1 | 0   |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|-----|-------|------|---|-----|

| Field          | ADDRSEL                                                                                                                                                                                                                                                                                                                |                                                                                                                          |      |     | USBSA |      |   |     |

| Reset          | 0                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                        | 0    | 0   | 0     | 0    | 0 | 0   |

| R/W            | R/W                                                                                                                                                                                                                                                                                                                    | R/W1                                                                                                                     | R/W1 | R/W | R/W   | R/W1 | W | R/W |

| Address        | F59h                                                                                                                                                                                                                                                                                                                   |                                                                                                                          |      |     |       |      |   |     |

| Bit            | Description                                                                                                                                                                                                                                                                                                            | Description                                                                                                              |      |     |       |      |   |     |

| [7]<br>ADDRSEL | 0: Special Fu                                                                                                                                                                                                                                                                                                          | Addressing Select<br>0: Special Function Register (SFR).<br>1: Endpoint buffer selected by EPSEL in the USBCTL Register. |      |     |       |      |   |     |

| [6:0]<br>USBSA | USB Subaddress<br>00-7F: Selects the USB Subdata Register accessed when USBSD is written. When access-<br>ing endpoint buffer memories, if AI=0 in USBCTL, this register auto-increments whenever<br>the USBSD is read (OUT endpoints) or written (IN endpoints) and wraps back to 0 at the<br>address space boundary. |                                                                                                                          |      |     |       |      |   |     |

Table 170. USB Subaddress Register (USBSA)

## 17.3.22. USB OUT 1–3 Control and Status Subregisters

The USB OUT 1–3 Control and Status subregisters, shown in Table 191, provide control and status for USB OUT endpoints 1–3.

| Table 191. USB | OUT 1–3 Contro | I and Status | Subregisters ( | (USBOxCS) |

|----------------|----------------|--------------|----------------|-----------|

|----------------|----------------|--------------|----------------|-----------|

| Bit            | 7                                                                             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5 | 4 | 3                       | 2     | 1 | 0   |  |  |

|----------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-------------------------|-------|---|-----|--|--|

| Field          |                                                                               | Reserved OUTBUS STALL<br>Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |                         |       |   |     |  |  |

| Reset          | 0                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0 | 0 | 0                       | 0     | 0 | 0   |  |  |

| R/W            | R                                                                             | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R | R | R                       | R     | R | R/W |  |  |

| Address        |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   | he USB Sul<br>USB Subda |       | • |     |  |  |

| Bit            | Descriptio                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |   |                         |       |   |     |  |  |

| [7:2]          | Reserved<br>These bits                                                        | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |   |                         |       |   |     |  |  |

| [1]<br>OUTBUSY | Software se<br>OUTBUSY<br>0 transition<br>0: Software<br>memory<br>1: The USE | <ul> <li>OUT Busy Status</li> <li>Software sets OUTBUSY by reloading the USBOxBC Register with a dummy value. While OUTBUSY is set, software should not read the buffer memory for this OUT endpoint. A 1 to 0 transition of OUTBUSY generates a USB interrupt request for the OUT endpoint.</li> <li>0: Software has control of the OUT endpoint buffer memory. The OUT endpoint buffer memory is ready for reading by software.</li> <li>1: The USB Module has control of the OUT endpoint buffer memory which is empty and ready to receive the next data packet from the host.</li> </ul> |   |   |                         |       |   |     |  |  |

| [0]<br>STALL   |                                                                               | end a STAL<br>STALL hanc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |   | o the endpo             | pint. |   |     |  |  |

379

# 19.3. Destination Selection

A variety of peripherals and GPIOs can be selected to be a destination for an Event System channel. Connecting a destination to an Event System channel is controlled in the Event System Destination Channel subregisters, ESDSTxCH. If DSTCON in the ESDSTxCH Subregister is set, the destination is connected to the Event System channel specified in DSTCHSEL; otherwise, the destination is connected to logic 0. Because each destination can connect to any Event System channel, multiple peripherals can be a destination for the same Event System channel.

The ESDSTxCH subregisters are accessed using the Event System Destination Subaddress Register (ESDSA) and the Event System Destination Subdata Register (ESDSD). An ESDSTxCH Subregister is selected by ESDSD in the ESDSA Register, and is accessed by writing/reading the ESDSD bit in the ESDSD Register.

Table 218 lists the Event System destinations.

| Peripheral    | Signal Connection                  |  |  |  |  |

|---------------|------------------------------------|--|--|--|--|

| Timer 0       | Input 0                            |  |  |  |  |

|               | Input 1                            |  |  |  |  |

| Timer 1       | Input 0                            |  |  |  |  |

|               | Input 1                            |  |  |  |  |

| Timer 2       | Input 0                            |  |  |  |  |

|               | Input 1                            |  |  |  |  |

| Multi-Channel | Multi-Channel Timer in A           |  |  |  |  |

| Timer         | Multi-Channel Timer in B           |  |  |  |  |

|               | Multi-Channel Timer in C           |  |  |  |  |

|               | Multi-Channel Timer in D           |  |  |  |  |

|               | Multi-Channel Timer in             |  |  |  |  |

| RTC           | RTC Source Select                  |  |  |  |  |

| ADC           | Convert                            |  |  |  |  |

| DAC           | Convert                            |  |  |  |  |

| Port C        | Port C[7:6] pins using ESOUT [1:0] |  |  |  |  |

| Port E        | Port E[6:3] pins using ESOUT [3:0] |  |  |  |  |

| Port F        | Port F[3:0] pins using ESOUT [3:0] |  |  |  |  |

Table 218. Event System Destinations

Four Event System GPIO outputs, ESOUT[3:0], are available to the port pins listed in Table 218. The GPIO PxAF, PxAFS1, and PxAFS2 subregisters select the Event System

# 19.6. Event System Register Definitions

Four register addresses provide access to the Event System subregisters that control source and destination selection for each Event System channel. Table 219 lists these Event System registers and subregisters.

| Event System Source S                                         | election Registers and Su | ubregisters                                             |  |  |  |  |

|---------------------------------------------------------------|---------------------------|---------------------------------------------------------|--|--|--|--|

| Register Mnemonic                                             | Address                   | Register Name                                           |  |  |  |  |

| ESSSA                                                         | F98h                      | Event System Source Subaddress Register                 |  |  |  |  |

| ESSSD                                                         | F99h                      | Event System Source Subdata Register                    |  |  |  |  |

| Subregister Mnemonic                                          | Subregister Address*      | Subregister Name                                        |  |  |  |  |

| ESCHxSRC                                                      | 0–7h                      | Event System Channel 0–7 Source subregisters            |  |  |  |  |

| Event System Destination Selection Registers and Subregisters |                           |                                                         |  |  |  |  |

| Register Mnemonic                                             | Address                   | Register Name                                           |  |  |  |  |

| ESDSA                                                         | F9Ah                      | Event System Destination Subaddress Register            |  |  |  |  |

| ESDSD                                                         | F9Bh                      | Event System Destination Subdata Register               |  |  |  |  |

| Subregister Mnemonic                                          | Subregister Address*      | Subregister Name                                        |  |  |  |  |

| ESCHDSTx                                                      | 0–3Fh                     | Event System Destination 0–3F Channel<br>subregisters   |  |  |  |  |

| Note: *The ESSSA Register<br>DSTx Subregister add             |                           | pregister address; the ESDSA Register contains the ESCH |  |  |  |  |

#### Table 219. Event System Registers and Subregisters

For both manual start and auto-start, while the accelerator is processing, the START/ BUSY bit remains set. The AES accelerator will detect as an error any attempt to write the AESKEY, AESIV or AESDATA registers during an encryption/decryption operation and access attempts are blocked. The detection of an error does not affect the encryption/ decryption operation but ERROR in the AESSTAT Register is set.

The completion of an encryption/decryption operation is indicated by the START/BUSY bit transition from one to zero. An interrupt will be generated if IRQ is set in the AESC-TRL Register.

### 20.2.1. AES Operation and DMA

Two DMA requests are provided: RxIRQ for receive data, and TxIRQ for transmit data. The load status bits used to control DMA receive and transmit data requests. When AESEN is set and KEYLD=1, DATALD=0 and IVLD=1 (if applicable), RxIRQ is asserted for DMA data transfer. When the DMA Controller has written; i.e., 16 bytes to the AESDATA Register, if AUTODIS=0, the AES accelerator will start processing.If AUTODIS=1, processing can be started by setting START/BUSY. When encryption/ decryption completes, START/BUSY is cleared, DATALD is cleared and the AES accelerator asserts TxIRQ. When 16 bytes are read from the AESDATA Register, TxIRQ is deasserted and RxIRQ is again asserted. This sequence will continue as long as the DMA configuration, as described in the <u>Direct Memory Access Controller</u> chapter on page 389. Table 227 summarizes DMA request conditions.

| Mode                    | START/<br>BUSY | IVLD      | KEYLD        | DATALD  | RxIRQ | TxIRQ |

|-------------------------|----------------|-----------|--------------|---------|-------|-------|

|                         | 0              | 0         | Х            | Х       | 0     | 0     |

|                         | 0              | 0         | 0            | Х       | 0     | 0     |

| 01 (OFB)<br>or 10 (CBC) | 0              | 1         | 1            | 0       | 1     | 0     |

| 0110(000)               | 1*             | 1         | 1            | 1       | 0     | 0     |

| -                       | 1→0            | 1         | 1            | 1→0     | 0     | 1     |

|                         | 0              | Х         | 0            | Х       | 0     | 0     |

|                         | 0              | Х         | 1 0          |         | 1     | 0     |

| 00 (ECB) -              | 1*             | Х         | 1            | 1       | 0     | 0     |

|                         | 1→0            | Х         | 1            | 1       | 0     | 1     |

| Note: *If AUTODI        | S=1, START/E   | BUSY must | be set by so | ftware. |       |       |

Table 227. Register Bit Settings for DMA Support, AUTODIS=0

## 20.2.2. AES Electronic Codebook (ECB) Mode

The following subsections describe AES ECB Mode.

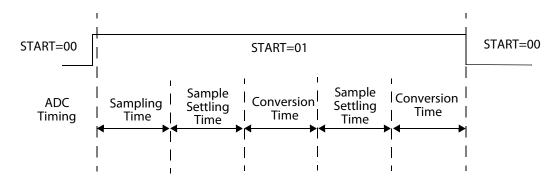

Figure 75. ADC Timing Diagram for 2-Pass 14-Bit Resolution with INMODE=10, 11

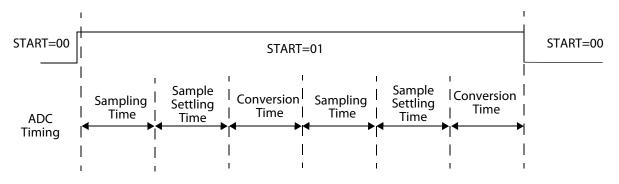

Figure 76. ADC Timing Diagram for 2-Pass 14-Bit Resolution with INMODE=01

#### 21.2.6.3. ADC Wake-up, Sampling, and Settling

As the ADC is designed for low-power applications, the ADC core can be configured to auto-disable when no further conversions are scheduled by clearing ADC to 00 in the PWRCTL1 Register. When triggered to start a new conversion while the ADC is idle and ADC=00, the ADC wake-up period,  $T_{WAKE\_ADC}$ , is automatically inserted prior to sampling (see the <u>Electrical Characteristics</u> chapter on page 598). If selected as VREF+, the internal voltage reference buffer will also automatically wake-up prior to sampling. When the conversion is completed and ADC = 00, the ADC's auto-disable feature will automatically disable the ADC when no further conversions are scheduled.

If performing multiple sequential conversions due to averaging, scanning or continuous conversion, it is recommended to turn off the ADC auto-disable function by setting ADC to 11 in the PWRCTL1 Register. When ADC is set to 11, the ADC is continuously enabled and  $T_{WAKE\_ADC}$  is not incurred when the ADC is triggered to perform a conversion. After setting ADC=11, wait  $T_{WAKE\_ADC}$  prior to triggering an ADC conversion.

### 21.2.8. ADC Interrupts and DMA

The ADC can generate an interrupt request upon each new ADC result for any completed conversion or calibration (START= 01, 10, 11). The ADC can also generate an interrupt if the conversion result is outside the range defined by the window threshold registers (ADCUWINH, ADCUWINL, ADCLINH, ADCLWINL). Use the IRQ bit in the ADC Control 0 Register to select whether interrupts are generated due to only exceeding the window thresholds or due to both exceeding the window thresholds and end of convert. An interrupt request that is pending when the ADC is disabled or idle (ready) is not automatically cleared.

The ADC will assert a DMA request upon each new ADC result, and will deassert a DMA request whenever the ADCD\_L Register (DMACTL=0) or ADCD\_H Register (DMACTL=1) is read by the DMA or software. When DMACTL=0, the typical goal is to transfer both data bytes, and the DMA is configured to have fixed word address control for the DMA source address; the source address is configured to be the ADCD\_H Register address. When DMACTL=1, the typical goal is to transfer only the most significant data byte, and the DMA is configured to have fixed address control for the DMA source address; the source to have fixed address control for the DMA source address; the source to have fixed address control for the DMA source address; the source address is configured to be the ADCD H Register address; the source address is configured to be the ADCD H Register address.

If starting a new ADC conversion and DMA transfer sequence, reading the ADC\_L Register (DMACTL=0) or the ADC\_H Register (DMACTL=1) prior to enabling DMA and starting conversion ensures that any residual ADC DMA request from prior ADC activity is deasserted. A DMA request is not asserted upon the completion of an offset or gain calibration.

### 21.2.9. Calibration and Compensation

Both gain and offset calibration can be performed in situ to achieve even higher accuracy than specified in the <u>Electrical Characteristics</u> chapter on page 598. These calibration operations are performed using the current ADC configuration, as defined by the INMODE, PRESCALE, ST, and SST bits. After these parameters are reconfigured, initiating calibration prior to performing conversions can optimize results. Only initiate calibration when continuous conversion is not selected (i.e., CONTCONV = 0).

Offset calibration is performed when the START bits are written to 10. Prior to initiating offset calibration, 14-bit resolution must be selected by setting RESOLUT = 1. The offset result can be used for both 12-bit and 14-bit resolution conversions. The calibration is complete when START is cleared to 00. The offset calibration result is stored in the OFF-SET field in the ADCOFF Register as a two's-complement value, and is automatically applied to compensate subsequent conversions by hardware. OFFSET can be read by software and can be stored and rewritten any time to the ADCOFF Register to allow consistent usage of offset calibrations. For example, when using multiple input modes, each mode can exhibit a unique offset calibration value.

# 24.2. Comparator Operation

Two identical general-purpose CMOS analog comparators each provide rail-to-rail operation with four speed-vs.-power settings and three hysteresis options. These comparators are enabled by setting the COMP0 and COMP1 bits in the PWRCTL0 Register, which is described in the <u>Low-Power Modes</u> chapter on page 50. The power setting is determined by the CPOWER bit, which selects current consumption ranging from  $27\mu$ A, with a propagation delay of 150ns, to  $0.2\mu$ A, with a propagation delay of  $10\mu$ s. The low power settings can allow for continuous comparator usage in low-power systems. Hysteresis is selected by the HYST bit; selections range from no hysteresis to 40 mV.

A 4-to-1 input multiplexer exists on each comparator positive input and each comparator negative input. The positive input is selected using the INPSEL bit to be either the temperature sensor, GPIO or one of the op amp outputs, AMPAOUT or AMPBOUT. The negative input is selected using the INNSEL and PREFEN bits to be either a GPIO, a fixed reference (0.75V/1.25V), the bandgap voltage, a programmable internal reference or the DAC output. Multiplexing can be configured such that a GPIO (C0INP/C1INP) pin provides the positive comparator input and/or a GPIO (C0INN/C1INN) provides the negative input. When connecting to GPIO, use the appropriate GPIO alternate function selection, as described in the <u>General-Purpose Input/Output</u> chapter on page 55.

The comparator output polarity is determined by the POLSEL bit. When POLSEL=0, the comparator output is noninverted such that the comparator output is High when the positive comparator input voltage is greater than the negative comparator input voltage. When POLSEL=1, the comparator output is inverted such that the comparator output is Low when the positive comparator input voltage is greater than the negative comparator input voltage.

The output of each comparator can be routed to a GPIO pin, COOUT or C1OUT, as well as to the Event System. When connecting to GPIO, use the appropriate GPIO alternate function selection, as described in the <u>General-Purpose Input/Output</u> chapter on page 55. Additionally, the comparator output state can be read directly from the CSTATUS bit in the COMPCTL Register. An additional output, C01, is the logical OR of each comparator output, and is an Event System source; it is useful for window detection signaling.

A window compare feature provides coordinated detection reporting for the two comparators. WINEN=1 selects Window Mode. The impact of WINEN and POLSEL on the comparator outputs is summarized in <u>Table 256</u> on page 488.

| LCDMODE   |           |      |        | Waveform |

|-----------|-----------|------|--------|----------|

| (LCDCTL2) | # Commons | Duty | Bias   | Туре     |

| 0000      | 1         | 1    | Static | Static   |

| 0001      | 2         | 1/2  | 1/2    | А        |

| 0010      | 2         | 1/2  | 1/2    | В        |

| 0011      | 2         | 1/2  | 1/3    | А        |

| 0100      | 2         | 1/2  | 1/3    | В        |

| 0101      | 3         | 1/3  | 1/2    | А        |

| 0110      | 3         | 1/3  | 1/2    | В        |

| 0111      | 3         | 1/3  | 1/3    | А        |

| 1000      | 3         | 1/3  | 1/3    | В        |

| 1001      | 4         | 1/4  | 1/2    | А        |

| 1010      | 4         | 1/4  | 1/2    | В        |

| 1011      | 4         | 1/4  | 1/3    | А        |

| 1100      | 4         | 1/4  | 1/3    | В        |

| Others    |           | Rese | erved  |          |

Table 265. LCD Mode Selection and Corresponding Waveform Characteristics

#### 26.2.8.1. Static Mode

Static Mode is selected by configuring LCDMODE=0000 in the LCDCTL2 Register. In this mode, only COM0 is used, and each SEGx drives one LCD display segment. Example waveforms for Static Mode are shown in Figure 87.

### 26.3.3. LCD Clock Register

The LCD Clock Register, shown in Table 269, controls the clocking of the LCD including: clock selection, clock prescale division and frame clock division.

#### Table 269. LCD Clock Register (LCDCLK)

| Bits              | 7                                                                                                                                                                                                                           | 6                                                                                                                                                                              | 5        | 4   | 3   | 2   | 1   | 0   |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-----|-----|-----|-----|--|

| Field             | CLKSEL                                                                                                                                                                                                                      |                                                                                                                                                                                | PRESCALE |     |     | FC  | DIV |     |  |

| Reset             | 0                                                                                                                                                                                                                           | 0                                                                                                                                                                              | 0        | 0   | 0   | 0   | 0   | 0   |  |

| R/W               | R/W                                                                                                                                                                                                                         | R/W                                                                                                                                                                            | R/W      | R/W | R/W | R/W | R/W | R/W |  |

| Address           | FB3h                                                                                                                                                                                                                        |                                                                                                                                                                                |          |     |     |     |     |     |  |

| Bit               | Descriptio                                                                                                                                                                                                                  | n                                                                                                                                                                              |          |     |     |     |     |     |  |

| [7]<br>CLKSEL     | LCD Clock<br>0: PCLK.<br>1: WTO.                                                                                                                                                                                            | Selection                                                                                                                                                                      |          |     |     |     |     |     |  |

| [6:4]<br>PRESCALE | 000: Divide<br>001: Divide<br>010: Divide<br>011: Divide<br>100: Divide<br>101: Divide                                                                                                                                      | LCD Clock Prescale Divider<br>000: Divide by 1.<br>001: Divide by 2.<br>010: Divide by 4.<br>011: Divide by 8.<br>100: Divide by 16.<br>101: Divide by 32.<br>110: Reserved.   |          |     |     |     |     |     |  |

| [3:0]<br>FDIV     | Frame Div<br>0000: Divid<br>0001: Divid<br>0010: Divid<br>0010: Divid<br>0100: Divid<br>0101: Divid<br>0111: Divid<br>1000: Divid<br>1001: Divid<br>1011: Divid<br>1011: Divid<br>1101: Divid<br>1101: Divid<br>1111: Divid | e by 8.<br>e by 9.<br>e by 10.<br>e by 11.<br>e by 12.<br>e by 13.<br>e by 14.<br>e by 16.<br>e by 20.<br>e by 22.<br>e by 22.<br>e by 24.<br>e by 26.<br>e by 28.<br>e by 30. |          |     |     |     |     |     |  |

Erase operation, the eZ8 CPU remains idle, but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the OCD, poll the Flash Status Register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

### 27.2.8. Mass Erase

Flash memory can also be mass erased using the Flash Controller, but only by using the On-Chip Debugger. Mass erasing Flash memory sets all bytes to the value FFh. With the Flash Controller unlocked, writing the value 63h to the Flash Control Register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU remains idle, but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status Register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

Mass Erase does not affect the user page in the Flash Information Area. Use Page Erase to erase the user page in the Flash Information Area.

### 27.2.9. Flash Controller Bypass

The Flash Controller can be bypassed so that the control signals for Flash memory can be brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Zilog recommends row programming for gang programming applications and large-volume customers who do not require the in-circuit initial programming of Flash memory. Mass Erase and Page Erase operations are also supported when the Flash Controller is bypassed.

For more information about bypassing the Flash Controller, please contact Zilog Technical Support.

## 27.2.10. Flash Controller Behavior in Debug Mode

The following changes in the behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Block Protect Register is ignored for programming operations

- Programming operations are not limited to the page selected in the Page Select Register

- Bits in the Flash Block Protect Register can be written to 1 or 0

- The second write of the Page Select Register to unlock the Flash Controller is not necessary

534

## 28.3.1. Trim Bit Address Space

All available trim bit addresses and their functions are summarized in Table 288. For details about each, see <u>Tables 290 through 301</u>.

| Address         | Function                                 |

|-----------------|------------------------------------------|

| 0000h           | Reserved                                 |

| 0001h           | Temperature Sensor Trim0                 |

| 0002h           | Temperature Sensor Trim1                 |

| 0003h           | Internal Precision Oscillator            |

| 0004h           | VBO and LVD                              |

| 0005h           | DAC and ADC/DAC Reference Voltage        |

| 0006h           | Band-gap reference and Voltage Regulator |

| 0007h           | WDT trim                                 |

| 0008h           | LCD Trim0                                |

| 0009h           | LCD Trim1                                |

| 000Ah           | Reserved                                 |

| 000Bh           | Reserved                                 |

| 000Ch           | VBIAS Trim                               |

| 000Dh–001<br>Fh | Reserved                                 |

#### Table 288. Trim Bit Address Description

### 28.3.1.1. Trim Bit Address Register 0000h

The Trim Option Bits Register at address 0000h, shown in Table 289, is reserved.

| Bit           | 7                                                     | 6                             | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|-------------------------------------------------------|-------------------------------|---|---|---|---|---|---|

| Field         | Reserved                                              |                               |   |   |   |   |   |   |

| Reset         | 0                                                     | 0                             | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W           | R                                                     | R                             | R | R | R | R | R | R |

| Address       |                                                       | Information Page Memory 0020h |   |   |   |   |   |   |

| Note: X = und | Note: X = undefined; R/W = read/write; R = read-only. |                               |   |   |   |   |   |   |

| Bit   | Description            |

|-------|------------------------|

| [7:0] | Reserved               |

|       | All bits are reserved. |

#### 28.3.1.7. Trim Bit Address 0007h

The Trim Option Bits Register at address 0007h (see Table 297), governs control of the WDT.

| Table 297. Tri | im Option Bits at | t Address 0007h | n (TWDT) |

|----------------|-------------------|-----------------|----------|

|----------------|-------------------|-----------------|----------|

| Bit           | 7                                                               | 6                                                                | 5           | 4        | 3   | 2   | 1   | 0   |  |

|---------------|-----------------------------------------------------------------|------------------------------------------------------------------|-------------|----------|-----|-----|-----|-----|--|

| Field         | Rese                                                            | erved                                                            |             | WDT_TRIM |     |     |     |     |  |

| Reset         | 0                                                               | 1                                                                | Х           | Х        | Х   | Х   | Х   | Х   |  |

| R/W           | R                                                               | R/W                                                              | R/W         | R/W      | R/W | R/W | R/W | R/W |  |

| Address       |                                                                 | Information Page Memory 0027h                                    |             |          |     |     |     |     |  |

| Note: X = uno | defined; $R/W = r$                                              | ead/write; R                                                     | = read-only |          |     |     |     |     |  |

| Bit           | Descriptio                                                      | on                                                               |             |          |     |     |     |     |  |

| [7]           | <b>Reserved</b><br>This bit is r                                | Reserved<br>This bit is reserved and is factory-programmed to 0. |             |          |     |     |     |     |  |

| [6]           | Reserved<br>This bit is reserved and is factory-programmed to 1 |                                                                  |             |          |     |     |     |     |  |

|                   | I his bit is reserved and is factory-programmed to 1. |

|-------------------|-------------------------------------------------------|

| [5:0]<br>WDT_TRIM | WDT Trim                                              |

#### 28.3.1.8. Trim Bit Addresses 0008h and 0009h

The Trim Option Bits registers at addresses 0008h and 00009h, shown in Tables 298 and 299, govern control of the LCD trim bits.

| <b>Table 298.</b> | Trim Option | Bits at | Address  | 0008h  | (TLCD0) |

|-------------------|-------------|---------|----------|--------|---------|

| Tubic 200.        |             | Bits at | Addi C55 | 000011 | (12020) |

| Bit                                                   | 7                             | 6          | 5   | 4   | 3            | 2   | 1   | 0   |

|-------------------------------------------------------|-------------------------------|------------|-----|-----|--------------|-----|-----|-----|

| Field                                                 | Reserved                      | LCDCO_TRIM |     |     | LCDVREG_TRIM |     |     |     |

| Reset                                                 | 0                             | Х          | Х   | Х   | Х            | Х   | Х   | Х   |

| R/W                                                   | R                             | R/W        | R/W | R/W | R/W          | R/W | R/W | R/W |

| Address                                               | Information Page Memory 0028h |            |     |     |              |     |     |     |

| Note: X = undefined; R/W = read/write; R = read-only. |                               |            |     |     |              |     |     |     |

| Bit                   | Description                                 |

|-----------------------|---------------------------------------------|

| [7]                   | Reserved<br>This bit is reserved.           |

| [6:4]<br>LCDCO_TRIM   | LCD Contrast Offset Trim                    |

| [3:0]<br>LCDVREG_TRIM | LCD Voltage Regulator and Current Bias Trim |

| aracteristics and Timing (Continued) |       |                                    |  |  |  |

|--------------------------------------|-------|------------------------------------|--|--|--|

| 6V<br>5°C                            | _     |                                    |  |  |  |

| Max                                  | Units | Conditions                         |  |  |  |

| ±4                                   | LSB   | RESOLUT=0, No gain calibration run |  |  |  |

| -                                    | LSB   | RESOLUT=0, Gain calibration run    |  |  |  |

| +16                                  | ISB   | PESOLUT-1 No gain                  |  |  |  |

#### Table 337. Analog-to-Digital Converter Electrical Character

Min

$V_{DD}$ =1.8V to 3.6V  $T_{A} = -40^{\circ}$ C to +85°C Тур\*

|                      |                                                                                                                                |     | -   | LSB | RESOLUT=0, Gain<br>calibration run    |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------------------------------|

|                      |                                                                                                                                |     | ±16 | LSB | RESOLUT=1, No gain<br>calibration run |

|                      |                                                                                                                                |     | -   | LSB | RESOLUT=1, Gain<br>calibration run    |

|                      | Offset Error                                                                                                                   |     | ±3  | LSB | RESOLUT=0, No offset calibration run  |

|                      |                                                                                                                                |     | ±1  | LSB | RESOLUT=0, Offset<br>calibration run  |

|                      |                                                                                                                                |     | ±12 | LSB | RESOLUT=1, No offset calibration run  |

|                      |                                                                                                                                |     | -   | LSB | RESOLUT=1, Offset<br>calibration run  |

| I <sub>DD</sub> ADCI | ADC Active Current with<br>Internal Reference<br>(REFSEL=1x)                                                                   | 180 |     | μA  | INMODE=0x,<br>POWER=00                |

|                      |                                                                                                                                | 230 |     | μA  | INMODE=1x,<br>POWER=00                |

|                      |                                                                                                                                | 95  |     | μA  | INMODE=0x,<br>POWER=10                |

|                      |                                                                                                                                | 115 |     | μA  | INMODE=1x,<br>POWER=10                |

| I <sub>DD</sub> ADCE | ADC Active Current with<br>External Reference or<br>V <sub>DD</sub> Reference<br>(REFSEL=0x) including<br>I <sub>DD</sub> VEXT | 155 |     | μA  | INMODE=0x,<br>POWER=00                |

|                      |                                                                                                                                | 205 |     | μA  | INMODE=1x,<br>POWER=00                |

|                      |                                                                                                                                | 85  |     | μA  | INMODE=0x,<br>POWER=10                |

|                      |                                                                                                                                | 105 |     | μA  | INMODE=1x,<br>POWER=10                |

Notes:

Symbol

Parameter

Gain Error

- 1. Data in the Typical column is from characterization at 3.0 V and 25°C. These values are provided for design guidance only and are not tested in production.

- 2.  $T_S$  is applied twice if INMODE = 10 and RESOLUT = 1.

- 3.  $T_{SS}$  is applied twice if RESOLUT=1.

628

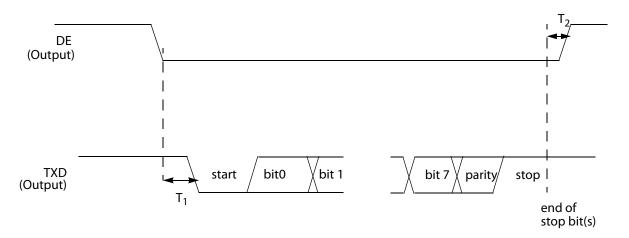

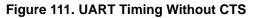

Figure 111 and Table 355 provide timing information for the UART pins for situations in which CTS is not used for flow control. DE asserts after the Transmit Data Register has been written. DE remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

| Table 35 | 5. UART | Timina | Without CTS |

|----------|---------|--------|-------------|

| 14010 00 | •••••   |        |             |

|                |                                                                        | Delay (ns)           |            |  |

|----------------|------------------------------------------------------------------------|----------------------|------------|--|

| Parameter      | Abbreviation                                                           | Min                  | Max        |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * SYSCLK<br>period | 1 bit time |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx Data Register is empty) | ± 5                  |            |  |