Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 24MHz                                                     |

| Connectivity               | DALI, DMX, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                              |

| Number of I/O              | 67                                                        |

| Program Memory Size        | 64KB (64K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 3.75K x 8                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                               |

| Data Converters            | A/D 12x12b; D/A 1x12b                                     |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 80-LQFP                                                   |

| Supplier Device Package    | 80-LQFP                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f6482at024xk |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore! XP<sup>®</sup> F6482 Series Product Specification

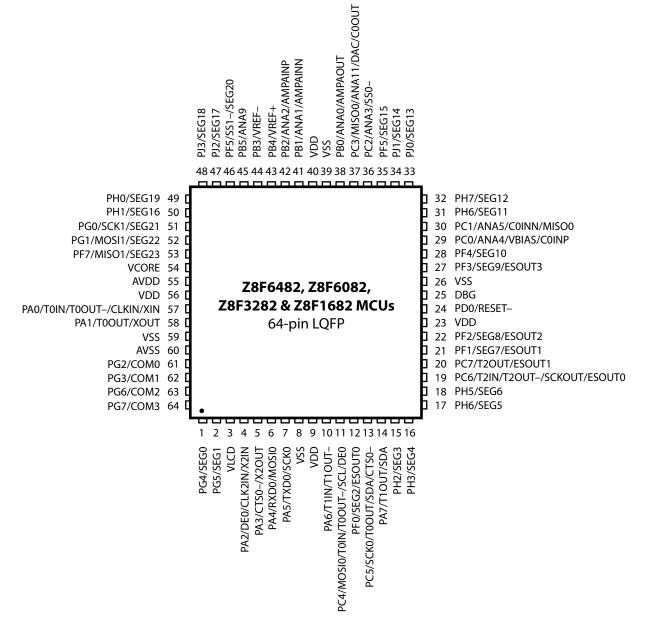

Figure 5. Z8F6482, Z8F6082, Z8F3282 & Z8F1682 MCUs, 64-Pin Low-Profile Quad Flat Package (LQFP)

16

47

# 5.3.3. Stop-Mode Recovery Using GPIO Port Pin Transition

Many of the GPIO Port pins can be configured as a Stop-Mode Recovery input source. Which GPIO can be configured as a Stop-Mode Recovery input source is described in the <u>General-Purpose Input/Output</u> chapter on page 55. On any GPIO pin enabled as a Stop-Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop-Mode Recovery. In the Reset Status Register, the STOP bit is set to 1.

If the GPIO is also configured as an interrupt source, an interrupt will occur once interrupts are reenabled.

**Caution:** In Stop Mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the Port pin until the end of the Stop-Mode Recovery delay. As a result, short pulses on the Port pin can initiate Stop-Mode Recovery without being written to the Port Input Data Register or without initiating an interrupt (if enabled for that pin).

# 5.3.4. Stop-Mode Recovery Using External RESET Pin

When the F6482 Series MCU is in Stop Mode and the external  $\overline{\text{RESET}}$  pin is driven Low, a System Reset occurs. Because of a glitch filter operating on the  $\overline{\text{RESET}}$  pin, the Low pulse must be greater than the minimum width specified, or it is ignored. For details, see the <u>Electrical Characteristics</u> chapter on page 598.

# 5.4. Low-Voltage Detection

In addition to the VBO Reset described earlier, it is also possible to generate an interrupt when the supply voltage drops below a user-selected value. To learn more about the available Low-Voltage Detection (LVD) threshold levels, see the <u>Flash Option Bits</u> chapter on page 540.

When the supply voltage drops below the LVD threshold, the LVD bit of the RSTSTAT Register is set to 1. This bit remains 1 until the low-voltage condition elapses. Reading or writing this bit does not clear it. The LVD circuit can also generate an interrupt when enabled; see the <u>Interrupt Controller</u> chapter on page 127. The LVD is not latched, so enabling the interrupt is the only way to guarantee detection of a transient low-voltage event.

The LVD circuit is either enabled or disabled by the Power Control Register bit 4. To learn more, see the <u>Power Control Register Definitions</u> section on page 52.

| Port                | Pin                     | Mnemonic             | Alternate Function Description             | Alternate Function<br>Set Subregisters |

|---------------------|-------------------------|----------------------|--------------------------------------------|----------------------------------------|

| Port A <sup>1</sup> | Port A <sup>1</sup> PA0 | T0IN/T0OUT           | Timer 0 Input/Timer 0 Output<br>Complement | AFS1[0]: 0                             |

|                     |                         | CLKIN                | External Clock Input                       | AFS1[0]: 1                             |

|                     | PA1                     | TOOUT                | Timer 0 Output                             | AFS1[1]: 0                             |

|                     |                         | Reserved             |                                            | AFS1[1]: 1                             |

|                     | PA2                     | DE0                  | UART 0 Driver Enable                       | AFS1[2]: 0                             |

|                     |                         | CLK2IN               | External Clock 2 Input                     | AFS1[2]: 1                             |

| PA3                 | CTS0                    | UART 0 Clear to Send | AFS1[3]: 0                                 |                                        |

|                     |                         | Reserved             |                                            | AFS1[3]: 1                             |

|                     | PA4                     | RXD0/                | UART 0 Receive Data                        | AFS1[4]: 0                             |

|                     |                         | MOSI0                | SPI 0 Master Out/Slave In                  | AFS1[4]: 1                             |

|                     | PA5                     | TXD0/                | UART 0 Transmit Data                       | AFS1[5]: 0                             |

|                     |                         | SCK0                 | SPI 0 Serial Clock                         | AFS1[5]: 1                             |

|                     | PA6                     | T1IN/T1OUT           | Timer 1 Input/Timer 1 Output<br>Complement | AFS1[6]: 0                             |

|                     |                         | SCL                  | I <sup>2</sup> C Serial Clock              | AFS1[6]: 1                             |

|                     | PA7                     | T1OUT                | Timer 1 Output                             | AFS1[7]: 0                             |

|                     |                         | SDA                  | I <sup>2</sup> C Serial Data               | AFS1[7]: 1                             |

## Table 19. Port Alternate Function Mapping (Z8Fxx81 64-Pin Parts)

Notes

Because there are at most two choices of alternate function for some pins of Ports A, B, D, E and F, the Alternate Function Set register AFS2 is not implemented. Additionally, alternate function selection, as described in the Port A–J Alternate Function Subregisters (see page 88), must also be enabled.

2. The alternate function selection for Port C, as described in the Port A–J Alternate Function Subregisters (see page 88), must also be enabled.

| PLL <sub>CLKIN</sub> |                            | PLL Core |                     | VCO   |                     |

|----------------------|----------------------------|----------|---------------------|-------|---------------------|

| (MHz)                | <b>PLL</b> <sub>RDIV</sub> | (MHz)    | PLL <sub>NDIV</sub> | (MHz) | PLL <sub>ODIV</sub> |

| 6                    | 1                          | 3        | 31                  | 96    | 1                   |

| 6.4                  | 2                          | 2.133333 | 44                  | 96    | 1                   |

| 7.2                  | 2                          | 2.4      | 39                  | 96    | 1                   |

| 8                    | 0                          | 8        | 11                  | 96    | 1                   |

| 9                    | 2                          | 3        | 31                  | 96    | 1                   |

| 9.6                  | 0                          | 9.6      | 9                   | 96    | 1                   |

| 10                   | 1                          | 5        | 47                  | 240   | 4                   |

| 12                   | 0                          | 12       | 7                   | 96    | 1                   |

| 12.8                 | 1                          | 6.4      | 14                  | 96    | 1                   |

| 14.4                 | 2                          | 4.8      | 19                  | 96    | 1                   |

| 16                   | 0                          | 16       | 5                   | 96    | 1                   |

| 18                   | 2                          | 6        | 15                  | 96    | 1                   |

| 19.2                 | 0                          | 19.2     | 4                   | 96    | 1                   |

| 20                   | 3                          | 5        | 47                  | 240   | 4                   |

| 24                   | 0                          | 24       | 3                   | 96    | 1                   |

Table 37. Common PLL Configurations for 48MHz PLLCLK (Continued)

To avoid spurious  $PLL_{CLK}$  behavior when modifying PLLh divider ratios, write CLKCTLA and CLKCTLB only when the PLL is disabled.

# 8.11. Clock System Register Definitions

The Clock System registers enable and disable the various oscillator circuits, enable and disable the failure detection and recovery circuitry, and select clock sources for System Clock, Peripheral Clock, and PLL clock.

# 8.11.1. Clock Control 0 Register

The Clock Control 0 (CLKCTL0) Register, shown in Table 38, selects System Clock and System Clock division, enables/disables System Clock failure detection, and provides clock system register locking status and control. SCKSEL is reset by both System Reset and Stop-Mode Recovery.

Before writing CLKCTL0, the clock control registers must be unlocked as described in the Clock System Control Register Unlocking/Locking section on page 103.

# **Caution:** When the timer is operating on PCLK or the WTO, the timer clock is asynchronous to System Clock. To ensure error-free operation, disable the timer before modifying its operation (including changing the timer clock source).

When the Timer uses PCLK or the WTO and the Timer is enabled, any read from TxH or TxL is not recommended, because results can be unpredictable. Disable the Timer first, then read it. If capture, capture/compare, Capture Restart or demodulation mode is selected, any read from TxPWM0H, TxPWM0L, TxPWM1H, TxPWM1L, or TxSTAT must be done after capture interrupt occurs, or results can be unpredictable. INPCAP in the Timer Control 0 Register has the same characteristics as these PWM registers. When the Timer clock selection is System Clock, registers can be written/read at any time.

# 10.1.2. Low-Power Modes

Timers can operate in both Halt Mode and Stop Mode. This section discusses each of these low-power modes.

## 10.1.2.1. Operation in Halt Mode

When the eZ8 CPU enters Halt Mode, the Timer will continue to operate if enabled. To minimize current in Halt Mode, the Timer can be disabled by clearing the TEN control bit. The Noise Filter, if enabled, will also continue to operate in Halt Mode and rejects any noise on the Timer Input 0.

# 10.1.2.2. Operation in Stop Mode

When the eZ8 CPU enters Stop Mode, the Timer continues to operate if enabled and PCLK or the WTO is selected as the timer clock. In Stop Mode, the timer interrupt (if enabled) automatically initiates a Stop-Mode Recovery and generates an interrupt request. In the Reset Status Register, the stop bit is set to 1. Also, timer interrupt request bit in Interrupt Request 0 Register is set. Following completion of the Stop-Mode Recovery, if interrupts are enabled, the CPU responds to the interrupt request by fetching the timer interrupt vector. The Noise Filter, if enabled, will also continue to operate in Stop Mode and rejects any noise on the Timer Input 0.

If System Clock is chosen as the timer clock, the Timer ceases to operate as System Clock is disabled in Stop Mode. In this case the registers are not reset and operation will resume after Stop-Mode Recovery occurs.

# 10.1.2.3. Power Reduction During Operation

Clearing TEN will inhibit clocking of the Timer. The CPU can still read/write registers when TEN is cleared.

| Bit                     | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6]<br>TPOL<br>(cont'd) | <ul> <li>PWM Dual Output Mode</li> <li>0: Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in Timer Control 0 Register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).</li> <li>1: Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon PWM count match and forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in Timer Control 0 Register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).</li> </ul> |

|                         | <b>Capture Restart Mode</b><br>0: Count is captured on the rising edge of the Timer Input 0 signal.<br>1: Count is captured on the falling edge of the Timer Input 0 signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                         | <ul> <li>Comparator Counter Mode</li> <li>When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer reload.</li> <li>Triggered One-Shot Mode and Dual Input Triggered One-Shot Mode</li> <li>OUTCTL = 0</li> <li>0: Timer counting is triggered on the rising edge of the Timer Input 0 signal.</li> <li>1: Timer counting is triggered on the falling edge of the Timer Input 0 signal.</li> <li>OUTCTL = 1</li> <li>0: Timer counting is triggered on the rising edge of the Timer Input 0 signal.</li> <li>1: Reserved.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         | <ul> <li>Demodulation Mode This functionality applies only if TPOLHI bit in Timer Control 2 Register is 0. If TPOLHI bit is 1 then timer counting is triggered on any edge of the Timer Input 0 signal and the current count is captured on both edges. The current count is captured into PWM0 registers on rising edges and PWM1 registers on falling edges of the Timer Input 0 signal. 0: Timer counting is triggered on the rising edge of the Timer Input 0 signal. The current count is captured into PWM0 High and Low byte registers on subsequent rising edges of the Timer Input 0 signal. </li> <li>1: Timer counting is triggered on the falling edge of the Timer Input 0 signal. The current count is captured into PWM1 High and Low byte registers on subsequent falling edges of the Timer Input 0 signal. </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# **11.3.** Capture/Compare Channel Operation

The Multi-Channel timer supports four Capture/Compare channels: CHA, CHB, CHC, and CHD. Each channel has the following features:

- A 16-bit Capture/Compare Register (MCTCHyH and MCTCHyL registers) used to capture input event times or to generate time intervals. Any user software update of the Capture/Compare Register value when the timer is running takes effect only at the end of the counting cycle, not immediately. The end of the counting cycle is when the counter transitions from the reload value to 0 (Count Modulo Mode) or from 1 to 0 (Count Up/Down Mode).

- A dedicated bidirectional GPIO pin (T4CHA, B, C, or D) and Event System input/ output that can be configured for the input capture function or to generate an output compare match or one-shot pulse.

Each channel is configured to operate in either One-Shot Compare, Continuous Compare, PWM Output, or Capture Mode.

# 11.3.1. One-Shot Compare Operation

In One-Shot Compare operation, a channel interrupt is generated when the channel compare value matches the timer count. The channel event flag, CHyEF, is set in the Channel Status 1 Register (MCTCHS1) to identify the responsible channel. Then the channel is automatically disabled. The timer continues counting according to the programmed mode. The channel output (TOutA, B, C, or D) changes state for one system clock cycle (from Low to High then back to Low or High to Low then back to High as determined by the CHPOL bit) on match.

# 11.3.2. Continuous Compare Operation

In Continuous Compare operation, a channel interrupt is generated when the channel compare value matches the timer count. The channel event flag (CHyEF) is set in the Channel Status1 Register (MCTCHS1) and the channel remains enabled. The timer continues counting according to the programmed mode. The channel output (TOutA, B, C, or D) changes state (from Low to High then back to Low, or High to Low then back to High as determined by the CHPOL bit) on match. For proper operation, configure the CHPOL bit prior to setting the CHEN bit.

# 11.3.3. PWM Output Operation

In PWM Output operation, the timer generates a PWM output signal on the channel output (TOutA, B, C, or D). The channel output toggles whenever the timer count matches the channel compare value (defined in the MCTCHyH and MCTCHyL) registers. In addition, a channel interrupt is generated and the channel event flag is set in the status register. The timer continues counting according to its programmed mode.

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>TDRE | <ul> <li>Transmitter Data Register Empty</li> <li>This bit indicates that the Transmit Data Register is empty and ready for additional data.</li> <li>Writing to the Transmit Data Register resets this bit.</li> <li>0: Do not write to the Transmit Data Register.</li> <li>1: The Transmit Data Register is ready to receive an additional byte for transmission.</li> </ul> |

| [1]<br>TXE  | <b>Transmitter Empty</b><br>This bit indicates that the Transmit Shift Register is empty and character transmission is finished.<br>0: Data is currently transmitting.<br>1: Transmission is complete.                                                                                                                                                                          |

| [0]<br>CTS  | Clear to Send Signal<br>When this bit is read it returns the level of the CTS signal. If LBEN=1, the CTS input signal is<br>replaced by the internal Receive Data Available signal to provide flow control in a loopback<br>mode. CTS only affects transmission if the CTSE bit=1.                                                                                              |

# Table 124. UART-LDD 0–1 Status 0 Registers, LIN Mode (UxSTAT0)

| Bit     | 7                              | 6   | 5  | 4  | 3    | 2    | 1   | 0   |

|---------|--------------------------------|-----|----|----|------|------|-----|-----|

| Field   | RDA                            | PLE | OE | FE | BRKD | TDRE | TXE | ATB |

| Reset   | 0                              | 0   | 0  | 0  | 0    | 1    | 1   | 0   |

| R/W     | R                              | R   | R  | R  | R    | R    | R   | R   |

| Address | U0STAT0 @ F41h, U1STAT0 @ F49h |     |    |    |      |      |     |     |

|         | and $y = 0.1$                  |     |    |    |      |      |     |     |

Note: R = read; x = 0, 1.

## Bit Description

# [7] Receive Data Available

RDA This bit indicates that the Receive Data Register has received data. Reading the Receive Data Register clears this bit.

0: The Receive Data Register is empty.

1: There is a byte in the Receive Data Register.

# [6] Physical Layer Error

PLE This bit indicates that transmit and receive data do not match when a LIN slave or master is transmitting. This could be by a fault in the physical layer or multiple devices driving the bus simultaneously. Reading the Status 0 Register or the Receive Data Register clears this bit.

PRELIMINARY

0: Transmit and Receive data match.

1: Transmit and Receive data do not match.

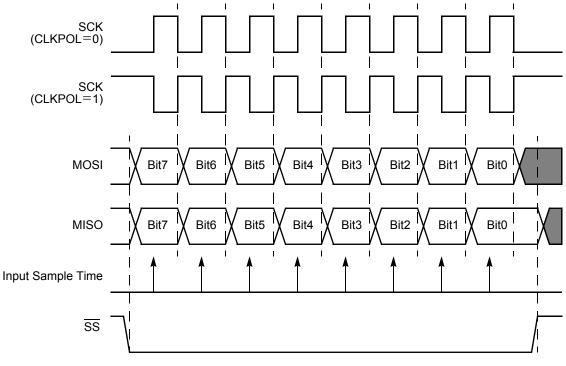

Figure 38. ESPI Timing when PHASE=0

# 15.3.2.2. Transfer Format When Phase Equals One

Figure 39 shows a timing diagram for an SPI-type transfer in which PHASE is 1. For SPI transfers, the clock only toggles during a character transfer. Two waveforms are depicted for SCK: one for CLKPOL=0 and another for CLKPOL=1.

303

Table 150 defines the valid ESPI states.

| ESPISTATE |                                           |

|-----------|-------------------------------------------|

| Value     | Description                               |

| 00_0000   | Idle.                                     |

| 00_0001   | Slave Wait for SCK.                       |

| 00_0010   | I <sup>2</sup> S Slave Mode start delay.  |

| 00_0011   | I <sup>2</sup> S Slave Mode start delay.  |

| 01_0000   | SPI Master Mode start delay.              |

| 11_0001   | I <sup>2</sup> S Master Mode start delay. |

| 11_0010   | I <sup>2</sup> S Master Mode start delay. |

| 10_1110   | Bit 7 Receive.                            |

| 10_1111   | Bit 7 Transmit.                           |

| 10_1100   | Bit 6 Receive.                            |

| 10_1101   | Bit 6 Transmit.                           |

| 10_1010   | Bit 5 Receive.                            |

| 10_1011   | Bit 5 Transmit.                           |

| 10_1000   | Bit 4 Receive.                            |

| 10_1001   | Bit 4 Transmit.                           |

| 10_0110   | Bit 3 Receive.                            |

| 10_0111   | Bit 3 Transmit.                           |

| 10_0100   | Bit 2 Receive.                            |

| 10_0101   | Bit 2 Transmit.                           |

| 10_0010   | Bit 1 Receive.                            |

| 10_0011   | Bit 1 Transmit.                           |

| 10_0000   | Bit 0 Receive.                            |

| 10_0001   | Bit 0 Transmit.                           |

#### Table 150. ESPISTATE Values

# 15.4.7. ESPI 0-1 Baud Rate High and Low Byte Registers

The ESPI 0-1 Baud Rate High and Low Byte registers, shown in Tables 151 and <u>152</u>, combine to form a 16-bit reload value, BRG[15:0], for the ESPI Baud Rate Generator. The ESPI baud rate is calculated using the following equation:

SPI Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{2 \times \text{BRG}[15:0]}$

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>ARBLST | Arbitration Lost<br>This bit is set when the I <sup>2</sup> C controller is enabled in MASTER Mode and loses arbitration (i.e.,<br>outputs a 1 on SDA and receives a 0 on SDA). The ARBLST bit clears when the I2CISTAT<br>Register is read.                                                                                                                                                                                                                                                                                                  |

| [1]<br>SPRS   | <b>Stop/Restart Condition Interrupt</b><br>This bit is set when the I <sup>2</sup> C controller is enabled in SLAVE Mode, and detects a stop or restart condition during a transaction directed to this slave. This bit clears when the I2CISTAT Register is read. Read the RSTR bit of the I2CSTATE Register to determine whether the interrupt was caused by a stop or restart condition.                                                                                                                                                   |

| [0]<br>NCKI   | <b>NAK Interrupt</b><br>In MASTER Mode, this bit is set when a Not Acknowledge condition is received or sent, and<br>neither the start nor the stop bit is active. In MASTER Mode, this bit can only be cleared by<br>setting the start or stop bits. In SLAVE Mode, this bit is set when a Not Acknowledge condition<br>is received (i.e., a master reading data from a slave), indicating that the master is finished<br>reading. A stop or restart condition follows. In SLAVE Mode this bit clears when the I2CISTAT<br>Register is read. |

# 16.3.3. I<sup>2</sup>C Control Register

The I<sup>2</sup>C Control Register, shown in Table 156, enables and configures I<sup>2</sup>C operation.

**Note:** The R/W1 bit can be set (written to 1) when IEN=1, but cannot be cleared (written to 0).

| Bit     | 7   | 6     | 5    | 4     | 3   | 2    | 1     | 0      |

|---------|-----|-------|------|-------|-----|------|-------|--------|

| Field   | IEN | START | STOP | BIRQS | TXI | NAK  | FLUSH | FILTEN |

| Reset   | 0   | 0     | 0    | 0     | 0   | 0    | 0     | 0      |

| R/W     | R/W | R/W1  | R/W1 | R/W   | R/W | R/W1 | W     | R/W    |

| Address |     |       |      | F5    | 2h  |      |       |        |

# Table 156. I<sup>2</sup>C Control Register (I2CCTL)

# Bit Description

[7] I<sup>2</sup>C Enable

IEN This bit enables the I<sup>2</sup>C controller.

# 17.3.7. USB OUT Endpoint 1–3 Start Address Subregisters

The USB OUT 1–3 Start Address subregisters, shown in Table 176, in conjunction with the USBISTADDR Register shown in Table 177, define the size of each OUT endpoint.

## Table 176. USB OUT Endpoint 1–3 Start Address Subregisters (USBOxADDR)

| Bit           | 7                                                                                                             | 6           | 5     | 4     | 3     | 2     | 1     | 0     |

|---------------|---------------------------------------------------------------------------------------------------------------|-------------|-------|-------|-------|-------|-------|-------|

| Field         |                                                                                                               |             |       | OUTA  | DDR   |       |       |       |

| Reset         | see below description                                                                                         |             |       |       |       |       |       |       |

| R/W           | R0/W*                                                                                                         | R0/W*       | R0/W* | R0/W* | R0/W* | R0/W* | R0/W* | R0/W* |

| Address       | If USBSA = 01h, 02h, 03h in the USB Subaddress Register,<br>it is accessible through the USB Subdata Register |             |       |       |       |       |       |       |

| Note: *R0/W = | = Write but re                                                                                                | ads back as | 0.    |       |       |       |       |       |

## [7:0] OUT Endpoint Start Address

Description

Bit

OUTADDR 00–FF: The start address of OUT endpoint memory buffers except OUT endpoint 0. The first starting address (OUT endpoint 0) is fixed at buffer memory address 000h. {0, OUTADDR[7:0], 0} maps to buffer memory address [9:0]; therefore the minimum increment of OUTADDR is 2 bytes of buffer memory. The size in bytes of an OUT endpoint is determined by subtracting consecutive starting address values then multiplying by 2. OUTADDR should be set to 00h for any OUT endpoint that doesn't exist (or is not used). See USB Endpoint Buffer Memory on page 341 for details.

## **Reset State:**

USBO1ADDR: 20h USBO2ADDR: 40h USBO3ADDR: 60h

# 17.3.11. USB Interrupt Identification Subregister

The USB Interrupt Identification Subregister, shown in Table 180, contains the USB Module interrupt identifier. When the USB Module generates a USB interrupt request, the USBIID Subregister is updated to indicate the source of the interrupt. If more than one USB interrupt request is asserted, the contents of IID reflect the highest priority interrupt based on the order listed in the IID description. To learn more, see the <u>Interrupts</u> section on page 355.

#### Table 180. USB Interrupt Identification Subregister (USBIID)

| Bit     | 7                                                                                             | 6 | 5 | 4   | 3 | 2 | 1    | 0     |

|---------|-----------------------------------------------------------------------------------------------|---|---|-----|---|---|------|-------|

| Field   | Reserved                                                                                      |   |   | IID |   |   | Rese | erved |

| Reset   | 0                                                                                             | 0 | 0 | 0   | 0 | 0 | 0    | 0     |

| R/W     | R                                                                                             | R | R | R   | R | R | R    | R     |

| Address | If USBSA = 28h in the USB Subaddress Register,<br>accessible through the USB Subdata Register |   |   |     |   |   |      |       |

#### Bit Description

## [7] Reserved

| This bit is reserved and must be programmed to 0. |

|---------------------------------------------------|

|                                                   |

| [6:2] | Interrupt Identification (Source) |

|-------|-----------------------------------|

|       |                                   |

- IID 00000: SUDAVIRQ in the USBIRQ Register. Highest priority. 00001: SOFIRQ in the USBIRQ Register.

- 00010: SUTOKIRQ in the USBIRQ Register.

- 00011: SUSPIRQ in the USBIRQ Register.

- 00100: URESIRQ in the USBIRQ Register.

- 00101: Reserved.

- 00110: IN0IRQ in the USBINIRQ Register.

- 00111: OUT0IRQ in the USBOUTIRQ Register.

- 01000: IN1IRQ in the USBINIRQ Register.

- 01001: OUT1IRQ in the USBOUTIRQ Register.

- 01010: IN2IRQ in the USBINIRQ Register.

- 01011: OUT2IRQ in the USBOUTIRQ Register.

- 01100: IN3IRQ in the USBINIRQ Register.

- 01101: OUT3IRQ in the USBOUTIRQ Register. Lowest priority.

- Others: Reserved.

# [1:0] **Reserved** These bits are reserved and must be programmed to 00.

| Bit            | Description (Continued)                                                                                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| [1]<br>CHAIN32 | Chain DMA3and DMA2<br>0: DMA3 and DMA2 are independent of each other.                                                       |

|                | <ol> <li>DMA3 and DMA2 are chained together, as described in the <u>Chain Operation</u> section on<br/>page 393.</li> </ol> |

| [0]            | Chain DMA1 and DMA0                                                                                                         |

| CHAIN10        | 0: DMA1 and DMA0 are independent of each other.                                                                             |

|                | <ol> <li>DMA1 and DMA0 are chained together, as described in the <u>Chain Operation</u> section on<br/>page 393.</li> </ol> |

# 18.3.4. DMA Source Address Subregisters

The DMAxSRCH and DMAxSRCL subregisters, shown in Tables 207 and 208, combine to form the 12-bit source address for the DMA transaction. Upon each byte transfer, the source address is updated based on the SRCCTL configuration in the DMAx Control 0 Subregister. In addition, DMAxSRCH contains transfer in list (TXLIST) control.

| Table 207. DMA Source Address High S | Subregister (DMAxSRCH) |

|--------------------------------------|------------------------|

|--------------------------------------|------------------------|

| Bit     | 7                                                                                | 6 | 5        | 4 | 3    | 2   | 1   | 0   |  |

|---------|----------------------------------------------------------------------------------|---|----------|---|------|-----|-----|-----|--|

| Field   | TXLIST                                                                           |   | Reserved |   | SRCH |     |     |     |  |

| Reset   | 0                                                                                | 0 | 0        | 0 | 0    | 0   | 0   | 0   |  |

| R/W     | R                                                                                | R | R        | R | R/W  | R/W | R/W | R/W |  |

| Address | If DMASA = 0h in the DMAxSA Register, accessible through the DMA 0–3 Subregister |   |          |   |      |     |     |     |  |

| Bit           | Description                                                                                                                                                       |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>TXLIST | <b>Transfer In List</b><br>TXLIST has an effect only during linked list operation, see the <u>Linked List Control Options</u><br>section on page 395 for details. |

| [6:4]         | Reserved<br>These bits are reserved and must be programmed to 000.                                                                                                |

| [3:0]<br>SRCH | Source Address High<br>0–F: Upper 4 bits of the DMA source address.                                                                                               |

## 28.3.1.2. Trim Bit Addresses 0001h and 0002h

The Trim Option Bits registers at addresses 0001h and 00002h, shown in Tables 290 and 291, govern control of the temperature sensor trim bits.

## Table 290. Trim Option Bits at Address 0001h (TTEMP0)

| Bit                                                   | 7    | 6                             | 5       | 4   | 3   | 2   | 1   | 0   |  |

|-------------------------------------------------------|------|-------------------------------|---------|-----|-----|-----|-----|-----|--|

| Field                                                 | Rese | erved                         | TS_GAIN |     |     |     |     |     |  |

| Reset                                                 | Х    | Х                             | Х       | Х   | Х   | Х   | Х   | Х   |  |

| R/W                                                   | R/W  | R/W                           | R/W     | R/W | R/W | R/W | R/W | R/W |  |

| Address                                               |      | Information Page Memory 0021h |         |     |     |     |     |     |  |

| Note: X = undefined; R/W = read/write; R = read-only. |      |                               |         |     |     |     |     |     |  |

|                                                       |      |                               |         |     |     |     |     |     |  |

| Bit     | Description                                             |

|---------|---------------------------------------------------------|

| [7:6]   | Reserved                                                |

|         | These bits are reserved.                                |

| [5:0]   | Temperature Gain Trim Bits                              |

| TS_GAIN | Contains gain trimming bits for the Temperature Sensor. |

# Table 291. Trim Option Bits at Address 0002h (TTEMP1)

| Bit                                                   | 7                             | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------------------------------------------------|-------------------------------|-----------|-----|-----|-----|-----|-----|-----|--|

| Field                                                 |                               | TS_OFFSET |     |     |     |     |     |     |  |

| Reset                                                 | Х                             | Х         | Х   | Х   | Х   | Х   | Х   | Х   |  |

| R/W                                                   | R/W                           | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Address                                               | Information Page Memory 0022h |           |     |     |     |     |     |     |  |

| Note: X = undefined; R/W = read/write; R = read-only. |                               |           |     |     |     |     |     |     |  |

| Bit       | Description                                               |

|-----------|-----------------------------------------------------------|

| [7:0]     | Temperature Sensor Offset Trim Bits                       |

| TS_OFFSET | Contains offset trimming bits for the Temperature Sensor. |

|          | 1.17        |                 |         |                                          |

|----------|-------------|-----------------|---------|------------------------------------------|

| LVD_TRIM | <br>Minimum | D Threshold     |         | _<br>Description                         |

| 00000    | winnmum     | Typical<br>3.20 | Maximum | Description Maximum LVD threshold        |

| 00001    |             | 3.15            |         |                                          |

| 00001    |             | 3.10            |         |                                          |

|          |             |                 |         |                                          |

| 00011    |             | 3.05            |         |                                          |

| 00100    |             | 3.00            |         |                                          |

| 00101    |             | 2.95            |         |                                          |

| 00110    |             | 2.90            |         |                                          |

| 00111    |             | 2.85            |         |                                          |

| 01000    |             | 2.80            |         |                                          |

| 01001    |             | 2.75            |         |                                          |

| 01010    |             | 2.70            |         |                                          |

| 01011    |             | 2.65            |         |                                          |

| 01100    |             | 2.60            |         |                                          |

| 01101    |             | 2.55            |         |                                          |

| 01110    |             | 2.50            |         |                                          |

| 01111    |             | 2.45            |         |                                          |

| 10000    |             | 2.40            |         |                                          |

| 10001    |             | 2.35            |         |                                          |

| 10010    |             | 2.30            |         |                                          |

| 10011    |             | 2.25            |         |                                          |

| 10100    |             | 2.20            |         |                                          |

| 10101    |             | 2.15            |         |                                          |

| 10110    |             | 2.10            |         |                                          |

| 10111    |             | 2.05            |         |                                          |

| 11000    |             | 2.00            |         |                                          |

| 11001    |             | 1.95            |         |                                          |

| 11010    |             | 1.90            |         |                                          |

| 11011    |             | 1.85            |         |                                          |

| 11100    |             | 1.80            |         |                                          |

| 11101    |             | 1.75            |         |                                          |

| 11110    |             | 1.70            |         |                                          |

| 11111    |             | 1.65            |         | Minimum LVD threshold; default on Reset. |

|          |             | 1.00            |         |                                          |

## Table 294. LVD\_Trim Values

|                       |                                             |                            | :1.8V to<br>∔0°C to |                            |       |                                                           |  |

|-----------------------|---------------------------------------------|----------------------------|---------------------|----------------------------|-------|-----------------------------------------------------------|--|

| Symbol                | Parameter                                   | Min Typ*                   |                     | Max                        | Units | Conditions                                                |  |

| R <sub>OUT</sub>      | Output Resistance                           |                            | 25                  | 75                         | Ω     | $V_{SS} \le V_{DACOUT} \le V_{DD}$                        |  |

|                       |                                             |                            |                     | 3                          | Ω     | $V_{SS}$ +0.3V $\leq$ $V_{DACOUT} \leq$<br>$V_{DD}$ -0.3V |  |

| V <sub>DAC</sub>      | DAC Output Voltage<br>Range                 | AV <sub>SS</sub> +0<br>.1V |                     | AV <sub>DD</sub> –0<br>.1V | V     |                                                           |  |

| T <sub>SET_FS</sub>   | Settling Time, full scale                   |                            | 15                  |                            | μs    | POWER=00                                                  |  |

|                       |                                             |                            | 40                  |                            | μs    | POWER=01                                                  |  |

|                       |                                             |                            | 100                 |                            | μs    | POWER=10                                                  |  |

| T <sub>SET_CC</sub>   | Settling Time, code to                      |                            | 1                   |                            | μs    | POWER=00                                                  |  |

|                       | code                                        |                            | 2                   |                            | μs    | POWER=01                                                  |  |

|                       | (adjacent codes)                            |                            | 5                   |                            | μs    | POWER=10                                                  |  |

| SR                    | Slew Rate                                   |                            | 5                   |                            | V/µs  | POWER=00                                                  |  |

|                       |                                             |                            | 1.4                 |                            | V/µs  | POWER=01                                                  |  |

|                       |                                             |                            | 0.35                |                            | V/µs  | POWER=10                                                  |  |

| T <sub>UP</sub>       | Update rate                                 |                            |                     | 1                          | μs    |                                                           |  |

| T <sub>WAKE_DR</sub>  | Time for Wake up,<br>Internal DAC Reference |                            | 0.5                 | 1.1                        | ms    | C <sub>VREFP</sub> =1µF                                   |  |

| T <sub>WAKE_DAC</sub> | Time for Wake up, DAC                       |                            | 18                  |                            | μs    | POWER=00                                                  |  |

|                       |                                             |                            | 25                  |                            | μs    | POWER=01                                                  |  |

|                       |                                             |                            | 35                  |                            | μs    | POWER=10                                                  |  |

## Table 338. Digital-to-Analog Converter Electrical Characteristics and Timing (Continued)

Note: \*Data in the Typical column is from characterization at 3.0V and 25°C. These values are provided for design guidance only and are not tested in production.

|                    |                                                             | T <sub>A</sub> =- | -40°C to +  | 85°C  |            |                                             |  |

|--------------------|-------------------------------------------------------------|-------------------|-------------|-------|------------|---------------------------------------------|--|

|                    | -                                                           | V <sub>DD</sub>   | =1.8V to 3  | 3.6V  | -          |                                             |  |

| Symbol             | Parameter                                                   | Min Typ* Max      |             | Units | Conditions |                                             |  |

| V <sub>CPT</sub>   | LCD Charge Pump Output<br>Voltage when tripler is           |                   | 2.5         |       | V          | V <sub>DD</sub> ≥ 1.8V,<br>CONTRAST=000     |  |

|                    | selected (CPEN=1,<br>CPTSEL=0)                              |                   | 2.64        |       | V          | V <sub>DD</sub> ≥ 1.8V,<br>CONTRAST=001     |  |

|                    | -                                                           |                   | 2.78        |       | V          | V <sub>DD</sub> ≥ 1.8V,<br>CONTRAST=010     |  |

|                    | -                                                           |                   | 2.92        |       | V          | V <sub>DD</sub> ≥ 1.8V,<br>CONTRAST=011     |  |

|                    | -                                                           |                   | 3.06        |       | V          | V <sub>DD</sub> ≥ 1.8V,<br>CONTRAST=100     |  |

|                    |                                                             |                   | 3.20        |       | V          | V <sub>DD</sub> ≥ 1.8V,<br>CONTRAST=101     |  |

|                    | -                                                           |                   | 3.35        |       | V          | V <sub>DD</sub> ≥ 1.8V,<br>CONTRAST=110     |  |

|                    |                                                             |                   | 3.5         |       | V          | V <sub>DD</sub> ≥ 2.0V,<br>CONTRAST=111     |  |

| R <sub>BIAS</sub>  | Resistance of Bias<br>Network (1/3 LCD                      |                   | 4.5, 4.5    |       | MΩ         | BIASGSEL=X, not during transition drive     |  |

|                    | waveform biasing, 1/2 LCD <sup>−</sup><br>waveform biasing) |                   | 340,<br>240 |       | kΩ         | BIASGSEL=0, during medium transition drive  |  |

|                    | -                                                           |                   | 100, 60     |       | kΩ         | BIASGSEL=1, during<br>high transition drive |  |

| C <sub>VLCD</sub>  | Capacitance on VLCD pin                                     |                   | 1           |       | μF         |                                             |  |

| C <sub>PANEL</sub> | VLCD Panel Capacitance                                      |                   |             | 8000  | pF         | 40 Hz frame frequency                       |  |

| TC <sub>VLCD</sub> | Time to Charge VLCD with<br>Internal Charge Pump            | 0.1               |             | 3     | µF* s      | BIASGSEL = 0                                |  |

## Table 344. LCD Electrical Characteristics (Continued)

Notes:

1. Data in the Typical column is from characterization at 3.0V and 25°C. These values are provided for design guidance only and are not tested in production.

Based on PCLK= 32.768kHz (CKSEL=0), 32 Hz frame rate (PRESCALE=011, FDIV=0111), and LCD mode of 1/ 4 duty, 1/3 bias, type A waveform (LCDMODE=1011). Either VLCD=3V (VLCDDIR=0) or V<sub>DD</sub>=3V (VLCDDIR=0, CPEN=0). No LCD panel load.

3. VLCD=3.06V (CONTRAST=100), V<sub>DD</sub>=3.0V.

| Symbol            | Parameter            | V <sub>DD</sub> =1.8V to 3.6V<br>T <sub>A</sub> =–40°C to +85°C |        |     |       |            |

|-------------------|----------------------|-----------------------------------------------------------------|--------|-----|-------|------------|

|                   |                      | Min                                                             | Тур*   | Max | Units | Conditions |

| F <sub>IPO</sub>  | Output Frequency     | -2%                                                             | 32.768 | +2% | kHz   |            |

|                   | Duty Cycle of Output | 45                                                              |        | 55  | %     |            |

| T <sub>WAKE</sub> | Time for Wake up     |                                                                 | 25     |     | μs    |            |

## Table 346. IPO Electrical Characteristics (Continued)

# 33.4.17. High Frequency Crystal Oscillator

Table 347 presents electrical and timing data for the F6482 Series' High Frequency Crystal Oscillator function.

| Symbol            | Parameter                      | $\frac{T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C}{V_{DD} = 1.8V \text{ to } 3.6V}$ |                               |     | _    |                          |

|-------------------|--------------------------------|----------------------------------------------------------------------------------------|-------------------------------|-----|------|--------------------------|

|                   |                                |                                                                                        |                               |     |      |                          |

|                   |                                | I <sub>DD</sub> HFXO                                                                   | HFXO Active Supply<br>Current |     | 100  |                          |

|                   | 150                            |                                                                                        |                               |     | μA   | HFXOBAND=01 <sup>2</sup> |

|                   | 200                            |                                                                                        |                               |     | μA   | HFXOBAND=10 <sup>2</sup> |

| F <sub>XTAL</sub> | HFXO Frequency                 | 1                                                                                      |                               | 8   | MHz  | HFXOBAND=00              |

|                   |                                | > 8                                                                                    |                               | 16  | MHz  | HFXOBAND=01              |

|                   |                                | >16                                                                                    |                               | 24  | MHz  | HFXOBAND=10              |

| gm                | Oscillator<br>Transconductance | 0.4                                                                                    |                               |     | mA/V | HFXOBAND=00 <sup>2</sup> |

|                   |                                | 1.0                                                                                    |                               |     | mA/V | HFXOBAND=01 <sup>2</sup> |

|                   |                                | 2.5                                                                                    |                               |     | mA/V | HFXOBAND=10 <sup>2</sup> |

| T <sub>WAKE</sub> | Time for Wake up               |                                                                                        | 2                             | 4   | ms   | HFXOBAND=00 <sup>2</sup> |

|                   |                                |                                                                                        | 1.2                           | 2.4 | ms   | HFXOBAND=01 <sup>2</sup> |

|                   |                                |                                                                                        | 1                             | 2   | ms   | HFXOBAND=10 <sup>2</sup> |

|                   | SCKOUT Duty Cycle              | 40                                                                                     | 50                            | 60  | %    |                          |

## Table 347. High Frequency Crystal Oscillator (HFXO) Characteristics

Notes:

1. Data in the Typical column is from characterization at 3.0V and 25°C. These values are provided for design guidance only and are not tested in production.

2. C<sub>LOAD</sub>=12.5 pF.

# 33.4.20. Digitally Controlled Oscillator and Frequency-Locked Loop

Table 350 presents electrical and timing data for the F6482 Series' Digitally Controlled Oscillator (DCO) and Frequency-Locked Loop functions.

| Symbol                | Parameter                                               | V <sub>DD</sub> =1.8V to 3.6V<br>T <sub>A</sub> =–40°C to +85°C |        |     |       |                                          |

|-----------------------|---------------------------------------------------------|-----------------------------------------------------------------|--------|-----|-------|------------------------------------------|

|                       |                                                         | Min                                                             | Тур*   | Max | Units | Conditions                               |

| I <sub>DD</sub> DCO   | DCO Active Supply Current                               |                                                                 | 25     |     | μA    | F <sub>DCO</sub> =1MHz                   |

|                       | -                                                       |                                                                 | 90     |     | μA    | F <sub>DCO</sub> =10MHz                  |

|                       | -                                                       |                                                                 | 125    |     | μA    | F <sub>DCO</sub> =20MHz                  |

|                       | -                                                       |                                                                 | 150    |     | μA    | F <sub>DCO</sub> =24MHz                  |

| I <sub>DD</sub> FLL   | FLL Active Supply Current                               |                                                                 | 20     |     | μA    |                                          |

| F <sub>DCO</sub>      | DCO Frequency                                           | 1                                                               |        | 24  | MHz   |                                          |

| F <sub>FLLCLKIN</sub> | FLL Input Clock Frequency                               |                                                                 | 32.768 |     | kHz   |                                          |

|                       | Duty Cycle of DCO Output                                | 45                                                              |        | 55  | %     |                                          |

|                       | DCO Resolution                                          |                                                                 | 150    |     | ps    |                                          |

|                       | DCO control word<br>resolution, {DCOCTLCH,<br>DCODTLCL} |                                                                 | 600    |     | ps    |                                          |

|                       | DCO Temperature<br>Coefficient (FLL off)                |                                                                 | +0.2   |     | %/C   |                                          |

|                       | DCO Voltage Coefficient<br>(FLL off)                    |                                                                 | +0.01  |     | %/V   | For changes in $V_{DD}$                  |

| T <sub>LOCK</sub>     | FLL Lock Time<br>(FLLLOCK=1)                            |                                                                 | 200    |     | μs    | PCLK=32.768kHz;<br>fast locking selected |

| T <sub>FLADONE</sub>  | FLL Fast Lock Algorithm<br>Time (FLADONE=1)             |                                                                 | 2.5    |     | ms    | PCLK=32.768kHz;<br>fast locking selected |

## Table 350. DCO and FLL Electrical Characteristics