Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | XCore                                                         |

| Core Size                  | 32-Bit 12-Core                                                |

| Speed                      | 2000MIPS                                                      |

| Connectivity               | -                                                             |

| Peripherals                | -                                                             |

| Number of I/O              | 88                                                            |

| Program Memory Size        | -                                                             |

| Program Memory Type        | ROMIess                                                       |

| EEPROM Size                | -                                                             |

| RAM Size                   | 512K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                  |

| Data Converters            | -                                                             |

| Oscillator Type            | External                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 128-TQFP Exposed Pad                                          |

| Supplier Device Package    | 128-TQFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xl212-512-tq128-i20 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1   | xCORE Multicore Microcontrollers     |

|-----|--------------------------------------|

| 2   | XL212-512-TQ128 Features             |

| 3   | Pin Configuration                    |

| 4   | Signal Description                   |

| 5   | Example Application Diagram          |

| 6   | Product Overview                     |

| 7   | PLL                                  |

| 8   | Boot Procedure                       |

| 9   | Memory                               |

| 10  | JTAG                                 |

| 11  | Board Integration                    |

| 12  | DC and Switching Characteristics     |

| 13  | Package Information                  |

| 14  | Ordering Information                 |

| App | endices                              |

| Α   | Configuration of the XL212-512-TQ128 |

| В   | Processor Status Configuration       |

| С   | Tile Configuration                   |

| D   | Node Configuration                   |

| E   | JTAG, xSCOPE and Debugging           |

| F   | Schematics Design Check List         |

| G   | PCB Layout Design Check List         |

| Н   | Associated Design Documentation      |

| 1   | Related Documentation                |

| J   | Revision History                     |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

# 1 xCORE Multicore Microcontrollers

The xCORE-200 Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

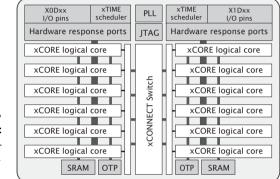

Figure 1: XL212-512-TQ128 block diagram

Key features of the XL212-512-TQ128 include:

- ► **Tiles**: Devices consist of one or more xCORE tiles. Each tile contains between five and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- Logical cores Each logical core can execute tasks such as computational code, DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 6.1

- xTIME scheduler The xTIME scheduler performs functions similar to an RTOS, in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores on events generated by hardware resources such as the I/O pins, communication channels and timers. Once triggered, a core runs independently and concurrently to other cores, until it pauses to wait for more events. Section 6.2

- Channels and channel ends Tasks running on logical cores communicate using channels formed between two channel ends. Data can be passed synchronously or asynchronously between the channel ends assigned to the communicating tasks. Section 6.5

- xCONNECT Switch and Links Between tiles, channel communications are implemented over a high performance network of xCONNECT Links and routed through a hardware xCONNECT Switch. Section 6.6

-XM()S

# 4 Signal Description

This section lists the signals and I/O pins available on the XL212-512-TQ128. The device provides a combination of 1 bit, 4bit, 8bit and 16bit ports, as well as wider ports that are fully or partially (gray) bonded out. All pins of a port provide either output or input, but signals in different directions cannot be mapped onto the same port.

Pins may have one or more of the following properties:

- PD/PU: The IO pin has a weak pull-down or pull-up resistor. The resistor is enabled during and after reset. Enabling a link or port that uses the pin disables the resistor. Thereafter, the resistor can be enabled or disabled under software control. The resistor is designed to ensure defined logic input state for unconnected pins. It should not be used to pull external circuitry. Note that the resistors are highly non-linear and only a maximum pull current is specified in Section 12.2.

- ST: The IO pin has a Schmitt Trigger on its input.

- IOL/IOT/IOR: The IO pin is powered from VDDIOL, VDDIOT, and VDDIOR respectively

|          | Power pins (8)            |      |            |

|----------|---------------------------|------|------------|

| Signal   | Function                  | Туре | Properties |

| GND      | Digital ground            | GND  |            |

| OTP_VCC  | OTP power supply          | PWR  |            |

| PLL_AGND | Analog ground for PLL     | PWR  |            |

| PLL_AVDD | Analog PLL power          | PWR  |            |

| VDD      | Digital tile power        | PWR  |            |

| VDDIOL   | Digital I/O power (left)  | PWR  |            |

| VDDIOR   | Digital I/O power (right) | PWR  |            |

| VDDIOT   | Digital I/O power (top)   | PWR  |            |

|        | JTAG pins (6)      |        |             |  |  |  |  |  |  |  |  |  |

|--------|--------------------|--------|-------------|--|--|--|--|--|--|--|--|--|

| Signal | Function           | Туре   | Properties  |  |  |  |  |  |  |  |  |  |

| RST_N  | Global reset input | Input  | IOL, PU, ST |  |  |  |  |  |  |  |  |  |

| тск    | Test clock         | Input  | IOL, PD, ST |  |  |  |  |  |  |  |  |  |

| TDI    | Test data input    | Input  | IOL, PU     |  |  |  |  |  |  |  |  |  |

| TDO    | Test data output   | Output | IOL, PD     |  |  |  |  |  |  |  |  |  |

| TMS    | Test mode select   | Input  | IOL, PU     |  |  |  |  |  |  |  |  |  |

| TRST_N | Test reset input   | Input  | IOL, PU, ST |  |  |  |  |  |  |  |  |  |

-XM()S

The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 8.3 Boot from SPI slave

If set to boot from SPI slave, the processor enables the three pins specified in Figure 12 and expects a boot image to be clocked in. The supported clock polarity and phase are 0/0 and 1/1.

Figure 12: SPI slave pins

| Pin   | Signal | Description                |

|-------|--------|----------------------------|

| X0D00 | SS     | Slave Select               |

| X0D10 | SCLK   | Clock                      |

| X0D11 | MOSI   | Master Out Slave In (Data) |

The xCORE Tile expects each byte to be transferred with the *least-significant bit first*. The pins used for SPI boot are hardcoded in the boot ROM and cannot be changed. If required, an SPI boot program can be burned into OTP that uses different pins.

#### 8.4 Boot from xConnect Link

If set to boot from an xConnect Link, the processor enables its link(s) around 2 us after the boot process starts. Enabling the Link switches off the pull-down resistors on the link, drives all the TX wires low (the initial state for the Link), and monitors the RX pins for boot-traffic; they must be low at this stage. If the internal pull-down is too weak to drain any residual charge, external pull-downs of 10K may be required on those pins.

The boot-rom on the core will then:

- 1. Allocate channel-end 0.

- 2. Input a word on channel-end 0. It will use this word as a channel to acknowledge the boot. Provide the null-channel-end 0x0000FF02 if no acknowledgment is required.

- 3. Input the boot image specified above, including the CRC.

- 4. Input an END control token.

- 5. Output an END control token to the channel-end received in step 2.

- 6. Free channel-end 0.

- 7. Jump to the loaded code.

#### 8.5 Boot from OTP

If an xCORE tile is set to use secure boot (see Figure 8), the boot image is read from address 0 of the OTP memory in the tile's security module.

The TRST\_N pin must be asserted low during and after power up for 100 ns. If JTAG is not required, the TRST\_N pin can be tied to ground to hold the JTAG module in reset.

The JTAG device identification register can be read by using the IDCODE instruction. Its contents are specified in Figure 15.

Figure 15 IDCODE return value

| 15:       | Bit | 31  |      |   |   |   |   |   |   |   |    |      | D   | evice | e Ide | ntifi | catio | n Re | egist | er |   |   |   |     |      |      |       |       |   |   | E | it0 |

|-----------|-----|-----|------|---|---|---|---|---|---|---|----|------|-----|-------|-------|-------|-------|------|-------|----|---|---|---|-----|------|------|-------|-------|---|---|---|-----|

| -         |     | Ver | sion |   |   |   |   |   |   |   | Ра | rt N | umb | er    |       |       |       |      |       |    |   |   | I | Man | ufac | ture | r Ide | ntity | , |   |   | 1   |

| DE<br>lue | 0   | 0   | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0    | 0   | 0     | 0     | 0     | 0     | 1    | 1     | 0  | 0 | 1 | 1 | 0   | 0    | 0    | 1     | 1     | 0 | 0 | 1 | 1   |

| lue       | 0   |     |      |   |   | ( | ) |   |   | ( | )  |      |     | (     | )     |       |       | 6    | 5     |    |   | e | 5 |     |      | 3    | 3     |       |   | 1 | 3 |     |

The JTAG usercode register can be read by using the USERCODE instruction. Its contents are specified in Figure 16. The OTP User ID field is read from bits [22:31] of the security register on xCORE Tile 0, *see* §9.1 (all zero on unprogrammed devices).

Figure 16 USERCODE return value

|         | Bit | itt 3 1<br>OTP User ID |  |   |   |   |     |   | 1 Usercode Register     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | В | lit0 |   |   |   |   |   |   |   |

|---------|-----|------------------------|--|---|---|---|-----|---|-------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|---|---|---|---|---|---|---|

| ):<br>- |     |                        |  |   |   |   |     |   | Unused Silicon Revision |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |      |   |   |   |   |   |   |   |

| Ξ       | 0   | 0                      |  | 0 | 0 | 0 | 0   | 0 | 0                       | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 5       |     | 0 0                    |  |   |   | ( | 0 2 |   |                         | 2 |   |   |   | 3 |   |   | ( | ) |   |   | ( | ) |   |   | ( | )    |   |   |   |   |   |   |   |

# 11 Board Integration

The device has the following power supply pins:

- ▶ VDD pins for the xCORE Tile

- VDDIO pins for the I/O lines. Separate I/O supplies are provided for the left, top, and right side of the package; different I/O voltages may be supplied on those. The signal description (Section 4) specifies which I/O is powered from which power-supply

- PLL\_AVDD pins for the PLL

- OTP\_VCC pins for the OTP

Several pins of each type are provided to minimize the effect of inductance within the package, all of which must be connected. The power supplies must be brought up monotonically and input voltages must not exceed specification at any time.

The VDD supply must ramp from 0V to its final value within 10 ms to ensure correct startup.

The VDDIO and OTP\_VCC supply must ramp to its final value before VDD reaches 0.4 V.

The PLL\_AVDD supply should be separated from the other noisier supplies on the board. The PLL requires a very clean power supply, and a low pass filter (for example, a  $4.7 \Omega$  resistor and 100 nF multi-layer ceramic capacitor) is recommended on this pin.

*IPC/JEDEC Standard For Moisture/Reflow Sensitivity Classification For Nonhermetic Solid State Surface-Mount Devices J-STD-020* Revision D.

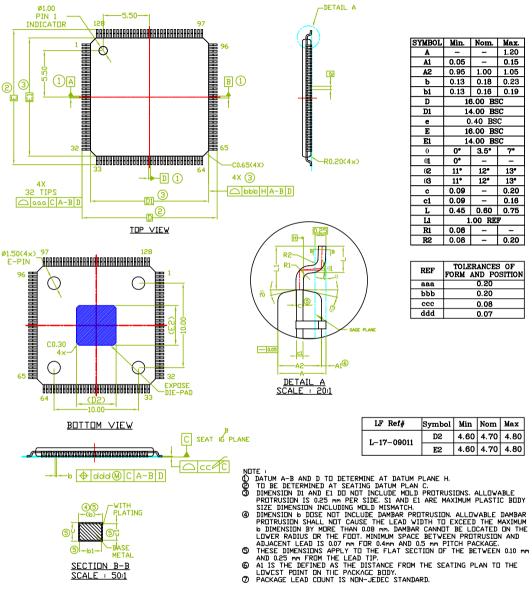

#### **Package Information** 13

| SYMBOL     | Min.      | Nom.    | Max.      |  |  |  |

|------------|-----------|---------|-----------|--|--|--|

| A          | -         | -       | 1.20      |  |  |  |

| A1         | 0.05      | -       | 0.15      |  |  |  |

| A2         | 0.95      | 1.00    | 1.05      |  |  |  |

| Ъ          | 0.13      | 0.18    | 0.23      |  |  |  |

| b1         | 0.13      | 0.16    | 0.19      |  |  |  |

| D          | 10        | 3.00 BS | C         |  |  |  |

| D1         | 14        | 1.00 BS | SC .      |  |  |  |

| e          | 0         | .40 BS  | С         |  |  |  |

| E          | 10        | 3.00 BS | šC        |  |  |  |

| E1         | 14.00 BSC |         |           |  |  |  |

| θ          | 0"        | 3.5°    | <b>7°</b> |  |  |  |

| <b>61</b>  | 0*        | -       | -         |  |  |  |

| 62         | 11•       | 12*     | 13*       |  |  |  |

| 6 <b>3</b> | 11*       | 12*     | 13*       |  |  |  |

| с          | 0.09      | -       | 0.20      |  |  |  |

| c1         | 0.09      | -       | 0.16      |  |  |  |

| L          | 0.45      | 0.60    | 0.75      |  |  |  |

| 11         | 1.00 REF  |         |           |  |  |  |

| R1         | 0.08      | -       | -         |  |  |  |

| R2         | 0.08      | -       | 0.20      |  |  |  |

| REF | TOLERANCES OF<br>FORM AND POSITION |

|-----|------------------------------------|

| aaa | 0.20                               |

| bbb | 0.20                               |

| ccc | 0.08                               |

| ddd | 0.07                               |

| LF Ref#    | Symbol | Min  | Nom  | Max  |

|------------|--------|------|------|------|

| L-17-09011 | D2     | 4.60 | 4.70 | 4.80 |

| D-11-09011 | E2     | 4.60 | 4.70 | 4.80 |

# Appendices

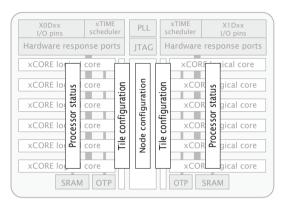

# A Configuration of the XL212-512-TQ128

The device is configured through banks of registers, as shown in Figure 29.

Figure 29: Registers

> The following communication sequences specify how to access those registers. Any messages transmitted contain the most significant 24 bits of the channel-end to which a response is to be sent. This comprises the node-identifier and the channel number within the node. if no response is required on a write operation, supply 24-bits with the last 8-bits set, which suppresses the reply message. Any multi-byte data is sent most significant byte first.

# A.1 Accessing a processor status register

The processor status registers are accessed directly from the processor instruction set. The instructions GETPS and SETPS read and write a word. The register number should be translated into a processor-status resource identifier by shifting the register number left 8 places, and ORing it with 0x0B. Alternatively, the functions getps(reg) and setps(reg,value) can be used from XC.

# A.2 Accessing an xCORE Tile configuration register

xCORE Tile configuration registers can be accessed through the interconnect using the functions write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tile  $\rightarrow$  ref, ...), where tileref is the name of the xCORE Tile, e.g. tile[1]. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the xCORE tile configuration registers. The destination of the channel-end should be set to 0xnnnnC20C where nnnnnn is the tile-identifier.

A write message comprises the following:

#### B.1 RAM base address: 0x00

This register contains the base address of the RAM. It is initialized to 0x00040000.

**0x00**: RAM base address

| 00: | Bits | Perm | Init | Description                                |

|-----|------|------|------|--------------------------------------------|

| se. | 31:2 | RW   |      | Most significant 16 bits of all addresses. |

| SS  | 1:0  | RO   | -    | Reserved                                   |

### B.2 Vector base address: 0x01

Base address of event vectors in each resource. On an interrupt or event, the 16 most significant bits of the destination address are provided by this register; the least significant 16 bits come from the event vector.

0x01: Vector base address

|   | Bits  | Perm | Init | Description                      |

|---|-------|------|------|----------------------------------|

| 2 | 31:18 | RW   |      | The event and interrupt vectors. |

| 5 | 17:0  | RO   | -    | Reserved                         |

# B.3 xCORE Tile control: 0x02

Register to control features in the xCORE tile

| Bits  | Perm | Init | Description                                                                                                                                                                                                                           |  |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                                                              |  |

| 25:18 | RW   | 0    | RGMII TX data delay value (in PLL output cycle increments)                                                                                                                                                                            |  |

| 17:9  | RW   | 0    | RGMII TX clock divider value. TX clk rises when counter (clocked<br>by PLL output) reaches this value and falls when counter reaches<br>(value»1). Value programmed into this field should be actual<br>divide value required minus 1 |  |

| 8     | RW   | 0    | Enable RGMII interface periph ports                                                                                                                                                                                                   |  |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                                                                              |  |

| 5     | RW   | 0    | Select the dynamic mode (1) for the clock divider when the clock divider is enabled. In dynamic mode the clock divider is only activated when all active threads are paused. In static mode the clock divider is always enabled.      |  |

| 4     | RW   | 0    | Enable the clock divider. This divides the output of the PLL to facilitate one of the low power modes.                                                                                                                                |  |

| 3:0   | RO   | -    | Reserved                                                                                                                                                                                                                              |  |

-XMOS<sup>®</sup>

0x02: xCORE Tile control

### B.4 xCORE Tile boot status: 0x03

This read-only register describes the boot status of the xCORE tile.

| Bits  | Perm | Init | Description                                               |  |

|-------|------|------|-----------------------------------------------------------|--|

| 31:24 | RO   | -    | Reserved                                                  |  |

| 23:16 | RO   |      | Processor number.                                         |  |

| 15:9  | RO   | -    | Reserved                                                  |  |

| 8     | RO   |      | Overwrite BOOT_MODE.                                      |  |

| 7:6   | RO   | -    | Reserved                                                  |  |

| 5     | RO   |      | Indicates if core1 has been powered off                   |  |

| 4     | RO   |      | Cause the ROM to not poll the OTP for correct read levels |  |

| 3     | RO   |      | Boot ROM boots from RAM                                   |  |

| 2     | RO   |      | Boot ROM boots from JTAG                                  |  |

| 1:0   | RO   |      | The boot PLL mode pin value.                              |  |

0x03: xCORE Tile boot status

# B.5 Security configuration: 0x05

Copy of the security register as read from OTP.

| Bits  | Perm | Init | Description                                                 |  |

|-------|------|------|-------------------------------------------------------------|--|

| 31    | RW   |      | Disables write permission on this register                  |  |

| 30:15 | RO   | -    | Reserved                                                    |  |

| 14    | RW   |      | Disable access to XCore's global debug                      |  |

| 13    | RO   | -    | Reserved                                                    |  |

| 12    | RW   |      | lock all OTP sectors                                        |  |

| 11:8  | RW   |      | lock bit for each OTP sector                                |  |

| 7     | RW   |      | Enable OTP reduanacy                                        |  |

| 6     | RO   | -    | Reserved                                                    |  |

| 5     | RW   |      | Override boot mode and read boot image from OTP             |  |

| 4     | RW   |      | Disable JTAG access to the PLL/BOOT configuration registers |  |

| 3:1   | RO   | -    | Reserved                                                    |  |

| 0     | RW   |      | Disable access to XCore's JTAG debug TAP                    |  |

**0x05:** Security configuration

| 0x13:                | Bits | Perm | Init | Description              |

|----------------------|------|------|------|--------------------------|

| DGETREG<br>operand 1 | 31:8 | RO   | -    | Reserved                 |

|                      | 7:0  | DRW  |      | Thread number to be read |

#### B.16 DGETREG operand 2: 0x14

Register number to be read by DGETREG

**0x14:** DGETREG operand 2

| <b>-</b> | Bits | Perm | Init | Description                |  |

|----------|------|------|------|----------------------------|--|

|          | 31:5 | RO   | -    | Reserved                   |  |

| 2        | 4:0  | DRW  |      | Register number to be read |  |

### B.17 Debug interrupt type: 0x15

Register that specifies what activated the debug interrupt.

| Bits  | Perm | Init | Description                                                                                                                                                                                                              |  |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                 |  |

| 17:16 | DRW  |      | Number of the hardware breakpoint/watchpoint which caused<br>the interrupt (always 0 for =HOST= and =DCALL=). If multiple<br>breakpoints/watchpoints trigger at once, the lowest number is<br>taken.                     |  |

| 15:8  | DRW  |      | Number of thread which caused the debug interrupt (always 0 in the case of $=HOST=$ ).                                                                                                                                   |  |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                 |  |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point |  |

**0x15:** Debug interrupt type

# B.18 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

-XMOS-

### B.22 Instruction breakpoint control: 0x40 .. 0x43

This register controls which logical cores may take an instruction breakpoint, and under which condition.

| Bits  | Perm | Init | Description                                                                                              |  |

|-------|------|------|----------------------------------------------------------------------------------------------------------|--|

| 31:24 | RO   | -    | Reserved                                                                                                 |  |

| 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint to be enabled individually for each thread. |  |

| 15:2  | RO   | -    | Reserved                                                                                                 |  |

| 1     | DRW  | 0    | When 0 break when PC == IBREAK_ADDR. When 1 = break when PC != IBREAK_ADDR.                              |  |

| 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                            |  |

0x40 .. 0x43: Instruction breakpoint control

### B.23 Data watchpoint address 1: 0x50 .. 0x53

This set of registers contains the first address for the four data watchpoints.

**0x50 .. 0x53:** Data watchpoint address 1

| Data<br>hpoint | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ress 1         | 31:0 | DRW  |      | Value.      |

#### B.24 Data watchpoint address 2: 0x60 .. 0x63

This set of registers contains the second address for the four data watchpoints.

0x60 .. 0x63: Data watchpoint address 2

| Data<br>chpoint | <b>D</b> <sup>1</sup> . <b>D</b> | Perm | Init | Description |

|-----------------|----------------------------------|------|------|-------------|

| dress 2         | 31:0                             | DRW  |      | Value.      |

# B.25 Data breakpoint control register: 0x70 .. 0x73

This set of registers controls each of the four data watchpoints.

-XMOS

XS2-L12A-512-TQ128

|                    | Bits  | Perm | Init | Description                                                                                              |

|--------------------|-------|------|------|----------------------------------------------------------------------------------------------------------|

|                    | 31:24 | RO   | -    | Reserved                                                                                                 |

|                    | 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint to be enabled individually for each thread. |

| 0x70 0x73:         | 15:3  | RO   | -    | Reserved                                                                                                 |

| Data<br>breakpoint | 2     | DRW  | 0    | When 1 the breakpoints will be be triggered on loads.                                                    |

| control            | 1     | DRW  | 0    | Determines the break condition: $0 = A AND B$ , $1 = A OR B$ .                                           |

| register           | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                            |

#### B.26 Resources breakpoint mask: 0x80 .. 0x83

This set of registers contains the mask for the four resource watchpoints.

| 0x80 0x83:<br>Resources |      |      |      |             |

|-------------------------|------|------|------|-------------|

| breakpoint              | Bits | Perm | Init | Description |

| mask                    | 31:0 | DRW  |      | Value.      |

#### B.27 Resources breakpoint value: 0x90 .. 0x93

This set of registers contains the value for the four resource watchpoints.

| <b>0x90 0x93:</b><br>Resources<br>breakpoint<br>value |      |      |      |             |

|-------------------------------------------------------|------|------|------|-------------|

|                                                       | Bits | Perm | Init | Description |

|                                                       | 31:0 | DRW  |      | Value.      |

#### B.28 Resources breakpoint control register: 0x9C .. 0x9F

This set of registers controls each of the four resource watchpoints.

0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                     |

|------|------|------|-----------------------------------------------------------------------------------------------------------------|

| 31   | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch, XCore(PS_DBG_Scratch) and JTAG |

| 30:1 | RO   | -    | Reserved                                                                                                        |

| 0    | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch                                 |

# C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

**0x05:** Cause debug interrupts

|    | Bits | Perm | Init | Description                                 |

|----|------|------|------|---------------------------------------------|

|    | 31:2 | RO   | -    | Reserved                                    |

| •  | 1    | CRW  | 0    | 1 when the processor is in debug mode.      |

| i. | 0    | CRW  | 0    | Request a debug interrupt on the processor. |

# C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| Bits  | Perm | Init | Description                                                   |

|-------|------|------|---------------------------------------------------------------|

| 31    | CRW  | 0    | Clock disable. Writing '1' will remove the clock to the tile. |

| 30:16 | RO   | -    | Reserved                                                      |

| 15:0  | CRW  | 0    | Clock divider.                                                |

# C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

-XMOS

44

0x41: PC of logical core 1

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

# C.11 PC of logical core 2: 0x42

Value of the PC of logical core 2.

0x42: PC of logical core 2

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

# C.12 PC of logical core 3: 0x43

Value of the PC of logical core 3.

| 0x43:         |      |      |      |             |

|---------------|------|------|------|-------------|

| PC of logical | Bits | Perm | Init | Description |

| core 3        | 31:0 | CRO  |      | Value.      |

#### C.13 PC of logical core 4: 0x44

Value of the PC of logical core 4.

**0x44** PC of logical core 4

| 0x44:<br>ogical | Bits | Perm | Init | Description |

|-----------------|------|------|------|-------------|

| ore 4           | 31:0 | CRO  |      | Value.      |

# C.14 PC of logical core 5: 0x45

Value of the PC of logical core 5.

**0x45:** PC of logical core 5

| • | Bits | Perm | Init | Description |

|---|------|------|------|-------------|

|   | 31:0 | CRO  |      | Value.      |

| Bits | Perm | Init | Description                                             |

|------|------|------|---------------------------------------------------------|

| 31:5 | RO   | -    | Reserved                                                |

| 4    | RW   |      | Reserved.                                               |

| 3:2  | RO   | -    | Reserved                                                |

| 1    | RW   |      | If set, XCore1 is the source of last GlobalDebug event. |

| 0    | RW   |      | If set, XCore0 is the source of last GlobalDebug event. |

**0x1F:** Debug source

# D.15 Link status, direction, and network: 0x20 .. 0x28

These registers contain status information for low level debugging (read-only), the network number that each link belongs to, and the direction that each link is part of. The registers control links 0..7.

| Bits  | Perm | Init | Description                                                                                 |

|-------|------|------|---------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                    |

| 25:24 | RO   |      | Identify the SRC_TARGET type 0 - SLink, 1 - PLink, 2 - SSCTL, 3 - Undefine.                 |

| 23:16 | RO   |      | When the link is in use, this is the destination link number to which all packets are sent. |

| 15:12 | RO   | -    | Reserved                                                                                    |

| 11:8  | RW   | 0    | The direction that this link operates in.                                                   |

| 7:6   | RO   | -    | Reserved                                                                                    |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, reset as 0.                              |

| 3     | RO   | -    | Reserved                                                                                    |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                       |

| 1     | RO   |      | 1 when the dest side of the link is in use.                                                 |

| 0     | RO   |      | 1 when the source side of the link is in use.                                               |

0x20 .. 0x28: Link status, direction, and network

### D.16 PLink status and network: 0x40 .. 0x47

These registers contain status information and the network number that each processor-link belongs to.

# E JTAG, xSCOPE and Debugging

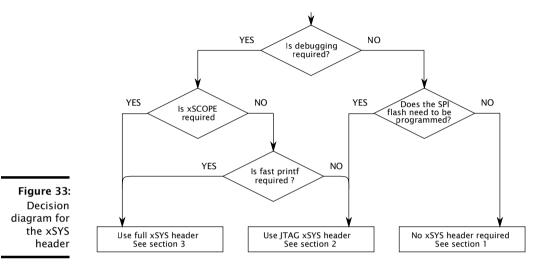

If you intend to design a board that can be used with the XMOS toolchain and xTAG debugger, you will need an xSYS header on your board. Figure 33 shows a decision diagram which explains what type of xSYS connectivity you need. The three subsections below explain the options in detail.

# E.1 No xSYS header

The use of an xSYS header is optional, and may not be required for volume production designs. However, the XMOS toolchain expects the xSYS header; if you do not have an xSYS header then you must provide your own method for writing to flash/OTP and for debugging.

# E.2 JTAG-only xSYS header

The xSYS header connects to an xTAG debugger, which has a 20-pin 0.1" female IDC header. The design will hence need a male IDC header. We advise to use a boxed header to guard against incorrect plug-ins. If you use a 90 degree angled header, make sure that pins 2, 4, 6, ..., 20 are along the edge of the PCB.

Connect pins 4, 8, 12, 16, 20 of the xSYS header to ground, and then connect:

$\mathbf{X}$  M()S

- ▶ TDI to pin 5 of the xSYS header

- TMS to pin 7 of the xSYS header

- TCK to pin 9 of the xSYS header

- TDO to pin 13 of the xSYS header

# F Schematics Design Check List

✓ This section is a checklist for use by schematics designers using the XL212-512-TQ128. Each of the following sections contains items to check for each design.

### F.1 Power supplies

- □ VDDIO and OTP\_VCC supply is within specification before the VDD (core) supply is turned on. Specifically, the VDDIO and OTP\_VCC supply is within specification before VDD (core) reaches 0.4V (Section 11).

- The VDD (core) supply ramps monotonically (rises constantly) from 0V to its final value (0.95V 1.05V) within 10ms (Section 11).

- The VDD (core) supply is capable of supplying 700 mA (Section 11 and Figure 18).

- PLL\_AVDD is filtered with a low pass filter, for example an RC filter, see Section 11

#### F.2 Power supply decoupling

- The design has multiple decoupling capacitors per supply, for example at least four0402 or 0603 size surface mount capacitors of 100nF in value, per supply (Section 11).

- A bulk decoupling capacitor of at least 10uF is placed on each supply (Section 11).

#### F.3 Power on reset

The RST\_N and TRST\_N pins are asserted (low) during or after power up. The device is not used until these resets have taken place.

#### F.4 Clock

- □ The CLK input pin is supplied with a clock with monotonic rising edges and low jitter.

- You have chosen an input clock frequency that is supported by the device (Section 7).

# G PCB Layout Design Check List

✓ This section is a checklist for use by PCB designers using the XS2-L12A-512-TQ128. Each of the following sections contains items to check for each design.

### G.1 Ground Plane

- □ Multiple vias (eg, 9) have been used to connect the center pad to the PCB ground plane. These minimize impedance and conduct heat away from the device. (Section 11.2).

- Other than ground vias, there are no (or only a few) vias underneath or closely around the device. This create a good, solid, ground plane.

### G.2 Power supply decoupling

- The decoupling capacitors are all placed close to a supply pin (Section 11).

- The decoupling capacitors are spaced around the device (Section 11).

- The ground side of each decoupling capacitor has a direct path back to the center ground of the device.

#### G.3 PLL\_AVDD

The PLL\_AVDD filter (especially the capacitor) is placed close to the PLL\_AVDD pin (Section 11).

# J Revision History

| Date       | Description                                                                   |

|------------|-------------------------------------------------------------------------------|

| 2015-03-20 | Preliminary release                                                           |

| 2015-04-14 | Added RST to pins to be pulled hard, and removed reference to TCK from Errata |

|            | Removed TRST_N references in packages that have no TRST_N                     |

| 2015-04-29 | VDDIOR and VDD (pins 47/48) switched - Section 3                              |

| 2015-05-06 | Removed references to DEBUG_N                                                 |

| 2015-07-09 | Updated electrical characteristics - Section 12                               |

| 2015-08-27 | Updated part marking - Section 14                                             |

| 2016-04-20 | Typical internal pull-up and pull down current diagrams added - Section 12    |

| 2017-02-02 | Clarified available boot modes/source pins - Section 8                        |

XMOS®

Copyright © 2017, All Rights Reserved.

Xmos Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. Xmos Ltd. makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.