Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | FR60 RISC                                                                     |

| Core Size                  | 32-Bit Single-Core                                                            |

| Speed                      | 80MHz                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, UART/USART                                  |

| Peripherals                | DMA, LVD, WDT                                                                 |

| Number of I/O              | 48                                                                            |

| Program Memory Size        | 288KB (288K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 14K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-LQFP                                                                       |

| Supplier Device Package    | 64-LQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb91f463ncpmc-gse1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part Number<br>Parameter            | CY91V460A                                   | CY91F463NA<br>CY91F463NC               |  |  |  |

|-------------------------------------|---------------------------------------------|----------------------------------------|--|--|--|

| 16-bit PFM                          | 1 channel                                   | No                                     |  |  |  |

| Sound Generator                     | 1 channel                                   | No                                     |  |  |  |

| 8/16-bit up/down counter            | 4 channels (8-bit) / 2 channels (16-bit)    | 2 channels (8-bit) /1 channel (16-bit) |  |  |  |

| C_CAN                               | 6 channels (128 message buffers)            | 2 channels (32 message buffers)        |  |  |  |

| LIN-USART                           | 4 channels + 4 channels (FIFO) + 8 channels | 4 channels                             |  |  |  |

| l <sup>2</sup> C (400 kbps)         | 4 channels                                  | 2 channels                             |  |  |  |

| FR external bus                     | Yes (32-bit address, 32-bit data)           | No                                     |  |  |  |

| External interrupt                  | 16 channels                                 | 10 channels                            |  |  |  |

| NMI interrupts                      | Yes                                         | No                                     |  |  |  |

| Stepping motor controller<br>(SMC)  | 6 channels                                  | No                                     |  |  |  |

| LCD controller (40 4)               | 1 channel                                   | No                                     |  |  |  |

| 10-bit A/D converter                | 32 channels                                 | 8 channels                             |  |  |  |

| Alarm comparator                    | 2 channels                                  | No                                     |  |  |  |

| Clock supervisor                    | Yes                                         | No                                     |  |  |  |

| Main clock oscillator               | 4 M                                         | Hz                                     |  |  |  |

| Sub clock oscillator                | 32 kHz                                      | -                                      |  |  |  |

| CR oscillator                       | 100 kHz                                     | 100 kHz / 2 MHz                        |  |  |  |

| PLL                                 | × 2                                         | 20                                     |  |  |  |

| DSU4                                | Yes                                         | No                                     |  |  |  |

| EDSU                                | Yes (32 BP) <sup>[1]</sup>                  | Yes (8 BP) <sup>[1]</sup>              |  |  |  |

| Power supply voltage                | 3 V /                                       | 5 V                                    |  |  |  |

| Regulator                           | Yes                                         |                                        |  |  |  |

| Power consumption                   | n.a.                                        | < 700 mW                               |  |  |  |

| Temperature range (T <sub>A</sub> ) | 0 °C to +70°C                               | - 40 °C to + 105°C                     |  |  |  |

| Package                             | BGA-660                                     | LQFP-64                                |  |  |  |

1. MPU channels use EDSU breakpoint registers (shared operation between MPU and EDSU).

# 5. Precautions for Handling The Devices

Any semiconductor devices have inherently a certain rate of failure. The possibility of failure is greatly affected by the conditions in which they are used (circuit conditions, environmental conditions, etc.). This page describes precautions that must be observed to minimize the chance of failure and to obtain higher reliability from your Cypress semiconductor devices.

## 5.1 **Precautions for Product Design**

This section describes precautions when designing electronic equipment using semiconductor devices.

### ■ Absolute Maximum Ratings

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### Recommended Operating Conditions

The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges. Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their Cypress representatives beforehand.

### Processing and Protection of Pins

These precautions must be followed when handling the pins which connect semiconductor devices to power supply and input/output functions.

#### 1. Preventing Over-Voltage and Over-Current Conditions

Exposure to voltage or current levels in excess of maximum ratings at any pin is likely to cause deterioration within the device, and in extreme cases leads to permanent damage of the device. Try to prevent such over voltage or over-current conditions at the design stage.

2. Protection of Output Pins

Shorting of output pins to supply pins or other output pins, or connection to large capacitance can cause large current flows. Such conditions if present for extended periods of time can damage the device. Therefore, avoid this type of connection.

#### 3. Handling of Unused Input Pins

Unconnected input pins with very high impedance levels can adversely affect stability of operation. Such pins should be connected through an appropriate resistance to a power supply pin or ground pin.

#### Latch-up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

#### Note:

The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

(a) Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

(b) Be sure that abnormal current flows do not occur during the power-on sequence.

### ■ Observance of Safety Regulations and Standards

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

## 5.3 **Precautions for Use Environment**

Reliability of semiconductor devices depends on ambient temperature and other conditions as described above. For reliable performance, do the following:

1. Humidity

Prolonged use in high humidity can lead to leakage in devices as well as printed circuit boards. If high humidity levels are anticipated, consider anti-humidity processing.

- Discharge of Static Electricity

When high-voltage charges exist close to semiconductor devices, discharges can cause abnormal operation. In such cases, use

anti-static measures or processing to prevent discharges.

- Corrosive Gases, Dust, or Oil

Exposure to corrosive gases or contact with dust or oil may lead to chemical reactions that will adversely affect the device. If you

use devices in such conditions, consider ways to prevent such exposure or to protect the devices.

- Radiation, Including Cosmic Radiation Most devices are not designed for environments involving exposure to radiation or cosmic radiation. Users should provide shielding as appropriate.

- 5. Smoke, Flame

**Note**: Plastic molded devices are flammable, and therefore should not be used near combustible substances. If devices begin to smoke or burn, there is danger of the release of toxic gases.

Customers considering the use of Cypress products in other special environmental conditions should consult with Cypress sales representatives.

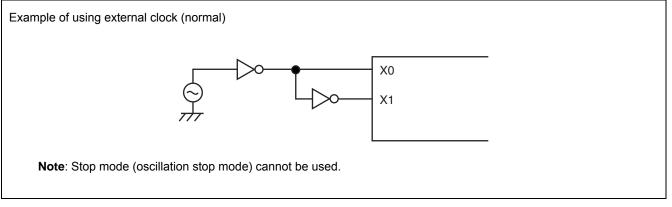

### Notes on using external clock

When using the external clock, as a general rule you should simultaneously supply X0 and X1 pins. And also, the clock signal to X0 should be supplied a clock signal with the reverse phase to X1 pins. However, in this case the stop mode (oscillation stop mode) must not be used.

### Notes on operating in PLL clock mode

If the oscillator is disconnected or the clock input stops when the PLL clock is selected, the microcontroller may continue to operate at the free-running frequency of the self-oscillating circuit of the PLL. However, this self-running operation cannot be guaranteed.

### 9.4 Registers

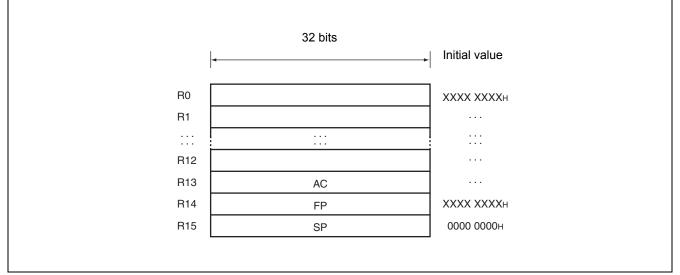

### 9.4.1 General-purpose Register

Registers R0 to R15 are general-purpose registers. These registers can be used as accumulators for computation operations and as pointers for memory access.

Enhanced commands are provided for some of the 16 registers to enable their use for particular applications.

R13 : Virtual accumulator

R14 : Frame pointer

R15 : Stack pointer

Initial values at reset are undefined for R0 to R14. The value for R15 is 0000000<sub>H</sub> (SSP value).

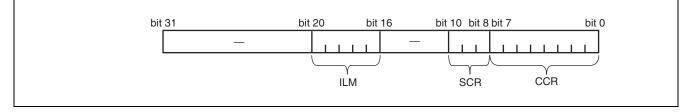

### 9.4.2 PS (Program Status)

This register holds the program status, and is divided into three parts, ILM, SCR, and CCR.

All undefined bits (-) in the diagram are reserved bits. The values are always read "0". Write access to these bits is invalid.

# 10. Mode Setting

In the FR family, the mode pins (MD2, MD1, MD0) and the mode register (MODR) are used to set the operating mode.

## 10.1 Mode Pins

The three pins MD2, MD1, MD0 are used to specify the mode vector fetch.

Settings other than shown in the table are prohibited.

| Мо  | Mode Pins <sup>[1]</sup> |     | Mode Name                | Reset Vector | Remarks     |  |

|-----|--------------------------|-----|--------------------------|--------------|-------------|--|

| MD2 | MD1                      | MD0 | mode Name                | Access Area  | Keinarks    |  |

| 0   | 0                        | 0   | Internal ROM mode vector | Internal     |             |  |

| 0   | 0                        | 1   | External ROM mode vector | External     | Not allowed |  |

1. Always use MD3 with "0".

# 10.2 Mode Register (MODR)

The data written to the mode register using mode vector fetch is called mode data.

After the mode register (MODR) is set, the device operates according to the operation mode set in this register.

The mode register is set by all reset sources. User programs cannot write data to the mode register.

Rewriting is allowed in the emulator mode. In this case, use an 8-bit length data transfer instruction.

Data cannot be written by the transfer instruction of the 16/32-bit length.

Be sure to set these bits to " $00000111_B$ ".

Operation is not guaranteed when any value other than " $00000111_B$ " is set.

**Note**: The mode data needs to be allocated in  $000FFFF8_H$  as byte data. The mode data ( $00000111_B$ ) must be allocated in bit 31 to bit 24, as the FR family uses the big endian architecture.

# **11. Recommended Setting**

### 11.1 Setting of PLL and Clock Gear

| Clock Input | PLL Multiplied Setting |      | Clock Gea | r Setting | PLL (vco) Output (X) | Base Clock |

|-------------|------------------------|------|-----------|-----------|----------------------|------------|

| [MHz]       | DIVM                   | DIVN | DIVG      | MULG      | [MHz]                | [MHz]      |

| 4           | 2                      | 20   | 16        | 20        | 160                  | 80         |

| 4           | 2                      | 19   | 16        | 20        | 152                  | 76         |

| 4           | 2                      | 18   | 16        | 20        | 144                  | 72         |

| 4           | 2                      | 17   | 16        | 16        | 136                  | 68         |

| 4           | 2                      | 16   | 16        | 16        | 128                  | 64         |

| 4           | 2                      | 15   | 16        | 16        | 120                  | 60         |

| 4           | 2                      | 14   | 16        | 16        | 112                  | 56         |

| 4           | 2                      | 13   | 16        | 12        | 104                  | 52         |

| 4           | 2                      | 12   | 16        | 12        | 96                   | 48         |

| 4           | 2                      | 11   | 16        | 12        | 88                   | 44         |

| 4           | 4                      | 10   | 16        | 24        | 160                  | 40         |

| 4           | 4                      | 9    | 16        | 24        | 144                  | 36         |

| 4           | 4                      | 8    | 16        | 24        | 128                  | 32         |

| 4           | 4                      | 7    | 16        | 24        | 112                  | 28         |

| 4           | 6                      | 6    | 16        | 24        | 144                  | 24         |

| 4           | 8                      | 5    | 16        | 28        | 160                  | 20         |

| 4           | 10                     | 4    | 16        | 32        | 160                  | 16         |

| 4           | 12                     | 3    | 16        | 32        | 144                  | 12         |

# 11.2 Setting of Flash Memory Controller

### 11.2.1 Setting of Flash Access Timing

For executing programs with a Flash memory, follow the settings below according to the frequency of CPU clock (CLKB). This setting is the most suitable for a high-speed access to the Flash memory.

### Table 2. Flash Memory Read Operating

| CPU Clock (CLKB) | ATD | ALEH | EQ | WEXH | WTC |

|------------------|-----|------|----|------|-----|

| To 24 MHz        | 0   | 0    | 0  | 0    | 1   |

| To 48 MHz        | 0   | 0    | 1  | 0    | 2   |

| To 80 MHz        | 1   | 1    | 3  | 0    | 4   |

### Table 3. Flash Memory Write Operating

| CPU Clock (CLKB) | ATD | ALEH | EQ | WEXH | WTC |

|------------------|-----|------|----|------|-----|

| To 32 MHz        | 1   | 0    | 1  | 0    | 4   |

| To 48 MHz        | 1   | 0    | 3  | 0    | 5   |

| To 64 MHz        | 1   | 1    | 3  | 0    | 6   |

| To 80 MHz        | 1   | 1    | 3  | 0    | 7   |

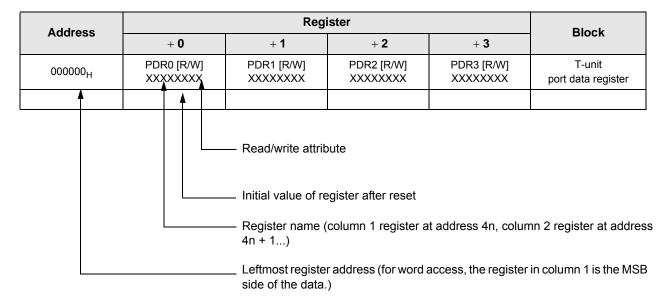

## 13. I/O Map

Note: Initial values of register bits are represented as follows:

- "1 ": Initial value "1 "

- " 0 ": Initial value " 0 "

- " X ": Initial value " undefined "

- " ": No physical register at this location

Access is prohibited to areas where the data access attributes are undefined.

| Address                                       |                                                            | Pleak                    |                           |                            |                                           |  |

|-----------------------------------------------|------------------------------------------------------------|--------------------------|---------------------------|----------------------------|-------------------------------------------|--|

| Address –                                     | +0                                                         | +1                       | +2                        | +3                         | Block                                     |  |

| 000060 <sub>H</sub><br>to 00007C <sub>H</sub> |                                                            | Rese                     | erved                     |                            | Reserved                                  |  |

| 000080 <sub>H</sub>                           | BGR100 [R/W]<br>00000000                                   | BGR000 [R/W]<br>00000000 | BGR101 [R/W]<br>00000000  | BGR001 [R/W]<br>00000000   |                                           |  |

| 000084 <sub>H</sub>                           | BGR102 [R/W]<br>00000000                                   | BGR002 [R/W]<br>00000000 | BGR103 [R/W]<br>00000000  | BGR003 [R/W]<br>00000000   | Baud rate<br>Generator<br>LIN-USART0 to 3 |  |

| 000088 <sub>H</sub> ,<br>00008C <sub>H</sub>  |                                                            | Rese                     | erved                     |                            |                                           |  |

| 000090 <sub>H</sub><br>to 0000FC <sub>H</sub> |                                                            | Rese                     | erved                     |                            | Reserved                                  |  |

| 000100 <sub>H</sub>                           | GCN10<br>00110010                                          |                          | Reserved                  | GCN20 [R/W]<br>0000        | PPG Control<br>0 to 3                     |  |

| 000104 <sub>H</sub>                           | GCN11<br>00110010                                          |                          | Reserved                  | GCN21 [R/W]<br>0000        | PPG Control<br>4 to 7                     |  |

| 000108 <sub>H</sub>                           |                                                            | Rese                     | erved                     |                            | Reserved                                  |  |

| 000110 <sub>H</sub>                           | PTMR<br>11111111                                           | • •                      |                           | 00 [W]<br>XXXXXXXX         |                                           |  |

| 000114 <sub>H</sub>                           | PDUT<br>XXXXXXXX                                           |                          | PCNH00 [R/W]<br>0000000 - | PCNL00 [R/W]<br>000000 - 0 | - PPG 0                                   |  |

| 000118 <sub>H</sub>                           | PTMR01 [R] PCSR01 [W]<br>11111111 1111111 XXXXXXXX XXXXXXX |                          |                           |                            |                                           |  |

| 00011C <sub>H</sub>                           | PDUT01 [W]<br>XXXXXXXX XXXXXXX                             |                          | PCNH01 [R/W]<br>0000000 - | PCNL01 [R/W]<br>000000 - 0 | - PPG 1                                   |  |

| 000120 <sub>H</sub>                           | PTMR<br>11111111                                           |                          | PCSR<br>XXXXXXXX          |                            |                                           |  |

| 000124 <sub>H</sub>                           | PDUT<br>XXXXXXXX                                           |                          | PCNH02 [R/W]<br>0000000 - | PCNL02 [R/W]<br>000000 - 0 | - PPG 2                                   |  |

| 000128 <sub>H</sub>                           | PTMR<br>11111111                                           |                          |                           | 03 [W]<br>XXXXXXXX         |                                           |  |

| 00012C <sub>H</sub>                           | PDUT<br>XXXXXXXX                                           | 03 [W]<br>XXXXXXXX       | PCNH03 [R/W]<br>0000000 - | PCNL03 [R/W]<br>000000 - 0 | - PPG 3                                   |  |

| 000130 <sub>H</sub>                           | PTMR<br>11111111                                           |                          |                           | 04 [W]<br>XXXXXXXX         | - PPG 4                                   |  |

| 000134 <sub>H</sub>                           | PDUT<br>XXXXXXXX                                           |                          | PCNH04 [R/W]<br>0000000 - | PCNL04 [R/W]<br>000000 - 0 | - PPG 4                                   |  |

| 000138 <sub>H</sub>                           | PTMR<br>11111111                                           |                          |                           | 05 [W]<br>XXXXXXXX         | DD0 5                                     |  |

| 00013C <sub>H</sub>                           | PDUT<br>XXXXXXXX                                           | 05 [W]<br>XXXXXXXX       | PCNH05 [R/W]<br>0000000 - | PCNL05 [R/W]<br>000000 - 0 | - PPG 5                                   |  |

| 000140 <sub>H</sub>                           | PTMR06 [R]<br>11111111 1111111                             |                          |                           | 06 [W]<br>XXXXXXXX         | <b>DDO 0</b>                              |  |

| 000144 <sub>H</sub>                           | PDUT<br>XXXXXXXX                                           | 06 [W]<br>XXXXXXXX       | PCNH06 [R/W]<br>0000000 - | PCNL06 [R/W]<br>000000 - 0 | PPG 6                                     |  |

| 000148 <sub>H</sub>                           | PTMR<br>11111111                                           |                          |                           | 07 [W]<br>XXXXXXXX         | 000 7                                     |  |

| 00014C <sub>H</sub>                           | PDUT<br>XXXXXXXX                                           |                          | PCNH07 [R/W]<br>0000000 - | PCNL07 [R/W]<br>000000 - 0 | - PPG 7                                   |  |

| Address                                       |                               | Block                            |                           |                                |                                  |

|-----------------------------------------------|-------------------------------|----------------------------------|---------------------------|--------------------------------|----------------------------------|

| Address –                                     | +0                            | +1                               | +2                        | +3                             | BIOCK                            |

| 000150 <sub>H</sub><br>to 00017C <sub>H</sub> |                               | Rese                             | erved                     |                                | Reserved                         |

| 000180 <sub>H</sub>                           | Reserved                      | ICS01 [R/W]<br>00000000          | Reserved                  | ICS23 [R/W]<br>00000000        |                                  |

| 000184 <sub>H</sub>                           | IPCP<br>XXXXXXXX              |                                  |                           | 1 [R]<br>XXXXXXXX              | Input<br>Capture<br>0 to 3       |

| 000188 <sub>H</sub>                           | IPCP2 [R]<br>XXXXXXXX XXXXXXX |                                  |                           | '3 [R]<br>XXXXXXXX             |                                  |

| 00018C <sub>H</sub>                           | OCS07<br>0 00                 | [R/W]<br>0000 00                 |                           | 3 [R/W]<br>0000 00             |                                  |

| 000190 <sub>H</sub>                           |                               | ) [R/W]<br>XXXXXXXX              |                           | 1 [R/W]<br>XXXXXXXX            | Output<br>Compare<br>0 to 3      |

| 000194 <sub>H</sub>                           | OCCP2<br>XXXXXXXX             |                                  |                           | 3 [R/W]<br>XXXXXXXX            |                                  |

| 000198 <sub>H</sub> ,<br>00019C <sub>H</sub>  |                               | Rese                             | erved                     |                                | Reserved                         |

| 0001A0 <sub>H</sub>                           |                               | Reserved ADERL [R/W]<br>00000000 |                           |                                |                                  |

| 0001A4 <sub>H</sub>                           | ADCS1 [R/W]<br>00000000       | ADCS0 [R/W]<br>00000000          | ADCR1 [R]<br>000000XX     | ADCR0 [R]<br>XXXXXXXX          | A/D<br>Converter                 |

| 0001A8 <sub>H</sub>                           | ADCT1 [R/W]<br>00010000       | ADCT0 [R/W]<br>00101100          | ADSCH [R/W]<br>00000      | ADECH [R/W]<br>00000           |                                  |

| 0001AC <sub>H</sub>                           |                               | Rese                             | erved                     |                                | Reserved                         |

| 0001B0 <sub>H</sub>                           | TMRLF<br>XXXXXXXX             |                                  |                           | 0 [R]<br>XXXXXXXX              | Dalaad Timor 0                   |

| 0001B4 <sub>H</sub>                           | Rese                          | erved                            | TMCSRH0<br>[R/W]<br>00000 | TMCSRL0<br>[R/W]<br>0 - 000000 | - Reload Timer 0<br>(PPG0, PPG1) |

| 0001B8 <sub>H</sub>                           | TMRLF<br>XXXXXXXX             | R1 [W]<br>XXXXXXXX               |                           | 1 [R]<br>XXXXXXXX              | - Reload Timer 1                 |

| 0001BC <sub>H</sub>                           | Rese                          | erved                            | TMCSRH1<br>[R/W]<br>00000 | TMCSRL1<br>[R/W]<br>0 - 000000 | (PPG2, PPG3)                     |

| 0001C0 <sub>H</sub>                           |                               | 2 [W]<br>XXXXXXXX                |                           | 2 [R]<br>XXXXXXXX              | Dalaad Timor O                   |

| 0001C4 <sub>H</sub>                           | Rese                          | erved                            | TMCSRH2<br>[R/W]<br>00000 | TMCSRL2<br>[R/W]<br>0 - 000000 | Reload Timer 2<br>(PPG4, PPG5)   |

| 0001C8 <sub>H</sub>                           | TMRLF<br>XXXXXXXX             | R3 [W]<br>XXXXXXXX               |                           | 3 [R]<br>XXXXXXXX              | Delas IT                         |

| 0001CC <sub>H</sub>                           | Rese                          | erved                            | TMCSRH3<br>[R/W]<br>00000 | TMCSRL3<br>[R/W]<br>0 - 000000 | - Reload Timer 3<br>(PPG6, PPG7) |

| 0001D0 <sub>H</sub><br>to 0001E7 <sub>H</sub> |                               | Rese                             | erved                     |                                | Reserved                         |

| <b>A</b> .   .                                   |                                                         | Black                                                                         |                                |                         |                                  |  |  |

|--------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------|-------------------------|----------------------------------|--|--|

| Address                                          | +0                                                      | +1                                                                            | +2                             | +3                      | Block                            |  |  |

| 0001E8 <sub>H</sub>                              | TMRLF<br>XXXXXXXX                                       |                                                                               |                                | 7 [R]<br>XXXXXXXX       | - Reload Timer 7                 |  |  |

| 0001EC <sub>H</sub>                              | Rese                                                    | rved                                                                          | TMCSRL7<br>[R/W]<br>0 - 000000 | (A/D converter)         |                                  |  |  |

| 0001F0 <sub>H</sub>                              |                                                         | TCDT0 [R/W]ReservedTCCS0 [R/W]XXXXXXXX XXXXXXX00000000                        |                                |                         |                                  |  |  |

| 0001F4 <sub>H</sub>                              |                                                         | TCDT1 [R/W]     Reserved     TCCS1 [R/W]       XXXXXXXX XXXXXXXX     00000000 |                                |                         |                                  |  |  |

| 0001F8 <sub>H</sub>                              | TCDT2 [R/W]ReservedTCCS2 [R/W]XXXXXXXX XXXXXXXX00000000 |                                                                               |                                |                         | Free-run Timer 2<br>(OCU0, OCU1) |  |  |

| 0001FC <sub>H</sub>                              | TCDT3<br>XXXXXXXX                                       |                                                                               | Reserved                       | TCCS3 [R/W]<br>00000000 | Free-run Timer 3<br>(OCU2, OCU3) |  |  |

| 000200 <sub>H</sub>                              |                                                         | DMACA0<br>00000000 0000XXXX X                                                 | [R/W] *<br>XXXXXXXX XXXXXXXX   |                         |                                  |  |  |

| 000204 <sub>H</sub>                              |                                                         |                                                                               | ) [R/W]<br>XXXXXXX XXXXXXXX    |                         |                                  |  |  |

| 000208 <sub>H</sub>                              |                                                         | DMACA1<br>00000000 0000XXXX X                                                 |                                |                         |                                  |  |  |

| 00020C <sub>H</sub>                              |                                                         | DMACB <sup>2</sup><br>00000000 00000000 X                                     | I [R/W]<br>XXXXXXX XXXXXXXX    |                         |                                  |  |  |

| 000210 <sub>H</sub>                              |                                                         | DMACA2<br>00000000 0000XXXX X                                                 |                                |                         |                                  |  |  |

| 000214 <sub>H</sub>                              |                                                         |                                                                               | 2 [R/W]<br>XXXXXXX XXXXXXXX    |                         |                                  |  |  |

| 000218 <sub>H</sub>                              |                                                         | DMACA3<br>00000000 0000XXXX X                                                 | [R/W] *<br>XXXXXXXX XXXXXXXX   |                         | DMAC                             |  |  |

| 00021C <sub>H</sub>                              |                                                         |                                                                               | 3 [R/W]<br>XXXXXXX XXXXXXXX    |                         |                                  |  |  |

| 000220 <sub>H</sub>                              |                                                         | DMACA4<br>00000000 0000XXXX X                                                 | [R/W] *<br>XXXXXXXX XXXXXXXX   |                         |                                  |  |  |

| 000224 <sub>H</sub>                              |                                                         |                                                                               | i [R/W]<br>XXXXXXX XXXXXXXX    |                         |                                  |  |  |

| 000228 <sub>H</sub><br>to<br>00023C <sub>H</sub> | Reserved                                                |                                                                               |                                |                         |                                  |  |  |

| 000240 <sub>H</sub>                              | DMACR [R/W]<br>0 0000                                   |                                                                               | Reserved                       |                         | -                                |  |  |

| 000244 <sub>H</sub><br>to<br>0002FC <sub>H</sub> |                                                         | Reserved                                                                      |                                |                         |                                  |  |  |

| 000300 <sub>H</sub>                              | UDRC1 [W]<br>00000000                                   | UDRC0 [W]<br>00000000                                                         | UDCR1 [R]<br>00000000          | UDCR0 [R]<br>00000000   |                                  |  |  |

| 000304 <sub>H</sub>                              | UDCCH0 [R/W]<br>00000000                                | UDCCL0 [R/W]<br>00001000                                                      | Reserved                       | UDCS0 [R/W]<br>00000000 | Up/Down Counter<br>0, 1          |  |  |

| 000308 <sub>H</sub>                              | UDCCH1 [R/W]<br>00000000                                | UDCCL1 [R/W]<br>00001000                                                      | Reserved                       | UDCS1 [R/W]<br>00000000 |                                  |  |  |

| Address –                                        | +0                            | +1                       | +2                   | +3                   | Block                |

|--------------------------------------------------|-------------------------------|--------------------------|----------------------|----------------------|----------------------|

| 000D40 <sub>H</sub><br>to<br>000D48 <sub>H</sub> |                               |                          |                      |                      |                      |

| 000D4C <sub>H</sub>                              | Rese                          |                          |                      |                      |                      |

| 000D50 <sub>H</sub>                              | Reserved DDR17 [R/W] Reserved |                          |                      |                      | R-bus Port Direction |

| 000D54 <sub>H</sub>                              | DDR20 [R/W]<br>-000- 000      | DDR21 [R/W]<br>-000- 000 | DDR22 [R/W]<br>0000  | Reserved             | Register             |

| 000D58 <sub>H</sub>                              | DDR24 [R/W]<br>00000000       |                          | Reserved             |                      |                      |

| 000D5C <sub>H</sub>                              | Reserved                      | DDR29 [R/W]<br>00000000  | Rese                 | erved                |                      |

| 000D60 <sub>H</sub>                              |                               | Rese                     | rved                 |                      |                      |

| 000D64 <sub>H</sub><br>to<br>000D7C <sub>H</sub> |                               | Rese                     | rved                 |                      | Reserved             |

| 000D80 <sub>H</sub><br>to<br>000D88 <sub>H</sub> | Reserved                      |                          |                      |                      |                      |

| 000D8C <sub>H</sub>                              | Rese                          | erved                    | PFR14 [R/W]<br>0000  | PFR15 [R/W]<br>0000  |                      |

| 000D90 <sub>H</sub>                              | Reserved                      | PFR17 [R/W]<br>00000000  | Rese                 | erved                | R-bus Port Function  |

| 000D94 <sub>H</sub>                              | PFR20 [R/W]<br>-000- 000      | PFR21 [R/W]<br>-000- 000 | PFR22 [R/W]<br>0000  | Reserved             | Register             |

| 000D98 <sub>H</sub>                              | PFR24 [R/W]<br>00000000       |                          | Reserved             |                      |                      |

| 000D9C <sub>H</sub>                              | Reserved                      | PFR29 [R/W]<br>00000000  | Rese                 | erved                |                      |

| 000DA0 <sub>H</sub>                              |                               | Rese                     | rved                 |                      |                      |

| 000DA4 <sub>H</sub><br>to<br>000DBC <sub>H</sub> |                               | Rese                     | rved                 |                      | Reserved             |

| 000DC0 <sub>H</sub><br>to 000DC8 <sub>H</sub>    |                               | R-bus Extension Port     |                      |                      |                      |

| 000DCC <sub>H</sub>                              | Rese                          | erved                    | EPFR14 [R/W]<br>0000 | EPFR15 [R/W]<br>0000 | Function Register    |

| 000DD0 <sub>H</sub>                              |                               |                          |                      |                      |                      |

| 000DD4 <sub>H</sub>                              | EPFR20 [R/W]<br>- 000- 000    | R-bus Extension Port     |                      |                      |                      |

| 000DD8 <sub>H</sub>                              | Reserved                      |                          |                      |                      | Function Register    |

| 000DDC <sub>H</sub>                              | Reserved                      |                          |                      |                      |                      |

| 000DE0 <sub>H</sub>                              |                               | Rese                     | rved                 |                      |                      |

| 000DE4 <sub>H</sub><br>to<br>000DFC <sub>H</sub> |                               | Rese                     | rved                 |                      | Reserved             |

| Address                                          | Register               |                            |                                              |                   |                                              |  |

|--------------------------------------------------|------------------------|----------------------------|----------------------------------------------|-------------------|----------------------------------------------|--|

| Audress                                          | +0                     | +1                         | +2                                           | +3                | Block                                        |  |

| 001000 <sub>H</sub>                              |                        |                            |                                              |                   |                                              |  |

| 001004 <sub>H</sub>                              |                        | DMADA<br>XXXXXXXX XXXXXXXX |                                              |                   |                                              |  |

| 001008 <sub>H</sub>                              |                        | DMASA<br>XXXXXXXX XXXXXXXX |                                              |                   |                                              |  |

| 00100C <sub>H</sub>                              |                        | DMADA<br>XXXXXXXX XXXXXXXX |                                              |                   |                                              |  |

| 001010 <sub>H</sub>                              |                        | DMASA<br>XXXXXXXX XXXXXXXX |                                              |                   | DMAC                                         |  |

| 001014 <sub>H</sub>                              |                        | DMADA<br>XXXXXXXX XXXXXXXX |                                              |                   | DIVIAG                                       |  |

| 001018 <sub>H</sub>                              |                        | DMASA<br>XXXXXXXX XXXXXXXX |                                              |                   |                                              |  |

| 00101C <sub>H</sub>                              |                        | DMADA<br>XXXXXXXX XXXXXXXX |                                              |                   |                                              |  |

| 001020 <sub>H</sub>                              |                        | DMASA<br>XXXXXXXX XXXXXXXX |                                              |                   |                                              |  |

| 001024 <sub>H</sub>                              |                        | DMADA<br>XXXXXXXX XXXXXXXX |                                              |                   |                                              |  |

| 001028 <sub>H</sub><br>to<br>006FFC <sub>H</sub> |                        | Reserved                   |                                              |                   |                                              |  |

| 007000 <sub>H</sub>                              | FMCS [R/W]<br>01101000 | FMCR [R/W]<br>0000         | FCHCF<br>00                                  |                   |                                              |  |

| 007004 <sub>H</sub>                              | FMWT<br>11111111       |                            | FMWT2 [R/W]<br>- 101                         | FMPS [R/W]<br>000 | Flash Memory/<br>I-Cache Control<br>Register |  |

| 007008 <sub>H</sub>                              |                        | FMA<br>00000               | C [R]<br>00000000 00000000                   |                   |                                              |  |

| 00700C <sub>H</sub>                              |                        | FCHA0                      | ) [R/W]<br>00000000 00000000                 |                   | I-Cache<br>Non-cacheable area                |  |

| 007010 <sub>H</sub>                              |                        | setting<br>Register        |                                              |                   |                                              |  |

| 007014 <sub>H</sub><br>to                        |                        | Reserved                   |                                              |                   |                                              |  |

| 00AFFC <sub>H</sub>                              |                        |                            |                                              |                   |                                              |  |

| 00B000 <sub>H</sub><br>to<br>00BFFC <sub>H</sub> |                        | BI-ROM size is 4 Kbytes    | : 00B000 <sub>H</sub> to 00BFFF <sub>H</sub> |                   | BI-ROM<br>4 Kbytes                           |  |

| 00C000 <sub>H</sub><br>to<br>00C3FC <sub>H</sub> |                        | Rese                       | rved                                         |                   | Reserved                                     |  |

# 14. Interrupt Source Table

|                                                            | Interrupt number |                  | Interrupt level  |                  | Interrupt vector |                           | Resource              |

|------------------------------------------------------------|------------------|------------------|------------------|------------------|------------------|---------------------------|-----------------------|

| Interrupt source                                           | Decimal          | Hexa-<br>decimal | Setting register | Register address | Offset           | Default vector<br>address | number <sup>[1]</sup> |

| Reset                                                      | 0                | 00               | -                | -                | 3FC <sub>H</sub> | 000FFFFC <sub>H</sub>     | -                     |

| Mode vector                                                | 1                | 01               | -                | -                | 3F8 <sub>H</sub> | 000FFFF8 <sub>H</sub>     | -                     |

| System reserved                                            | 2                | 02               | -                | -                | 3F4 <sub>H</sub> | 000FFFF4 <sub>H</sub>     | -                     |

| System reserved                                            | 3                | 03               | -                | -                | 3F0 <sub>H</sub> | 000FFFF0 <sub>H</sub>     | -                     |

| System reserved                                            | 4                | 04               | -                | -                | 3EC <sub>H</sub> | 000FFFEC <sub>H</sub>     | -                     |

| CPU supervisor mode<br>(INT #5 instruction) <sup>[2]</sup> | 5                | 05               | -                | -                | 3E8 <sub>H</sub> | 000FFFE8 <sub>H</sub>     | -                     |

| Memory protection exception <sup>[2]</sup>                 | 6                | 06               | -                | -                | 3E4 <sub>H</sub> | 000FFFE4 <sub>H</sub>     | -                     |

| System reserved                                            | 7                | 07               | -                | -                | 3E0 <sub>H</sub> | 000FFFE0 <sub>H</sub>     | -                     |

| System reserved                                            | 8                | 08               | -                | -                | 3DC <sub>H</sub> | 000FFFDC <sub>H</sub>     | -                     |

| System reserved                                            | 9                | 09               | -                | -                | 3D8 <sub>H</sub> | 000FFFD8 <sub>H</sub>     | -                     |

| System reserved                                            | 10               | 0A               | -                | -                | 3D4 <sub>H</sub> | 000FFFD4 <sub>H</sub>     | -                     |

| System reserved                                            | 11               | 0B               | -                | -                | 3D0 <sub>H</sub> | 000FFFD0 <sub>H</sub>     | -                     |

| System reserved                                            | 12               | 0C               | -                | -                | 3CC <sub>H</sub> | 000FFFCC <sub>H</sub>     | -                     |

| System reserved                                            | 13               | 0D               | -                | -                | 3C8 <sub>H</sub> | 000FFFC8 <sub>H</sub>     | -                     |

| Undefined instruction exception                            | 14               | 0E               | -                | -                | 3C4 <sub>H</sub> | 000FFFC4 <sub>H</sub>     | -                     |

| NMI request                                                | 15               | 0F               | F <sub>H</sub> 1 | fixed            | 3C0 <sub>H</sub> | 000FFFC0 <sub>H</sub>     | -                     |

| External interrupt 0                                       | 16               | 10               | 10000            | 440              | 3BC <sub>H</sub> | 000FFFBC <sub>H</sub>     | 0, 16                 |

| External interrupt 1                                       | 17               | 11               | ICR00            | 440 <sub>H</sub> | 3B8 <sub>H</sub> | 000FFFB8 <sub>H</sub>     | 1, 17                 |

| External interrupt 2                                       | 18               | 12               | 10004            |                  | 3B4 <sub>H</sub> | 000FFFB4 <sub>H</sub>     | 2, 18                 |

| External interrupt 3                                       | 19               | 13               | ICR01            | 441 <sub>H</sub> | 3B0 <sub>H</sub> | 000FFFB0 <sub>H</sub>     | 3, 19                 |

| External interrupt 4                                       | 20               | 14               | 10000            | 440              | 3AC <sub>H</sub> | 000FFFAC <sub>H</sub>     | 20                    |

| External interrupt 5                                       | 21               | 15               | ICR02            | 442 <sub>H</sub> | 3A8 <sub>H</sub> | 000FFFA8 <sub>H</sub>     | 21                    |

| External interrupt 6                                       | 22               | 16               | 10000            | 440              | 3A4 <sub>H</sub> | 000FFFA4 <sub>H</sub>     | 22                    |

| External interrupt 7                                       | 23               | 17               | ICR03            | 443 <sub>H</sub> | 3A0 <sub>H</sub> | 000FFFA0 <sub>H</sub>     | 23                    |

| System reserved                                            | 24               | 18               | 10504            |                  | 39C <sub>H</sub> | 000FFF9C <sub>H</sub>     | -                     |

| System reserved                                            | 25               | 19               | ICR04            | 444 <sub>H</sub> | 398 <sub>H</sub> | 000FFF98 <sub>H</sub>     | -                     |

| System reserved                                            | 26               | 1A               | 10005            |                  | 394 <sub>H</sub> | 000FFF94 <sub>H</sub>     | -                     |

| System reserved                                            | 27               | 1B               | ICR05            | 445 <sub>H</sub> | 390 <sub>H</sub> | 000FFF90 <sub>H</sub>     | -                     |

| External interrupt 12                                      | 28               | 1C               | 10500            |                  | 38C <sub>H</sub> | 000FFF8C <sub>H</sub>     | -                     |

| External interrupt 13                                      | 29               | 1D               | ICR06            | 446 <sub>H</sub> | 388 <sub>H</sub> | 000FFF88 <sub>H</sub>     | -                     |

| System reserved                                            | 30               | 1E               | 1000             |                  | 384 <sub>H</sub> | 000FFF84 <sub>H</sub>     | -                     |

| System reserved                                            | 31               | 1F               | ICR07            | 447 <sub>H</sub> | 380 <sub>H</sub> | 000FFF80 <sub>H</sub>     | -                     |

| Reload timer 0                                             | 32               | 20               | 10500            |                  | 37C <sub>H</sub> | 000FFF7C <sub>H</sub>     | 4, 32                 |

| Reload timer 1                                             | 33               | 21               | ICR08            | 448 <sub>H</sub> | 378 <sub>H</sub> | 000FFF78 <sub>H</sub>     | 5, 33                 |

| Reload timer 2                                             | 34               | 22               | 105              |                  | 374 <sub>H</sub> | 000FFF74 <sub>H</sub>     | 34                    |

| Reload timer 3                                             | 35               | 23               | ICR09            | 449 <sub>H</sub> | 370 <sub>H</sub> | 000FFF70 <sub>H</sub>     | 35                    |

| System reserved                                            | 36               | 24               |                  |                  | 36C <sub>H</sub> | 000FFF6C <sub>H</sub>     | 36                    |

| System reserved                                            | 37               | 25               | ICR10            | 44A <sub>H</sub> | 368 <sub>H</sub> | 000FFF68 <sub>H</sub>     | 37                    |

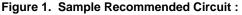

4.

- Corresponding pins: Pin name P29\_0 to P29\_7, P24\_0 to P24\_7, P22\_0 to P22\_3, P20\_0 to P20\_2, P20\_4 to P20\_6, P15\_0 to P15\_3, P17\_0 to P17\_7, P21\_0 to P21\_2, P21\_4 to P21\_6, P14\_0 to P14\_3

- Use within recommended operating conditions.

- Use at DC voltage (current).

- The + B signal is an input signal exceeding V<sub>CC</sub> voltage. The + B signal should always be applied by connecting a limiting resistor between the + B signal and the microcontroller.

- The value of the limiting resistor should be set so that the current input to the microcontroller pin does not exceed rated values at any time regardless of instantaneously or constantly when the + B signal is input.

- Note that when the microcontroller drive current is low, such as in the low power consumption modes, the + B input potential can increase the potential at the VCC pin via a protective diode, possibly affecting other devices.

- Note that if the + B signal is input when the microcontroller is off (not fixed at 0 V), since the power is supplied through the pin, the microcontroller may operate incompletely.

- Note that if the + B signal is input at power-on, since the power is supplied through the pin, the power supply voltage may become the voltage at which a power-on reset does not work.

- Do not leave + B input pins open.

- "Note that analog input/output pins can input the + B signal only at using as a port.

- 5. Maximum output current is defined as the value of the peak current flowing through any one of the corresponding pins.

- 6. Average output current is defined as the value of the average current flowing through any one of the corresponding pins for a 100 ms period.

- 7. Total average output current is defined as the value of the average current flowing through all of the corresponding pins for a 100 ms period.

**WARNING:** Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

# **15.3 DC Characteristics**

$(V_{CC}=3.0 \text{ V to } 3.6 \text{ V}/ 4.5 \text{ V to } 5.5 \text{ V}, \text{ } V_{SS}=\text{AV}_{SS}=0 \text{ V}, \text{ } T_{A}=-40^{\circ}\text{C to } +105^{\circ}\text{C}/-40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Paramotor                                                     | Symbol           | Din Nome                               | Condition                                                                           | Value                 |             |                       | Unit | Remarks |

|---------------------------------------------------------------|------------------|----------------------------------------|-------------------------------------------------------------------------------------|-----------------------|-------------|-----------------------|------|---------|

| Parameter                                                     | Symbol           | Pin Name                               | Condition                                                                           | Min                   | Min Typ Max |                       |      |         |

| "H" level<br>input voltage                                    | V <sub>IHS</sub> | Port pin                               | When CMOS hysteresis input type1 are selected                                       | $0.7 	imes V_{CC}$    | -           | V <sub>CC</sub> + 0.3 | V    |         |

|                                                               | V <sub>IHC</sub> | Port pin                               | When CMOS hysteresis input type2 are selected                                       | $0.8 	imes V_{CC}$    | -           | V <sub>CC</sub> + 0.3 | V    |         |

|                                                               | V <sub>IHA</sub> | Port pin                               | When Automotive inputs are selected                                                 | $0.8 	imes V_{CC}$    | -           | V <sub>CC</sub> + 0.3 | V    |         |

|                                                               | V <sub>IHT</sub> | Port pin                               | When TTL input levels are selected                                                  | 2.0                   | -           | V <sub>CC</sub> + 0.3 | V    |         |

|                                                               | V <sub>IH1</sub> | MD2<br>to<br>MD0                       | CMOS level input                                                                    | $0.7 	imes V_{CC}$    | -           | V <sub>CC</sub> + 0.3 | V    |         |

|                                                               | V <sub>IH2</sub> | MD3, INITX                             | CMOS hysteresis input                                                               | $0.7 	imes V_{CC}$    | -           | V <sub>CC</sub> + 0.3 | V    |         |

| "L" level V <sub>II</sub><br>input<br>voltage V <sub>II</sub> | V <sub>ILS</sub> | Port pin                               | When CMOS hysteresis<br>input type1 are selected                                    | V <sub>SS</sub> - 0.3 | -           | $0.3 	imes V_{CC}$    | V    |         |

|                                                               | V <sub>ILC</sub> | Port pin                               | When CMOS hysteresis<br>input type2 are selected                                    | V <sub>SS</sub> - 0.3 | -           | $0.2 \times V_{CC}$   | V    |         |

|                                                               | V <sub>ILA</sub> | Port pin                               | When Automotive inputs are selected                                                 | V <sub>SS</sub> - 0.3 | -           | $0.5 	imes V_{CC}$    | V    |         |

|                                                               | V <sub>ILT</sub> | Port pin                               | When TTL input levels are selected                                                  | V <sub>SS</sub> - 0.3 | -           | 0.8                   | V    |         |

|                                                               | V <sub>IL1</sub> | MD2<br>to<br>MD0                       | CMOS level input                                                                    | V <sub>SS</sub> – 0.3 | -           | $0.3 \times V_{CC}$   | V    |         |

|                                                               | V <sub>IL2</sub> | MD3, INITX                             | CMOS hysteresis input                                                               | V <sub>SS</sub> - 0.3 | -           | $0.3 	imes V_{CC}$    | V    |         |

| "H" level<br>output<br>voltage                                | V <sub>OH1</sub> | Port pin                               | $V_{CC} = 5.0 V,$<br>$I_{OH} = -2.0 mA/$<br>$V_{CC} = 3.3 V,$<br>$I_{OH} = -1.0 mA$ | V <sub>CC</sub> – 0.5 | -           | -                     | V    | [1]     |

|                                                               | V <sub>OH2</sub> | I <sup>2</sup> C<br>common<br>port pin | $V_{CC} = 5.0 V,$<br>$I_{OH} = -3.0 mA/$<br>$V_{CC} = 3.3 V,$<br>$I_{OH} = -3.0 mA$ | V <sub>CC</sub> – 0.5 | -           | -                     | V    |         |

|                                                               | V <sub>OH3</sub> | Port pin                               | $V_{CC} = 5.0 V,$<br>$I_{OH} = -5.0 mA/$<br>$V_{CC} = 3.3 V,$<br>$I_{OH} = -3.0 mA$ | V <sub>CC</sub> – 0.5 | -           | -                     | V    | [1]     |

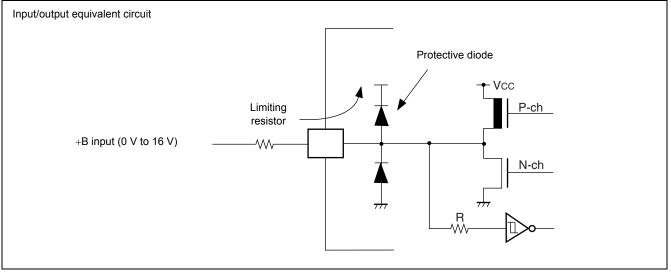

# **15.5** Electrical Characteristics for A/D Converter

$(V_{CC} = 3.0 \text{ V to } 3.6 \text{ V}/ 4.5 \text{ V to } 5.5 \text{ V}, V_{SS} = \text{AV}_{SS} = 0 \text{ V}, \text{ T}_{A} = -40 \text{ }^{\circ}\text{C} \text{ to } + 105 \text{ }^{\circ}\text{C}/-40 \text{ }^{\circ}\text{C} \text{ to } + 85 \text{ }^{\circ}\text{C})$

| Parameter                                         | Symbol           | Pin Name       | Value                     |                           |                           |      |                               |

|---------------------------------------------------|------------------|----------------|---------------------------|---------------------------|---------------------------|------|-------------------------------|

| Parameter                                         |                  |                | Min                       | Тур                       | Max                       | Unit | Remarks                       |

| Resolution                                        | -                | -              | -                         | -                         | 10                        | bit  |                               |

| Total error <sup>[1]</sup>                        | -                | -              | -                         | -                         | ± 3                       | LSB  |                               |

| Linearity error <sup>[1]</sup>                    | -                | -              | _                         | -                         | ± 2.5                     | LSB  |                               |

| Differential linearity error <sup>[1]</sup>       | -                | -              | -                         | -                         | ± 1.9                     | LSB  |                               |

| Zero transition voltage <sup>[1]</sup>            | V <sub>OT</sub>  | AN0 to AN7     | AV <sub>SS</sub> -1.5 LSB | AV <sub>SS</sub> -0.5 LSB | AV <sub>SS</sub> -2.5 LSB | V    |                               |

| Full scale transition voltage <sup>[1]</sup>      | V <sub>FST</sub> | AN0 to AN7     | AVRH-3.5 LSB              | AVRH-1.5 LSB              | AVRH-0.5 LSB              | V    |                               |

| Conversion time                                   | -                | _              | 1 <sup>[2]</sup>          | _                         | _                         | μS   | Using at 5 V                  |

|                                                   |                  |                | 3 [2]                     | _                         | _                         | μS   | Using at 3.3 V                |

| Analog port input current                         | I <sub>AIN</sub> | AN0 to AN7     | -                         | _                         | 10                        | μA   |                               |

| Analog input voltage                              | V <sub>AIN</sub> | AN0 to AN7     | AV <sub>SS</sub>          | _                         | AVRH                      | V    |                               |

| Reference voltage                                 | -                | AVRH           | AV <sub>SS</sub>          | _                         | AV <sub>CC</sub>          | V    |                               |

| Analog power supply current<br>(analog + digital) | Ι <sub>Α</sub>   | AVCC           | _                         | 2.4                       | 4.7                       | mA   | Including<br>reference supply |

| Reference voltage supply current                  | I <sub>R</sub>   | AVRH           | _                         | 0.65                      | 1.0                       | mA   |                               |

| Analog input equivalent capacitance               | Cin              | AN0 to AN7     | _                         | -                         | 8.5                       | pF   |                               |

| Analog input equivalent resistance                | Rin              | Rin AN0 to AN7 | _                         | _                         | 2.6                       | kΩ   | AVcc ? 4.5 V                  |

|                                                   |                  |                | _                         | _                         | 12.1                      | kΩ   | AVcc ? 3.0 V                  |

| Output impedance of analog signal source          | Rext             | -              | _                         | _                         | 4.2                       | kΩ   |                               |

1. Measured in the CPU sleep state

2. Set no shorter than this time period in the peripheral clock and conversion setting register

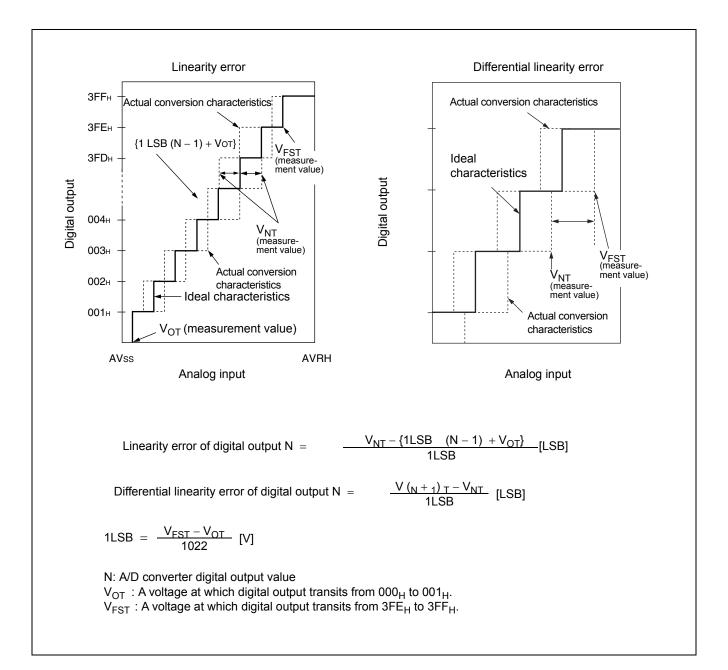

### 17. Package Dimension

| SYMBOL   | DIMENSION |      |      |  |  |

|----------|-----------|------|------|--|--|

| STIVIBOL | MIN.      | NOM. | MAX. |  |  |

| A        |           | —    | 1.70 |  |  |

| A1       | 0.00      |      | 0.20 |  |  |

| b        | 0.27      | 0.32 | 0.37 |  |  |

| С        | 0.09      |      | 0.20 |  |  |

| D        | 14.00 BSC |      |      |  |  |

| D1       | 12.00 BSC |      |      |  |  |

| е        | 0.65 BSC  |      | с 🔰  |  |  |

| E        | 14.00 BSC |      | С    |  |  |

| E1       | 12.00 BSC |      |      |  |  |

| L        | 0.45      | 0.60 | 0.75 |  |  |

| L1       | 0.30      | 0.50 | 0.70 |  |  |

| θ        | 0°        |      | 8°   |  |  |

#### NOTES

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- ▲ DATUM PLANE H IS LOCATED AT THE BOTTOM OF THE MOLD PARTING LINE COINCIDENT WITH WHERE THE LEAD EXITS THE BODY.

- ⚠ DATUMS A-B AND D TO BE DETERMINED AT DATUM PLANE H.

- $\triangle$  TO BE DETERMINED AT SEATING PLANE C.

- ▲ DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25mm PRE SIDE. DIMENSIONS D1 AND E1 INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE H.

- ▲ DETAILS OF PIN 1 IDENTIFIER ARE OPTIONAL BUT MUST BE LOCATED WITHIN THE ZONE INDICATED.

- ☆ REGARDLESS OF THE RELATIVE SIZE OF THE UPPER AND LOWER BODY SECTIONS. DIMENSIONS D1 AND E1 ARE DETERMINED AT THE LARGEST FEATURE OF THE BODY EXCLUSIVE OF MOLD FLASH AND GATE BURRS. BUT INCLUDING ANY MISMATCH BETWEEN THE UPPER AND LOWER SECTIONS OF THE MOLDER BODY.

- ▲ DIMENSION b DOES NOT INCLUDE DAMBER PROTRUSION. THE DAMBAR PROTRUSION (\$) SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED b MAXIMUM BY MORE THAN 0.08mm. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE LEAD FOOT.

- THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10mm AND 0.25mm FROM THE LEAD TIP.

- A1 IS DEFINED AS THE DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY.

002-13881 \*\*

PACKAGE OUTLINE, 64 LEAD LQFP 12.0X12.0X1.7 MM LQG064 REV\*\*

### Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### Products

| Arm <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

PSoC<sup>®</sup> Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

### Cypress Developer Community

Community | Projects | Video | Blogs | Training | Components

Technical Support cypress.com/support

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

© Cypress Semiconductor Corporation, 2007-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and other countries that one to the property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software in binary code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any ibaility arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.