Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, LVD, POR, PWM, WDT           |

| Number of I/O              | 68                                                                            |

| Program Memory Size        | 66KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 80-TQFP                                                                       |

| Supplier Device Package    | 80-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f5013-20e-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name   | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                 |

|------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1       |             | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode;                                                                             |

|            |             |                | CMOS otherwise.                                                                                                                             |

| OSC2       | I/O         | —              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. |

| PGD        | I/O         | ST             | In-Circuit Serial Programming™ data input/output pin.                                                                                       |

| PGC        |             | ST             | In-Circuit Serial Programming clock input pin.                                                                                              |

| RA6-RA7    | I/O         | ST             | PORTA is a bidirectional I/O port.                                                                                                          |

| RA9-RA10   | I/O         | ST             |                                                                                                                                             |

| RA12-RA15  | I/O         | ST             |                                                                                                                                             |

| RB0-RB15   | I/O         | ST             | PORTB is a bidirectional I/O port.                                                                                                          |

| RC1-RC4    | I/O         | ST             | PORTC is a bidirectional I/O port.                                                                                                          |

| RC13-RC15  | I/O         | ST             |                                                                                                                                             |

| RD0-RD15   | I/O         | ST             | PORTD is a bidirectional I/O port.                                                                                                          |

| RF0-RF8    | I/O         | ST             | PORTF is a bidirectional I/O port.                                                                                                          |

| RG0-RG3    | I/O         | ST             | PORTG is a bidirectional I/O port.                                                                                                          |

| RG6-RG9    | I/O         | ST             |                                                                                                                                             |

| RG12-RG15  | I/O         | ST             |                                                                                                                                             |

| SCK1       | I/O         | ST             | Synchronous serial clock input/output for SPI1.                                                                                             |

| SDI1       | I           | ST             | SPI1 Data In.                                                                                                                               |

| SDO1       | 0           | _              | SPI1 Data Out.                                                                                                                              |

| SS1        | l I         | ST             | SPI1 Slave Synchronization.                                                                                                                 |

| SCK2       | I/O         | ST             | Synchronous serial clock input/output for SPI2.                                                                                             |

| SDI2       | I           | ST             | SPI2 Data In.                                                                                                                               |

| SDO2       | 0           | —              | SPI2 Data Out.                                                                                                                              |

| SS2        |             | ST             | SPI2 Slave Synchronization.                                                                                                                 |

| SCL        | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C™.                                                                                |

| SDA        | I/O         | ST             | Synchronous serial data input/output for I <sup>2</sup> C.                                                                                  |

| SOSCO      | 0           | _              | 32 kHz low-power oscillator crystal output.                                                                                                 |

| SOSCI      | I           | ST/CMOS        | 32 kHz low-power oscillator crystal input. ST buffer when                                                                                   |

|            |             |                | configured in RC mode; CMOS otherwise.                                                                                                      |

| T1CK       | I           | ST             | Timer1 external clock input.                                                                                                                |

| T2CK       | I           | ST             | Timer2 external clock input.                                                                                                                |

| ТЗСК       | I           | ST             | Timer3 external clock input.                                                                                                                |

| T4CK       |             | ST             | Timer4 external clock input.                                                                                                                |

| T5CK       | I           | ST             | Timer5 external clock input.                                                                                                                |

| U1RX       | I           | ST             | UART1 Receive.                                                                                                                              |

| U1TX       | 0           | —              | UART1 Transmit.                                                                                                                             |

| U1ARX      | I           | ST             | UART1 Alternate Receive.                                                                                                                    |

| J1ATX      | 0           |                | UART1 Alternate Transmit.                                                                                                                   |

| J2RX       |             | ST             | UART2 Receive.                                                                                                                              |

| J2TX       | 0           | —              | UART2 Transmit.                                                                                                                             |

| VDD        | Р           | —              | Positive supply for logic and I/O pins.                                                                                                     |

| Vss        | Р           | _              | Ground reference for logic and I/O pins.                                                                                                    |

| VREF+      | I           | Analog         | Analog Voltage Reference (High) input.                                                                                                      |

| Vref-      | I           | Analog         | Analog Voltage Reference (Low) input.                                                                                                       |

| Legend: CN | IOS = CM    | Ţ              | ble input or output Analog = Analog input                                                                                                   |

| ST         |             |                | input with CMOS levels O = Output                                                                                                           |

| U.         | = Inp       |                | P = Power                                                                                                                                   |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

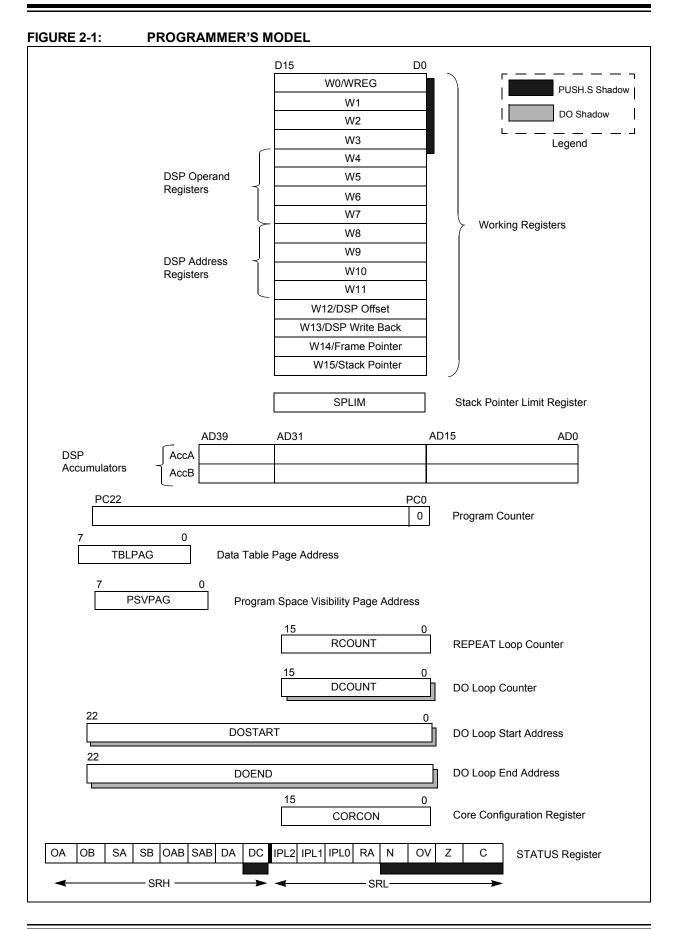

# dsPIC30F5011/5013

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A sign-extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

#### 3.2.5 NEAR DATA SPACE

An 8 Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using MOV instructions, which support memory direct addressing with a 16-bit address field.

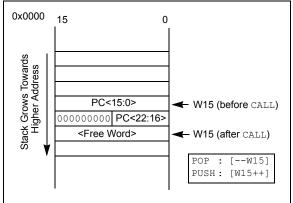

#### 3.2.6 SOFTWARE STACK

The dsPIC DSC devices contain a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes as shown in Figure 3-9. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

**Note:** A PC push during exception processing will concatenate the SRL register to the MSB of the PC prior to the push.

There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word aligned. Whenever an effective address (EA) is generated using W15 as a source or destination pointer, the address thus generated is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a Stack Error Trap will not occur. The Stack Error Trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a Stack Error Trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 3-9: CALL STACK FRAME

#### 3.2.7 DATA RAM PROTECTION FEATURE

The dsPIC30F5011/5013 devices support data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 3-3 for the BSRAM and SSRAM SFRs.

#### 6.4 RTSP Operation

The dsPIC30F Flash program memory is organized into rows and panels. Each row consists of 32 instructions, or 96 bytes. Each panel consists of 128 rows, or 4K x 24 instructions. RTSP allows the user to erase one row (32 instructions) at a time and to program four instructions at one time. RTSP may be used to program multiple program memory panels, but the table pointer must be changed at each panel boundary.

Each panel of program memory contains write latches that hold 32 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the panel write latches. The data to be programmed into the panel is loaded in sequential order into the write latches: instruction 0, instruction 1, etc. The instruction words loaded must always be from a group of 32 boundary.

The basic sequence for RTSP programming is to set up a table pointer, then do a series of TBLWT instructions to load the write latches. Programming is performed by setting the special bits in the NVMCON register. 32 TBLWTL and four TBLWTH instructions are required to load the 32 instructions. If multiple panel programming is required, the table pointer needs to be changed and the next set of multiple write latches written.

All of the table write operations are single-word writes (2 instruction cycles), because only the table latches are written. A programming cycle is required for programming each row.

The Flash Program Memory is readable, writable and erasable during normal operation over the entire VDD range.

#### 6.5 Control Registers

The four SFRs used to read and write the program Flash memory are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

#### 6.5.1 NVMCON REGISTER

The NVMCON register controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

#### 6.5.2 NVMADR REGISTER

The NVMADR register is used to hold the lower two bytes of the effective address. The NVMADR register captures the EA<15:0> of the last table instruction that has been executed and selects the row to write.

#### 6.5.3 NVMADRU REGISTER

The NVMADRU register is used to hold the upper byte of the effective address. The NVMADRU register captures the EA<23:16> of the last table instruction that has been executed.

#### 6.5.4 NVMKEY REGISTER

NVMKEY is a write-only register that is used for write protection. To start a programming or an erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 6.6 "Programming Operations"** for further details.

Note: The user can also directly write to the NVMADR and NVMADRU registers to specify a program memory address for erasing or programming.

#### 9.1 Timer Gate Operation

The 16-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal TCY to increment the respective timer when the gate input signal (T1CK pin) is asserted high. Control bit TGATE (T1CON<6>) must be set to enable this mode. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

When the CPU goes into the Idle mode, the timer will stop incrementing unless TSIDL = 0. If TSIDL = 1, the timer will resume the incrementing sequence upon termination of the CPU Idle mode.

#### 9.2 Timer Prescaler

The input clock (Fosc/4 or external clock) to the 16-bit Timer has a prescale option of 1:1, 1:8, 1:64 and 1:256, selected by control bits TCKPS<1:0> (T1CON<5:4>). The prescaler counter is cleared when any of the following occurs:

- A write to the TMR1 register

- · A write to the T1CON register

- A device Reset, such as a POR and a BOR

However, if the timer is disabled (TON = 0), then the timer prescaler cannot be reset since the prescaler clock is halted.

The TMR1 register is not cleared when the T1CON register is written. It is cleared by writing to the TMR1 register.

#### 9.3 Timer Operation During Sleep Mode

During CPU Sleep mode, the timer will operate if:

- The timer module is enabled (TON = 1) and

- The timer clock source is selected as external (TCS = 1) and

- The TSYNC bit (T1CON<2>) is asserted to a logic '0' which defines the external clock source as asynchronous.

When all three conditions are true, the timer will continue to count up to the Period register and be reset to 0x0000.

When a match between the timer and the Period register occurs, an interrupt can be generated if the respective timer interrupt enable bit is asserted.

#### 9.4 Timer Interrupt

The 16-bit timer has the ability to generate an interrupt on period match. When the timer count matches the Period register, the T1IF bit is asserted and an interrupt will be generated if enabled. The T1IF bit must be cleared in software. The timer interrupt flag, T1IF, is located in the IFS0 Control register in the interrupt controller. When the Gated Time Accumulation mode is enabled, an interrupt will also be generated on the falling edge of the gate signal (at the end of the accumulation cycle).

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

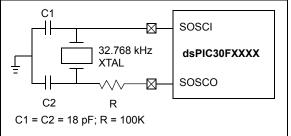

#### 9.5 Real-Time Clock

Timer1, when operating in Real-Time Clock (RTC) mode, provides time of day and event time-stamping capabilities. Key operational features of the RTC are:

- Operation from 32 kHz LP oscillator

- 8-bit prescaler

- Low power

- Real-Time clock interrupts

These operating modes are determined by setting the appropriate bit(s) in the T1CON Control register.

#### FIGURE 9-2: RECOMMENDED COMPONENTS FOR TIMER1 LP OSCILLATOR RTC

#### 9.5.1 RTC OSCILLATOR OPERATION

When TON = 1, TCS = 1 and TGATE = 0, the timer increments on the rising edge of the 32 kHz LP oscillator output signal, up to the value specified in the Period register and is then reset to '0'.

The TSYNC bit must be asserted to a logic '0' (Asynchronous mode) for correct operation.

Enabling LPOSCEN (OSCCON<1>) will disable the normal Timer and Counter modes and enable a timer carry-out wake-up event.

When the CPU enters Sleep mode, the RTC will continue to operate provided the 32 kHz external crystal oscillator is active and the control bits have not been changed. The TSIDL bit should be cleared to '0' in order for RTC to continue operation in Idle mode.

#### 9.5.2 RTC INTERRUPTS

When an interrupt event occurs, the respective interrupt flag, T1IF, is asserted and an interrupt will be generated if enabled. The T1IF bit must be cleared in software. The respective Timer interrupt flag, T1IF, is located in the IFS0 Status register in the interrupt controller.

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

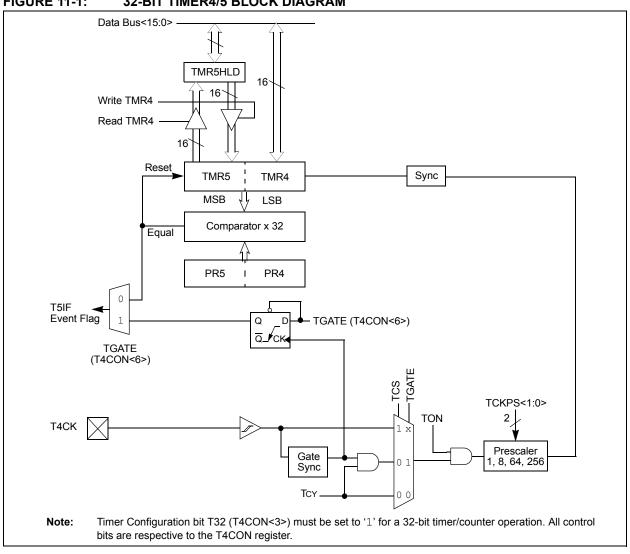

#### 11.0 TIMER4/5 MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU. peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046)

This section describes the second 32-bit General Purpose (GP) Timer module (Timer4/5) and associated operational modes. Figure 11-1 depicts the simplified block diagram of the 32-bit Timer4/5 module. Figure 11-2 and Figure 11-3 show Timer4/5 configured as two independent 16-bit timers, Timer4 and Timer5, respectively.

The Timer4/5 module is similar in operation to the Timer2/3 module. However, there are some differences which are listed as follows:

**FIGURE 11-1:** 32-BIT TIMER4/5 BLOCK DIAGRAM

- The Timer4/5 module does not support the ADC event trigger feature

- · Timer4/5 can not be utilized by other peripheral modules, such as input capture and output compare

The operating modes of the Timer4/5 module are determined by setting the appropriate bit(s) in the 16-bit T4CON and T5CON SFRs.

For 32-bit timer/counter operation, Timer4 is the least significant word and Timer5 is the most significant of the 32-bit timer.

For 32-bit timer operation, T5CON control Note: bits are ignored. Only T4CON control bits are used for setup and control. Timer4 clock and gate inputs are utilized for the 32-bit timer module but an interrupt is generated with the Timer5 interrupt flag (T5IF) and the interrupt is enabled with the Timer5 interrupt enable bit (T5IE).

#### 13.5 Output Compare Operation During CPU Sleep Mode

When the CPU enters Sleep mode, all internal clocks are stopped. Therefore, when the CPU enters the Sleep state, the output compare channel will drive the pin to the active state that was observed prior to entering the CPU Sleep state.

For example, if the pin was high when the CPU entered the Sleep state, the pin will remain high. Likewise, if the pin was low when the CPU entered the Sleep state, the pin will remain low. In either case, the output compare module will resume operation when the device wakes up.

#### 13.6 Output Compare Operation During CPU Idle Mode

When the CPU enters the Idle mode, the output compare module can operate with full functionality.

The output compare channel will operate during the CPU Idle mode if the OCSIDL bit (OCxCON<13>) is at logic '0' and the selected time base (Timer2 or Timer3) is enabled and the TSIDL bit of the selected timer is set to logic '0'.

#### 13.7 Output Compare Interrupts

The output compare channels have the ability to generate an interrupt on a compare match, for whichever Match mode has been selected.

For all modes except the PWM mode, when a compare event occurs, the respective interrupt flag (OCxIF) is asserted and an interrupt will be generated if enabled. The OCxIF bit is located in the corresponding IFS Status register and must be cleared in software. The interrupt is enabled via the respective compare interrupt enable (OCxIE) bit located in the corresponding IEC Control register.

For the PWM mode, when an event occurs, the respective timer interrupt flag (T2IF or T3IF) is asserted and an interrupt will be generated if enabled. The IF bit is located in the IFS0 Status register and must be cleared in software. The interrupt is enabled via the respective timer interrupt enable bit (T2IE or T3IE) located in the IEC0 Control register. The output compare interrupt flag is never set during the PWM mode of operation.

UART1 REGISTER MAP<sup>(1)</sup> TABLE 16-1:

| SFR Name Addr. Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 10 Bit 9 Bit 8 | Bit 8      | Bit 7                         | Bit 6             | Bit 5 Bit 4 Bit 3 Bit 2 | Bit 4             | Bit 3  | Bit 2  | Bit 1  | Bit 0 | Reset State                                                                             |

|---------------------------------------------------|---------|--------|---------|--------|--------|--------|--------------------|------------|-------------------------------|-------------------|-------------------------|-------------------|--------|--------|--------|-------|-----------------------------------------------------------------------------------------|

| U1MODE 020C UARTEN                                | UARTEN  | I      | - NSIDL | I      | 1      |        |                    | I          | WAKE                          | WAKE LPBACK ABAUD | ABAUD                   | Ι                 |        | PDSEL1 | PDSEL0 | STSEL | PDSEL1 PDSEL0 STSEL 0000 0000 0000                                                      |

| U1STA 020E UTXISEL                                | UTXISEL |        | I       |        | UTXBRK | UTXEN  | UTXBF              | TRMT       | <b>URXISEL1</b>               | URXISELO          | ADDEN                   | RIDLE             | PERR   | FERR   | OERR   | URXDA | UTXEN UTXBF TRMT URXISEL1 URXISEL0 ADDEN RIDLE PERR FERR OERR URXDA 0000 0001 0001 0000 |

| U1TXREG 0210                                      | Ι       |        | I       |        | I      | I      | I                  | UTX8       |                               |                   | Tra                     | Transmit Register | gister |        |        |       | nnnn nnnn n000 0000                                                                     |

| U1RXREG 0212                                      | Ι       |        | I       |        | I      | I      | I                  | URX8       |                               |                   | Re                      | Receive Register  | gister |        |        |       | 0000 0000 0000 0000                                                                     |

| U1BRG 0214                                        |         |        |         |        |        |        | Bau                | id Rate G€ | Baud Rate Generator Prescaler | caler             |                         |                   |        |        |        |       | 0000 0000 0000 0000                                                                     |

Legend: Note 1:

u = uninitialized bit; — = unimplemented, read as '0' Refer to the "*dsPlC30F Family Reference Manual*" (DS70046) for descriptions of register bit fields.

# UART2 REGISTER MAP<sup>(1)</sup> **TABLE 16-2**:

| SFR<br>Name        | Addr.  | Addr. Bit 15 Bit 14 Bit 13 Bit 12 Bit 11              | Bit 14    | Bit 13    | Bit 12    |           | Bit 10 | Bit 10 Bit 9 | Bit 8      | Bit 7                                                         | Bit 6        | Bit 5 | Bit 4             | Bit 4 Bit 3 | Bit 2  | Bit 1  | Bit 0 | Reset State                         |     |

|--------------------|--------|-------------------------------------------------------|-----------|-----------|-----------|-----------|--------|--------------|------------|---------------------------------------------------------------|--------------|-------|-------------------|-------------|--------|--------|-------|-------------------------------------|-----|

| <b>U2MODE</b>      | 0216   | J2MODE 0216 UARTEN                                    | Ι         | NSIDL     | Ι         | 1         |        | 1            | Ι          | WAKE                                                          | LPBACK ABAUD | ABAUD |                   |             | PDSEL1 | PDSEL0 | STSEL | PDSEL1 PDSEL0 STSEL 0000 0000 0000  | 000 |

| U2STA 0218 UTXISEL | 0218   | UTXISEL                                               | I         | I         | I         | UTXBRK    | UTXEN  | UTXBF        | TRMT       | UTXEN UTXBF TRMT URXISEL1 URXISEL0 ADDEN RIDLE PERR           | URXISELO     | ADDEN | RIDLE             | PERR        | FERR   | OERR   | URXDA | FERR OERR URXDA 0000 0001 0001 0000 | 000 |

| U2TXREG 021A       | 021A   | 1                                                     | I         | I         | Ι         | 1         |        | I            | UTX8       |                                                               |              | Ţ,    | Transmit Register | egister     |        |        |       | nnnn nnnn n000 0000                 | nnn |

| UZRXREG 021C       | 021C   | Ι                                                     |           | Ι         | -         | 1         |        | I            | URX8       |                                                               |              | Ř     | Receive Register  | sgister     |        |        |       | 0000 0000 0000 0000                 | 000 |

| U2BRG 021E         | 021E   |                                                       |           |           |           |           |        |              | aud Rate ( | Baud Rate Generator Prescaler                                 | escaler      |       |                   |             |        |        |       | 0000 0000 0000 0000                 | 000 |

| Legend:            | un = n | u = uninitialized bit; — = unimplemented, read as '0' | it; — = 1 | unimpleme | snted, re | ad as '0' |        |              |            | Legend: u = uninitialized bit; — = unimplemented, read as '0' |              |       |                   |             |        |        |       |                                     |     |

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. ÷ Note

#### 17.3 Modes of Operation

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Loopback Mode

- Error Recognition Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time which is defined as at least 11 consecutive recessive bits.

#### 17.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module can not be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers.

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

#### 17.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set and TXREQ bit is cleared.

#### 17.3.3 NORMAL OPERATION MODE

Normal operating mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins assume the CAN bus functions. The module transmits and receives CAN bus messages via the CxTX and CxRX pins.

#### 17.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

#### 17.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting the REQOP<2:0> bits to '111'. In this mode, the data which is in the message assembly buffer until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

#### 17.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module connects the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

## dsPIC30F5011/5013

NOTES:

In the Multi-Channel mode, a new data frame transfer will begin one CSCK cycle after the COFS pin is sampled high (see Figure 18-2). The pulse on the COFS pin resets the frame sync generator logic.

In the  $l^2S$  mode, a new data word will be transferred one CSCK cycle after a low-to-high or a high-to-low transition is sampled on the COFS pin. A rising or falling edge on the COFS pin resets the frame sync generator logic. In the AC-Link mode, the tag slot and subsequent data slots for the next frame will be transferred one CSCK cycle after the COFS pin is sampled high.

The COFSG and WS bits must be configured to provide the proper frame length when the module is operating in the Slave mode. Once a valid frame sync pulse has been sampled by the module on the COFS pin, an entire data frame transfer will take place. The module will not respond to further frame sync pulses until the data frame transfer has completed.

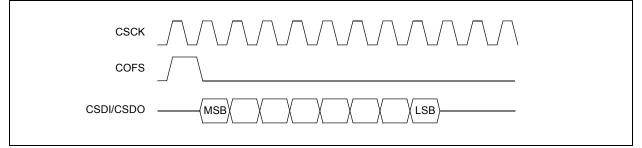

#### FIGURE 18-2: FRAME SYNC TIMING, MULTI-CHANNEL MODE

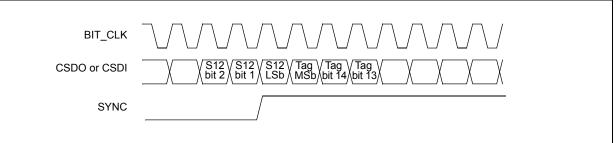

#### FIGURE 18-3: FRAME SYNC TIMING, AC-LINK START-OF-FRAME

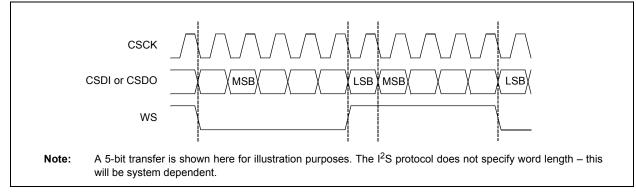

#### FIGURE 18-4: I<sup>2</sup>S INTERFACE FRAME SYNC TIMING

#### 18.3.8 SAMPLE CLOCK EDGE CONTROL BIT

The sample clock edge (CSCKE) control bit determines the sampling edge for the CSCK signal. If the CSCK bit is cleared (default), data will be sampled on the falling edge of the CSCK signal. The AC-Link protocols and most Multi-Channel formats require that data be sampled on the falling edge of the CSCK signal. If the CSCK bit is set, data will be sampled on the rising edge of CSCK. The I<sup>2</sup>S protocol requires that data be sampled on the rising edge of the CSCK signal.

#### 18.3.9 DATA JUSTIFICATION CONTROL BIT

In most applications, the data transfer begins one CSCK cycle after the COFS signal is sampled active. This is the default configuration of the DCI module. An alternate data alignment can be selected by setting the DJST control bit in the DCICON1 SFR. When DJST = 1, data transfers will begin during the same CSCK cycle when the COFS signal is sampled active.

#### 18.3.10 TRANSMIT SLOT ENABLE BITS

The TSCON SFR has control bits that are used to enable up to 16 time slots for transmission. These control bits are the TSE<15:0> bits. The size of each time slot is determined by the WS<3:0> word size selection bits and can vary up to 16 bits.

If a transmit time slot is enabled via one of the TSE bits (TSEx = 1), the contents of the current transmit shadow buffer location will be loaded into the CSDO Shift register and the DCI buffer control unit is incremented to point to the next location.

During an unused transmit time slot, the CSDO pin will drive '0's or will be tri-stated during all disabled time slots depending on the state of the CSDOM bit in the DCICON1 SFR.

The data frame size in bits is determined by the chosen data word size and the number of data word elements in the frame. If the chosen frame size has less than 16 elements, the additional slot enable bits will have no effect.

Each transmit data word is written to the 16-bit transmit buffer as left justified data. If the selected word size is less than 16 bits, then the LSbs of the transmit buffer memory will have no effect on the transmitted data. The user should write '0's to the unused LSbs of each transmit buffer location.

### 18.3.11 RECEIVE SLOT ENABLE BITS

The RSCON SFR contains control bits that are used to enable up to 16 time slots for reception. These control bits are the RSE<15:0> bits. The size of each receive time slot is determined by the WS<3:0> word size selection bits and can vary from 1 to 16 bits.

If a receive time slot is enabled via one of the RSE bits (RSEx = 1), the shift register contents will be written to the current DCI receive shadow buffer location and the buffer control unit will be incremented to point to the next buffer location.

Data is not packed in the receive memory buffer locations if the selected word size is less than 16 bits. Each received slot data word is stored in a separate 16-bit buffer location. Data is always stored in a left justified format in the receive memory buffer.

## 18.3.12 SLOT ENABLE BITS OPERATION WITH FRAME SYNC

The TSE and RSE control bits operate in concert with the DCI frame sync generator. In the Master mode, a COFS signal is generated whenever the frame sync generator is reset. In the Slave mode, the frame sync generator is reset whenever a COFS pulse is received.

The TSE and RSE control bits allow up to 16 consecutive time slots to be enabled for transmit or receive. After the last enabled time slot has been transmitted/ received, the DCI will stop buffering data until the next occurring COFS pulse.

#### 18.3.13 SYNCHRONOUS DATA TRANSFERS

The DCI buffer control unit will be incremented by one word location whenever a given time slot has been enabled for transmission or reception. In most cases, data input and output transfers will be synchronized, which means that a data sample is received for a given channel at the same time a data sample is transmitted. Therefore, the transmit and receive buffers will be filled with equal amounts of data when a DCI interrupt is generated.

In some cases, the amount of data transmitted and received during a data frame may not be equal. As an example, assume a two-word data frame is used. Furthermore, assume that data is only received during slot #0 but is transmitted during slot #0 and slot #1. In this case, the buffer control unit counter would be incremented twice during a data frame but only one receive register location would be filled with data.

### 20.0 SYSTEM INTEGRATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

Several system integration features maximize system reliability, minimize cost through elimination of external components, provide Power-Saving Operating modes and offer code protection:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Programmable Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- Low-Voltage Detect

- Power-Saving Modes (Sleep and Idle)

- Code Protection

- · Unit ID Locations

- In-Circuit Serial Programming (ICSP)

dsPIC30F devices have a Watchdog Timer that is permanently enabled via the Configuration bits or can be software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a delay on power-up only to keep the part in Reset while the power supply stabilizes. With these two timers on chip, most applications need no external Reset circuitry.

Sleep mode is designed to offer a very low-current Power-down mode. The user application can wake-up from Sleep through external Reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit a wide variety of applications. In Idle mode, the clock sources are still active but the CPU is shut-off. The RC oscillator option saves system cost while the LP crystal option saves power.

#### 20.1 Oscillator System Overview

The dsPIC30F oscillator system has the following features:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to boost internal operating frequency

- A clock switching mechanism between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- · Oscillator Control register (OSCCON)

- · Configuration bits for main oscillator selection

Configuration bits determine the clock source upon Power-on Reset (POR) and Brown-out Reset (BOR). Thereafter, the clock source can be changed between permissible clock sources. The OSCCON register controls the clock switching and reflects system clock related status bits.

Table 20-1 provides a summary of the dsPIC30F Oscillator operating modes. A simplified diagram of the oscillator system is shown in Figure 20-1.

## 20.3.1.1 POR with Long Crystal Start-up Time (with FSCM Enabled)

The oscillator start-up circuitry is not linked to the POR circuitry. Some crystal circuits (especially low frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the POR timer and the PWRT have expired:

- · The oscillator circuit has not begun to oscillate

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used)

- The PLL has not achieved a LOCK (if PLL is used)

If the FSCM is enabled and one of the above conditions is true, then a clock failure trap will occur. The device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the trap ISR.

#### 20.3.1.2 Operating without FSCM and PWRT

If the FSCM is disabled and the Power-up Timer (PWRT) is also disabled, then the device will exit rapidly from Reset on power-up. If the clock source is FRC, LPRC, EXTRC or EC, it will be active immediately.

If the FSCM is disabled and the system clock has not started, the device will be in a frozen state at the Reset vector until the system clock starts. From the user's perspective, the device will appear to be in Reset until a system clock is available.

#### 20.3.2 BOR: PROGRAMMABLE BROWN-OUT RESET

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

The BOR module allows selection of one of the following voltage trip points (see Table 23-11):

- 2.6V-2.71V

- 4.1V-4.4V

- 4.58V-4.73V

Note: The BOR voltage trip points indicated here are nominal values provided for design guidance only. Refer to the Electrical Specifications in the specific device data sheet for BOR voltage limit specifications. A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source based on the device Configuration bit values (FOS<1:0> and FPR<3:0>). Furthermore, if an Oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the POR time-out (TPOR) and the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100  $\mu$ s is applied. The total delay in this case is (TPOR + TFSCM).

The BOR Status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit, if enabled, will continue to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

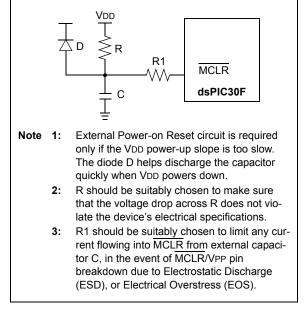

#### FIGURE 20-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

Note: Dedicated supervisory devices, such as the MCP1XX and MCP8XX, may also be used as an external Power-on Reset circuit.

## 21.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The dsPIC30F instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from PIC MCU instruction sets.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word divided into an 8-bit opcode which specifies the instruction type, and one or more operands which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- Control operations

Table 21-1 shows the general symbols used in describing the instructions.

The dsPIC30F instruction set summary in Table 21-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The  ${\tt MAC}$  class of DSP instructions may use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- · The X and Y address space prefetch destinations

- · The accumulator write back destination

The other DSP instructions do not involve any multiplication, and may include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions may use some of the following operands:

- A program memory address

- The mode of the table read and table write instructions

#### 23.1 DC Characteristics

#### TABLE 23-1: OPERATING MIPS VS. VOLTAGE

| Vop Benge | Tomp Dongo     |                  | Max MIPS         |                  |

|-----------|----------------|------------------|------------------|------------------|

| VDD Range | Temp Range     | dsPIC30F501X-30I | dsPIC30F501X-20I | dsPIC30F501X-20E |

| 4.75-5.5V | -40°C to 85°C  | 30               | 20               | _                |

| 4.75-5.5V | -40°C to 125°C | —                | —                | 20               |

| 3.0-3.6V  | -40°C to 85°C  | 15               | 10               | —                |

| 3.0-3.6V  | -40°C to 125°C | —                | —                | 10               |

| 2.5-3.0V  | -40°C to 85°C  | 7.5              | 7.5              | —                |

#### TABLE 23-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                                                                                                                                                              | Symbol         | Min | Тур                                 | Max  | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|-------------------------------------|------|------|

| dsPIC30F501x-30I                                                                                                                                                                                                                                                                                                                    |                |     |                                     |      |      |

| Operating Junction Temperature Range                                                                                                                                                                                                                                                                                                | Т <sub>Ј</sub> | -40 |                                     | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                                                                                                                                 | T <sub>A</sub> | -40 |                                     | +85  | °C   |

| dsPIC30F501x-20I                                                                                                                                                                                                                                                                                                                    |                |     |                                     |      |      |

| Operating Junction Temperature Range                                                                                                                                                                                                                                                                                                | Т <sub>Ј</sub> | -40 |                                     | +150 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                                                                                                                                 | T <sub>A</sub> | -40 |                                     | +85  | °C   |

| dsPIC30F501x-20E                                                                                                                                                                                                                                                                                                                    |                |     |                                     |      |      |

| Operating Junction Temperature Range                                                                                                                                                                                                                                                                                                | Т <sub>Ј</sub> | -40 |                                     | +150 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                                                                                                                                 | T <sub>A</sub> | -40 | _                                   | +125 | °C   |

| $\begin{array}{l} \mbox{Power Dissipation:} \\ \mbox{Internal chip power dissipation:} \\ P_{\rm INT} = V_{\rm DD} \times \left( I_{\rm DD} - \sum I_{\rm OH} \right) \\ \mbox{I/O Pin power dissipation:} \\ P_{\rm I/O} = \sum (\{V_{\rm DD} - V_{\rm OH}\} \times I_{\rm OH}) + \sum (V_{\rm OL} \times I_{\rm OL}) \end{array}$ | P <sub>D</sub> |     | P <sub>INT</sub> + P <sub>I/O</sub> |      | w    |

| Maximum Allowed Power Dissipation                                                                                                                                                                                                                                                                                                   | PDMAX          | (`  | $T_{J}$ - $T_{A}$ ) / $\theta$      | JA   | W    |

#### TABLE 23-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                      | Symbol        | Тур | Мах | Unit | Notes |

|-----------------------------------------------------|---------------|-----|-----|------|-------|

| Package Thermal Resistance, 64-pin TQFP (10x10x1mm) | $\theta_{JA}$ | 39  |     | °C/W | 1     |

| Package Thermal Resistance, 80-pin TQFP (12x12x1mm) | $\theta_{JA}$ | 39  |     | °C/W | 1     |

Note 1: Junction to ambient thermal resistance, Theta-ja ( $\theta_{JA}$ ) numbers are achieved by package simulations.

| DC CHA       | RACTER | ISTICS                                     |         | otherwi            | se stated)<br>erature - | )<br>40°C ≤T | <b>2.5V to 5.5V</b><br>A ≤+85°C for Industrial<br>A ≤+125°C for Extended |

|--------------|--------|--------------------------------------------|---------|--------------------|-------------------------|--------------|--------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                             | Min     | Typ <sup>(1)</sup> | Мах                     | Units        | Conditions                                                               |

|              | VIL    | Input Low Voltage <sup>(2)</sup>           |         |                    |                         |              |                                                                          |

| DI10         |        | I/O pins:<br>with Schmitt Trigger buffer   | Vss     | _                  | 0.2 Vdd                 | V            |                                                                          |

| DI15         |        | MCLR                                       | Vss     | —                  | 0.2 VDD                 | V            |                                                                          |

| DI16         |        | OSC1 (in XT, HS and LP modes)              | Vss     | —                  | 0.2 VDD                 | V            |                                                                          |

| DI17         |        | OSC1 (in RC mode) <sup>(3)</sup>           | Vss     | —                  | 0.3 VDD                 | V            |                                                                          |

| DI18         |        | SDA, SCL                                   | Vss     | —                  | 0.3 VDD                 | V            | SM bus disabled                                                          |

| DI19         |        | SDA, SCL                                   | Vss     | —                  | 0.8                     | V            | SM bus enabled                                                           |

|              | VIH    | Input High Voltage <sup>(2)</sup>          |         |                    |                         |              |                                                                          |

| DI20         |        | I/O pins:<br>with Schmitt Trigger buffer   | 0.8 Vdd | _                  | Vdd                     | V            |                                                                          |

| DI25         |        | MCLR                                       | 0.8 VDD | _                  | Vdd                     | V            |                                                                          |

| DI26         |        | OSC1 (in XT, HS and LP modes)              | 0.7 Vdd | _                  | Vdd                     | V            |                                                                          |

| DI27         |        | OSC1 (in RC mode) <sup>(3)</sup>           | 0.9 Vdd | _                  | Vdd                     | V            |                                                                          |

| DI28         |        | SDA, SCL                                   | 0.7 Vdd | _                  | Vdd                     | V            | SM bus disabled                                                          |

| DI29         |        | SDA, SCL                                   | 2.1     | _                  | Vdd                     | V            | SM bus enabled                                                           |

|              | ICNPU  | CNxx Pull-up Current <sup>(2)</sup>        |         |                    |                         |              |                                                                          |

| DI30         |        |                                            | 50      | 250                | 400                     | μA           | VDD = 5V, VPIN = VSS                                                     |

|              | lı∟    | Input Leakage Current <sup>(2)(4)(5)</sup> |         |                    |                         |              |                                                                          |

| DI50         |        | I/O ports                                  | _       | 0.01               | ±1                      | μA           | Vss ≤VPIN ≤VDD,<br>Pin at high-impedance                                 |

| DI51         |        | Analog input pins                          | _       | 0.50               | _                       | μA           | Vss ≤VPIN ≤VDD,<br>Pin at high-impedance                                 |

| DI55         |        | MCLR                                       | —       | 0.05               | ±5                      | μA           | Vss ⊴Vpin ⊴Vdd                                                           |

| DI56         |        | OSC1                                       | _       | 0.05               | ±5                      | μA           | Vss ≤VPIN ≤VDD, XT, HS<br>and LP Osc mode                                |

#### TABLE 23-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

**3:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the dsPIC30F device be driven with an external clock while in RC mode.

4: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

5: Negative current is defined as current sourced by the pin.

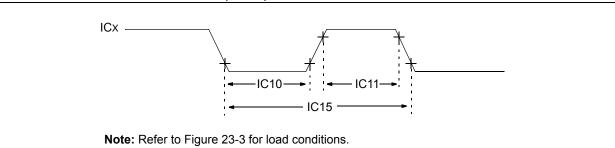

#### FIGURE 23-9: **INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS**

| АС СНА       | RACTERI | STICS               | (unless otherwis      | ing Conditions: 2<br>se stated)<br>rature -40°C ≤TA<br>-40°C ≤TA | ≤+85°C foi | Industria |                                  |

|--------------|---------|---------------------|-----------------------|------------------------------------------------------------------|------------|-----------|----------------------------------|

| Param<br>No. | Symbol  | Characte            | ristic <sup>(1)</sup> | Min                                                              | Мах        | Units     | Conditions                       |

| IC10         | TccL    | ICx Input Low Time  | No Prescaler          | 0.5 Tcy + 20                                                     | _          | ns        |                                  |

|              |         |                     | With Prescaler        | 10                                                               |            | ns        |                                  |

| IC11         | TccH    | ICx Input High Time | No Prescaler          | 0.5 Tcy + 20                                                     |            | ns        |                                  |

|              |         |                     | With Prescaler        | 10                                                               |            | ns        |                                  |

| IC15         | TccP    | ICx Input Period    |                       | (2 Tcy + 40)/N                                                   |            | ns        | N = prescale<br>value (1, 4, 16) |

#### TABLE 23-26: INPUT CAPTURE TIMING REQUIREMENTS

| TABLE 23-35: I <sup>2</sup> C <sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE |

|--------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------|

| АС СНА       | RACTER  | ISTICS           |                           | Standard Operatin<br>(unless otherwise<br>Operating tempera | stated)<br>ture -40 | )°C ≤Ta ≤+ | V to 5.5V<br>85°C for Industrial<br>125°C for Extended |  |

|--------------|---------|------------------|---------------------------|-------------------------------------------------------------|---------------------|------------|--------------------------------------------------------|--|

| Param<br>No. | Symbol  | Charac           | teristic                  | Min <sup>(1)</sup>                                          | Max                 | Units      | Conditions                                             |  |

| IM10         | TLO:SCL | Clock Low Time   | 100 kHz mode              | Tcy / 2 (BRG + 1)                                           |                     | μs         |                                                        |  |

|              |         |                  | 400 kHz mode              | Tcy / 2 (BRG + 1)                                           | _                   | μs         |                                                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy / 2 (BRG + 1)                                           | _                   | μs         |                                                        |  |

| IM11         | THI:SCL | Clock High Time  | 100 kHz mode              | TCY / 2 (BRG + 1)                                           | _                   | μs         |                                                        |  |

|              |         |                  | 400 kHz mode              | TCY / 2 (BRG + 1)                                           | _                   | μs         |                                                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy / 2 (BRG + 1)                                           | _                   | μs         |                                                        |  |

| IM20         | TF:SCL  | SDA and SCL      | 100 kHz mode              | _                                                           | 300                 | ns         | CB is specified to be                                  |  |

|              |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                 | ns         | from 10 to 400 pF                                      |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> |                                                             | 100                 | ns         |                                                        |  |

| IM21         | TR:SCL  | SDA and SCL      | 100 kHz mode              |                                                             | 1000                | ns         | CB is specified to be                                  |  |

|              |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                 | ns         | from 10 to 400 pF                                      |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                           | 300                 | ns         |                                                        |  |

| IM25         | TSU:DAT | Data Input       | 100 kHz mode              | 250                                                         |                     | ns         |                                                        |  |

|              |         | Setup Time       | 400 kHz mode              | 100                                                         |                     | ns         |                                                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                           |                     | ns         |                                                        |  |

| IM26         | THD:DAT | Data Input       | 100 kHz mode              | 0                                                           |                     | ns         |                                                        |  |

|              |         | Hold Time        | 400 kHz mode              | 0                                                           | 0.9                 | μs         |                                                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                           | _                   | ns         |                                                        |  |

| IM30         | TSU:STA | Start Condition  | 100 kHz mode              | Tcy / 2 (BRG + 1)                                           |                     | μs         | Only relevant for<br>repeated Start<br>condition       |  |

|              |         | Setup Time       | 400 kHz mode              | Tcy / 2 (BRG + 1)                                           |                     | μs         |                                                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy / 2 (BRG + 1)                                           |                     | μs         |                                                        |  |

| IM31         | THD:STA | Start Condition  | 100 kHz mode              | Tcy / 2 (BRG + 1)                                           |                     | μs         | After this period the first clock pulse is             |  |

|              |         | Hold Time        | 400 kHz mode              | Tcy / 2 (BRG + 1)                                           |                     | μs         |                                                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy / 2 (BRG + 1)                                           |                     | μs         | generated                                              |  |

| IM33         | Tsu:sto | Stop Condition   | 100 kHz mode              | Tcy / 2 (BRG + 1)                                           |                     | μs         |                                                        |  |

|              |         | Setup Time       | 400 kHz mode              | TCY / 2 (BRG + 1)                                           |                     | μs         |                                                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy / 2 (BRG + 1)                                           |                     | μs         |                                                        |  |

| IM34         | THD:STO | Stop Condition   | 100 kHz mode              | Tcy / 2 (BRG + 1)                                           |                     | ns         |                                                        |  |

|              |         | Hold Time        | 400 kHz mode              | TCY / 2 (BRG + 1)                                           |                     | ns         |                                                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy / 2 (BRG + 1)                                           |                     | ns         | -                                                      |  |

| IM40         | TAA:SCL | Output Valid     | 100 kHz mode              |                                                             | 3500                | ns         |                                                        |  |

|              |         | From Clock       | 400 kHz mode              | _                                                           | 1000                | ns         |                                                        |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                           | _                   | ns         |                                                        |  |

| IM45         | TBF:SDA | Bus Free Time    | 100 kHz mode              | 4.7                                                         |                     | μs         | Time the bus must be                                   |  |

| -            |         |                  | 400 kHz mode              | 1.3                                                         |                     | μs         | free before a new                                      |  |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | _                                                           | _                   | μs         | transmission can start                                 |  |

| IM50         | Св      | Bus Capacitive L |                           | _                                                           | 400                 | pF         |                                                        |  |

Note 1: BRG is the value of the l<sup>2</sup>C Baud Rate Generator. Refer to Section 21. "Inter-Integrated Circuit™ (l<sup>2</sup>C)" in the "dsPIC30F Family Reference Manual" (DS70046).

**2:** Maximum pin capacitance = 10 pF for all I<sup>2</sup>C pins (for 1 MHz mode only).

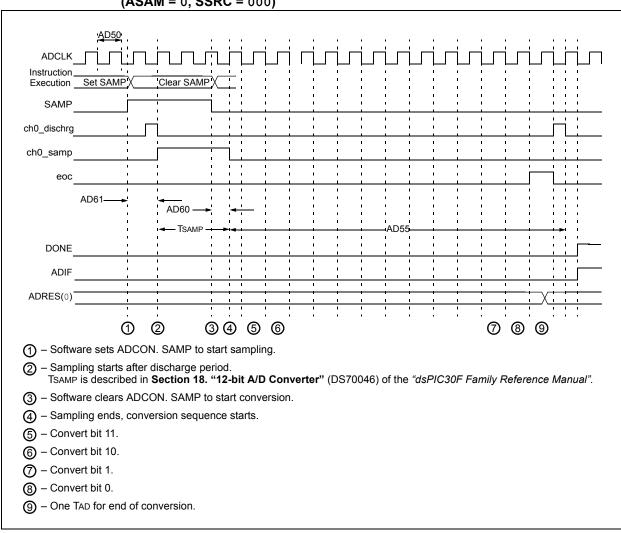

#### FIGURE 23-23: 12-BIT A/D CONVERSION TIMING CHARACTERISTICS (ASAM = 0, SSRC = 000)