Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 30 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, LVD, POR, PWM, WDT            |

| Number of I/O              | 68                                                                             |

| Program Memory Size        | 66KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 1K x 8                                                                         |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f5013t-30i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The SA and SB bits are modified each time data passes through the adder/subtracter but can only be cleared by the user. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation, or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow and thus indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The overflow and saturation status bits can optionally be viewed in the STATUS register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). This allows programmers to check one bit in the STATUS register to determine if either accumulator has overflowed, or one bit to determine if either accumulator has saturated. This would be useful for complex number arithmetic which typically uses both the accumulators.

The device supports three Saturation and Overflow modes:

- Bit 39 Overflow and Saturation:

- When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 (0x7FFFFFFFF), or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. This is referred to as 'super saturation' and provides protection against errone-ous data, or unexpected algorithm problems (e.g., gain calculations).

- Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFFF), or maximally negative 1.31 value (0x008000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user. When this Saturation mode is in effect, the guard bits are not used (so the OA, OB or OAB bits are never set).

- Bit 39 Catastrophic Overflow: The bit 39 overflow Status bit from the adder is used to set the SA or SB bit which remain set until cleared by the user. No saturation operation is performed and the accumulator is allowed to overflow (destroying its sign). If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

## 2.4.2.2 Accumulator 'Write Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator that is not targeted by the instruction into data space memory. The write is performed across the X bus into combined X and Y address space. The following Addressing modes are supported:

- W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction.

- [W13]+=2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

## 2.4.2.3 Round Logic

The round logic is a combinational block which performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16bit, 1.15 data value which is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word (Isw) is simply discarded.

Conventional rounding takes bit 15 of the accumulator, zero-extends it and adds it to the ACCxH word (bits 16 through 31 of the accumulator). If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented. If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged. A consequence of this algorithm is that over a succession of random rounding operations, the value will tend to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. If this is the case, the LSb (bit 16 of the accumulator) of ACCxH is examined. If it is '1', ACCxH is incremented. If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme will remove any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC) or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus (subject to data saturation, see **Section 2.4.2.4** "**Data Space Write Saturation**"). Note that for the MAC class of instructions, the accumulator write back operation will function in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

# 4.4 Interrupt Sequence

All interrupt event flags are sampled in the beginning of each instruction cycle by the IFSx registers. A pending interrupt request (IRQ) is indicated by the flag bit being equal to a '1' in an IFSx register. The IRQ will cause an interrupt to occur if the corresponding bit in the Interrupt Enable (IECx) register is set. For the remainder of the instruction cycle, the priorities of all pending interrupt requests are evaluated.

If there is a pending IRQ with a priority level greater than the current processor priority level in the IPL bits, the processor will be interrupted.

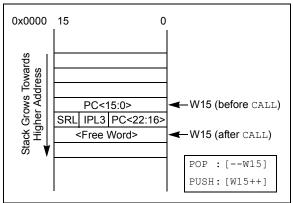

The processor then stacks the current program counter and the low byte of the processor STATUS register (SRL), as shown in Figure 4-2. The low byte of the STATUS register contains the processor priority level at the time prior to the beginning of the interrupt cycle. The processor then loads the priority level for this interrupt into the STATUS register. This action will disable all lower priority interrupts until the completion of the Interrupt Service Routine.

FIGURE 4-2: INTERRUPT STACK FRAME

- Note 1: The user can always lower the priority level by writing a new value into SR. The Interrupt Service Routine must clear the interrupt flag bits in the IFSx register before lowering the processor interrupt priority, in order to avoid recursive interrupts.

- The IPL3 bit (CORCON<3>) is always clear when interrupts are being processed. It is set only during execution of traps.

The RETFIE (return from interrupt) instruction will unstack the program counter and STATUS registers to return the processor to its state prior to the interrupt sequence.

# 4.5 Alternate Vector Table

In program memory, the Interrupt Vector Table (IVT) is followed by the Alternate Interrupt Vector Table (AIVT), as shown in Figure 4-1. Access to the alternate vector table is provided by the ALTIVT bit in the INTCON2 register. If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors. The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

If the AIVT is not required, the program memory allocated to the AIVT may be used for other purposes. AIVT is not a protected section and may be freely programmed by the user.

# 4.6 Fast Context Saving

A context saving option is available using shadow registers. Shadow registers are provided for the DC, N, OV, Z and C bits in SR, and the registers W0 through W3. The shadows are only one level deep. The shadow registers are accessible using the PUSH.S and POP.S instructions only.

When the processor vectors to an interrupt, the PUSH.S instruction can be used to store the current value of the aforementioned registers into their respective shadow registers.

If an ISR of a certain priority uses the PUSH.S and POP.S instructions for fast context saving, then a higher priority ISR should not include the same instructions. Users must save the key registers in software during a lower priority interrupt if the higher priority ISR uses fast context saving.

# 4.7 External Interrupt Requests

The interrupt controller supports up to five external interrupt request signals, INT0-INT4. These inputs are edge sensitive; they require a low-to-high or a high-to-low transition to generate an interrupt request. The INTCON2 register has five bits, INT0EP-INT4EP, that select the polarity of the edge detection circuitry.

# 4.8 Wake-up from Sleep and Idle

The interrupt controller may be used to wake-up the processor from either Sleep or Idle modes, if Sleep or Idle mode is active when the interrupt is generated.

If an enabled interrupt request of sufficient priority is received by the interrupt controller, then the standard interrupt request is presented to the processor. At the same time, the processor will wake-up from Sleep or Idle and begin execution of the Interrupt Service Routine (ISR) needed to process the interrupt request.

# 5.1.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (register offset) field is shared between both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

## 5.1.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the data pointers through register indirect tables.

The 2 source operand prefetch registers must be a member of the set {W8, W9, W10, W11}. For data reads, W8 and W9 will always be directed to the X RAGU and W10 and W11 will always be directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

Note: Register indirect with register offset addressing is only available for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 5.1.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

# 5.2 Modulo Addressing

Modulo addressing is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo addressing can operate in either data or program space (since the data pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for modulo addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can only be configured to operate in one direction, as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers) based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-2 length. As these buffers satisfy the start and end address criteria, they may operate in a Bidirectional mode (i.e., address boundary checks are performed on both the lower and upper address boundaries).

## 6.6 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. A programming operation is nominally 2 msec in duration and the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

### 6.6.1 PROGRAMMING ALGORITHM FOR PROGRAM FLASH

The user can erase or program one row of program Flash memory at a time. The general process is:

- 1. Read one row of program Flash (32 instruction words) and store into data RAM as a data "image".

- 2. Update the data image with the desired new data.

- 3. Erase program Flash row.

- a) Set up NVMCON register for multi-word, program Flash, erase and set WREN bit.

- b) Write address of row to be erased into NVMADRU/NVMDR.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit. This will begin erase cycle.

- f) CPU will stall for the duration of the erase cycle.

- g) The WR bit is cleared when erase cycle ends.

- Write 32 instruction words of data from data RAM "image" into the program Flash write latches.

- 5. Program 32 instruction words into program Flash.

- Set up NVMCON register for multi-word, program Flash, program, and set WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. This will begin program cycle.

- e) CPU will stall for duration of the program cycle.

- f) The WR bit is cleared by the hardware when program cycle ends.

- 6. Repeat steps 1 through 5 as needed to program desired amount of program Flash memory.

# 6.6.2 ERASING A ROW OF PROGRAM MEMORY

Example 6-1 shows a code sequence that can be used to erase a row (32 instructions) of program memory.

# EXAMPLE 6-1: ERASING A ROW OF PROGRAM MEMORY

|   | ; Setup NVMCON  | for erase operation, multi wor      | d | write                                     |

|---|-----------------|-------------------------------------|---|-------------------------------------------|

|   | ; program memor | ry selected, and writes enabled     |   |                                           |

|   | MOV             | #0x4041,W0                          | ; |                                           |

|   | MOV             | W0,NVMCON                           | ; | Init NVMCON SFR                           |

|   | ; Init pointer  | to row to be ERASED                 |   |                                           |

|   | MOV             | <pre>#tblpage(PROG_ADDR),W0</pre>   | ; |                                           |

|   | MOV             | W0,NVMADRU                          | ; | Initialize PM Page Boundary SFR           |

|   | MOV             | <pre>#tbloffset(PROG ADDR),W0</pre> | ; | Intialize in-page EA[15:0] pointer        |

|   | MOV             | W0, NVMADR                          | ; | Initialize NVMADR SFR                     |

|   | DISI            | #5                                  | ; | Block all interrupts with priority <7 for |

|   |                 |                                     | ; | next 5 instructions                       |

|   | MOV             | #0x55,W0                            |   |                                           |

|   | MOV             | WO,NVMKEY                           | ; | Write the 0x55 key                        |

|   | MOV             | #OxAA,W1                            | ; |                                           |

|   | MOV             | W1,NVMKEY                           | ; | Write the OxAA key                        |

|   | BSET            | NVMCON, #WR                         | ; | Start the erase sequence                  |

|   | NOP             |                                     | ; | Insert two NOPs after the erase           |

|   | NOP             |                                     | ; | command is asserted                       |

| 1 |                 |                                     |   |                                           |

# 13.1 Timer2 and Timer3 Selection Mode

Each output compare channel can select between one of two 16-bit timers, Timer2 or Timer3.

The selection of the timers is controlled by the OCTSEL bit (OCxCON<3>). Timer2 is the default timer resource for the output compare module.

## 13.2 Simple Output Compare Match Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 001, 010 or 011, the selected output compare channel is configured for one of three simple Output Compare Match modes:

- Compare forces I/O pin low

- Compare forces I/O pin high

- · Compare toggles I/O pin

The OCxR register is used in these modes. The OCxR register is loaded with a value and is compared to the selected incrementing timer count. When a compare occurs, one of these Compare Match modes occurs. If the counter resets to zero before reaching the value in OCxR, the state of the OCx pin remains unchanged.

# 13.3 Dual Output Compare Match Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 100 or 101, the selected output compare channel is configured for one of two Dual Output Compare modes, which are:

- Single Output Pulse mode

- Continuous Output Pulse mode

## 13.3.1 SINGLE PULSE MODE

For the user to configure the module for the generation of a single output pulse, the following steps are required (assuming timer is off):

- 1. Determine instruction cycle time Tcy.

- Calculate desired pulse width value based on Tcy.

- 3. Calculate time to start pulse from timer start value of 0x0000.

- 4. Write pulse width start and stop times into OCxR and OCxRS Compare registers (x denotes channel 1, 2,...,N).

- 5. Set Timer Period register to value equal to, or greater than value in OCxRS Compare register.

- 6. Set OCM<2:0> = 100.

- 7. Enable timer, TON (TxCON<15>) = 1.

To initiate another single pulse, issue another write to set OCM<2:0> = 100.

## 13.3.2 CONTINUOUS PULSE MODE

For the user to configure the module for the generation of a continuous stream of output pulses, the following steps are required:

- 1. Determine instruction cycle time Tcy.

- 2. Calculate desired pulse value based on Tcy.

- 3. Calculate timer to start pulse width from timer start value of 0x0000.

- 4. Write pulse width start and stop times into OCxR and OCxRS (x denotes channel 1, 2,..., N) Compare registers, respectively.

- 5. Set Timer Period register to value equal to, or greater than value in OCxRS Compare register.

- 6. Set OCM<2:0> = 101.

- 7. Enable timer, TON (TxCON<15>) = 1.

## 13.4 Simple PWM Mode

When control bits OCM<2:0> (OCxCON<2:0>) = 110 or 111, the selected output compare channel is configured for the PWM mode of operation. When configured for the PWM mode of operation, OCxR is the main latch (read-only) and OCxRS is the secondary latch. This enables glitchless PWM transitions.

The user must perform the following steps in order to configure the output compare module for PWM operation:

- 1. Set the PWM period by writing to the appropriate period register.

- 2. Set the PWM duty cycle by writing to the OCxRS register.

- 3. Configure the output compare module for PWM operation.

- 4. Set the TMRx prescale value and enable the Timer, TON (TxCON<15>) = 1.

## 13.4.1 INPUT PIN FAULT PROTECTION FOR PWM

When control bits OCM<2:0> (OCxCON<2:0>) = 111, the selected output compare channel is again configured for the PWM mode of operation with the additional feature of input Fault protection. While in this mode, if a logic '0' is detected on the OCFA/B pin, the respective PWM output pin is placed in the high impedance input state. The OCFLT bit (OCxCON<4>) indicates whether a Fault condition has occurred. This state will be maintained until both of the following events have occurred:

- The external Fault condition has been removed

- The PWM mode has been reenabled by writing to the appropriate control bits

NOTES:

## 15.4.1 10-BIT MODE SLAVE TRANSMISSION

Once a slave is addressed in this fashion with the full 10-bit address (we will refer to this state as "PRIOR\_ADDR\_MATCH"), the master can begin sending data bytes for a slave reception operation.

## 15.4.2 10-BIT MODE SLAVE RECEPTION

Once addressed, the master can generate a Repeated Start, Reset the high byte of the address and set the R\_W bit without generating a Stop bit, thus initiating a slave transmit operation.

# 15.5 Automatic Clock Stretch

In the Slave modes, the module can synchronize buffer reads and write to the master device by clock stretching.

## 15.5.1 TRANSMIT CLOCK STRETCHING

Both 10-bit and 7-bit Transmit modes implement clock stretching by asserting the SCLREL bit after the falling edge of the ninth clock, if the TBF bit is cleared, indicating the buffer is empty.

In Slave Transmit modes, clock stretching is always performed irrespective of the STREN bit.

Clock synchronization takes place following the ninth clock of the transmit sequence. If the device samples an ACK on the falling edge of the ninth clock and if the TBF bit is still clear, then the SCLREL bit is automatically cleared. The SCLREL being cleared to '0' will assert the SCL line low. The user's ISR must set the SCLREL bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the I2CTRN before the master device can initiate another transmit sequence.

- Note 1: If the user loads the contents of I2CTRN, setting the TBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- **2:** The SCLREL bit can be set in software, regardless of the state of the TBF bit.

## 15.5.2 RECEIVE CLOCK STRETCHING

The STREN bit in the I2CCON register can be used to enable clock stretching in Slave Receive mode. When the STREN bit is set, the SCL pin will be held low at the end of each data receive sequence.

## 15.5.3 CLOCK STRETCHING DURING 7-BIT ADDRESSING (STREN = 1)

When the STREN bit is set in Slave Receive mode, the SCL line is held low when the buffer register is full. The method for stretching the SCL output is the same for both 7 and 10-bit Addressing modes.

Clock stretching takes place following the ninth clock of the receive sequence. On the falling edge of the ninth clock at the end of the ACK sequence, if the RBF bit is set, the SCLREL bit is automatically cleared, forcing the SCL output to be held low. The user's ISR must set the SCLREL bit before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the I<sup>2</sup>CRCV before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring.

- Note 1: If the user reads the contents of the I2CRCV, clearing the RBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- 2: The SCLREL bit can be set in software regardless of the state of the RBF bit. The user should be careful to clear the RBF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

## 15.5.4 CLOCK STRETCHING DURING 10-BIT ADDRESSING (STREN = 1)

Clock stretching takes place automatically during the addressing sequence. Because this module has a register for the entire address, it is not necessary for the protocol to wait for the address to be updated.

After the address phase is complete, clock stretching will occur on each data receive or transmit sequence as was described earlier.

# 15.6 Software Controlled Clock Stretching (STREN = 1)

When the STREN bit is '1', the SCLREL bit may be cleared by software to allow software to control the clock stretching. The logic will synchronize writes to the SCLREL bit with the SCL clock. Clearing the SCLREL bit will not assert the SCL output until the module detects a falling edge on the SCL output and SCL is sampled low. If the SCLREL bit is cleared by the user while the SCL line has been sampled low, the SCL output will be asserted (held low). The SCL output will remain low until the SCLREL bit is set, and all other devices on the  $I^2$ C bus have de-asserted SCL. This ensures that a write to the SCLREL bit will not violate the minimum high time requirement for SCL.

If the STREN bit is '0', a software write to the SCLREL bit will be disregarded and have no effect on the SCLREL bit.

# 18.0 DATA CONVERTER INTERFACE (DCI) MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

# 18.1 Module Introduction

The dsPIC30F Data Converter Interface (DCI) module allows simple interfacing of devices, such as audio coder/decoders (codecs), A/D converters and D/A converters. The following interfaces are supported:

- Framed Synchronous Serial Transfer (Single or Multi-Channel)

- Inter-IC Sound (I<sup>2</sup>S) Interface

- AC-Link Compliant mode

The DCI module provides the following general features:

- Programmable word size up to 16 bits

- Support for up to 16 time slots, for a maximum frame size of 256 bits

- Data buffering for up to 4 samples without CPU overhead

# 18.2 Module I/O Pins

There are four I/O pins associated with the module. When enabled, the module controls the data direction of each of the four pins.

# 18.2.1 CSCK PIN

The CSCK pin provides the serial clock for the DCI module. The CSCK pin may be configured as an input or output using the CSCKD control bit in the DCICON2 SFR. When configured as an output, the serial clock is provided by the dsPIC30F. When configured as an input, the serial clock must be provided by an external device.

# 18.2.2 CSDO PIN

The serial data output (CSDO) pin is configured as an output only pin when the module is enabled. The CSDO pin drives the serial bus whenever data is to be transmitted. The CSDO pin is tri-stated or driven to '0' during CSCK periods when data is not transmitted, depending on the state of the CSDOM control bit. This allows other devices to place data on the serial bus during transmission periods not used by the DCI module.

# 18.2.3 CSDI PIN

The serial data input (CSDI) pin is configured as an input only pin when the module is enabled.

## 18.2.3.1 COFS PIN

The codec frame synchronization (COFS) pin is used to synchronize data transfers that occur on the CSDO and CSDI pins. The COFS pin may be configured as an input or an output. The data direction for the COFS pin is determined by the COFSD control bit in the DCICON1 register.

The DCI module accesses the shadow registers while the CPU is in the process of accessing the memory mapped buffer registers.

## 18.2.4 BUFFER DATA ALIGNMENT

Data values are always stored left justified in the buffers since most codec data is represented as a signed 2's complement fractional number. If the received word length is less than 16 bits, the unused LSbs in the receive buffer registers are set to '0' by the module. If the transmitted word length is less than 16 bits, the unused LSbs in the transmit buffer register are ignored by the module. The word length setup is described in subsequent sections of this document.

## 18.2.5 TRANSMIT/RECEIVE SHIFT REGISTER

The DCI module has a 16-bit shift register for shifting serial data in and out of the module. Data is shifted in/ out of the shift register MSb first, since audio PCM data is transmitted in signed 2's complement format.

# 18.2.6 DCI BUFFER CONTROL

The DCI module contains a buffer control unit for transferring data between the shadow buffer memory and the serial shift register. The buffer control unit is a simple 2-bit address counter that points to word locations in the shadow buffer memory. For the receive memory space (high address portion of DCI buffer memory), the address counter is concatenated with a '0' in the MSb location to form a 3-bit address. For the transmit memory space (high portion of DCI buffer memory), the address counter is concatenated with a '1' in the MSb location.

Note: The DCI buffer control unit always accesses the same relative location in the transmit and receive buffers, so only one address counter is provided.

# 20.0 SYSTEM INTEGRATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

Several system integration features maximize system reliability, minimize cost through elimination of external components, provide Power-Saving Operating modes and offer code protection:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Programmable Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- Low-Voltage Detect

- Power-Saving Modes (Sleep and Idle)

- Code Protection

- · Unit ID Locations

- In-Circuit Serial Programming (ICSP)

dsPIC30F devices have a Watchdog Timer that is permanently enabled via the Configuration bits or can be software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a delay on power-up only to keep the part in Reset while the power supply stabilizes. With these two timers on chip, most applications need no external Reset circuitry.

Sleep mode is designed to offer a very low-current Power-down mode. The user application can wake-up from Sleep through external Reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit a wide variety of applications. In Idle mode, the clock sources are still active but the CPU is shut-off. The RC oscillator option saves system cost while the LP crystal option saves power.

## 20.1 Oscillator System Overview

The dsPIC30F oscillator system has the following features:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to boost internal operating frequency

- A clock switching mechanism between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- Oscillator Control register (OSCCON)

- · Configuration bits for main oscillator selection

Configuration bits determine the clock source upon Power-on Reset (POR) and Brown-out Reset (BOR). Thereafter, the clock source can be changed between permissible clock sources. The OSCCON register controls the clock switching and reflects system clock related status bits.

Table 20-1 provides a summary of the dsPIC30F Oscillator operating modes. A simplified diagram of the oscillator system is shown in Figure 20-1.

# 20.4 Watchdog Timer (WDT)

## 20.4.1 WATCHDOG TIMER OPERATION

The primary function of the Watchdog Timer (WDT) is to reset the processor in the event of a software malfunction. The WDT is a free-running timer which runs off an on-chip RC oscillator, requiring no external component. Therefore, the WDT timer will continue to operate even if the main processor clock (e.g., the crystal oscillator) fails.

## 20.4.2 ENABLING AND DISABLING THE WDT

The Watchdog Timer can be "Enabled" or "Disabled" only through a Configuration bit (FWDTEN) in the Configuration register, FWDT.

Setting FWDTEN = 1 enables the Watchdog Timer. The enabling is done when programming the device. By default, after chip erase, FWDTEN bit = 1. Any device programmer capable of programming dsPIC30F devices allows programming of this and other Configuration bits.

If enabled, the WDT will increment until it overflows or "times out". A WDT time-out will force a device Reset (except during Sleep). To prevent a WDT time-out, the user must clear the Watchdog Timer using a CLRWDT instruction.

If a WDT times out during Sleep, the device will wakeup. The WDTO bit in the RCON register will be cleared to indicate a wake-up resulting from a WDT time-out.

Setting FWDTEN = 0 allows user software to enable/ disable the Watchdog Timer via the SWDTEN (RCON<5>) control bit.

## 20.5 Low-Voltage Detect

The Low-Voltage Detect (LVD) module is used to detect when the VDD of the device drops below a threshold value, VLVD, which is determined by the LVDL<3:0> bits (RCON<11:8>) and is thus user programmable. The internal voltage reference circuitry requires a nominal amount of time to stabilize, and the BGST bit (RCON<13>) indicates when the voltage reference has stabilized.

In some devices, the LVD threshold voltage may be applied externally on the LVDIN pin.

The LVD module is enabled by setting the LVDEN bit (RCON<12>).

## 20.6 Power-Saving Modes

There are two power-saving states that can be entered through the execution of a special instruction, PWRSAV; these are Sleep and Idle.

The format of the PWRSAV instruction is as follows:

PWRSAV <parameter>, where 'parameter' defines Idle or Sleep mode.

## 20.6.1 SLEEP MODE

In Sleep mode, the clock to the CPU and peripherals is shutdown. If an on-chip oscillator is being used, it is shutdown.

The Fail-Safe Clock Monitor is not functional during Sleep since there is no clock to monitor. However, LPRC clock remains active if WDT is operational during Sleep.

The brown-out protection circuit and the Low-Voltage Detect circuit, if enabled, will remain functional during Sleep.

The processor wakes up from Sleep if at least one of the following conditions has occurred:

- Any interrupt that is individually enabled and meets the required priority level

- Any Reset (POR, BOR and MCLR)

- A WDT time-out

On waking up from Sleep mode, the processor will restart the same clock that was active prior to entry into Sleep mode. When clock switching is enabled, bits COSC<1:0> will determine the oscillator source that will be used on wake-up. If clock switch is disabled, then there is only one system clock.

Note: If a POR or BOR occurred, the selection of the oscillator is based on the FOS<1:0> and FPR<3:0> Configuration bits.

If the clock source is an oscillator, the clock to the device will be held off until OST times out (indicating a stable oscillator). If PLL is used, the system clock is held off until LOCK = 1 (indicating that the PLL is stable). In either case, TPOR, TLOCK and TPWRT delays are applied.

If EC, FRC, LPRC or EXTRC oscillators are used, then a delay of TPOR (~ 10  $\mu$ s) is applied. This is the smallest delay possible on wake-up from Sleep.

Moreover, if LP oscillator was active during Sleep and LP is the oscillator used on wake-up, then the start-up delay will be equal to TPOR. PWRT delay and OST timer delay are not applied. In order to have the smallest possible start-up delay when waking up from Sleep, one of these faster wake-up options should be selected before entering Sleep.

| TABL               | E 21-2:              | INSTRU    | CTION SET OVERVIE               | W (CONTINUED)                                            |               |                |                          |

|--------------------|----------------------|-----------|---------------------------------|----------------------------------------------------------|---------------|----------------|--------------------------|

| Base<br>Instr<br># | Assembly<br>Mnemonic |           | Assembly Syntax                 | Description                                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

| 9                  | BTG                  | BTG       | f,#bit4                         | Bit Toggle f                                             | 1             | 1              | None                     |

|                    |                      | BTG       | Ws,#bit4                        | Bit Toggle Ws                                            | 1             | 1              | None                     |

| 10                 | BTSC                 | BTSC      | f,#bit4                         | Bit Test f, Skip if Clear                                | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSC      | Ws,#bit4                        | Bit Test Ws, Skip if Clear                               | 1             | 1<br>(2 or 3)  | None                     |

| 11                 | BTSS                 | BTSS      | f,#bit4                         | Bit Test f, Skip if Set                                  | 1             |                | None                     |

|                    |                      | BTSS      | Ws,#bit4                        | Bit Test Ws, Skip if Set                                 | 1             | 1<br>(2 or 3)  | None                     |

| 12                 | BTST                 | BTST      | f,#bit4                         | Bit Test f                                               | 1             | 1              | Z                        |

|                    |                      | BTST.C    | Ws,#bit4                        | Bit Test Ws to C                                         | 1             | 1              | С                        |

|                    |                      | BTST.Z    | Ws,#bit4                        | Bit Test Ws to Z                                         | 1             | 1              | Z                        |

|                    |                      | BTST.C    | Ws,Wb                           | Bit Test Ws <wb> to C</wb>                               | 1             | 1              | С                        |

|                    |                      | BTST.Z    | Ws,Wb                           | Bit Test Ws <wb> to Z</wb>                               | 1             | 1              | Z                        |

| 13                 | BTSTS                | BTSTS     | f,#bit4                         | Bit Test then Set f                                      | 1             | 1              | Z                        |

|                    |                      | BTSTS.C   | Ws,#bit4                        | Bit Test Ws to C, then Set                               | 1             | 1              | С                        |

|                    |                      | BTSTS.Z   | Ws,#bit4                        | Bit Test Ws to Z, then Set                               | 1             | 1              | Z                        |

| 14                 | CALL                 | CALL      | lit23                           | Call subroutine                                          | 2             | 2              | None                     |

|                    |                      | CALL      | Wn                              | Call indirect subroutine                                 | 1             | 2              | None                     |

| 15                 | CLR                  | CLR       | f                               | f = 0x0000                                               | 1             | 1              | None                     |

| 10                 | OLIV                 | CLR       | WREG                            | WREG = 0x0000                                            | 1             | 1              | None                     |

|                    |                      | CLR       | Ws                              | Ws = 0x0000                                              | 1             | 1              | None                     |

|                    |                      | CLR       | Acc,Wx,Wxd,Wy,Wyd,AWB           | Clear Accumulator                                        | 1             | 1              | OA,OB,SA,SB              |

| 16                 | CLRWDT               | CLRWDT    | Acc, VVX, VVXU, VVY, VVYU, AVVD |                                                          | 1             | 1              | WDTO,Sleep               |

| 17                 | COM                  | COM       | f                               | Clear Watchdog Timer<br>$f = \overline{f}$               | 1             | 1              | N,Z                      |

| 17                 | CON                  | COM       |                                 | WREG = $\overline{f}$                                    | 1             | 1              | ,                        |

|                    |                      |           | f,WREG<br>Ws,Wd                 | Wd = Ws                                                  |               | 1              | N,Z                      |

| 40                 | 0.0                  | COM<br>CP | f                               |                                                          | 1             |                | N,Z                      |

| 18                 | CP                   | -         |                                 | Compare f with WREG                                      | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP        | Wb,#lit5                        | Compare Wb with lit5                                     | 1             | 1              | C,DC,N,OV,Z              |

|                    | 0.50                 | CP        | Wb,Ws                           | Compare Wb with Ws (Wb - Ws)                             | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CP0                  | CP0       | f                               | Compare f with 0x0000                                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP0       | Ws                              | Compare Ws with 0x0000                                   | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB       | f                               | Compare f with WREG, with Borrow                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB       | Wb,#lit5                        | Compare Wb with lit5, with Borrow                        | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | СРВ       | Wb,Ws                           | Compare W <u>b</u> with Ws, with Borrow<br>(Wb - Ws - C) | 1             | 1              | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ     | Wb, Wn                          | Compare Wb with Wn, skip if =                            | 1             | 1<br>(2 or 3)  | None                     |

| 22                 | CPSGT                | CPSGT     | Wb, Wn                          | Compare Wb with Wn, skip if >                            | 1             | 1<br>(2 or 3)  | None                     |

| 23                 | CPSLT                | CPSLT     | Wb, Wn                          | Compare Wb with Wn, skip if <                            | skip if < 1   |                | None                     |

| 24                 | CPSNE                | CPSNE     | Wb, Wn                          | Compare Wb with Wn, skip if ≠                            | 1             | 1<br>(2 or 3)  | None                     |

| 25                 | DAW                  | DAW       | Wn                              | Wn = decimal adjust Wn                                   | 1             | 1              | С                        |

| 26                 | DEC                  | DEC       | f                               | f = f -1                                                 | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC       | f,WREG                          | WREG = f -1                                              | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC       | Ws,Wd                           | Wd = Ws - 1                                              | 1             | 1              | C,DC,N,OV,Z              |

| 27                 | DEC2                 | DEC2      | f                               | f = f -2                                                 | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2      | f,WREG                          | WREG = f -2                                              | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2      | Ws,Wd                           | Wd = Ws - 2                                              | 1             | 1              | C,DC,N,OV,Z              |

| 28                 | DISI                 | DISI      | #lit14                          | Disable Interrupts for k instruction cycles              | 1             | 1              | None                     |

TABLE 21-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| DC CHARACTERISTICS |            |                                                                  |      | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |     |       |                                  |  |  |

|--------------------|------------|------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------------------------------|--|--|

| Param<br>No.       | Symbol     | Characteristic                                                   | Min  | Typ <sup>(1)</sup>                                                                                                                                               | Max | Units | Conditions                       |  |  |

| Operatir           | ng Voltage | (2)                                                              |      |                                                                                                                                                                  |     |       |                                  |  |  |

| DC10               | Vdd        | Supply Voltage                                                   | 2.5  | _                                                                                                                                                                | 5.5 | V     | Industrial temperature           |  |  |

| DC11               | Vdd        | Supply Voltage                                                   | 3.0  | —                                                                                                                                                                | 5.5 | V     | Extended temperature             |  |  |

| DC12               | Vdr        | RAM Data Retention Voltage <sup>(3)</sup>                        | 1.75 | _                                                                                                                                                                |     | V     |                                  |  |  |

| DC16               | VPOR       | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal | —    | Vss                                                                                                                                                              | —   | V     |                                  |  |  |

| DC17               | SVDD       | VDD Rise Rate<br>to ensure internal<br>Power-on Reset signal     | 0.05 | —                                                                                                                                                                | —   | V/ms  | 0-5V in 0.1 sec<br>0-3V in 60 ms |  |  |

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

**3:** This is the limit to which VDD can be lowered without losing RAM data.

#### TABLE 23-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACT                             | ERISTICS               |      | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |       |      |                 |  |  |  |

|----------------------------------------|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----------------|--|--|--|

| Parameter<br>No.                       | Typical <sup>(1)</sup> | Мах  | Units                                                                                                                                                            |       | Сог  | nditions        |  |  |  |

| Operating Current (IDD) <sup>(2)</sup> |                        |      |                                                                                                                                                                  |       |      |                 |  |  |  |

| DC30a                                  | 7.3                    | 11   | mA                                                                                                                                                               | 25°C  |      |                 |  |  |  |

| DC30b                                  | 7.5                    | 11.2 | mA                                                                                                                                                               | 85°C  | 3.3V |                 |  |  |  |

| DC30c                                  | 7.6                    | 11.4 | mA                                                                                                                                                               | 125°C |      |                 |  |  |  |

| DC30e                                  | 12.9                   | 19.2 | mA                                                                                                                                                               | 25°C  |      | FRC (~2 MIPS)   |  |  |  |

| DC30f                                  | 12.8                   | 19.1 | mA                                                                                                                                                               | 85°C  | 5V   |                 |  |  |  |

| DC30g                                  | 12.8                   | 19.1 | mA                                                                                                                                                               | 125°C |      |                 |  |  |  |

| DC31a                                  | 1.9                    | 2.8  | mA                                                                                                                                                               | 25°C  |      |                 |  |  |  |

| DC31b                                  | 2.0                    | 3    | mA                                                                                                                                                               | 85°C  | 3.3V |                 |  |  |  |

| DC31c                                  | 2.0                    | 3    | mA                                                                                                                                                               | 125°C |      |                 |  |  |  |

| DC31e                                  | 4.1                    | 6.1  | mA                                                                                                                                                               | 25°C  |      | LPRC (~512 kHz) |  |  |  |

| DC31f                                  | 4.0                    | 6    | mA                                                                                                                                                               | 85°C  | 5V   |                 |  |  |  |

| DC31g                                  | 3.8                    | 5.7  | mA                                                                                                                                                               | 125°C |      |                 |  |  |  |

**Note 1:** Data in "Typical" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature also have an impact on the current consumption. The test conditions for all IDD measurements are as follows: OSC1 driven with external square wave from rail to rail. All I/O pins are configured as Inputs and pulled to VDD. MCLR = VDD, WDT, FSCM, LVD and BOR are disabled. CPU, SRAM, Program Memory and Data Memory are operational. No peripheral modules are operating.

## TABLE 23-17: INTERNAL CLOCK TIMING EXAMPLES

| Clock<br>Oscillator Mode | Fosc<br>(MHz) <sup>(1)</sup> | Τ <b>ϲ</b> Υ<br>(μsec) <sup>(2)</sup> | MIPS <sup>(3)</sup><br>w/o PLL | MIPS <sup>(3)</sup><br>w PLL x4 | MIPS <sup>(3)</sup><br>w PLL x8 | MIPS <sup>(3)</sup><br>w PLL x16 |

|--------------------------|------------------------------|---------------------------------------|--------------------------------|---------------------------------|---------------------------------|----------------------------------|

| EC                       | 0.200                        | 20.0                                  | 0.05                           | —                               | —                               | —                                |

|                          | 4                            | 1.0                                   | 1.0                            | 4.0                             | 8.0                             | 16.0                             |

|                          | 10                           | 0.4                                   | 2.5                            | 10.0                            | 20.0                            | —                                |

|                          | 25                           | 0.16                                  | 6.25                           | —                               | —                               | —                                |

| XT                       | 4                            | 1.0                                   | 1.0                            | 4.0                             | 8.0                             | 16.0                             |

|                          | 10                           | 0.4                                   | 2.5                            | 10.0                            | 20.0                            | —                                |

**Note 1:** Assumption: Oscillator Postscaler is divide by 1.

**2:** Instruction Execution Cycle Time: Tcy = 1 / MIPS.

3: Instruction Execution Frequency: MIPS = (Fosc \* PLLx) / 4 [since there are 4 Q clocks per instruction cycle].

## TABLE 23-18: AC CHARACTERISTICS: INTERNAL FRC ACCURACY

| АС СНА       | AC CHARACTERISTICS      |        | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |                      |       |                   |                |  |  |  |

|--------------|-------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|-------------------|----------------|--|--|--|

| Param<br>No. | Characteristic          | Min    | Тур                                                                                                                                                                                                      | Max                  | Units | Condit            | ions           |  |  |  |

|              | Internal FRC Accuracy @ | FRC Fr | eq. = 7.3                                                                                                                                                                                                | 7 MHz <sup>(1)</sup> |       |                   |                |  |  |  |

| OS63         | FRC                     | _      | _                                                                                                                                                                                                        | ±2.00                | %     | -40°C ≤TA ≤+85°C  | VDD = 3.0-5.5V |  |  |  |

|              |                         | _      | _                                                                                                                                                                                                        | ±5.00                | %     | -40°C ≤Ta ≤+125°C | VDD = 3.0-5.5V |  |  |  |

**Note 1:** Overall FRC variation can be calculated by adding the absolute values of jitter, accuracy and drift percentages.

## TABLE 23-19: AC CHARACTERISTICS: INTERNAL LPRC ACCURACY

| АС СНА       | RACTERISTICS                          | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |     |     |       |                  |  |

|--------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------------------|--|

| Param<br>No. | Characteristic                        | Min                                                                                                                                                              | Тур | Max | Units | Conditions       |  |

|              | LPRC @ Freq. = 512 kHz <sup>(1)</sup> |                                                                                                                                                                  |     |     |       |                  |  |

| OS65A        |                                       | -50                                                                                                                                                              | _   | +50 | %     | VDD = 5.0V, ±10% |  |

| OS65B        |                                       | -60                                                                                                                                                              | —   | +60 | %     | VDD = 3.3V, ±10% |  |

| OS65C        |                                       | -70                                                                                                                                                              |     | +70 | %     | VDD = 2.5V       |  |

**Note 1:** Change of LPRC frequency as VDD changes.

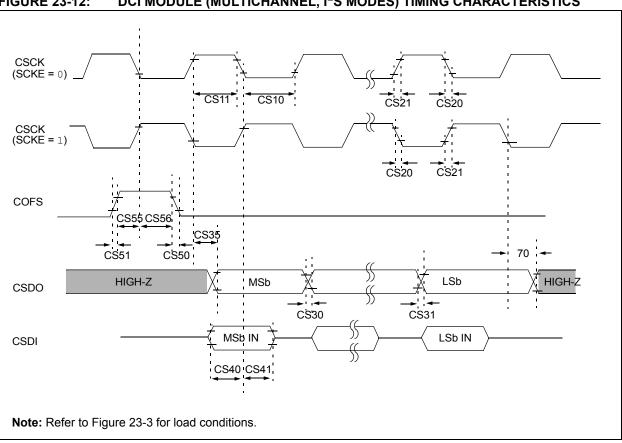

# FIGURE 23-12: DCI MODULE (MULTICHANNEL, I<sup>2</sup>S MODES) TIMING CHARACTERISTICS

|              |        |                                                                                | Standard Operating Conditions: 2.5V to 5.5V   (unless otherwise stated)   Operating temperature -40°C ≤TA ≤+85°C for Industrial   -40°C ≤TA ≤+125°C for Extended |                    |     |       |            |  |  |

|--------------|--------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|--|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>                                                  | Min                                                                                                                                                              | Typ <sup>(2)</sup> | Max | Units | Conditions |  |  |

| CS10         | TCSCKL | CSCK Input Low Time<br>(CSCK pin is an input)                                  | Tcy / 2 +<br>20                                                                                                                                                  | —                  | —   | ns    |            |  |  |

|              |        | CSCK Output Low Time <sup>(3)</sup><br>(CSCK pin is an output)                 | 30                                                                                                                                                               | —                  | —   | ns    |            |  |  |

| CS11         | Тсѕскн | CSCK Input High Time<br>(CSCK pin is an input)                                 | Tcy / 2 +<br>20                                                                                                                                                  | —                  | —   | ns    |            |  |  |

|              |        | CSCK Output High Time <sup>(3)</sup><br>(CSCK pin is an output)                | 30                                                                                                                                                               | —                  | —   | ns    |            |  |  |

| CS20         | TCSCKF | CSCK Output Fall Time <sup>(4)</sup><br>(CSCK pin is an output)                | —                                                                                                                                                                | 10                 | 25  | ns    |            |  |  |

| CS21         | TCSCKR | CSCK Output Rise Time <sup>(4)</sup><br>(CSCK pin is an output)                | —                                                                                                                                                                | 10                 | 25  | ns    |            |  |  |

| CS30         | Tcsdof | CSDO Data Output Fall Time <sup>(4)</sup>                                      | _                                                                                                                                                                | 10                 | 25  | ns    |            |  |  |

| CS31         | Tcsdor | CSDO Data Output Rise Time <sup>(4)</sup>                                      | _                                                                                                                                                                | 10                 | 25  | ns    |            |  |  |

| CS35         | Tdv    | Clock edge to CSDO data valid                                                  | _                                                                                                                                                                | _                  | 10  | ns    |            |  |  |

| CS36         | TDIV   | Clock edge to CSDO tri-stated                                                  | 10                                                                                                                                                               | —                  | 20  | ns    |            |  |  |

| CS40         | TCSDI  | Setup time of CSDI data input to<br>CSCK edge (CSCK pin is input<br>or output) | 20                                                                                                                                                               | —                  | _   | ns    |            |  |  |

| CS41         | THCSDI | Hold time of CSDI data input to<br>CSCK edge (CSCK pin is input<br>or output)  | 20                                                                                                                                                               | —                  | —   | ns    |            |  |  |

| CS50         | Tcofsf | COFS Fall Time<br>(COFS pin is output)                                         | —                                                                                                                                                                | 10                 | 25  | ns    | Note 1     |  |  |

| CS51         | Tcofsr | COFS Rise Time<br>(COFS pin is output)                                         | —                                                                                                                                                                | 10                 | 25  | ns    | Note 1     |  |  |

| CS55         | TSCOFS | Setup time of COFS data input to CSCK edge (COFS pin is input)                 | 20                                                                                                                                                               | —                  |     | ns    |            |  |  |

| CS56         | THCOFS | Hold time of COFS data input to CSCK edge (COFS pin is input)                  | 20                                                                                                                                                               | —                  | _   | ns    |            |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for CSCK is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all DCI pins.

| АС СНА       | RACTERIS                  | TICS                                                | Standard Op<br>(unless othe<br>Operating ter | rwise state        | nditions: 2.5V to 5.5V<br>ed)<br>-40°C ≤TA ≤+85°C for Industrial<br>-40°C ≤TA ≤+125°C for Extended |       |                       |  |

|--------------|---------------------------|-----------------------------------------------------|----------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------|-------|-----------------------|--|

| Param<br>No. | Symbol                    | Characteristic <sup>(1)</sup>                       | Min                                          | Тур <sup>(2)</sup> | Max                                                                                                | Units | Conditions            |  |

| SP70         | TscL                      | SCKx Input Low Time                                 | 30                                           | _                  | —                                                                                                  | ns    |                       |  |

| SP71         | TscH                      | SCKx Input High Time                                | 30                                           | _                  | _                                                                                                  | ns    |                       |  |

| SP72         | TscF                      | SCKx Input Fall Time <sup>(3)</sup>                 | —                                            | 10                 | 25                                                                                                 | ns    |                       |  |

| SP73         | TscR                      | SCKx Input Rise Time <sup>(3)</sup>                 | —                                            | 10                 | 25                                                                                                 | ns    |                       |  |

| SP30         | TdoF                      | SDOx Data Output Fall Time <sup>(3)</sup>           | —                                            | —                  | —                                                                                                  | ns    | See parameter<br>DO32 |  |

| SP31         | TdoR                      | SDOx Data Output Rise Time <sup>(3)</sup>           | —                                            | —                  | —                                                                                                  | ns    | See parameter DO31    |  |

| SP35         | TscH2doV<br>,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge           | —                                            | _                  | 30                                                                                                 | ns    |                       |  |

| SP40         | TdiV2scH,<br>TdiV2scL     | Setup Time of SDIx Data Input to SCKx Edge          | 20                                           | —                  | _                                                                                                  | ns    |                       |  |

| SP41         | TscH2diL,<br>TscL2diL     | Hold Time of SDIx Data Input to SCKx Edge           | 20                                           | —                  | _                                                                                                  | ns    |                       |  |

| SP50         | TssL2scH,<br>TssL2scL     | SSx↓to SCKx↓or SCKx↑ input                          | 120                                          | —                  | —                                                                                                  | ns    |                       |  |

| SP51         | TssH2doZ                  | SS↑ to SDOx Output<br>High-Impedance <sup>(4)</sup> | 10                                           | —                  | 50                                                                                                 | ns    |                       |  |

| SP52         | TscH2ssH<br>TscL2ssH      | SSx↑ after SCKx Edge                                | 1.5 Tcy + 40                                 | —                  | —                                                                                                  | ns    |                       |  |

| SP60         | TssL2doV                  | SDOx Data Output Valid after<br>SSx Edge            | —                                            | —                  | 50                                                                                                 | ns    |                       |  |

## TABLE 23-34: SPI MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCK is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI pins.

| TABLE 23-35: I <sup>2</sup> C <sup>™</sup> BUS DATA TIMING REQUIREMENTS (MASTER MODE |

|--------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------|

|              |         |                               |                           | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |      |       |                                                      |