# E·XFL

Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application charific microcontrollars are analyzared to

#### Details

| Details                 |                                                                              |

|-------------------------|------------------------------------------------------------------------------|

| Product Status          | Last Time Buy                                                                |

| Applications            | RKE, Security Systems                                                        |

| Core Processor          | PIC                                                                          |

| Program Memory Type     | FLASH (1.75kB)                                                               |

| Controller Series       | rfPIC™                                                                       |

| RAM Size                | 64 x 8                                                                       |

| Interface               | -                                                                            |

| Number of I/O           | 6                                                                            |

| Voltage - Supply        | 2V ~ 5.5V                                                                    |

| Operating Temperature   | -40°C ~ 85°C                                                                 |

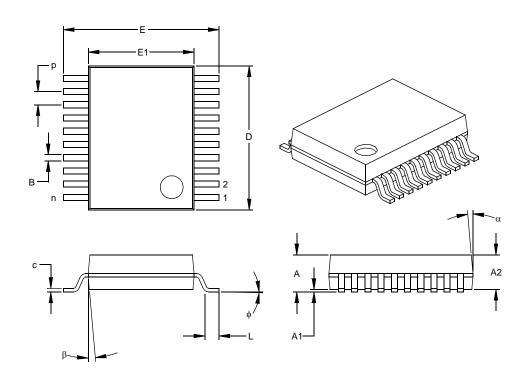

| Mounting Type           | Surface Mount                                                                |

| Package / Case          | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package | 20-SSOP                                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/rfpic12f675kt-i-ss |

|                         |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | PIN          | BUI    | FER    | WEAK    | DESCRIPTION                                                                                      |

|----|--------------|--------|--------|---------|--------------------------------------------------------------------------------------------------|

|    | FIIN         | IN     | OUT    | PULL-UP | DESCRIPTION                                                                                      |

| 1  | Vdd          | Direct | _      | —       | Power Supply                                                                                     |

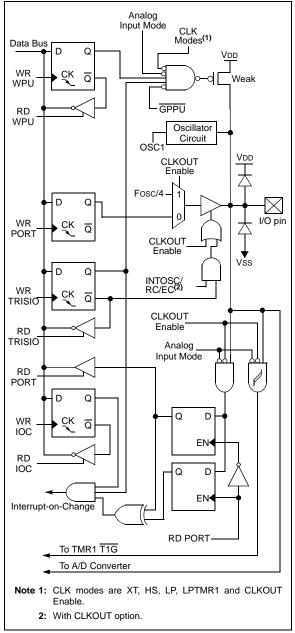

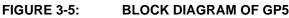

|    | GP5          | TTL    | CMOS   | Prog    | General purpose I/O. Individually controlled interrupt-on-chang<br>Individually enabled pull-up. |

| 2  | T1CKI        | ST     | _      | —       | Timer1 clock                                                                                     |

|    | OSC1         | Xtal   | _      | Bias    | XTAL connection                                                                                  |

|    | CLKIN        | ST     | _      | —       | External RC network or clock input                                                               |

|    | GP4          | TTL    | CMOS   | Prog    | General purpose I/O. Individually controlled interrupt-on-chang<br>Individually enabled pull-up. |

| 3  | T1G          | ST     | _      |         | Timer1 gate                                                                                      |

| 3  | AN3          | Analog |        | —       | A/D Channel 3 input                                                                              |

|    | OSC2         | —      | Xtal   | Bias    | XTAL connection                                                                                  |

|    | CLKOUT       | —      | CMOS   | —       | Tosc/4 reference clock                                                                           |

|    | GP3          | TTL    | _      |         | General purpose input. Individually controlled interrupt-on-<br>change.                          |

| 4  | MCLR         | ST     | _      | No      | Master Clear Reset                                                                               |

|    | Vpp          | HV     | _      | —       | Programming voltage                                                                              |

| 5  | RFXTAL       | Xtal   | Xtal   | Bias    | RF Crystal                                                                                       |

| 6  | RFEN         | TTL    | _      | —       | RF Enable                                                                                        |

| 7  | REFCLK       | —      | CMOS   | _       | Reference Clock/4 Output (on rfPIC12F675K/F)<br>Reference Clock/8 Output (on rfPIC12F675H)       |

| 8  | PS           | Analog | _      | Bias    | Power Select                                                                                     |

| 9  | VDDRF        | Direct | _      | —       | RF Power Supply                                                                                  |

| 10 | VSSRF        | Direct | _      | —       | RF Ground Reference                                                                              |

| 11 | ANT          | —      | OD     | —       | RF power amp output to antenna                                                                   |

| 12 | VSSRF        | Direct | _      | —       | RF Ground Reference                                                                              |

| 13 | LF           | Analog | Analog | —       | Loop Filter                                                                                      |

| 14 | DATAASK      | TTL    | _      | _       | ASK modulation data                                                                              |

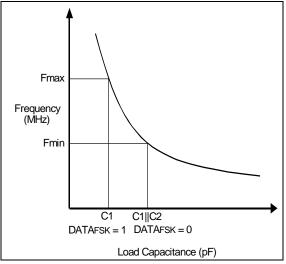

| 15 | DATAFSK      | TTL    | _      | —       | FSK modulation data                                                                              |

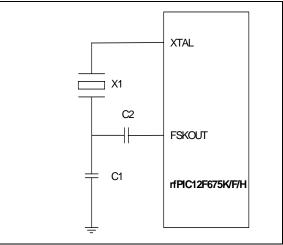

| 16 | FSKOUT       | —      | OD     | —       | FSK output to modulate reference crystal                                                         |

|    | GP2          | ST     | CMOS   | Prog    | General purpose I/O. Individually controlled interrupt-on-chang<br>Individually enabled pull up. |

| 17 | AN2          | Analog | _      | _       | A/D Channel 2 input                                                                              |

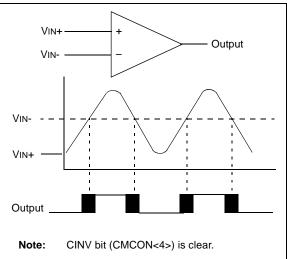

| 17 | COUT         | —      | CMOS   | —       | Comparator output                                                                                |

|    | <b>T0CKI</b> | ST     | —      | —       | External clock for Timer0                                                                        |

|    | INT          | ST     | —      | —       | External interrupt                                                                               |

|    | GP1          | TTL    | CMOS   | Prog    | General purpose I/O. Individually controlled interrupt-on-chang<br>Individually enabled pull-up. |

| 18 | AN1          | Analog | _      | —       | A/D Channel 1 input                                                                              |

| 10 | CIN-         | Analog |        | —       | Comparator input - negative                                                                      |

|    | Vref         | Analog |        | —       | External voltage reference                                                                       |

|    | ICSPCLK      | ST     | _      | —       | Serial programming clock                                                                         |

|    | GP0          | TTL    | CMOS   | Prog    | General purpose I/O. Individually controlled interrupt-on-chang<br>Individually enabled pull-up. |

| 19 | AN0          | Analog |        |         | A/D Channel 0 input                                                                              |

|    | CIN+         | Analog |        | _       | Comparator input - positive                                                                      |

|    | ICSPDAT      | TTL    | CMOS   | —       | Serial Programming Data I/O                                                                      |

| 20 | Vss          | Direct |        | _       | Ground reference                                                                                 |

| Address | Name                  | Bit 7              | Bit 6              | Bit 5          | Bit 4         | Bit 3           | Bit 2          | Bit 1         | Bit 0   | Value on<br>POR, BOD | Page  |

|---------|-----------------------|--------------------|--------------------|----------------|---------------|-----------------|----------------|---------------|---------|----------------------|-------|

| Bank 1  |                       |                    |                    |                |               |                 |                |               |         |                      |       |

| 80h     | INDF <sup>(1)</sup>   | Addressing         | this Location      | uses Conte     | nts of FSR to | Address Dat     | a Memory       |               |         | 0000 0000            | 16,63 |

| 81h     | OPTION_REG            | GPPU               | INTEDG             | TOCS           | TOSE          | PSA             | PS2            | PS1           | PS0     | 1111 1111            | 10,26 |

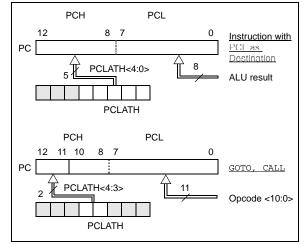

| 82h     | PCL                   | Program Co         | ounter's (PC)      | Least Signifi  | cant Byte     |                 |                |               |         | 0000 0000            | 15    |

| 83h     | STATUS                | IRP <sup>(2)</sup> | RP1 <sup>(2)</sup> | RP0            | TO            | PD              | Z              | DC            | С       | 0001 1xxx            | 9     |

| 84h     | FSR                   | Indirect Data      | a Memory Ac        | dress Pointe   | er            |                 |                | •             | •       | xxxx xxxx            | 16    |

| 85h     | TRISIO                | _                  | _                  | TRISI05        | TRISIO4       | TRISIO3         | TRISIO2        | TRISIO1       | TRISIO0 | 11 1111              | 17    |

| 86h     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | _     |

| 87h     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | _     |

| 88h     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | _     |

| 89h     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | _                    | —     |

| 8Ah     | PCLATH                | _                  | _                  | _              | Write Buffer  | for Upper 5     | bits of Progra | am Counter    |         | 0 0000               | 15    |

| 8Bh     | INTCON                | GIE                | PEIE               | T0IE           | INTE          | GPIE            | T0IF           | INTF          | GPIF    | 0000 0000            | 11    |

| 8Ch     | PIE1                  | EEIE               | ADIE               | _              | _             | CMIE            |                | _             | TMR1IE  | 00 00                | 12    |

| 8Dh     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | —     |

| 8Eh     | PCON                  | -                  | —                  | _              | _             |                 |                | POR           | BOD     | 0x                   | 14    |

| 8Fh     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | —     |

| 90h     | OSCCAL                | CAL5               | CAL4               | CAL3           | CAL2          | CAL1            | CAL0           | _             | —       | 1000 00              | 14    |

| 91h     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | —     |

| 92h     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | —     |

| 93h     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | —     |

| 94h     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | —     |

| 95h     | WPU                   | —                  | —                  | WPU5           | WPU4          | -               | WPU2           | WPU1          | WPU0    | 11 -111              | 18    |

| 96h     | IOC                   | —                  | —                  | IOC5           | IOC4          | IOC3            | IOC2           | IOC1          | IOC0    | 00 0000              | 19    |

| 97h     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | —     |

| 98h     | —                     | Unimpleme          | nted               |                |               |                 |                |               |         | —                    | —     |

| 99h     | VRCON                 | VREN               | —                  | VRR            | —             | VR3             | VR2            | VR1           | VR0     | 0-0- 0000            | 38    |

| 9Ah     | EEDATA                | Data EEPR          | OM Data Reg        | gister         |               |                 |                |               |         | 0000 0000            | 45    |

| 9Bh     | EEADR                 | —                  | Data EEPR          | OM Address     | Register      |                 |                |               |         | -000 0000            | 45    |

| 9Ch     | EECON1                | _                  | _                  | _              | _             | WRERR           | WREN           | WR            | RD      | x000                 | 46    |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROM C           | ontrol Regist      | er 2           |               |                 |                |               |         |                      | 46    |

| 9Eh     | ADRESL                | Least Signif       | icant 2 bits o     | f the Left Shi | fted A/D Res  | ult of 8 bits o | r the Right S  | hifted Result |         | XXXX XXXX            | 40    |

| 9Fh     | ANSEL                 | _                  | ADCS2              | ADCS1          | ADCS0         | ANS3            | ANS2           | ANS1          | ANS0    | -000 1111            | 42,63 |

## TABLE 2-1: SPECIAL FUNCTION REGISTERS SUMMARY (CONTINUED)

Legend: — = unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note 1:** This is not a physical register.

2: These bits are reserved and should always be maintained as '0'.

### 2.2.2.2 OPTION Register

The OPTION register is a readable and writable register, which contains various control bits to configure:

- TMR0/WDT prescaler

- External GP2/INT interrupt

- TMR0

- Weak pull-ups on GPIO

### **REGISTER 2-2:** OPTION\_REG — OPTION REGISTER (ADDRESS: 81h)

|         | R/W-1                                                                                                                                                                                                                                                                                                                                                                     | R/W-1                                                                                                                         | R/W-1         | R/W-1             | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|-------|-------|-------|-------|--|--|--|--|

|         | GPPU                                                                                                                                                                                                                                                                                                                                                                      | INTEDG                                                                                                                        | TOCS          | T0SE              | PSA   | PS2   | PS1   | PS0   |  |  |  |  |

|         | bit 7                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                               |               |                   |       |       |       | bit 0 |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                               |               |                   |       |       |       |       |  |  |  |  |

| bit 7   | <b>GPPU:</b> GPIO Pull-up Enable bit<br>1 = GPIO pull-ups are disabled<br>0 = GPIO pull-ups are enabled by individual port latch values                                                                                                                                                                                                                                   |                                                                                                                               |               |                   |       |       |       |       |  |  |  |  |

| bit 6   | INTEDG: Interrupt Edge Select bit<br>1 = Interrupt on rising edge of GP2/INT pin<br>0 = Interrupt on falling edge of GP2/INT pin                                                                                                                                                                                                                                          |                                                                                                                               |               |                   |       |       |       |       |  |  |  |  |

| bit 5   | 1 = Transit                                                                                                                                                                                                                                                                                                                                                               | <b>TOCS:</b> TMR0 Clock Source Select bit<br>1 = Transition on GP2/T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT) |               |                   |       |       |       |       |  |  |  |  |

| bit 4   | <b>T0SE:</b> TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on GP2/T0CKI pin<br>0 = Increment on low-to-high transition on GP2/T0CKI pin                                                                                                                                                                                                          |                                                                                                                               |               |                   |       |       |       |       |  |  |  |  |

| bit 3   | 1 = Presca                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                               | ned to the V  | VDT<br>IMER0 modu | ıle   |       |       |       |  |  |  |  |

| bit 2-0 | PS2:PS0:                                                                                                                                                                                                                                                                                                                                                                  | Prescaler                                                                                                                     | Rate Select I | oits              |       |       |       |       |  |  |  |  |

|         | l                                                                                                                                                                                                                                                                                                                                                                         | Bit Value                                                                                                                     | TMR0 Rate     | WDT Rate          |       |       |       |       |  |  |  |  |

|         | Dit value         Hikko Kale         WDT Kale           000         1:2         1:1           001         1:4         1:2           010         1:8         1:4           011         1:16         1:8           100         1:32         1:16           101         1:64         1:32           110         1:128         1:64           111         1:256         1:128 |                                                                                                                               |               |                   |       |       |       |       |  |  |  |  |

|         | Legend:                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                               |               |                   |       |       |       |       |  |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT by setting PSA bit to '1' (OPTION<3>). See Section 4.4.

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the interrupt flag bits, as shown in Register 2-5.

- n = Value at POR

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1 — PERIPHERAL INTERRUPT REGISTER 1 (ADDRESS: 0Ch)

| R/W-0                                                                                                                                                   | ) R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                                  | U-0                                                                                                        | R/W-0                                        | U-0                             | U-0            | R/W-0  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------|----------------|--------|--|--|--|--|--|

| EEIF                                                                                                                                                    | ADIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                    | —                                                                                                          | CMIF                                         | —                               | _              | TMR1IF |  |  |  |  |  |

| bit 7                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                      |                                                                                                            |                                              |                                 |                | bit 0  |  |  |  |  |  |

|                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                      |                                                                                                            |                                              |                                 |                |        |  |  |  |  |  |

|                                                                                                                                                         | EPROM Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                      |                                                                                                            |                                              |                                 |                |        |  |  |  |  |  |

|                                                                                                                                                         | write operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                      |                                                                                                            |                                              |                                 |                |        |  |  |  |  |  |

|                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                      | -                                                                                                          | ias not beer                                 | started                         |                |        |  |  |  |  |  |

|                                                                                                                                                         | ADIF: A/D Converter Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                      |                                                                                                            |                                              |                                 |                |        |  |  |  |  |  |

|                                                                                                                                                         | <ul> <li>1 = The A/D conversion is complete (must be cleared in software)</li> <li>0 = The A/D conversion is not complete</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                      |                                                                                                            |                                              |                                 |                |        |  |  |  |  |  |

|                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                      | piero                                                                                                      |                                              |                                 |                |        |  |  |  |  |  |

| -                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                      |                                                                                                            |                                              |                                 |                |        |  |  |  |  |  |

|                                                                                                                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                      |                                                                                                            |                                              | (                               |                |        |  |  |  |  |  |

|                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                    |                                                                                                            | eared in soi                                 | tware)                          |                |        |  |  |  |  |  |

| -                                                                                                                                                       | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                      | igeu                                                                                                       |                                              |                                 |                |        |  |  |  |  |  |

| Unimple                                                                                                                                                 | emented: Rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | d as 0                                                                                                                                                                               |                                                                                                            |                                              |                                 |                |        |  |  |  |  |  |

|                                                                                                                                                         | : TMR1 Overfl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                    | -                                                                                                          |                                              |                                 |                |        |  |  |  |  |  |