#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | TriCore™                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | ASC, CANbus, MLI, MSC, SSC                                                        |

| Peripherals                | DMA, POR, WDT                                                                     |

| Number of I/O              | 81                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | ·                                                                                 |

| RAM Size                   | 76K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.42V ~ 1.58V                                                                     |

| Data Converters            | A/D 36x12b                                                                        |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 176-LQFP                                                                          |

| Supplier Device Package    | PG-LQFP-176-2                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-tc1164-128f80hl-ab |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **General Device Information**

# 2 General Device Information

Chapter 2 provides the general information for the TC1163/TC1164.

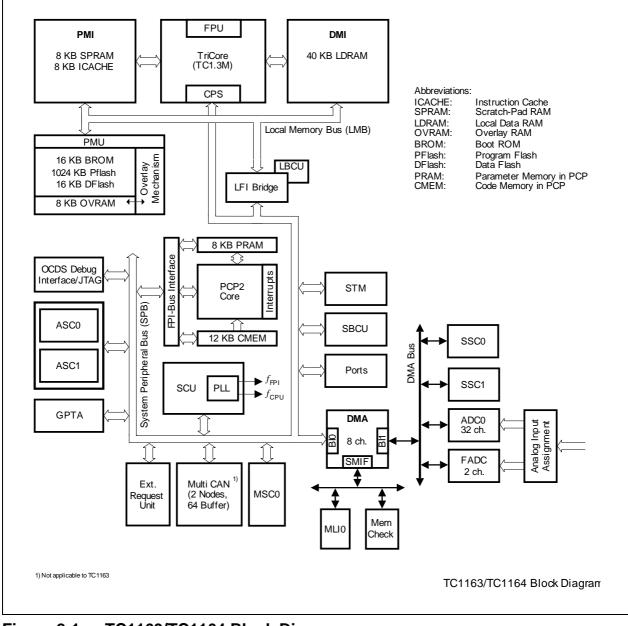

## 2.1 Block Diagram

Figure 2-1 shows the TC1163/TC1164 block diagram.

Figure 2-1 TC1163/TC1164 Block Diagram

### Preliminary

### **General Device Information**

## Table 2-2Pin Definitions and Functions (cont'd)

| Symbol          | Pins       | I/O    | Pad<br>Driver<br>Class | Power<br>Supply  | Functions                                                                                                                                                 |

|-----------------|------------|--------|------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSC0 Ou         | tputs      |        |                        |                  |                                                                                                                                                           |

| FCLP0A<br>FCLN0 | 157<br>156 | 0<br>0 | С                      | V <sub>DDP</sub> | LVDS MSC Clock and Data Outputs <sup>4)</sup><br>MSC0 Differential Driver Clock Output<br>Positive A<br>MSC0 Differential Driver Clock Output<br>Negative |

| SOP0A<br>SON0   | 159<br>158 | 0<br>0 |                        |                  | MSC0 Differential Driver Serial Data Output<br>Positive A<br>MSC0 Differential Driver Serial Data Output<br>Negative                                      |

## Preliminary

### **General Device Information**

| Symbol    | Pins | I/O | Pad<br>Driver<br>Class | Power<br>Supply | Functions                                    |  |  |  |

|-----------|------|-----|------------------------|-----------------|----------------------------------------------|--|--|--|

| Analog In | puts | 1   | 1                      |                 |                                              |  |  |  |

| AN[35:0]  |      | I   | D                      | _               | Analog Input Port                            |  |  |  |

|           |      |     |                        |                 | The Analog Input Port provides altogether 36 |  |  |  |

|           |      |     |                        |                 | analog input lines to ADC0 and FADC.         |  |  |  |

|           |      |     |                        |                 | AN[31:0]: ADC0 analog inputs [31:0]          |  |  |  |

|           |      |     |                        |                 | AN[35:32]: FADC analog differential inputs   |  |  |  |

| AN0       | 67   |     |                        |                 | Analog input 0                               |  |  |  |

| AN1       | 66   |     |                        |                 | Analog input 1                               |  |  |  |

| AN2       | 65   |     |                        |                 | Analog input 2                               |  |  |  |

| AN3       | 64   |     |                        |                 | Analog input 3                               |  |  |  |

| AN4       | 63   |     |                        |                 | Analog input 4                               |  |  |  |

| AN5       | 62   |     |                        |                 | Analog input 5                               |  |  |  |

| AN6       | 61   |     |                        |                 | Analog input 6                               |  |  |  |

| AN7       | 36   |     |                        |                 | Analog input 7                               |  |  |  |

| AN8       | 60   |     |                        |                 | Analog input 8                               |  |  |  |

| AN9       | 59   |     |                        |                 | Analog input 9                               |  |  |  |

| AN10      | 58   |     |                        |                 | Analog input 10                              |  |  |  |

| AN11      | 57   |     |                        |                 | Analog input 11                              |  |  |  |

| AN12      | 56   |     |                        |                 | Analog input 12                              |  |  |  |

| AN13      | 55   |     |                        |                 | Analog input 13                              |  |  |  |

| AN14      | 50   |     |                        |                 | Analog input 14                              |  |  |  |

| AN15      | 49   |     |                        |                 | Analog input 15                              |  |  |  |

| AN16      | 48   |     |                        |                 | Analog input 16                              |  |  |  |

| AN17      | 47   |     |                        |                 | Analog input 17                              |  |  |  |

| AN18      | 46   |     |                        |                 | Analog input 18                              |  |  |  |

| AN19      | 45   |     |                        |                 | Analog input 19                              |  |  |  |

| AN20      | 44   |     |                        |                 | Analog input 20                              |  |  |  |

| AN21      | 43   |     |                        |                 | Analog input 21                              |  |  |  |

| AN22      | 42   |     |                        |                 | Analog input 22                              |  |  |  |

| AN23      | 41   |     |                        |                 | Analog input 23                              |  |  |  |

| AN24      | 40   |     |                        |                 | Analog input 24                              |  |  |  |

| AN25      | 39   |     |                        |                 | Analog input 25                              |  |  |  |

| AN26      | 38   |     |                        |                 | Analog input 26                              |  |  |  |

| AN27      | 37   |     |                        |                 | Analog input 27                              |  |  |  |

| AN28      | 35   |     |                        |                 | Analog input 28                              |  |  |  |

| AN29      | 34   |     |                        |                 | Analog input 29                              |  |  |  |

| AN30      | 33   |     |                        |                 | Analog input 30                              |  |  |  |

#### Table 2-2 Pin Definitions and Functions (cont'd)

## Preliminary

#### **General Device Information**

## Table 2-2Pin Definitions and Functions (cont'd)

| Symbol              | Pins                                            | I/O | Pad<br>Driver<br>Class | Power<br>Supply | Functions                                                                                                     |  |  |  |

|---------------------|-------------------------------------------------|-----|------------------------|-----------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| N.C.                | 21,<br>89                                       | _   | -                      | -               | <b>Not Connected</b><br>These pins are reserved for future extension<br>and must not be connected externally. |  |  |  |

| Power Su            | upplies                                         | 5   |                        |                 | 1                                                                                                             |  |  |  |

| V <sub>DDM</sub>    | 54                                              | _   | _                      | _               | ADC Analog Part Power Supply (3.3 V)                                                                          |  |  |  |

| V <sub>SSM</sub>    | 53                                              | _   | -                      | _               | ADC Analog Part Ground for $V_{\text{DDM}}$                                                                   |  |  |  |

|                     | 24                                              | _   | -                      | _               | FADC Analog Part Power Supply (3.3 V)                                                                         |  |  |  |

| V <sub>SSMF</sub>   | 25                                              | -   | _                      | _               | FADC Analog Part Ground for $V_{\text{DDMF}}$                                                                 |  |  |  |

| $V_{DDAF}$          | 23                                              | -   | -                      | -               | FADC Analog Part Logic Power Supply<br>(1.5 V)                                                                |  |  |  |

| V <sub>SSAF</sub>   | 22                                              | _   | -                      | _               | FADC Analog Part Logic Ground for $V_{\text{DDAF}}$                                                           |  |  |  |

| V <sub>AREF0</sub>  | 52                                              | -   | -                      | _               | ADC Reference Voltage                                                                                         |  |  |  |

| V <sub>AGND0</sub>  | 51                                              | -   | -                      | _               | ADC Reference Ground                                                                                          |  |  |  |

| V <sub>FAREF</sub>  | 26                                              | -   | -                      | -               | FADC Reference Voltage                                                                                        |  |  |  |

|                     | 27                                              | -   | -                      | _               | FADC Reference Ground                                                                                         |  |  |  |

| V <sub>DDOSC</sub>  | 105                                             | -   | -                      | -               | Main Oscillator and PLL Power Supply (1.5 V)                                                                  |  |  |  |

| V <sub>DDOSC3</sub> | 106                                             | -   | -                      | _               | Main Oscillator Power Supply (3.3 V)                                                                          |  |  |  |

| V <sub>ssosc</sub>  | 104                                             | _   | -                      | _               | Main Oscillator and PLL Ground                                                                                |  |  |  |

|                     | 141                                             | _   | <b> </b> -             | -               | Power Supply for Flash (3.3 V)                                                                                |  |  |  |

| V <sub>DD</sub>     | 10,<br>68,<br>84,<br>99,<br>123,<br>153,<br>170 | _   | -                      | -               | Core Power Supply (1.5 V)                                                                                     |  |  |  |

## **Functional Description**

| Instruction Group | Description                                                                                                                      |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DMA primitives    | Efficient DMA channel implementation                                                                                             |  |  |  |  |  |

| Load/Store        | Transfer data between PRAM or FPI memory and the general purpose registers, as well as move or exchange values between registers |  |  |  |  |  |

| Arithmetic        | Add, subtract, compare and complement                                                                                            |  |  |  |  |  |

| Divide/Multiply   | Divide and multiply                                                                                                              |  |  |  |  |  |

| Logical           | And, Or, Exclusive Or, Negate                                                                                                    |  |  |  |  |  |

| Shift             | Shift right or left, rotate right or left, prioritize                                                                            |  |  |  |  |  |

| Bit Manipulation  | Set, clear, insert and test bits                                                                                                 |  |  |  |  |  |

| Flow Control      | Jump conditionally, jump long, exit                                                                                              |  |  |  |  |  |

| Miscellaneous     | No operation, Debug                                                                                                              |  |  |  |  |  |

## **Functional Description**

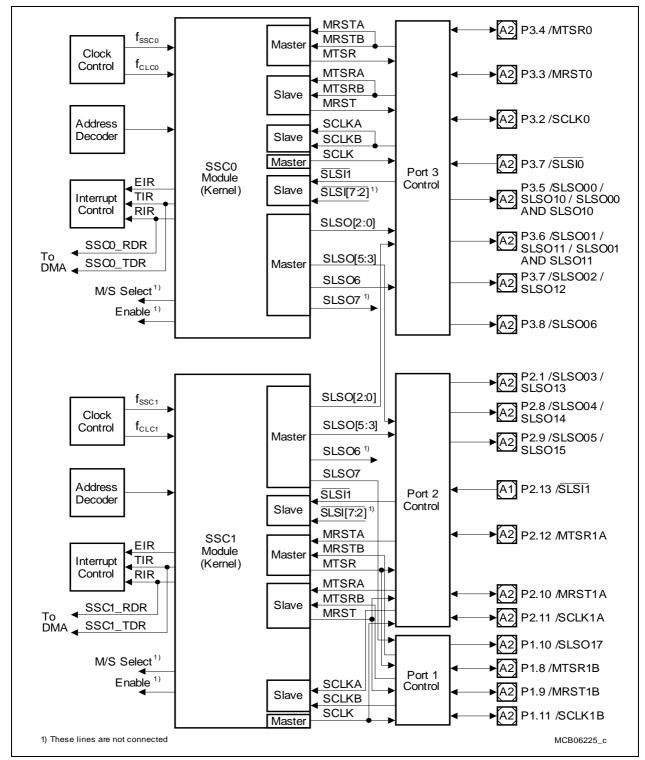

## 3.9 High-Speed Synchronous Serial Interfaces (SSC0 and SSC1)

**Figure 3-5** shows a global view of the functional blocks and interfaces of the two highspeed Synchronous Serial Interfaces, SSC0 and SSC1.

Figure 3-5 Block Diagram of the SSC Interfaces

#### **Functional Description**

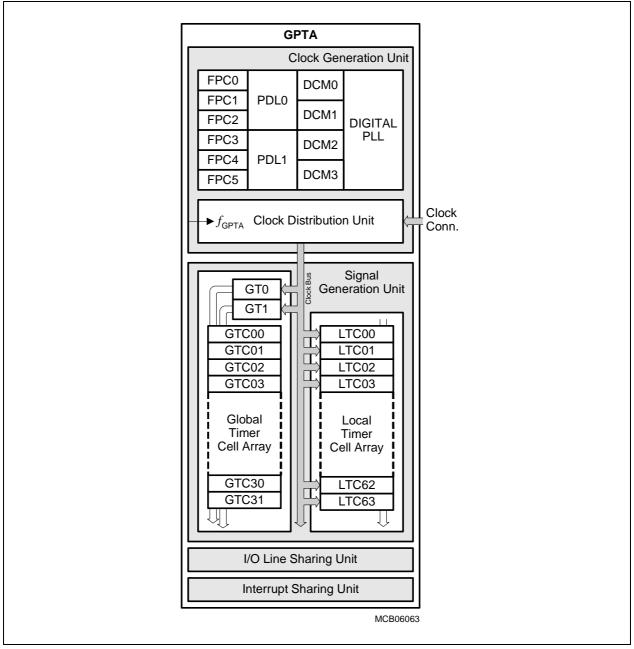

## 3.13 General Purpose Timer Array

The GPTA provides a set of timer, compare, and capture functionalities that can be flexibly combined to form signal measurement and signal generation units. They are optimized for tasks typical of electrical motor control applications, but can also be used to generate simple and complex signal waveforms needed in other industrial applications.

The TC1163/TC1164 contains one General Purpose Timer Array (GPTA0). **Figure 3-10** shows a global view of the GPTA module.

Figure 3-10 Block Diagram of the GPTA Module

## **Functional Description**

- Duty Cycle Measurement (DCM)

- Four independent units

- 0 100% margin and time-out handling

- $f_{\text{GPTA}}$  maximum resolution

- $-f_{\rm GPTA}/2$  maximum input signal frequency

- Digital Phase Locked Loop (PLL)

- One unit

- Arbitrary multiplication factor between 1 and 65535

- $f_{\rm GPTA}$  maximum resolution

- $-f_{GPTA}/2$  maximum input signal frequency

- Clock Distribution Unit (CDU)

- One unit

•

– Provides nine clock output signals:  $f_{\rm GPTA}$ , divided  $f_{\rm GPTA}$  clocks, FPC1/FPC4 outputs, DCM clock, LTC prescaler clock

## **Signal Generation Unit**

- Global Timers (GT)

- Two independent units

- Two operating modes (Free-Running Timer and Reload Timer)

- 24-bit data width

- $-f_{\rm GPTA}$  maximum resolution

- $-f_{\rm GPTA}/2$  maximum input signal frequency

- Global Timer Cell (GTC)

- 32 units related to the Global Timers

- Two operating modes (Capture, Compare and Capture after Compare)

- 24-bit data width

- $f_{\text{GPTA}}$  maximum resolution

- $-f_{\rm GPTA}/2$  maximum input signal frequency

- Local Timer Cell (LTC)

- 64 independent units

- Three basic operating modes (Timer, Capture and Compare) for 63 units

- Special compare modes for one unit

- 16-bit data width

- $-f_{\rm GPTA}$  maximum resolution

- $f_{\rm GPTA}/2$  maximum input signal frequency

### **Interrupt Control Unit**

• 111 interrupt sources, generating up to 38 service requests

#### Preliminary

#### **Functional Description**

#### **OCDS Level 1 Debug Support**

The OCDS Level 1 debug support is mainly assigned for real-time software debugging purposes which have a demand for low-cost standard debugger hardware.

The OCDS Level 1 is based on a JTAG interface that is used by the external debug hardware to communicate with the system. The on-chip Cerberus module controls the interactions between the JTAG interface and the on-chip modules. The external debug hardware may become master of the internal buses, and read or write the on-chip register/memory resources. The Cerberus also makes it possible to define breakpoint and trigger conditions as well as to control user program execution (run/stop, break, single-step).

#### **OCDS Level 2 Debug Support**

The OCDS Level 2 debug support makes it possible to implement program tracing capabilities for enhanced debuggers by extending the OCDS Level 1 debug functionality with an additional 16-bit wide trace output port with trace clock. With the trace extension, the following four trace capabilities are provided (only one of the four trace capabilities can be selected at a time):

- Trace of the CPU program flow

- Trace of the PCP2 program flow

- Trace of the DMA Controller transaction requests

- Trace of the DMA Controller Move Engine status information

#### **Electrical Parameters**

### 4.1.2 Pad Driver and Pad Classes Summary

This section gives an overview on the different pad driver classes and its basic characteristics. More details (mainly DC parameters) are defined in Section 4.2.1.

| Class | Power<br>Supply  | Туре                        | Sub Class                               | Speed<br>Grade | Load   | Leakage <sup>1)</sup>                | Termination                                                |  |  |  |  |  |

|-------|------------------|-----------------------------|-----------------------------------------|----------------|--------|--------------------------------------|------------------------------------------------------------|--|--|--|--|--|

| A     | A 3.3V           | LVTTL<br>I/O,               | A1<br>(e.g. GPIO)                       | 6 MHz          | 100 pF | 500 nA                               | No                                                         |  |  |  |  |  |

|       | LVTTL<br>outputs | A2<br>(e.g. serial<br>I/Os) | 40<br>MHz                               | 50 pF          | 6 μΑ   | Series<br>termination<br>recommended |                                                            |  |  |  |  |  |

|       |                  |                             | <b>A3</b><br>(e.g. BRKIN,<br>BRKOUT)    | 80<br>MHz/     | 50 pF  | 6 μΑ                                 | Series<br>termination<br>recommended<br>(for $f > 25$ MHz) |  |  |  |  |  |

|       |                  |                             | A4<br>(e.g. Trace<br>Clock)             | 80<br>MHz      | 25 pF  | 6 μΑ                                 | Series<br>termination<br>recommended                       |  |  |  |  |  |

| С     | 3.3V             | LVDS                        | -                                       | 50<br>MHz      |        | _                                    | Parallel termination <sup>2)</sup> , 100 $\Omega \pm 10\%$ |  |  |  |  |  |

| D     | -                | Analog ir                   | Analog inputs, reference voltage inputs |                |        |                                      |                                                            |  |  |  |  |  |

1) Values are for  $T_{\text{Jmax}} = 125 \text{ °C}.$

2) In applications where the LVDS pins are not used (disabled), these pins must be either left unconnected, or properly terminated with the differential parallel termination of  $100\Omega \pm 10\%$ .

#### **Electrical Parameters**

| Table 4-4 | Pin Groups for Overload/Short-Circuit Current Sum Parameter                               |

|-----------|-------------------------------------------------------------------------------------------|

| Group     | Pins                                                                                      |

| 1         | TRCLK, P5.[7:0], P0.[7:6], P0.[15:14]                                                     |

| 2         | P0.[13:12], P0.[5:4], P2.[13:8], SOP0A, SON0, FCLP0A, FCLN0                               |

| 3         | P0.[11:8], P0.[3:0], P3.[13:11]                                                           |

| 4         | P3[10:0], P3.[15:14]                                                                      |

| 5         | HDRST, PORST, NMI, TESTMODE, BRKIN, BRKOUT, BYPASS, TCK,<br>TRST, TDO, TMS, TDI, P1.[7:4] |

| 6         | P1.[3:0], P1.[11:8], P4.[3:0]                                                             |

| 7         | P2.[7:0], P1.[14:12]                                                                      |

| 8         | P5.[15:8]                                                                                 |

#### **Electrical Parameters**

#### 4.2 DC Parameters

The electrical characteristics of the DC Parameters are detailed in this section.

#### 4.2.1 Input/Output Pins

Table 4-5 provides the characteristics of the input/output pins of the TC1163/TC1164.

| Table 4-5 | Input/Output DC-Characteristics | (Operating Conditions apply) |

|-----------|---------------------------------|------------------------------|

|-----------|---------------------------------|------------------------------|

| Parameter                                      | Symbol               |        | Limi                         | t Values                                 | Unit | Test Conditions                                                    |  |

|------------------------------------------------|----------------------|--------|------------------------------|------------------------------------------|------|--------------------------------------------------------------------|--|

|                                                |                      |        | Min. Max.                    |                                          |      |                                                                    |  |

| General Paramete                               | ers                  |        |                              |                                          |      |                                                                    |  |

| Pull-up current <sup>1)</sup>                  | I <sub>PUH</sub>     | CC     | 10                           | 100                                      | μA   | V <sub>IN</sub> < V <sub>IHAmin</sub> ;<br>class A1/A2/Input pads. |  |

|                                                |                      |        | 20                           | 200                                      | μA   | V <sub>IN</sub> < V <sub>IHAmin</sub> ;<br>class A3/A4 pads.       |  |

| Pull-down<br>current <sup>1)</sup>             | $ I_{PDL} $          | CC     | 10                           | 150                                      | μA   | V <sub>IN</sub> > V <sub>ILAmax</sub> ;<br>class A1/A2/Input pads. |  |

|                                                |                      |        | 20                           | 200                                      | μA   | $V_{\rm IN} > V_{\rm ILAmax};$<br>class A3/A4 pads.                |  |

| Pin capacitance <sup>1)</sup><br>(Digital I/O) | C <sub>IO</sub>      | CC     | -                            | 10                                       | pF   | f = 1  MHz<br>$T_A = 25 \text{ °C}$                                |  |

| Input only Pads (                              | $V_{\text{DDP}} = 3$ | .13 to | 5 3.47 V                     | = 3.3V ±5%                               | )    |                                                                    |  |

| Input low voltage class A1/A2 pins             | V <sub>ILA</sub>     | SR     | -0.3                         | $0.34 	imes V_{	extsf{DDP}}$             | V    | _                                                                  |  |

| Input high voltage class A1/A2 pins            | V <sub>IHA</sub>     | SR     | $0.64 \times V_{\text{DDP}}$ | V <sub>DDP</sub> +<br>0.3 or<br>max. 3.6 | V    | Whatever is lower                                                  |  |

| Ratio $V_{\rm IL}/V_{\rm IH}$                  |                      | CC     | 0.53                         | _                                        | -    | -                                                                  |  |

| Input low voltage class A3 pins                | V <sub>ILA3</sub>    | SR     | -                            | 0.8                                      | V    | -                                                                  |  |

| Input high voltage class A3 pins               | V <sub>IHA3</sub>    | SR     | 2.0                          | -                                        | V    | -                                                                  |  |

| Input hysteresis                               | HYSA                 | CC     | $0.1 	imes V_{ m DDP}$       | -                                        | V    | 2)5)                                                               |  |

| Input leakage<br>current                       | I <sub>OZI</sub>     | CC     | -                            | ±3000                                    | nA   | $((V_{DDP}/2)-1) < V_{IN} < ((V_{DDP}/2)+1)$                       |  |

|                                                |                      |        |                              | ±6000                                    |      | otherwise <sup>3)</sup>                                            |  |

#### **Electrical Parameters**

## 4.2.2 Analog to Digital Converter (ADC0)

Table 4-6 provides the characteristics of the ADC module in the TC1163/TC1164.

| Parameter                                          | Symbol                          |    | Lim                                | it Valu     | es                                              | Unit                    | Test Conditions /                                        |  |

|----------------------------------------------------|---------------------------------|----|------------------------------------|-------------|-------------------------------------------------|-------------------------|----------------------------------------------------------|--|

|                                                    |                                 |    |                                    | Min. Typ. M |                                                 |                         | Remarks                                                  |  |

| Analog supply                                      | $V_{DDM}$                       | SR | 3.13                               | 3.3         | 3.47 <sup>1)</sup>                              | V                       | _                                                        |  |

| voltage                                            | V <sub>DD</sub>                 | SR | 1.42                               | 1.5         | 1.58 <sup>2)</sup>                              | V                       | Power supply for<br>ADC digital part,<br>internal supply |  |

| Analog ground voltage                              | V <sub>SSM</sub>                | SR | -0.1                               | -           | 0.1                                             | V                       | -                                                        |  |

| Analog reference<br>voltage <sup>17)</sup>         | V <sub>AREFx</sub>              | SR | V <sub>AGNDx</sub> +<br>1V         | $V_{DDM}$   | V <sub>DDM</sub> +<br>0.05<br><sub>1)3)4)</sub> | V                       | -                                                        |  |

| Analog reference ground <sup>17)</sup>             | V <sub>AGNDx</sub>              | SR | V <sub>SSMx</sub> -<br>0.05V       | 0           | V <sub>AREF</sub><br>- 1 V                      | V                       | -                                                        |  |

| Analog reference<br>voltage range <sup>5)17)</sup> | $V_{ m AREFx}$ - $V_{ m AGNDx}$ | SR | $V_{\rm DDM}/2$                    |             | V <sub>DDM</sub><br>+ 0.05                      |                         |                                                          |  |

| Analog input<br>voltage range                      | V <sub>AIN</sub>                | SR | $V_{AGNDx}$                        | -           | V <sub>AREFx</sub>                              | V                       | -                                                        |  |

| V <sub>DDM</sub><br>supply current                 | I <sub>DDM</sub>                | SR |                                    | 2.5         | 4                                               | mA<br>rms               | 6)                                                       |  |

| Power-up<br>calibration<br>time                    | t <sub>PUC</sub>                | CC | _                                  | -           | 3840                                            | f <sub>adc</sub><br>CLK | _                                                        |  |

| Internal ADC                                       | $f_{\rm BC}$                    | CC | 2                                  | -           | 40                                              | MHz                     | $f_{\rm BC} = f_{\rm ANA} \times 4$                      |  |

| clocks                                             | f <sub>ana</sub>                | CC | 0.5                                | -           | 10                                              | MHz                     | $f_{ANA} = f_{BC} / 4$                                   |  |

| Sample time                                        | t <sub>S</sub>                  | CC | $4 \times (CHC + 2) \times t_{BC}$ |             | STC                                             | μS                      | -                                                        |  |

|                                                    |                                 |    | $8 \times t_{BC}$                  | _           | -                                               | μS                      |                                                          |  |

#### **Electrical Parameters**

#### 4.3.2 Output Rise/Fall Times

Table 4-11 provides the characteristics of the output rise/fall times in the TC1163/TC1164.

| Table 4-11 | <b>Output Rise/Fall Times</b> | (Operating Conditions apply) |

|------------|-------------------------------|------------------------------|

|            |                               |                              |

| Parameter                                                                                        | Symbol                              | Limit Values |                                                                    | Unit | Test Conditions                                                                                                                                                                                                                                                                                |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------------------|--------------|--------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                  |                                     | Min.         | Max.                                                               |      |                                                                                                                                                                                                                                                                                                |  |  |

| Class A1 Pads                                                                                    | 1                                   |              |                                                                    |      |                                                                                                                                                                                                                                                                                                |  |  |

| Rise/fall times <sup>1)</sup><br>Class A1 pads                                                   | t <sub>RA1</sub> , t <sub>FA1</sub> |              | 50<br>140<br>18000<br>150<br>550<br>65000                          | ns   | Regular (medium) driver, 50 pF<br>Regular (medium) driver, 150 pF<br>Regular (medium) driver, 20 nF<br>Weak driver, 20 pF<br>Weak driver, 150 pF<br>Weak driver, 20 000 pF                                                                                                                     |  |  |

| Class A2 Pads                                                                                    |                                     |              |                                                                    |      |                                                                                                                                                                                                                                                                                                |  |  |

| Rise/fall times <sup>1)</sup><br>Class A2 pads<br>Class A3 Pads<br>Rise/fall times <sup>1)</sup> | t <sub>FA2</sub> , t <sub>FA2</sub> |              | 3.3<br>6<br>5.5<br>16<br>50<br>140<br>18000<br>150<br>550<br>65000 | ns   | Strong driver, sharp edge, 50 pF<br>Strong driver, sharp edge, 100pF<br>Strong driver, med. edge, 50 pF<br>Strong driver, soft edge, 50 pF<br>Medium driver, 50 pF<br>Medium driver, 150 pF<br>Medium driver, 20 000 pF<br>Weak driver, 20 pF<br>Weak driver, 150 pF<br>Weak driver, 20 000 pF |  |  |

| Class A3 pads                                                                                    | *FA37 *FA3                          |              | 2.0                                                                |      |                                                                                                                                                                                                                                                                                                |  |  |

| Class A4 Pads                                                                                    |                                     | -            |                                                                    | 1    |                                                                                                                                                                                                                                                                                                |  |  |

| Rise/fall times <sup>1)</sup><br>Class A4 pads                                                   | $t_{FA4}, t_{FA4}$                  |              | 2.0                                                                | ns   | 25 pF                                                                                                                                                                                                                                                                                          |  |  |

| Class C Pads                                                                                     |                                     |              |                                                                    |      |                                                                                                                                                                                                                                                                                                |  |  |

| Rise/fall times<br>Class C pads                                                                  | $t_{\rm rC,} t_{\rm fC}$            |              | 2                                                                  | ns   |                                                                                                                                                                                                                                                                                                |  |  |

1) Not all parameters are subject to production test, but verified by design/characterization and test correlation.

#### **Electrical Parameters**

- 4) Applicable for input pins TESTMODE, TRST, BRKIN, and TXD1A with noise suppression filter of PORST switched-on (BYPASS = 0).

- 5) The setup/hold values are applicable for Port 0 and Port 4 input pins with noise suppression filter of HDRST switched-on (BYPASS = 0), independently whether HDRST is used as input or output.

- 6) Not subject to production test, verified by design / characterization.

- 7) This parameter includes the delay of the analog spike filter in the PORST pad.

- 8) Not subject to production test, verified by design / characterization.

- 9) In case of power loss during internal flash write, prevents Flash write to random address.

- 10) Booting from Flash, the duration of the boot-time is defined between the rising edge of the PORST and the moment when the first user instruction has entered the CPU and its processing starts.

11) Booting from Flash, the duration of the boot time is defined between the following events: 1. Hardware reset: the falling edge of a short  $\overline{\text{HDRST}}$  pulse and the moment when the first user instruction has entered the CPU and its processing starts, if the  $\overline{\text{HDRST}}$  pulse is shorter than  $1024 \times T_{\text{SYS}}$ . If the  $\overline{\text{HDRST}}$  pulse is longer than  $1024 \times T_{\text{SYS}}$ , only the time beyond the  $1024 \times T_{\text{SYS}}$  should be added to the

boot time (HDRST falling edge to first user instruction).2. Software reset: the moment of starting the software reset and the moment when the first user instruction

has entered the CPU and its processing starts

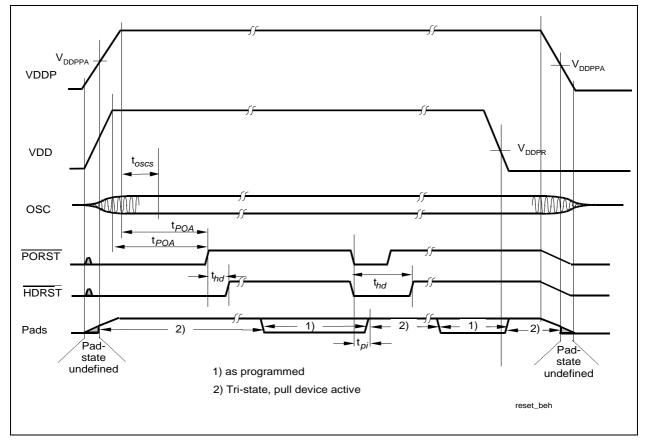

Figure 4-11 Power, Pad and Reset Timing

#### **Electrical Parameters**

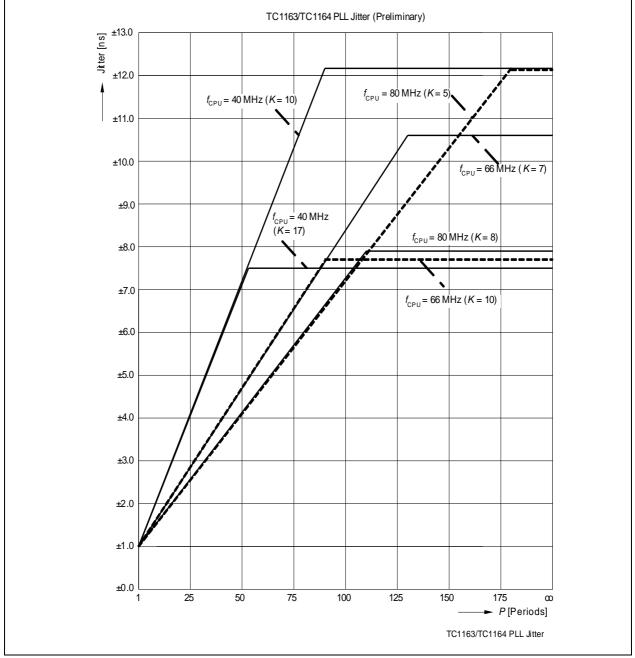

Note: The frequency of system clock  $f_{SYS}$  can be selected to be either  $f_{CPU}$  or  $f_{CPU}/2$ .

With rising number *P* of clock cycles the maximum jitter increases linearly up to a value of *P* that is defined by the K-factor of the PLL. Beyond this value of *P* the maximum accumulated jitter remains at a constant value. Further, a lower CPU clock frequency  $f_{\rm CPU}$  results in a higher absolute maximum jitter value.

**Figure 4-12** illustrates the jitter curve for several K/ $f_{CPU}$  combinations.

Figure 4-12 Approximated Maximum Accumulated PLL Jitter for Typical CPU Clock Frequencies  $f_{CPU}$  (overview)

#### **Electrical Parameters**

## Table 4-16 JTAG Timing Parameter<sup>1)</sup>

| Parameter                                                 | Symbol                |    | Limit<br>Values |      | Unit | Test<br>Conditions /           |

|-----------------------------------------------------------|-----------------------|----|-----------------|------|------|--------------------------------|

|                                                           |                       |    | Min.            | Max. |      | Remarks                        |

| TMS setup to TCK                                          | t <sub>1</sub>        | SR | 6.0             | -    | ns   | -                              |

| TMS hold to TCK                                           | <i>t</i> <sub>2</sub> | SR | 6.0             | _    | ns   | -                              |

| TDI setup to TCK<br>∡                                     | <i>t</i> <sub>1</sub> | SR | 6.0             | _    | ns   | _                              |

| TDI hold to TCK<br>∡                                      | <i>t</i> <sub>2</sub> | SR | 6.0             | -    | ns   | _                              |

| TDO valid output from TCK <sup>2)</sup>                   | $t_3$                 | CC | -               | 14.5 | ns   | $C_{L} = 50 \text{ pF}^{3)4}$  |

| ۹_                                                        |                       |    | 3.0             | _    |      | C <sub>L</sub> = 20 pF         |

| TDO high impedance to valid output from TCK <sup>2)</sup> | t <sub>4</sub>        | CC | -               | 15.5 | ns   | $C_{L} = 50 \text{ pF}^{3)4)}$ |

| TDO valid output to high impedance from TCK <sup>2)</sup> | <i>t</i> <sub>5</sub> | CC | -               | 14.5 | ns   | $C_{L} = 50 \text{ pF}^{4)}$   |

1) Not subject to production test, verified by design / characterization.

2) The falling edge on TCK is used to capture the TDO timing.

3) By reducing the load from 50 pF to 20 pF, a reduction of approximately 1.0 ns in timing is expected.

4) By reducing the power supply range from +/-5 % to +5/-2 %, a reduction of approximately 0.5 ns in timing is expected.

#### Package and Reliability

# 5 Package and Reliability

**Chapter 5** provides the information of the TC1163/TC1164 package and reliability section.

## 5.1 Package Parameters (PG-LQFP-176-2)

Table 5-1 provides the thermal characteristics of the package.

| Table 5-1 | Thermal | Characteristics | of the | Package |

|-----------|---------|-----------------|--------|---------|

|-----------|---------|-----------------|--------|---------|

| Parameter                                          | Symbol            |    | Limit | Values | Unit | Notes |

|----------------------------------------------------|-------------------|----|-------|--------|------|-------|

|                                                    |                   |    | Min.  | Max.   |      |       |

| Thermal resistance junction case top <sup>1)</sup> | R <sub>TJCT</sub> | CC | -     | 5.4    | K/W  | _     |

| Thermal resistance junction leads <sup>1)</sup>    | R <sub>TJL</sub>  | CC | -     | 21.5   | K/W  | -     |

1) The thermal resistances between the case top and the ambient (R<sub>TCAT</sub>), the leads and the ambient (R<sub>TLA</sub>) are to be combined with the thermal resistances between the junction and the case top (R<sub>TJCT</sub>), the junction and the leads (R<sub>TJL</sub>) given above, in order to calculate the total thermal resistance between the junction and the ambient (R<sub>TLA</sub>). The thermal resistances between the case top and the ambient (R<sub>TCAT</sub>), the leads and the ambient (R<sub>TLA</sub>) depend on the external system (PCB, case) characteristics, and are under user responsibility. The junction temperature can be calculated using the following equation: T<sub>J</sub>=T<sub>A</sub>+R<sub>TJA</sub> × P<sub>D</sub>, where the R<sub>TJA</sub> is the total thermal resistance between the junction and the ambient resistance R<sub>TJA</sub> can be obtained from the upper four partial thermal resistances.

#### Package and Reliability

### 5.4 Quality Declaration

Table 5-3 shows the characteristics of the quality parameters in the TC1163/TC1164.

#### Table 5-3Quality Parameters

| Parameter                                                             | Symbol            | Limit | Values    | Unit | Notes                                    |  |

|-----------------------------------------------------------------------|-------------------|-------|-----------|------|------------------------------------------|--|

|                                                                       |                   | Min.  | Min. Max. |      |                                          |  |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)          | V <sub>HBM</sub>  | -     | 2000      | V    | Conforming to<br>EIA/JESD22-<br>A114-B   |  |

| ESD susceptibility of the LVDS pins                                   | V <sub>HBM1</sub> | _     | 500       | V    | -                                        |  |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins | V <sub>CDM</sub>  | -     | 500       | V    | Conforming to<br>JESD22-C101-C           |  |

| Moisture Sensitivity Level<br>(MSL)                                   | _                 | _     | 3         | -    | Conforming to<br>J-STD-020C for<br>240°C |  |

Note: Information about soldering can be found on the "package" information page under: http://www.infineon.com/products.

www.infineon.com