Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 40                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 6K x 8                                                                  |

| RAM Size                   | 20K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 13x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l081cbt6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1 Device overview

### Table 1. Ultra-low-power STM32L081xx device features and peripheral counts

| Perip                                  | oheral              | STM32L081CB                                                                                       | STM32L081KZ            | STM32L081CZ            |  |  |

|----------------------------------------|---------------------|---------------------------------------------------------------------------------------------------|------------------------|------------------------|--|--|

| Flash (Kbytes)                         |                     | 128 Kbytes 192 Kbytes                                                                             |                        |                        |  |  |

| Data EEPROM (Kb                        | oytes)              |                                                                                                   |                        |                        |  |  |

| RAM (Kbytes)                           |                     |                                                                                                   | 20 Kbytes              |                        |  |  |

| AES                                    |                     |                                                                                                   | 1                      |                        |  |  |

|                                        | General-<br>purpose | 4                                                                                                 |                        |                        |  |  |

| Timers                                 | Basic               |                                                                                                   | 2                      |                        |  |  |

|                                        | LPTIMER             |                                                                                                   | 1                      |                        |  |  |

| RTC/SYSTICK/IWDG/WWDG                  |                     |                                                                                                   | 1/1/1/1                |                        |  |  |

|                                        | SPI/I2S             | 6(4) <sup>(1)</sup> /1                                                                            | 4(3) <sup>(2)</sup> /0 | 6(4) <sup>(1)</sup> /1 |  |  |

| Com. interfaces                        | l <sup>2</sup> C    | 3                                                                                                 | 2                      | 3                      |  |  |

|                                        | USART               | 4                                                                                                 | 3                      | 4                      |  |  |

|                                        | LPUART              |                                                                                                   | 1                      |                        |  |  |

| GPIOs                                  |                     | 40                                                                                                | 25 <sup>(3)</sup>      | 40                     |  |  |

| Clocks: HSE/LSE/                       | HSI/MSI/LSI         |                                                                                                   | 1/1/1/1/1              |                        |  |  |

| 12-bit synchronize<br>Number of channe |                     | 1 1 1<br>13 10 13                                                                                 |                        |                        |  |  |

| Comparators                            |                     |                                                                                                   | 2                      |                        |  |  |

| Max. CPU frequen                       | су                  | 32 MHz                                                                                            |                        |                        |  |  |

| Operating voltage                      |                     | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option 1.65 to<br>3.6 V without BOR option |                        |                        |  |  |

| Operating tempera                      | atures              | Ambient temperature: -40 to +125 °C<br>Junction temperature: -40 to +130 °C                       |                        |                        |  |  |

| Packages LQFP48 LQFP3                  |                     |                                                                                                   | LQFP32, UFQFPN32       | LQFP48                 |  |  |

$1. \quad 4 \; \text{SPI interfaces are USARTs operating in SPI master mode.}$

2. 3 SPI interfaces are USARTs operating in SPI master mode.

3. UFQFPN32 has 2 GPIOs less than LQFP32.

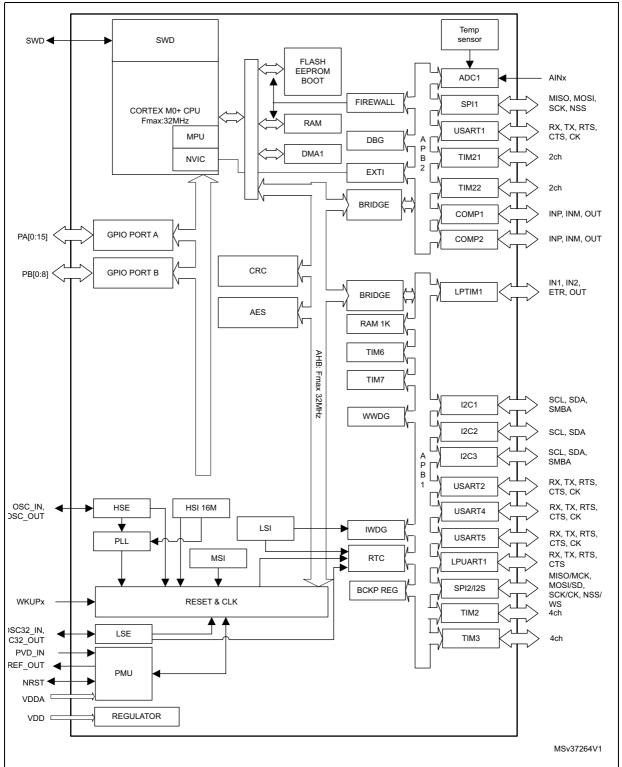

Figure 1. STM32L081xx block diagram

DocID027513 Rev 4

#### • Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USART/I2C/LPUART/LPTIMER wakeup events.

#### • Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE crystal and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

#### Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

| Operating newsrawark                           | Functionalities depending on the operating power supply range |                                |                            |  |  |  |

|------------------------------------------------|---------------------------------------------------------------|--------------------------------|----------------------------|--|--|--|

| Operating power supply<br>range                | ADC operation Dynamic voltage scaling range                   |                                | I/O operation              |  |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | ADC only,<br>conversion time up<br>to 570 ksps                | Range 2 or<br>range 3          | Degraded speed performance |  |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time up<br>to 1.14 Msps               | Range 1, range 2 or<br>range 3 | Degraded speed performance |  |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>         | Conversion time up<br>to 1.14 Msps                            | Range1, range 2 or<br>range 3  | Degraded speed performance |  |  |  |

| Table 4. Functionalities depending on the working mode          |  |

|-----------------------------------------------------------------|--|

| (from Run/active down to standby) (continued) <sup>(1)(2)</sup> |  |

|                                              |                        |                        | Low-         | Low-           | Stop                                   | S | Standby                                |

|----------------------------------------------|------------------------|------------------------|--------------|----------------|----------------------------------------|---|----------------------------------------|

| IPs                                          | Run/Active             | Sleep                  | power<br>run | power<br>sleep | Wakeup<br>capability                   |   | Wakeup<br>capability                   |

|                                              |                        |                        |              |                | 4 μΑ (No<br>V <sub>DD</sub> =1.8 V     |   | 28 µA (No<br>) V <sub>DD</sub> =1.8 V  |

| Consumption<br>V <sub>DD</sub> =1.8 to 3.6 V | Down to<br>140 µA/MHz  | Down to<br>37 µA/MHz   | Down to      | Down to        | β μΑ (with<br>V <sub>DD</sub> =1.8 V   |   | 5 µA (with<br>) V <sub>DD</sub> =1.8 V |

| (Typ)                                        | (from Flash<br>memory) | (from Flash<br>memory) | 8 μΑ         | 4.5 µA         | 4 μΑ (No<br>V <sub>DD</sub> =3.0 V     |   | 29 µA (No<br>) V <sub>DD</sub> =3.0 V  |

|                                              |                        |                        |              |                | <br>(with RTC)<br><sub>DD</sub> =3.0 V |   | 5 μΑ (with<br>) V <sub>DD</sub> =3.0 V |

1. Legend:

"Y" = Yes (enable). "O" = Optional can be enabled/disabled by software) "-" = Not available

2. The consumption values given in this table are preliminary data given for indication. They are subject to slight changes.

- 3. Some peripherals with wakeup from Stop capability can request HSI to be enabled. In this case, HSI is woken up by the peripheral, and only feeds the peripheral which requested it. HSI is automatically put off when the peripheral does not need it anymore.

- 4. UART and LPUART reception is functional in Stop mode. It generates a wakeup interrupt on Start. To generate a wakeup on address match or received frame event, the LPUART can run on LSE clock while the UART has to wake up or keep running the HSI clock.

- 5. I2C address detection is functional in Stop mode. It generates a wakeup interrupt in case of address match. It will wake up the HSI during reception.

#### 3.2 Interconnect matrix

Several peripherals are directly interconnected. This allows autonomous communication between peripherals, thus saving CPU resources and power consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, Low-power run, Low-power sleep and Stop modes.

| Interconnect<br>source | Interconnect<br>destination | Interconnect action                                               | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |

|------------------------|-----------------------------|-------------------------------------------------------------------|-----|-------|----------------------|------------------------|------|

| COMPx                  | TIM2,TIM21,<br>TIM22        | Timer input channel,<br>trigger from analog<br>signals comparison | Y   | Y     | Y                    | Y                      | -    |

| COMPX                  | LPTIM                       | Timer input channel,<br>trigger from analog<br>signals comparison | Y   | Y     | Y                    | Y                      | Y    |

| TIMx                   | TIMx                        | Timer triggered by other timer                                    | Y   | Y     | Y                    | Y                      | -    |

| Table 5. STM32L0xx peripherals interconnect matrix |

|----------------------------------------------------|

|----------------------------------------------------|

# 3.10 Direct memory access (DMA)

The flexible 7-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: AES, SPI, I<sup>2</sup>C, USART, LPUART, general-purpose timers, and ADC.

# 3.11 Analog-to-digital converter (ADC)

A native 12-bit, extended to 16-bit through hardware oversampling, analog-to-digital converter is embedded into STM32L081xx device. It has up to 16 external channels and 3 internal channels (temperature sensor, voltage reference). Three channels, PA0, PA4 and PA5, are fast channels, while the others are standard channels.

The ADC performs conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC frequency is independent from the CPU frequency, allowing maximum sampling rate of 1.14 MSPS even with a low CPU speed. The ADC consumption is low at all frequencies (~25  $\mu$ A at 10 kSPS, ~240  $\mu$ A at 1MSPS). An auto-shutdown function guarantees that the ADC is powered off except during the active conversion phase.

The ADC can be served by the DMA controller. It can operate from a supply voltage down to 1.65 V.

The ADC features a hardware oversampler up to 256 samples, this improves the resolution to 16 bits (see AN2668).

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all scanned channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start triggers, to allow the application to synchronize A/D conversions and timers.

# 3.12 Temperature sensor

The temperature sensor (T<sub>SENSE</sub>) generates a voltage V<sub>SENSE</sub> that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN18 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

DocID027513 Rev 4

# 3.15.6 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 3.16 Communication interfaces

# 3.16.1 I<sup>2</sup>C bus

Up to three I<sup>2</sup>C interfaces (I2C1 and I2C3) can operate in multimaster or slave modes.

Each I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask) are also supported as well as programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |

Table 9. Comparison of I2C analog and digital filters

In addition, I2C1 and I2C3 provide hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1/I2C3 also have a clock domain independent from the CPU clock, allowing the I2C1/I2C3 to wake up the MCU from Stop mode on address match.

Each I2C interface can be served by the DMA controller.

Refer to *Table 10* for an overview of I2C interface features.

| Table 10. STM32L081xx I <sup>2</sup> C implementat | ion |

|----------------------------------------------------|-----|

|----------------------------------------------------|-----|

| I2C features <sup>(1)</sup>      | I2C1 | I2C2 | I2C3 |

|----------------------------------|------|------|------|

| 7-bit addressing mode            | Х    | Х    | Х    |

| 10-bit addressing mode           | Х    | Х    | Х    |

| Standard mode (up to 100 kbit/s) | Х    | Х    | Х    |

| Fast mode (up to 400 kbit/s)     | Х    | Х    | Х    |

## 3.16.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock. It can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

## 3.16.4 Serial peripheral interface (SPI)/Inter-integrated sound (I2S)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The USARTs with synchronous capability can also be used as SPI master.

One standard I2S interfaces (multiplexed with SPI2) is available. It can operate in master or slave mode, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When the I2S interfaces is configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

The SPIs can be served by the DMA controller.

Refer to *Table 12* for the differences between SPI1 and SPI2.

| SPI features <sup>(1)</sup> | SPI1 | SPI2 |

|-----------------------------|------|------|

| Hardware CRC calculation    | Х    | Х    |

| I2S mode                    | -    | Х    |

| TI mode                     | Х    | Х    |

#### Table 12. SPI/I2S implementation

1. X = supported.

| പ   |

|-----|

| S   |

| 321 |

| 000 |

| X   |

| X   |

5

|        |      |                                                                                          |                                 | Table 15.                                                                       | Alternate fund    | tions port A                                       |                                          |                                                             |                                   |

|--------|------|------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------|-------------------|----------------------------------------------------|------------------------------------------|-------------------------------------------------------------|-----------------------------------|

|        |      | AF0                                                                                      | AF1                             | AF2                                                                             | AF3               | AF4                                                | AF5                                      | AF6                                                         | AF7                               |

| Port   |      | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/<br>LPTIM1<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/<br>I2C1/TIM2/21 | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/LPTIM1/<br>TIM2/3/<br>EVENTOUT/<br>SYS_AF | I2C1/<br>EVENTOUT | I2C1/USART1/2/L<br>PUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/<br>EVENTOUT | I2C3/LPUART1/<br>COMP1/2/<br>TIM3 |

|        | PA0  | -                                                                                        | -                               | TIM2_CH1                                                                        | -                 | USART2_CTS                                         | TIM2_ETR                                 | USART4_TX                                                   | COMP1_OUT                         |

|        | PA1  | EVENTOUT                                                                                 | -                               | TIM2_CH2                                                                        | -                 | USART2_RTS_D<br>E                                  | TIM21_ETR                                | USART4_RX                                                   | -                                 |

|        | PA2  | TIM21_CH1                                                                                | -                               | TIM2_CH3                                                                        | -                 | USART2_TX                                          | -                                        | LPUART1_TX                                                  | COMP2_OUT                         |

|        | PA3  | TIM21_CH2                                                                                | -                               | TIM2_CH4                                                                        | -                 | USART2_RX                                          | -                                        | LPUART1_RX                                                  | -                                 |

|        | PA4  | SPI1_NSS                                                                                 | -                               | -                                                                               | -                 | USART2_CK                                          | TIM22_ETR                                | -                                                           | -                                 |

|        | PA5  | SPI1_SCK                                                                                 | -                               | TIM2_ETR                                                                        | -                 |                                                    | TIM2_CH1                                 | -                                                           | -                                 |

|        | PA6  | SPI1_MISO                                                                                | -                               | TIM3_CH1                                                                        | -                 | LPUART1_CTS                                        | TIM22_CH1                                | EVENTOUT                                                    | COMP1_OUT                         |

| ∢      | PA7  | SPI1_MOSI                                                                                | -                               | TIM3_CH2                                                                        | -                 | -                                                  | TIM22_CH2                                | EVENTOUT                                                    | COMP2_OUT                         |

| Port A | PA8  | MCO                                                                                      | -                               | -                                                                               | EVENTOUT          | USART1_CK                                          | -                                        | -                                                           | I2C3_SCL                          |

|        | PA9  | MCO                                                                                      | -                               | -                                                                               | -                 | USART1_TX                                          | -                                        | I2C1_SCL                                                    | I2C3_SMBA                         |

|        | PA10 | -                                                                                        | -                               | -                                                                               | -                 | USART1_RX                                          | -                                        | I2C1_SDA                                                    | -                                 |

|        | PA11 | SPI1_MISO                                                                                | -                               | EVENTOUT                                                                        | -                 | USART1_CTS                                         | -                                        | -                                                           | COMP1_OUT                         |

|        | PA12 | SPI1_MOSI                                                                                | -                               | EVENTOUT                                                                        | -                 | USART1_RTS_D<br>E                                  | -                                        | -                                                           | COMP2_OUT                         |

|        | PA13 | SWDIO                                                                                    | -                               | -                                                                               | -                 | -                                                  | -                                        | LPUART1_RX                                                  | -                                 |

|        | PA14 | SWCLK                                                                                    | -                               | -                                                                               | -                 | USART2_TX                                          | -                                        | LPUART1_TX                                                  | -                                 |

|        | PA15 | SPI1_NSS                                                                                 | -                               | TIM2_ETR                                                                        | EVENTOUT          | USART2_RX                                          | TIM2_CH1                                 | USART4_RTS_D<br>E                                           | -                                 |

Pin descriptions

39/110

# 6.3 Operating conditions

# 6.3.1 General operating conditions

#### Table 20. General operating conditions

| Symbol             | Parameter                                                                                                 | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Min  | Мах                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Unit  |

|--------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0    | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0    | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MHz   |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency -<br>BOR detector disabled                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0    | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|                    |                                                                                                           | BOR detector disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.65 | 0       32         0       32         0       32         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         65       3.6         0       5.5         0.3       V_DD+0.3         -       333         -       93         139       -         -       83         40       85         40       105         40       105         40       125                              |       |

| V <sub>DD</sub>    | Standard operating voltage                                                                                | BOR detector enabled, at power on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.8  | 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V     |

|                    |                                                                                                           | BOR detector disabled, after power on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.65 | 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| V <sub>DDA</sub>   | Analog operating voltage (all features)                                                                   | icy-incy-incy-incy-incy-BOR detector disabledBOR detector enabled, at power<br>onBOR detector disabled, after<br>power onall features)Must be the same voltage as<br>$V_{DD}^{(1)}$ all features) $2.0 V \le V_{DD} \le 3.6 V$ in- $1.65 V \le V_{DD} \le 2.0 V$ in- $2.0 V \le V_{DD} \le 2.0 V$ in- $V_{DP}^{(1)} \le V_{DD} \le 2.0 V$ in- $V_{DD} \le 0.0 V$ in- $V_{DD} \le 0.0 V$ in- $V_{DD} \le 0.0 V$ in-in-in-in-in-in-in-in-in-in-in- </td <td>3.6</td> <td>V</td> |      | 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V     |

| V <sub>DDIO2</sub> | Standard operating voltage                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.65 | 3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V     |

|                    | Input voltage on FT, FTf and RST pins <sup>(2)</sup>                                                      | $2.0~V \leq V_{DD} \leq 3.6~V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -0.3 | 32       MHz         32       MHz         32       MHz         32       V         3.6       V         5.5       V         VDD+0.3       MW         370       MW         333       MW         93       MW         139       MW         83       85         105       °C         105       °C         105       °C |       |

| V <sub>IN</sub>    | input voltage off 1, 1 fr and KST pins                                                                    | $1.65~V \leq V_{DD} \leq 2.0~V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.3 | 5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V     |

| VIN                | Input voltage on BOOT0 pin                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0    | 5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | v     |

|                    | Input voltage on TC pin                                                                                   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.3 | V <sub>DD</sub> +0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

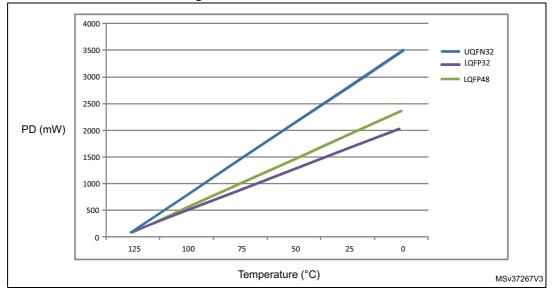

|                    | Power dissipation at $T_A = 85 \text{ °C}$ (range 6)<br>or $T_A = 105 \text{ °C}$ (rage 7) <sup>(3)</sup> | LQFP48 package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | 370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|                    |                                                                                                           | UFQFPN32 package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | 556                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| P <sub>D</sub>     |                                                                                                           | LQFP32 package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | 333                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | m\//  |

| I D                |                                                                                                           | LQFP48 package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11100 |

|                    | Power dissipation at $T_A = 125 \degree C$ (range 3) <sup>(3)</sup>                                       | UFQFPN32 package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|                    |                                                                                                           | LQFP32 package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -    | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

|                    |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -40  | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| Та                 | Temperature range                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -40  | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -     |

|                    |                                                                                                           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -40  | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | °C    |

|                    | Junction temperature range (range 6)                                                                      | -40 $^\circ C \leq T_A \leq 85 \ ^\circ$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -40  | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| TJ                 | Junction temperature range (range 7)                                                                      | -40 $^\circ C \leq T_A \leq$ 105 $^\circ C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -40  | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|                    | Junction temperature range (range 3)                                                                      | -40 °C $\leq$ T <sub>A</sub> $\leq$ 125 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -40  | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

1. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and normal operation.

2. To sustain a voltage higher than  $V_{DD}$ +0.3V, the internal pull-up/pull-down resistors must be disabled.

3. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_J$  max (see *Table 19: Thermal characteristics on page 45*).

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol               | Parameter                     |                                                                                 | Conditions                               |           | f <sub>HCLK</sub> | Тур                                      | Unit       |           |       |     |    |

|----------------------|-------------------------------|---------------------------------------------------------------------------------|------------------------------------------|-----------|-------------------|------------------------------------------|------------|-----------|-------|-----|----|

|                      |                               |                                                                                 |                                          | Dhrystone |                   | 570                                      |            |           |       |     |    |

|                      |                               |                                                                                 | Range 3,                                 | CoreMark  | 4 MHz             | 670                                      |            |           |       |     |    |

|                      | Supply current in             | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,                  | V                                        |           | VOS[1             | V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11 |            | Fibonacci | 4 M⊡Z | 410 | μA |

| I <sub>DD</sub> (Run | Run mode, code executed from  |                                                                                 |                                          | while(1)  |                   | 375                                      |            |           |       |     |    |

| from<br>RAM)         | RAM, Flash<br>memory switched | f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above<br>16 MHz (PLL on) <sup>(2)</sup> |                                          | Dhrystone |                   | 6,65                                     |            |           |       |     |    |

|                      | off                           |                                                                                 | Range 1,                                 | CoreMark  | 32 MHz            | 6,95                                     | <b>m</b> 4 |           |       |     |    |

|                      |                               |                                                                                 | V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | Fibonacci |                   | 5,9                                      | mA         |           |       |     |    |

|                      |                               |                                                                                 |                                          | while(1)  |                   | 5,2                                      |            |           |       |     |    |

# Table 27. Current consumption in Run mode vs code type, code with data processing running from RAM<sup>(1)</sup>

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

|          |                                               |                                                        | it consumption in                                 |                                            | noue                       |      |                    |      |

|----------|-----------------------------------------------|--------------------------------------------------------|---------------------------------------------------|--------------------------------------------|----------------------------|------|--------------------|------|

| Symbol   | Parameter                                     |                                                        | Condition                                         |                                            | f <sub>HCLK</sub><br>(MHz) | Тур  | Max <sup>(1)</sup> | Unit |

|          |                                               | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | 9,45                                              | 12                                         |                            |      |                    |      |

|          |                                               |                                                        | MSI clock = 65 kHz,                               | T <sub>A</sub> = 85°C                      | 0.000                      | 14   | 58                 |      |