## Renesas - D12350F20IV Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                     |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 20MHz                                                                        |

| Connectivity               | SCI, SmartCard                                                               |

| Peripherals                | DMA, POR, PWM, WDT                                                           |

| Number of I/O              | 87                                                                           |

| Program Memory Size        | -                                                                            |

| Program Memory Type        | ROMIess                                                                      |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b SAR; D/A 2x8b                                                      |

| Oscillator Type            | External, Internal                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 128-BFQFP                                                                    |

| Supplier Device Package    | 128-QFP (14x20)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/d12350f20iv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

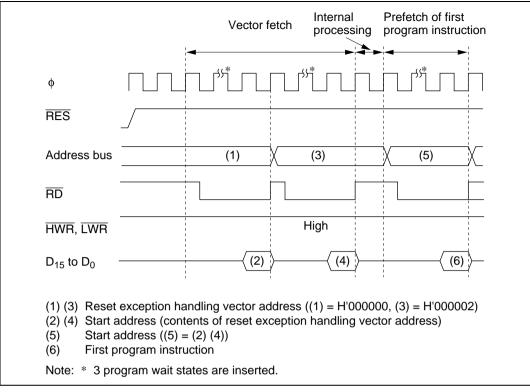

Figure 4.3 Reset Sequence (Mode 4)

## 4.2.4 Interrupts after Reset

If an interrupt is accepted after a reset but before the stack pointer (SP) is initialized, the PC and CCR will not be saved correctly, leading to a program crash. To prevent this, all interrupt requests, including NMI, are disabled immediately after a reset. Since the first instruction of a program is always executed immediately after the reset state ends, make sure that this instruction initializes the stack pointer (example: MOV.L #xx:32, SP).

## 4.2.5 State of On-Chip Supporting Modules after Reset Release

After reset release, MSTPCR is initialized to H'3FFF and all modules except the DMAC and DTC enter module stop mode. Consequently, on-chip supporting module registers cannot be read or written to. Register reading and writing is enabled when module stop mode is exited.

|               | ASTCR<br>ASTn | WCI | RH, WCRL | Bus Spee  | cifications (Basic | Bus Interface)         |

|---------------|---------------|-----|----------|-----------|--------------------|------------------------|

| ABWCR<br>ABWn |               | Wn1 | Wn0      | Bus Width | Access States      | Program Wait<br>States |

| 0             | 0             |     |          | 16        | 2                  | 0                      |

|               | 1             | 0   | 0        |           | 3                  | 0                      |

|               |               |     | 1        |           | 1                  |                        |

|               |               | 1   | 0        |           |                    | 2                      |

|               |               |     | 1        |           |                    | 3                      |

| 1             | 0             |     | _        | 8         | 2                  | 0                      |

|               | 1             | 0   | 0        |           | 3                  | 0                      |

|               |               |     | 1        |           |                    | 1                      |

|               |               | 1   | 0        |           |                    | 2                      |

|               |               |     | 1        |           |                    | 3                      |

#### Table 6.3 Bus Specifications for Each Area (Basic Bus Interface)

#### 6.3.3 Memory Interfaces

The H8S/2350 Group memory interfaces comprise a basic bus interface that allows direct connection of ROM, SRAM, and so on; a DRAM interface that allows direct connection of DRAM; and a burst ROM interface that allows direct connection of burst ROM. The interface can be selected independently for each area.

An area for which the basic bus interface is designated functions as normal space, an area for which the DRAM interface is designated functions as DRAM space, and an area for which the burst ROM interface is designated functions as burst ROM space.

## 6.5 **DRAM Interface**

#### 6.5.1 Overview

When the H8S/2350 Group is in advanced mode, external space areas 2 to 5 can be designated as DRAM space, and DRAM interfacing performed. With the DRAM interface, DRAM can be directly connected to the H8S/2350 Group. A DRAM space of 2, 4, or 8 Mbytes can be set by means of bits RMTS2 to RMTS0 in BCRH. Burst operation is also possible, using fast page mode.

#### 6.5.2 Setting DRAM Space

Areas 2 to 5 are designated as DRAM space by setting bits RMTS2 to RMTS0 in BCRH. The relation between the settings of bits RMTS2 to RMTS0 and DRAM space is shown in table 6.5. Possible DRAM space settings are: one area (area 2), two areas (areas 2 and 3), and four areas (areas 2 to 5).

| Table 6.5 | Settings of Bits RMTS2 to RMTS0 and | <b>Corresponding DRAM Spaces</b> |

|-----------|-------------------------------------|----------------------------------|

|-----------|-------------------------------------|----------------------------------|

| RMTS2 | RMTS1 | RMTS0 | Area 5                  | Area 4 | Area 3     | Area 2 |

|-------|-------|-------|-------------------------|--------|------------|--------|

| 0     | 0     | 1     | Normal space DRAM sp    |        | DRAM space |        |

|       | 1     | 0     | Normal space DRAM space |        | space      |        |

|       |       | 1     | DRAM space              |        |            |        |

- Module stop mode can be set

- The initial setting enables DMAC registers to be accessed. DMAC operation is halted by setting module stop mode

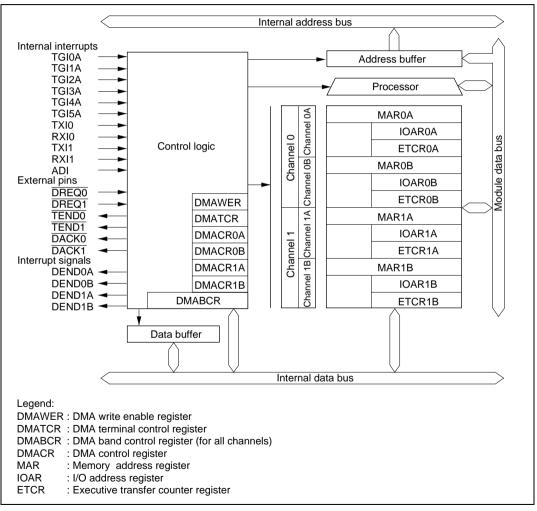

#### 7.1.2 Block Diagram

A block diagram of the DMAC is shown in figure 7.1.

Rev. 3.00 Sep 15, 2006 page 196 of 988 REJ09B0330-0300

**Bit 0—Write Enable 0A (WE0A):** Enables or disables writes to all bits in DMACR0A, and bits 8, 4, and 0 in DMABCR.

| Bit 0<br>WE0A | Description                                                                                |

|---------------|--------------------------------------------------------------------------------------------|

| 0             | Writes to all bits in DMACR0A, and bits 8, 4, and 0 in DMABCR are disabled (Initial value) |

| 1             | Writes to all bits in DMACR0A, and bits 8, 4, and 0 in DMABCR are enabled                  |

Writes by the DTC to bits 15 to 12 (FAE and SAE) in DMABCR are invalid regardless of the DMAWER settings. These bits should be changed, if necessary, by CPU processing.

In writes by the DTC to bits 7 to 4 (DTE) in DMABCR, 1 can be written without first reading 0. To reactivate a channel set to full address mode, write 1 to both Write Enable A and Write Enable B for the channel to be reactivated.

MAR, IOAR, and ETCR are always write-enabled regardless of the DMAWER settings. When modifying these registers, the channel for which the modification is to be made should be halted.

#### 7.5.4 Repeat Mode

Repeat mode can be specified by setting the RPE bit in DMACR to 1, and clearing the DTIE bit to 0. In repeat mode, MAR is updated after each byte or word transfer in response to a single transfer request, and this is executed the number of times specified in ETCR. On completion of the specified number of transfers, MAR and ETCRL are automatically restored to their original settings and operation continues.

One address is specified by MAR, and the other by IOAR. The transfer direction can be specified by the DTDIR bit in DMACR.

Table 7.8 summarizes register functions in repeat mode.

| Register             | DTDIR = 0                          | DTDIR = 1                          | Initial Setting                                                      | Operation                                                                                                     |

|----------------------|------------------------------------|------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 23 0<br>MAR          | Source<br>address<br>register      | Destination<br>address<br>register | Start address<br>of transfer<br>destination or<br>transfer source    | Incremented/<br>decremented every<br>transfer. Initial<br>setting is restored<br>when value reaches<br>H'0000 |

| 23 15 0<br>H'FF IOAR | Destination<br>address<br>register | Source<br>address<br>register      | Start address<br>of transfer<br>source or<br>transfer<br>destination | Fixed                                                                                                         |

| 7 0<br>ETCRH         | Holds numb<br>transfers            | er of                              | Number of transfers                                                  | Fixed                                                                                                         |

| 7 ♥ 0<br>ETCRL       | Transfer cou                       | unter                              | Number of transfers                                                  | Decremented every<br>transfer. Loaded<br>with ETCRH value<br>when count reaches<br>H'00                       |

#### Table 7.8 Register Functions in Repeat Mode

Legend:

MAR: Memory address register

IOAR: I/O address register

ETCR: Transfer count register

DTDIR: Data transfer direction bit

# Section 10 16-Bit Timer Pulse Unit (TPU)

## 10.1 Overview

The H8S/2350 Group has an on-chip 16-bit timer pulse unit (TPU) that comprises six 16-bit timer channels.

### 10.1.1 Features

- Maximum 16-pulse input/output

- A total of 16 timer general registers (TGRs) are provided (four each for channels 0 and 3, and two each for channels 1, 2, 4, and 5), each of which can be set independently as an output compare/input capture register

- TGRC and TGRD for channels 0 and 3 can also be used as buffer registers

- Selection of 8 counter input clocks for each channel

- The following operations can be set for each channel:

- Waveform output at compare match: Selection of 0, 1, or toggle output

- Input capture function: Selection of rising edge, falling edge, or both edge detection

- Counter clear operation: Counter clearing possible by compare match or input capture

- Synchronous operation: Multiple timer counters (TCNT) can be written to simultaneously

- Simultaneous clearing by compare match and input capture possible

- Register simultaneous input/output possible by counter synchronous operation

- PWM mode: Any PWM output duty can be set

- Maximum of 15-phase PWM output possible by combination with synchronous operation

- Buffer operation settable for channels 0 and 3

- Input capture register double-buffering possible

- Automatic rewriting of output compare register possible

- Phase counting mode settable independently for each of channels 1, 2, 4, and 5

- Two-phase encoder pulse up/down-count possible

- Cascaded operation

- Channel 2 (channel 5) input clock operates as 32-bit counter by setting channel 1 (channel 4) overflow/underflow

- Fast access via internal 16-bit bus

- Fast access is possible via a 16-bit bus interface

# Renesas

**Bit 7—A/D Conversion Start Request Enable (TTGE):** Enables or disables generation of A/D conversion start requests by TGRA input capture/compare match.

| Bit 7 | Description                                      |                 |

|-------|--------------------------------------------------|-----------------|

| TTGE  | Description                                      |                 |

| 0     | A/D conversion start request generation disabled | (Initial value) |

| 1     | A/D conversion start request generation enabled  |                 |

Bit 6—Reserved: Read-only bit, always read as 1.

**Bit 5—Underflow Interrupt Enable (TCIEU):** Enables or disables interrupt requests (TCIU) by the TCFU flag when the TCFU flag in TSR is set to 1 in channels 1 and 2.

In channels 0 and 3, bit 5 is reserved. It is always read as 0 and cannot be modified.

| Bit 5<br>TCIEU | Description                                |                 |

|----------------|--------------------------------------------|-----------------|

| 0              | Interrupt requests (TCIU) by TCFU disabled | (Initial value) |

| 1              | Interrupt requests (TCIU) by TCFU enabled  |                 |

**Bit 4—Overflow Interrupt Enable (TCIEV):** Enables or disables interrupt requests (TCIV) by the TCFV flag when the TCFV flag in TSR is set to 1.

| Bit 4<br>TCIEV | Description                                |                 |

|----------------|--------------------------------------------|-----------------|

| 0              | Interrupt requests (TCIV) by TCFV disabled | (Initial value) |

| 1              | Interrupt requests (TCIV) by TCFV enabled  |                 |

**Bit 3—TGR Interrupt Enable D (TGIED):** Enables or disables interrupt requests (TGID) by the TGFD bit when the TGFD bit in TSR is set to 1 in channels 0 and 3.

In channels 1, 2, 4, and 5, bit 3 is reserved. It is always read as 0 and cannot be modified.

Bit 3 TGIED

Description

0

Interrupt requests (TGID) by TGFD bit disabled (Initial value)

1

Interrupt requests (TGID) by TGFD bit enabled

## Renesas

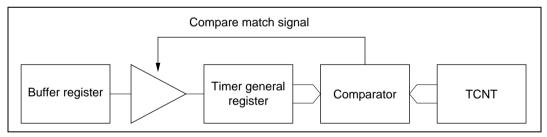

### **10.4.4 Buffer Operation**

Buffer operation, provided for channels 0 and 3, enables TGRC and TGRD to be used as buffer registers.

Buffer operation differs depending on whether TGR has been designated as an input capture register or as a compare match register.

Table 10.5 shows the register combinations used in buffer operation.

| Channel | Timer General Register | Buffer Register |  |

|---------|------------------------|-----------------|--|

| 0       | TGR0A                  | TGR0C           |  |

|         | TGR0B                  | TGR0D           |  |

| 3       | TGR3A                  | TGR3C           |  |

|         | TGR3B                  | TGR3D           |  |

Table 10.5

Register Combinations in Buffer Operation

• When TGR is an output compare register

When a compare match occurs, the value in the buffer register for the corresponding channel is transferred to the timer general register.

This operation is illustrated in figure 10.16.

Figure 10.16 Compare Match Buffer Operation

Bit 6—Receive Data Register Full (RDRF): Indicates that the received data is stored in RDR.

| Bit 6 |                                                                                                                                                               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDRF  | Description                                                                                                                                                   |

| 0     | [Clearing conditions] (Initial value)                                                                                                                         |

|       | <ul> <li>When 0 is written to RDRF after reading RDRF = 1</li> </ul>                                                                                          |

|       | When the DMAC or DTC is activated by an RXI interrupt and read data from RDR                                                                                  |

| 1     | [Setting condition]                                                                                                                                           |

|       | When serial reception ends normally and receive data is transferred from RSR to RDR                                                                           |

| Note: | RDR and the RDRF flag are not affected and retain their previous values when an error is detected during reception or when the RE bit in SCR is cleared to 0. |

If reception of the next data is completed while the RDRF flag is still set to 1, an overrun error will occur and the receive data will be lost.

**Bit 5—Overrun Error (ORER):** Indicates that an overrun error occurred during reception, causing abnormal termination.

| Bit 5<br>ORER | Description                                                                                                                                                                   |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| URER          | Description                                                                                                                                                                   |  |

| 0             | [Clearing condition] (Initial value)*1                                                                                                                                        |  |

|               | When 0 is written to ORER after reading ORER = 1                                                                                                                              |  |

| 1             | [Setting condition]                                                                                                                                                           |  |

|               | When the next serial reception is completed while RDRF = 1                                                                                                                    |  |

| Notes: 1      | otes: 1. The ORER flag is not affected and retains its previous state when the RE bit in SCF cleared to 0.                                                                    |  |

| 2             | . The receive data prior to the overrun error is retained in RDR, and the data received subsequently is lost. Also, subsequent serial reception cannot be continued while the |  |

2. The receive data prior to the overrun error is retained in RDR, and the data received subsequently is lost. Also, subsequent serial reception cannot be continued while the ORER flag is set to 1. In clocked synchronous mode, serial transmission cannot be continued, either.

**Bit 4—Framing Error (FER):** Indicates that a framing error occurred during reception in asynchronous mode, causing abnormal termination.

| Bit 4<br>FER |    | Description                                                                                                                                                                                                                                                                                                 |                                         |

|--------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 0            |    | [Clearing condition]                                                                                                                                                                                                                                                                                        | (Initial value) <sup>*1</sup>           |

|              |    | When 0 is written to FER after reading FER = 1                                                                                                                                                                                                                                                              |                                         |

| 1            |    | [Setting condition]                                                                                                                                                                                                                                                                                         |                                         |

|              |    | When the SCI checks whether the stop bit at the end of the receive reception ends, and the stop bit is $0^{*2}$                                                                                                                                                                                             | e data when                             |

| Notes:       | 1. | The FER flag is not affected and retains its previous state when the cleared to 0.                                                                                                                                                                                                                          | RE bit in SCR is                        |

|              | 2. | In 2-stop-bit mode, only the first stop bit is checked for a value of 0; is not checked. If a framing error occurs, the receive data is transfer RDRF flag is not set. Also, subsequent serial reception cannot be c FER flag is set to 1. In clocked synchronous mode, serial transmiss continued, either. | rred to RDR but the continued while the |

**Bit 3—Parity Error (PER):** Indicates that a parity error occurred during reception using parity addition in asynchronous mode, causing abnormal termination.

| Bit 3<br>PER | Description                                                                                                                                                                                                                                      |                               |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 0            | [Clearing condition]                                                                                                                                                                                                                             | (Initial value) <sup>*1</sup> |

|              | When 0 is written to PER after reading PER = 1                                                                                                                                                                                                   |                               |

| 1            | [Setting condition]                                                                                                                                                                                                                              |                               |

|              | When, in reception, the number of 1 bits in the receive data plus the parameter match the parity setting (even or odd) specified by the $O/\overline{E}$ bit in SMR*                                                                             | arity bit does not            |

| Notes:       | 1. The PER flag is not affected and retains its previous state when the RE cleared to 0.                                                                                                                                                         | bit in SCR is                 |

|              | <ol> <li>If a parity error occurs, the receive data is transferred to RDR but the RI set. Also, subsequent serial reception cannot be continued while the PE 1. In clocked synchronous mode, serial transmission cannot be continued.</li> </ol> | R flag is set to              |

In serial reception, the SCI operates as described below.

- [1] The SCI monitors the transmission line, and if a 0 stop bit is detected, performs internal synchronization and starts reception.

- [2] The received data is stored in RSR in LSB-to-MSB order.

- [3] The parity bit and stop bit are received.

After receiving these bits, the SCI carries out the following checks.

[a] Parity check:

The SCI checks whether the number of 1 bits in the receive data agrees with the parity (even or odd) set in the  $O/\overline{E}$  bit in SMR.

[b] Stop bit check:

The SCI checks whether the stop bit is 1.

If there are two stop bits, only the first is checked.

[c] Status check:

The SCI checks whether the RDRF flag is 0, indicating that the receive data can be transferred from RSR to RDR.

If all the above checks are passed, the RDRF flag is set to 1, and the receive data is stored in RDR.

If a receive error\* is detected in the error check, the operation is as shown in table 13.11.

- Note: \* Subsequent receive operations cannot be performed when a receive error has occurred.

Also note that the RDRF flag is not set to 1 in reception, and so the error flags must be cleared to 0.

- [4] If the RIE bit in SCR is set to 1 when the RDRF flag changes to 1, a receive data full interrupt (RXI) request is generated.

Also, if the RIE bit in SCR is set to 1 when the ORER, PER, or FER flag changes to 1, a receive error interrupt (ERI) request is generated.

# Renesas

In serial transmission, the SCI operates as described below.

- [1] The SCI monitors the TDRE flag in SSR, and if is 0, recognizes that data has been written to TDR, and transfers the data from TDR to TSR.

- [2] After transferring data from TDR to TSR, the SCI sets the TDRE flag to 1 and starts transmission.

If the TIE bit is set to 1 at this time, a transmit data empty interrupt (TXI) is generated.

The serial transmit data is sent from the TxD pin in the following order.

[a] Start bit:

One 0-bit is output.

[b] Transmit data:

8-bit or 7-bit data is output in LSB-first order.

[c] Multiprocessor bit

One multiprocessor bit (MPBT value) is output.

[d] Stop bit(s):

One or two 1-bits (stop bits) are output.

[e] Mark state:

1 is output continuously until the start bit that starts the next transmission is sent.

[3] The SCI checks the TDRE flag at the timing for sending the stop bit.

If the TDRE flag is cleared to 0, data is transferred from TDR to TSR, the stop bit is sent, and then serial transmission of the next frame is started.

If the TDRE flag is set to 1, the TEND flag in SSR is set to 1, the stop bit is sent, and then the mark state is entered in which 1 is output continuously. If the TEIE bit in SCR is set to 1 at this time, a transmission end interrupt (TEI) request is generated.

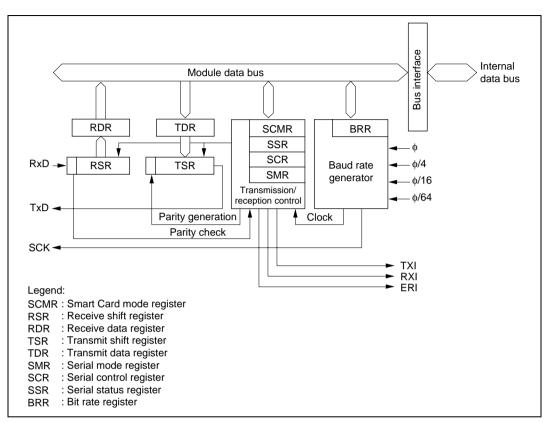

### 14.1.2 Block Diagram

Figure 14.1 shows a block diagram of the Smart Card interface.

Figure 14.1 Block Diagram of Smart Card Interface

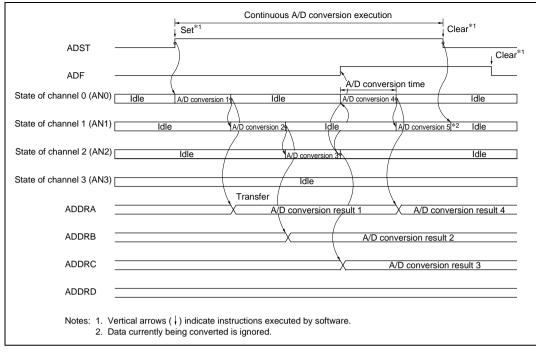

Figure 15.4 Example of A/D Converter Operation (Scan Mode, Channels AN0 to AN2 Selected)

# 21.5 D/A Conversion Characteristics

Table 21.10 lists the D/A conversion characteristics

### Table 21.10 D/A Conversion Characteristics

```

Condition A: V_{CC} = AV_{CC} = 2.7 \text{ V to } 5.5 \text{ V}, V_{ref} = 2.7 \text{ V to } AV_{CC}, V_{SS} = AV_{SS} = 0 \text{ V},

\phi = 2 \text{ to } 10 \text{ MHz}, T_a = -20 \text{ to } +75^{\circ}\text{C} \text{ (regular specifications)},

T_a = -40 \text{ to } +85^{\circ}\text{C} \text{ (wide-range specifications)}

```

Condition B:  $V_{CC} = AV_{CC} = 5.0 V \pm 10\%$ ,  $V_{ref} = 4.5 V$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 V$ ,  $\phi = 2$  to 20 MHz,  $T_a = -20$  to  $+75^{\circ}C$  (regular specifications),  $T_a = -40$  to  $+85^{\circ}C$  (wide-range specifications)

|                   | c   | conditio | on A | C   | conditio | n B  |      |                             |

|-------------------|-----|----------|------|-----|----------|------|------|-----------------------------|

| Item              | Min | Тур      | Мах  | Min | Тур      | Max  | Unit | Test Conditions             |

| Resolution        | 8   | 8        | 8    | 8   | 8        | 8    | bit  |                             |

| Conversion time   | _   | _        | 10   | _   | _        | 10   | μs   | 20-pF capacitive load       |

| Absolute accuracy | —   | ±2.0     | ±3.0 | _   | ±1.0     | ±1.5 | LSB  | 2-M $\Omega$ resistive load |

|                   | _   | _        | ±2.0 | _   |          | ±1.0 | LSB  | 4-M $\Omega$ resistive load |

# 21.6 Usage Note

Although both the ZTAT and mask ROM versions fully meet the electrical specifications listed in this manual, due to differences in the fabrication process, the on-chip ROM, and the layout patterns, there will be differences in the actual values of the electrical characteristics, the operating margins, the noise margins, and other aspects.

Therefore, if a system is evaluated using the ZTAT version, a similar evaluation should also be performed using the mask ROM version.

| Mnemonic         Operand Size           ADD         ADD.B #xx:8,Rd         B         2           ADD.B Rs,Rd         B         2         4           ADD.M #xx:16,Rd         W         4         4           ADD.W Rs,Rd         B         2         4           ADD.W Rs,Rd         W         4         4           ADD.W Rs,Rd         W         4         4           ADD.U Rs,Rd         W         4         4           ADD.L ERS,ERd         L         6         2           ADDX         ADDX #xx:3,Rd         B         2           ADDX Rs,Rd         B         2         4           ADDX Rs,Rd         B         2         2           ADDX Rs,Rd         B         2         3         2           ADDS #1, ERd         L         L         2         2           ADDS #1, ERd         L         L         2         2 | 0 0 8 8 8 V   | @(q;ERn)<br>@ERn |            |             |    | <b>T</b>               |          |                   |                   |                                               |                   |                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|------------|-------------|----|------------------------|----------|-------------------|-------------------|-----------------------------------------------|-------------------|-----------------------------|

| Mnemonic     Operand Size       ADD.B #xx:8,Rd     B       ADD.B Rs,Rd     B       ADD.W rs,Rd     B       ADD.W rs,rl6,Rd     W       ADD.W rs,rd     W       ADD.W rs,rd     B       ADD.W rs,rd     B       ADD.W rs,rd     B       ADD.W rs,rd     B       ADD.K rs,rd     B       ADD.K rs,rd     C       ADD.L Ers, Erd     L       ADD X rs,rd     B       ADD X rs,rd     B       ADD X strad     L       ADD S #1, Erd     L       ADD S #1, Erd     L                                                                                                                                                                                                                                                                                                                                                                    | N N <b>Ku</b> |                  | 1          | _           |    |                        |          |                   |                   |                                               |                   |                             |

| Mnemonic         ADD.B #xx:8,Rd         B         2           ADD.B Rs,Rd         B         2         4           ADD.B Rs,Rd         B         2         4           ADD.W #xx:16,Rd         W         4         4           ADD.W Rs,Rd         W         4         4           ADD.W Rs,Rd         W         4         4           ADD.U Rs,Rd         W         4         4           ADD.L #xx:32,ERd         L         6         2           ADD.L ERS,ERd         L         6         2         4           ADDX #xx:8,Rd         B         2         4         2           ADDX RxS,Rd         B         2         4         2         4           ADDS #1,ERd         L         L         1         1         1                                                                                                           | N N K         |                  | 8∃@/u8∃    | а, PC)<br>а | 86 |                        |          | Cone              | Condition Code    | õ                                             | e                 | No. of States* <sup>1</sup> |

| ADD.B #xx.8,Rd       B       2         ADD.B Rs,Rd       B       3         ADD.M #xx:16,Rd       W       4         ADD.W Rs,Rd       W       4         ADD.W Rs,Rd       W       1         ADD.L ERs,ERd       L       6         ADD.L ERs,ERd       L       6         ADD.L ERs,FRd       L       6         ADD.K #xx:32,ERd       L       6         ADD.K #xr:32,ERd       L       6         ADD.K #xr:32,ERd       L       6         ADD.L ERs,FRd       L       6         ADDX #xx:8,Rd       B       2         ADDX #xx:8,Rd       L       1         ADDS #1,ERd       L       1         ADDS #2,ERd       L       1         ADDS #4,ERd       L       1                                                                                                                                                                      |               |                  | <b> -@</b> | в@<br>0)@   |    | Operation              |          | <u>т</u>          | z                 | ><br>2                                        | ပ                 | Normal Advanced             |

| ADD.B Rs,Rd       B         ADD.W #xx:16,Rd       W         ADD.W Rs,Rd       W         ADD.W Rs,Rdd       L         ADD.L ERS,ERdd       L         ADD.L ERS,ERdd       L         ADD.L ERS,FRdd       L         ADD.K #xx:8,Rd       B         ADDX #xx:8,Rd       B         ADDX Rs,Rd       B         ADDX SA:1,ERd       L         ADDS #1,ERdd       L         ADDS #2,ERd       L                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |                  |            |             |    | Rd8+#xx:8→Rd8          | 1        | $\leftrightarrow$ | $\leftrightarrow$ | $\leftrightarrow \\ \leftrightarrow$          | $\leftrightarrow$ | 1                           |

| ADD.W #xx:16,Rd         W         4           ADD.W Rs,Rd         W         N         N           ADD.L #xx:32,ERd         L         6           ADD.L ERs,ERd         L         6           ADD.L Ers,FRd         L         8         2           ADDX #xx:8,Rd         B         2         2           ADDX Rs,Rd         B         2         2           ADDX Rs,Rd         B         2         2           ADDX Rs,Rd         B         2         2           ADDS R1,ERd         L         1         1           ADDS #1,ERd         L         1         1                                                                                                                                                                                                                                                                    |               |                  |            |             |    | Rd8+Rs8→Rd8            | 1        | $\leftrightarrow$ | $\leftrightarrow$ | $\leftrightarrow \leftrightarrow \Rightarrow$ | $\leftrightarrow$ | 1                           |

| ADD.W Rs,Rd         W           ADD.L #xx:32,ERd         L         6           ADD.L ERs,ERd         L         6           ADD.L Ers,Rrd         B         2           ADDX #xx:8,Rd         B         2           ADDX Rs,Rd         B         2           ADDX Rs,Rd         B         2           ADDX Rs,Rd         B         2           ADDX Rs,Rd         B         2           ADDS #1,ERd         L         1           ADDS #2,ERd         L         1                                                                                                                                                                                                                                                                                                                                                                   |               |                  |            |             |    | Rd16+#xx:16→Rd16       | 1        | - [3]             | $\leftrightarrow$ | $\stackrel{\leftrightarrow}{\leftrightarrow}$ | $\leftrightarrow$ | 2                           |

| ADD.L #xx:32,ERd         L         6           ADD.L ERs,ERd         L         7           ADD.X #xx:8,Rd         B         2           ADDX Rs,Rd         B         2           ADDX Rs,Rd         B         1           ADDX state         L         1           ADDX state         L         1           ADDS #1,ERd         L         1           ADDS #2,ERd         L         1           ADDS #4,ERd         L         1                                                                                                                                                                                                                                                                                                                                                                                                    |               |                  |            |             |    | Rd16+Rs16→Rd16         |          | - [3]             | $\leftrightarrow$ | $\stackrel{\leftrightarrow}{\leftrightarrow}$ | $\leftrightarrow$ | +                           |

| ADD.L ERS, ERd         L           ADDX #xx:8, Rd         B         2           ADDX Rs, Rd         B         2           ADDX Rs, Rd         B         2           ADDS R1, ERd         L         1           ADDS #1, ERd         L         1           ADDS #4, ERd         L         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2             |                  |            |             |    | ERd32+#xx:32→ERd32     | 1        | — [4]             | $\leftrightarrow$ | $\stackrel{\leftrightarrow}{\leftrightarrow}$ | $\leftrightarrow$ | 3                           |

| ADDX #xx:8,RdBADDX Rs,RdBADDS #1,ERdLADDS #1,ERdLADDS #4,ERdL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                  |            |             |    | ERd32+ERs32→ERd32      | 1        | — [4]             | $\leftrightarrow$ | $\leftrightarrow \\ \leftrightarrow$          | $\leftrightarrow$ | -                           |

| ADDX Rs,RdBADDS #1,ERdLADDS #2,ERdLADDS #4,ERdL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                  |            |             |    | Rd8+#xx:8+C→Rd8        | 1        | $\leftrightarrow$ | $\leftrightarrow$ | [5] ¢                                         | $\leftrightarrow$ | 1                           |

| ADDS #1,ERd L<br>ADDS #2,ERd L<br>ADDS #4,ERd L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2             |                  |            |             |    | Rd8+Rs8+C→Rd8          | 1        | $\leftrightarrow$ | ↔                 | [5] ¢                                         | $\leftrightarrow$ | 1                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7             |                  |            |             |    | ERd32+1→ERd32          | 1        |                   |                   |                                               |                   | -                           |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2             |                  |            |             |    | ERd32+2→ERd32          | 1        |                   |                   |                                               | Ι                 | 1                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2             |                  |            |             |    | ERd32+4→ERd32          | 1        |                   |                   |                                               |                   | Ţ                           |

| INC INC.B Rd B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2             |                  |            |             |    | Rd8+1→Rd8              |          |                   | $\leftrightarrow$ | $\leftrightarrow \\ \leftrightarrow$          | Ι                 | ÷                           |

| INC.W #1,Rd W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ~             |                  |            |             |    | Rd16+1→Rd16            |          |                   | $\leftrightarrow$ | $\leftrightarrow \\ \leftrightarrow$          | Ι                 | -                           |

| INC.W #2,Rd W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2             |                  |            |             |    | Rd16+2→Rd16            |          |                   | $\leftrightarrow$ | $\leftrightarrow \\ \leftrightarrow$          |                   | -                           |

| INC.L #1,ERd L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2             |                  |            |             |    | ERd32+1→ERd32          | 1        |                   | $\leftrightarrow$ | $\stackrel{\leftrightarrow}{\leftrightarrow}$ |                   | L                           |

| INC.L #2,ERd L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2             |                  |            |             |    | ERd32+2→ERd32          | 1        |                   | $\leftrightarrow$ | $\leftrightarrow$ $\leftrightarrow$           |                   | Ţ                           |

| DAA DAA Rd B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2             |                  |            |             |    | Rd8 decimal adjust→Rd8 |          | *                 | $\leftrightarrow$ | *                                             | $\leftrightarrow$ | ÷                           |

| SUB SUB.B Rs,Rd B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2             |                  |            |             |    | Rd8-Rs8→Rd8            |          | $\leftrightarrow$ | $\leftrightarrow$ | $\leftrightarrow$ $\leftrightarrow$           | $\leftrightarrow$ | ÷                           |

| SUB.W #xx:16,Rd W 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                  |            |             |    | Rd16-#xx:16→Rd16       | $\vdash$ | - [3]             | $\leftrightarrow$ | $\leftrightarrow \\ \leftrightarrow$          | $\leftrightarrow$ | 2                           |

## Rev. 3.00 Sep 15, 2006 page 738 of 988 REJ09B0330-0300

(2) Arithmetic Instructions

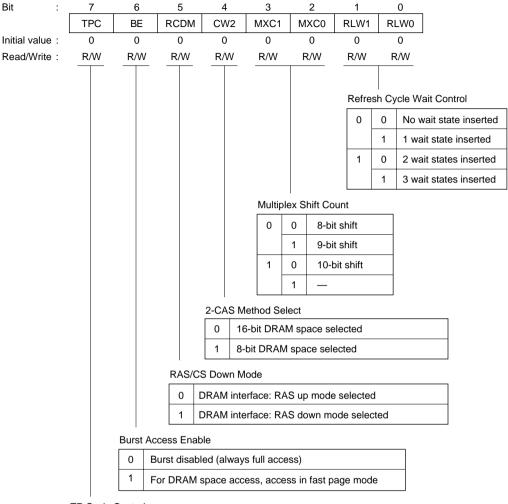

#### MCR—Memory Control Register

H'FED6

**Bus Controller**

| TP Cyc | le Control |  |

|--------|------------|--|

|--------|------------|--|

| 0 | 1-state precharge cycle is inserted |

|---|-------------------------------------|

| 1 | 2-state precharge cycle is inserted |

| PMR—PPG O       | utput Mod | le Registe | r            | Н                                                                  | ['FF47                     |            |            | PPG      |

|-----------------|-----------|------------|--------------|--------------------------------------------------------------------|----------------------------|------------|------------|----------|

| Bit :           | 7         | 6          | 5            | 4                                                                  | 3                          | 2          | 1          | 0        |

|                 | G3INV     | G2INV      | G1INV        | G0INV                                                              | <b>G3NOV</b>               | G2NOV      | G1NOV      | G0NOV    |

| Initial value : | 1         | 1          | 1            | 1                                                                  | 0                          | 0          | 0          | 0        |

| Read/Write :    | R/W       | R/W        | R/W          | R/W                                                                | R/W                        | R/W        | R/W        | R/W      |

|                 |           |            | Opera<br>0 N | Output Gro<br>tion Select<br>Normal ope<br>ralues upda<br>PU chann | ration in p<br>ated at cor | ulse outpu | It group n | · ·      |

|                 |           |            | (            | Non-overlag<br>independe<br>or B in the s<br>n = 3 to 0            | nt 1 and 0                 | output at  | compare r  | <b>U</b> |

|                 | Pulse Out | put Group  | n Direct/    | Inverted O                                                         | utput                      |            |            |          |

Inverted output for pulse output group n (low-level output at pin for a 1 in PODRH)

Direct output for pulse output group n (high-level output at pin for a 1 in PODRH)

Note: n = 3 to 0

| NDERH—Next Data Enable Registers H | H'FF48 | PPG |

|------------------------------------|--------|-----|

| NDERL—Next Data Enable Registers L | H'FF49 | PPG |

#### NDERH

| Bit           | : | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|---------------|---|--------|--------|--------|--------|--------|--------|-------|-------|

|               |   | NDER15 | NDER14 | NDER13 | NDER12 | NDER11 | NDER10 | NDER9 | NDER8 |

| Initial value | : | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| Read/Write    | : | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W   | R/W   |

|               |   |        |        |        |        |        |        |       |       |

#### Pulse Output Enable/Disable

| 0 | Pulse outputs PO15 to PO8 are disabled |

|---|----------------------------------------|

| 1 | Pulse outputs PO15 to PO8 are enabled  |

#### NDERL

| Bit           | : | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---------------|---|-------|-------|-------|-------|-------|-------|-------|-------|

|               |   | NDER7 | NDER6 | NDER5 | NDER4 | NDER3 | NDER2 | NDER1 | NDER0 |

| Initial value | : | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Read/Write    | : | R/W   |

|               |   |       |       |       |       |       |       |       |       |

Pulse Output Enable/Disable

| 0 | Pulse outputs PO7 to PO0 are disabled |

|---|---------------------------------------|

| 1 | Pulse outputs PO7 to PO0 are enabled  |