# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | AVR                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 23                                                                     |

| Program Memory Size        | 8KB (4K x 16)                                                          |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-TQFP                                                                |

| Supplier Device Package    | 32-TQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega8a-aur |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2. Configuration Summary

| Features                 | ATmega8A                           |

|--------------------------|------------------------------------|

| Pin count                | 32                                 |

| Flash (KB)               | 8                                  |

| SRAM (KB)                | 1                                  |

| EEPROM (Bytes)           | 512                                |

| General Purpose I/O pins | 23                                 |

| SPI                      | 1                                  |

| TWI (I <sup>2</sup> C)   | 1                                  |

| USART                    | 1                                  |

| ADC                      | 10-bit 15ksps                      |

| ADC channels             | 6 (8 in TQFP and QFN/MLF packages) |

| AC propagation delay     | Typ 400ns                          |

| 8-bit Timer/Counters     | 2                                  |

| 16-bit Timer/Counters    | 1                                  |

| PWM channels             | 3                                  |

| RC Oscillator            | +/-3%                              |

| Operating voltage        | 2.7 - 5.5V                         |

| Max operating frequency  | 16MHz                              |

| Temperature range        | -40°C to +105°C                    |

## 5.2. Accessing 16-bit Registers

The TCNT1, OCR1A/B, and ICR1 are 16-bit registers that can be accessed by the AVR CPU via the 8-bit data bus. A 16-bit register must be byte accessed using two read or write operations. The 16-bit timer has a single 8-bit register for temporary storing of the High byte of the 16-bit access. The same temporary register is shared between all 16-bit registers within the 16-bit timer. Accessing the Low byte triggers the 16-bit read or write operation. When the Low byte of a 16-bit register is written by the CPU, the High byte stored in the temporary register, and the Low byte written are both copied into the 16-bit register in the same clock cycle. When the Low byte of a 16-bit register is read by the CPU, the High byte of the 16-bit register is copied into the temporary register in the same clock cycle as the Low byte is read.

Not all 16-bit accesses uses the temporary register for the High byte. Reading the OCR1A/B 16-bit registers does not involve using the temporary register.

To do a 16-bit write, the High byte must be written before the Low byte. For a 16-bit read, the Low byte must be read before the High byte.

The following code examples show how to access the 16-bit Timer Registers assuming that no interrupts updates the temporary register. The same principle can be used directly for accessing the OCR1A/B and ICR1 Registers. Note that when using "C", the compiler handles the 16-bit access.

```

Assembly Code Example<sup>(1)</sup>

:.

; Set TCNT1 to 0x01FF

ldi r17,0x01

ldi r16,0xFF

out TCNT1H,r17

out TCNT1L,r16

; Read TCNT1 into r17:r16

in r16, TCNT1L

in

r17,TCNT1H

:.

C Code Example<sup>(1)</sup>

unsigned int i;

:.

/* Set TCNT1 to 0x01FF */

TCNT1 = 0 \times 1 FF;

/* Read TCNT1 into i */

i = TCNT1;

:.

```

Note: 1. See About Code Examples.

The assembly code example returns the TCNT1 value in the r17:r16 Register pair.

It is important to notice that accessing 16-bit registers are atomic operations. If an interrupt occurs between the two instructions accessing the 16-bit register, and the interrupt code updates the temporary register by accessing the same or any other of the 16-bit Timer Registers, then the result of the access outside the interrupt will be corrupted. Therefore, when both the main code and the interrupt code update the temporary register, the main code must disable the interrupts during the 16-bit access.

The following code examples show how to do an atomic read of the TCNT1 Register contents. Reading any of the OCR1A/B or ICR1 Registers can be done by using the same principle.

#### **Related Links**

Boot Loader Support – Read-While-Write Self-Programming on page 266 Memory Programming on page 283 Instruction Execution Timing on page 30

## 12.3. SRAM Data Memory

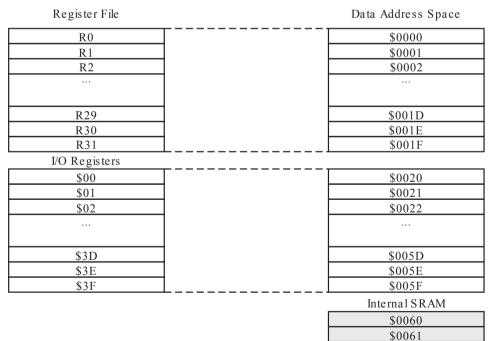

The figure below shows how the Atmel AVR ATmega8A SRAM Memory is organized.

The lower 1120 Data memory locations address the Register File, the I/O Memory, and the internal data SRAM. The first 96 locations address the Register File and I/O Memory, and the next 1024 locations address the internal data SRAM.

The five different addressing modes for the Data memory cover: Direct, Indirect with Displacement, Indirect, Indirect with Pre-decrement, and Indirect with Post-increment. In the Register File, registers R26 to R31 feature the indirect addressing pointer registers.

The direct addressing reaches the entire data space.

The Indirect with Displacement mode reaches 63 address locations from the base address given by the Y- or Z-register.

When using register indirect addressing modes with automatic pre-decrement and post-increment, the address registers X, Y and Z are decremented or incremented.

The 32 general purpose working registers, 64 I/O Registers, and the 1024 bytes of internal data SRAM in the ATmega8A are all accessible through all these addressing modes. The Register File is described in *General Purpose Register File*.

#### Figure 12-2 Data Memory Map

<u>\$045E</u> \$045F

#### **Related Links**

System and Reset Characteristics on page 305

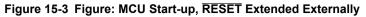

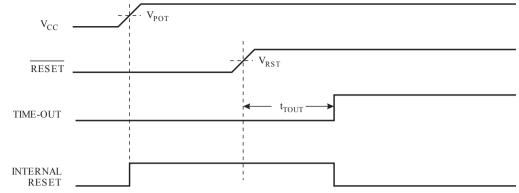

#### 15.2.2. External Reset

An External Reset is generated by a low level on the  $\overline{\text{RESET}}$  pin. Reset pulses longer than the minimum pulse width (see table in *System and Reset Characteristics*) will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset Threshold Voltage – V<sub>RST</sub> on its positive edge, the delay counter starts the MCU after the time-out period t<sub>TOUT</sub> has expired.

#### Figure 15-4 External Reset During Operation

**Related Links**

System and Reset Characteristics on page 305

## 15.2.3. Brown-out Detection

ATmega8A has an On-chip Brown-out Detection (BOD) circuit for monitoring the V<sub>CC</sub> level during operation by comparing it to a fixed trigger level. The trigger level for the BOD can be selected by the fuse BODLEVEL to be 2.7V (BODLEVEL unprogrammed), or 4.0V (BODLEVEL programmed). The trigger level has a hysteresis to ensure spike free Brown-out Detection. The hysteresis on the detection level should be interpreted as  $V_{BOT+} = V_{BOT} + V_{HYST}/2$  and  $V_{BOT-} = V_{BOT} - V_{HYST}/2$ .

The BOD circuit can be enabled/disabled by the fuse BODEN. When the BOD is enabled (BODEN programmed), and V<sub>CC</sub> decreases to a value below the trigger level (V<sub>BOT</sub>- in the figure below), the Brown-out Reset is immediately activated. When V<sub>CC</sub> increases above the trigger level (V<sub>BOT</sub>+ in the figure below), the delay counter starts the MCU after the time-out period t<sub>TOUT</sub> has expired.

The BOD circuit will only detect a drop in  $V_{CC}$  if the voltage stays below the trigger level for longer than  $t_{BOD}$  given in the table in *System and Reset Characteristics*.

| Adddress   | Labels | Code            |          | Comments                                   |

|------------|--------|-----------------|----------|--------------------------------------------|

| \$004      |        | out             | SPL,r16  |                                            |

| \$005      |        | sei             |          | ; Enable<br>interrupts                     |

| \$006      |        | <instr></instr> | XXX      |                                            |

| ;          |        |                 |          |                                            |

| .org \$c01 |        |                 |          |                                            |

| \$c01      |        | rjmp            | EXT_INT0 | ; IRQ Handler                              |

| \$c02      |        | rjmp            | EXT_INT1 | ; IRQ  Handler                             |

| :.         |        | :.              | :.       |                                            |

| \$c12      |        | rjmp            | SPM_RDY  | ; Store Program<br>Memory Ready<br>Handler |

When the BOOTRST Fuse is programmed and the boot section size set to 2K bytes, the most typical and general program setup for the Reset and Interrupt Vector Addresses is:

| Address    | Labels | Code            |                            | Comments                                |

|------------|--------|-----------------|----------------------------|-----------------------------------------|

| .org \$001 |        |                 |                            |                                         |

| \$001      |        | rjmp            | EXT_INT0                   | ; IRQ0 Handler                          |

| \$002      |        |                 | EXT_INT1                   | ; IRQ1 Handler                          |

| :.         |        | :.              | :.                         | ;                                       |

| \$012      |        | rjmp            | SPM_RDY                    | ; Store Program<br>Memory Handler       |

| ;          |        |                 |                            |                                         |

| .org \$c00 |        |                 |                            |                                         |

| \$c00      |        | rjmp            | RESET                      | ; Reset handler                         |

| ;          |        |                 |                            |                                         |

| \$c01      | RESET: | ldi             | r16,high(RAMEND)           | ; Main program<br>start                 |

| \$c02      |        | out             | SPH,r16                    | ; Set Stack<br>Pointer to top of<br>RAM |

| \$c03      |        | ldi             | r16,low(RAMENSPL,r<br>16D) |                                         |

| \$c04      |        | out             | SPL,r16                    |                                         |

| \$c05      |        | sei             |                            | ; Enable<br>interrupts                  |

| \$c06      |        | <instr></instr> | XXX                        |                                         |

## 17.1.3. GIFR – General Interrupt Flag Register

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses. The device is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

Name:

GIFR

Offset:

0x3A

Reset:

0

Property:

When addressing I/O Registers as data space the offset address is 0x5A

| Bit    | 7     | 6     | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|-------|-------|---|---|---|---|---|---|

|        | INTF1 | INTF0 |   |   |   |   |   |   |

| Access | R/W   | R/W   |   |   |   |   |   |   |

| Reset  | 0     | 0     |   |   |   |   |   |   |

## Bit 7 – INTF1: External Interrupt Flag 1

When an event on the INT1 pin triggers an interrupt request, INTF1 becomes set (one). If the I-bit in SREG and the INT1 bit in GICR are set (one), the MCU will jump to the corresponding Interrupt Vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. This flag is always cleared when INT1 is configured as a level interrupt.

## Bit 6 – INTF0: External Interrupt Flag 0

When an event on the INT0 pin triggers an interrupt request, INTF0 becomes set (one). If the I-bit in SREG and the INT0 bit in GICR are set (one), the MCU will jump to the corresponding Interrupt Vector. The flag is cleared when the interrupt routine is executed. Alternatively, the flag can be cleared by writing a logical one to it. This flag is always cleared when INT0 is configured as a level interrupt.

## 19.7.1. TCCR0 – Timer/Counter Control Register

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses. The device is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

Name:TCCR0Offset:0x33Reset:0Property:When addressing I/O Registers as data space the offset address is 0x53

| Bit    | 7 | 6 | 5 | 4 | 3 | 2    | 1    | 0    |

|--------|---|---|---|---|---|------|------|------|

|        |   |   |   |   |   | CS02 | CS01 | CS00 |

| Access |   |   |   |   |   | R/W  | R/W  | R/W  |

| Reset  |   |   |   |   |   | 0    | 0    | 0    |

#### Bits 2:0 – CS0n: Clock Select [n = 2:0]

The three clock select bits select the clock source to be used by the Timer/Counter.

| CS02 | CS01 | CS00 | Description                                             |

|------|------|------|---------------------------------------------------------|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped).                |

| 0    | 0    | 1    | clk <sub>I/O</sub> /(No prescaling)                     |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)                  |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64 (From prescaler)                 |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256 (From prescaler)                |

| 1    | 0    | 1    | clk <sub>I/O</sub> /1024 (From prescaler)               |

| 1    | 1    | 0    | External clock source on T0 pin. Clock on falling edge. |

| 1    | 1    | 1    | External clock source on T0 pin. Clock on rising edge.  |

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

N represents the prescale divider (1, 8, 64, 256, or 1024).

The extreme values for the OCR1x Register represents special cases when generating a PWM waveform output in the fast PWM mode. If the OCR1x is set equal to BOTTOM (0x0000) the output will be a narrow spike for each TOP+1 timer clock cycle. Setting the OCR1x equal to TOP will result in a constant high or low output (depending on the polarity of the output set by the COM1x1:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC1A to toggle its logical level on each Compare Match (COM1A1:0 = 1). This applies only if OCR1A is used to define the TOP value (WGM13:0 = 15). The waveform generated will have a maximum frequency of  $f_{OC1A} = f_{clk\_l/O}/2$  when OCR1A is set to zero (0x0000). This feature is similar to the OC1A toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode.

#### 21.9.4. Phase Correct PWM Mode

The *phase correct Pulse Width Modulation* or phase correct PWM mode (WGM13:0 = 1, 2, 3, 10, or 11) provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is, like the phase and frequency correct PWM mode, based on a dual-slope operation. The counter counts repeatedly from BOTTOM (0x0000) to TOP and then from TOP to BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC1x) is cleared on the Compare Match between TCNT1 and OCR1x while upcounting, and set on the Compare Match while downcounting. In inverting Output Compare mode, the operation is inverted. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

The PWM resolution for the phase correct PWM mode can be fixed to 8-, 9-, or 10-bit, or defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to 0x0003), and the maximum resolution is 16-bit (ICR1 or OCR1A set to MAX). The PWM resolution in bits can be calculated by using the following equation:

$$R_{\rm PCPWM} = \frac{\log(\rm TOP+1)}{\log(2)}$$

In phase correct PWM mode the counter is incremented until the counter value matches either one of the fixed values 0x00FF, 0x01FF, or 0x03FF (WGM13:0 = 1, 2, or 3), the value in ICR1 (WGM13:0 = 10), or the value in OCR1A (WGM13:0 = 11). The counter has then reached the TOP and changes the count direction. The TCNT1 value will be equal to TOP for one timer clock cycle. The timing diagram for the phase correct PWM mode is shown in the figure below. The figure shows phase correct PWM mode when OCR1A or ICR1 is used to define TOP. The TCNT1 value is in the timing diagram shown as a histogram for illustrating the dual-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT1 slopes represent compare matches between OCR1x and TCNT1. The OC1x Interrupt Flag will be set when a Compare Match occurs.

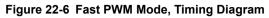

small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2 and TCNT2.

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches MAX. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC2 pin. Setting the COM21:0 bits to 2 will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM21:0 to 3 (refer to Table 22-4 Compare Output Mode, Fast PWM Mode(1) on page 162). The actual OC2 value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC2 Register at the Compare Match between OCR2 and TCNT2, and clearing (or setting) the OC2 Register at the timer clock cycle the counter is cleared (changes from MAX to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{\text{OCnPWM}} = \frac{f_{\text{clk}\_I/0}}{N \cdot 256}$$

The N variable represents the prescaler factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2 Register represent special cases when generating a PWM waveform output in the fast PWM mode. If the OCR2 is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR2 equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM21:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC2 to toggle its logical level on each Compare Match (COM21:0 = 1). The waveform generated will have a maximum frequency of  $f_{oc2} = f_{clk_l/O}/2$  when OCR2 is set to zero. This feature is similar to the OC2 toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode.

## 22.7.4. Phase Correct PWM Mode

The phase correct PWM mode (WGM21:0 = 1) provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is based on a dual-slope operation. The counter counts

Note: 1. See About Code Examples.

The following code examples show how to initialize the SPI as a Slave and how to perform a simple reception.

#### Assembly Code Example<sup>(1)</sup>

```

SPI_SlaveInit:

; Set MISO output, all others input

ldi   r17,(1<<DD MISO)

out   DDR_SPI,r17

; Enable SPI

ldi   r17,(1<<SPE)

out   SPCR,r17

ret

SPI_SlaveReceive:

; Wait for reception complete

sbis   SPSR,SPIF

rjmp   SPI_SlaveReceive

; Read received data and return

in   r16,SPDR

ret

```

#### C Code Example<sup>(1)</sup>

```

void SPI_SlaveInit(void)

{

/* Set MISO output, all others input */

DDR SPI = (1<<DD_MISO);

/* Enable SPI */

SPCR = (1<<SPE);

}

char SPI_SlaveReceive(void)

{

/* Wait for reception complete */

while(!(SPSR & (1<<SPIF)))

;

/* Return Data Register */

return SPDR;

}</pre>

```

Note: 1. See About Code Examples.

#### **Related Links**

Pin Configurations on page 13 Alternate Functions of Port B on page 83 Alternate Port Functions on page 81 About Code Examples on page 23

## 23.3. SS Pin Functionality

#### 23.3.1. Slave Mode

When the SPI is configured as a Slave, the Slave Select ( $\overline{SS}$ ) pin is always input. When  $\overline{SS}$  is held low, the SPI is activated, and MISO becomes an output if configured so by the user. All other pins are inputs.

## 24.2.1. AVR USART vs. AVR UART - Compatibility

The USART is fully compatible with the AVR UART regarding:

- Bit locations inside all USART Registers.

- Baud Rate Generation.

- Transmitter Operation.

- Transmit Buffer Functionality.

- Receiver Operation.

However, the receive buffering has two improvements that will affect the compatibility in some special cases:

- A second Buffer Register has been added. The two Buffer Registers operate as a circular FIFO buffer. Therefore the UDR must only be read once for each incoming data! More important is the fact that the Error Flags (FE and DOR) and the ninth data bit (RXB8) are buffered with the data in the receive buffer. Therefore the status bits must always be read before the UDR Register is read. Otherwise the error status will be lost since the buffer state is lost.

- The Receiver Shift Register can now act as a third buffer level. This is done by allowing the received data to remain in the serial Shift Register (see Block Diagram in previous section) if the Buffer Registers are full, until a new start bit is detected. The USART is therefore more resistant to Data OverRun (DOR) error conditions.

The following control bits have changed name, but have same functionality and register location:

- CHR9 is changed to UCSZ2.

- OR is changed to DOR.

## 24.3. Clock Generation

The clock generation logic generates the base clock for the Transmitter and Receiver. The USART supports four modes of clock operation: normal asynchronous, double speed asynchronous, Master synchronous and Slave Synchronous mode. The UMSEL bit in USART Control and Status Register C (UCSRC) selects between asynchronous and synchronous operation. Double speed (Asynchronous mode only) is controlled by the U2X found in the UCSRA Register. When using Synchronous mode (UMSEL = 1), the Data Direction Register for the XCK pin (DDR\_XCK) controls whether the clock source is internal (Master mode) or external (Slave mode). The XCK pin is only active when using Synchronous mode.

Below is a block diagram of the clock generation logic.

| Operating Mode                              | Equation for Calculating Baud<br>Rate <sup>(1)</sup> | Equation for Calculating UBRR<br>Value                         |

|---------------------------------------------|------------------------------------------------------|----------------------------------------------------------------|

| Asynchronous Normal<br>mode (U2X = 0)       | $BAUD = \frac{f_{OSC}}{16(UBRR + 1)}$                | $\mathbf{UBRR} = \frac{f_{\mathrm{OSC}}}{16\mathrm{BAUD}} - 1$ |

| Asynchronous Double<br>Speed mode (U2X = 1) | $BAUD = \frac{f_{OSC}}{8(UBRR + 1)}$                 | $\mathbf{UBRR} = \frac{f_{\mathrm{OSC}}}{8\mathrm{BAUD}} - 1$  |

| Synchronous Master mode                     | $BAUD = \frac{f_{OSC}}{2(UBRR+1)}$                   | $\mathbf{UBRR} = \frac{f_{\mathrm{OSC}}}{2\mathrm{BAUD}} - 1$  |

Note: 1. The baud rate is defined to be the transfer rate in bit per second (bps).

**BAUD** Baud rate (in bits per second, bps).

fosc System oscillator clock frequency.

UBRR Contents of the UBRRH and UBRRL Registers, (0-4095).

Some examples of UBRR values for some system clock frequencies are found in Table 24-9 Examples of UBRR Settings for Commonly Used Oscillator Frequencies on page 207.

## 24.3.2. Double Speed Operation (U2X)

The transfer rate can be doubled by setting the U2X bit in UCSRA. Setting this bit only has effect for the asynchronous operation. Set this bit to zero when using synchronous operation.

Setting this bit will reduce the divisor of the baud rate divider from 16 to 8, effectively doubling the transfer rate for asynchronous communication. Note however that the Receiver will in this case only use half the number of samples (reduced from 16 to 8) for data sampling and clock recovery, and therefore a more accurate baud rate setting and system clock are required when this mode is used.

For the Transmitter, there are no downsides.

## 24.3.3. External Clock

External clocking is used by the synchronous slave modes of operation. The description in this section refers to Figure 24-2 Clock Generation Logic, Block Diagram on page 183.

External clock input from the XCK pin is sampled by a synchronization register to minimize the chance of meta-stability. The output from the synchronization register must then pass through an edge detector before it can be used by the Transmitter and Receiver. This process introduces a two CPU clock period delay and therefore the maximum external XCK clock frequency is limited by the following equation:

$$f_{\rm XCK} < \frac{f_{\rm OSC}}{4}$$

The value of  $f_{osc}$  depends on the stability of the system clock source. It is therefore recommended to add some margin to avoid possible loss of data due to frequency variations.

## 24.3.4. Synchronous Clock Operation

When Synchronous mode is used (UMSEL = 1), the XCK pin will be used as either clock input (Slave) or clock output (Master). The dependency between the clock edges and data sampling or data change is the same. The basic principle is that data input (on RxD) is sampled at the opposite XCK clock edge of the edge the data output (TxD) is changed.

#### Bit 1 – RXB8: Receive Data Bit 8

RXB8 is the ninth data bit of the received character when operating with serial frames with nine data bits. Must be read before reading the low bits from UDR.

#### Bit 0 – TXB8: Transmit Data Bit 8

TXB8 is the ninth data bit in the character to be transmitted when operating with serial frames with nine data bits. Must be written before writing the low bits to UDR.

- 1. The transfer must be initiated.

- 2. The EEPROM must be instructed what location should be read.

- 3. The reading must be performed.

- 4. The transfer must be finished.

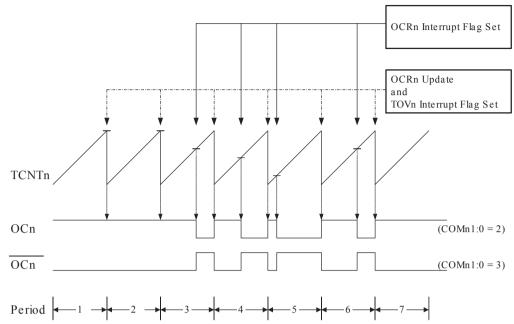

Note that data is transmitted both from Master to Slave and vice versa. The Master must instruct the Slave what location it wants to read, requiring the use of the MT mode. Subsequently, data must be read from the Slave, implying the use of the MR mode. Thus, the transfer direction must be changed. The Master must keep control of the bus during all these steps, and the steps should be carried out as an atomical operation. If this principle is violated in a multimaster system, another Master can alter the data pointer in the EEPROM between steps 2 and 3, and the Master will read the wrong data location. Such a change in transfer direction is accomplished by transmitting a REPEATED START between the transmission of the address byte and reception of the data. After a REPEATED START, the Master keeps ownership of the bus. The following figure shows the flow in this transfer.

#### Figure 25-19 Combining Several TWI Modes to Access a Serial EEPROM

## 25.7. Multi-master Systems and Arbitration

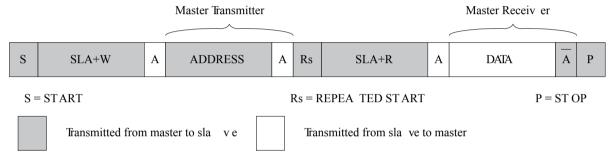

If multiple masters are connected to the same bus, transmissions may be initiated simultaneously by one or more of them. The TWI standard ensures that such situations are handled in such a way that one of the masters will be allowed to proceed with the transfer, and that no data will be lost in the process. An example of an arbitration situation is depicted below, where two masters are trying to transmit data to a Slave Receiver.

#### Figure 25-20 An Arbitration Example

Several different scenarios may arise during arbitration, as described below:

• Two or more masters are performing identical communication with the same Slave. In this case, neither the Slave nor any of the masters will know about the bus contention.

## 26.3.2. ACSR – Analog Comparator Control and Status Register

When using the I/O specific commands IN and OUT, the I/O addresses 0x00 - 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these offset addresses. The device is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

Name:

ACSR

Offset:

0x08

Reset:

N/A

Property:

When addressing I/O Registers as data space the offset address is 0x28

| Bit    | 7   | 6    | 5   | 4   | 3    | 2    | 1     | 0     |

|--------|-----|------|-----|-----|------|------|-------|-------|

| ĺ      | ACD | ACBG | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 |

| Access | R/W | R/W  | R   | R/W | R/W  | R/W  | R/W   | R/W   |

| Reset  | 0   | 0    | а   | 0   | 0    | 0    | 0     | 0     |

## Bit 7 – ACD: Analog Comparator Disable

When this bit is written logic one, the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. This will reduce power consumption in Active and Idle mode. When changing the ACD bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

## Bit 6 – ACBG: Analog Comparator Bandgap Select

When this bit is set, a fixed bandgap reference voltage replaces the positive input to the Analog Comparator. When this bit is cleared, AIN0 is applied to the positive input of the Analog Comparator. Refer to Internal Voltage Reference in System Control and Reset.

## Bit 5 – ACO: Analog Comparator Output

The output of the Analog Comparator is synchronized and then directly connected to ACO. The synchronization introduces a delay of 1 - 2 clock cycles.

## Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set by hardware when a comparator output event triggers the interrupt mode defined by ACIS1 and ACIS0. The Analog Comparator interrupt routine is executed if the ACIE bit is set and the I-bit in SREG is set. ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logic one to the flag.

## Bit 3 – ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is written logic one and the I-bit in the Status Register is set, the Analog Comparator interrupt is activated. When written logic zero, the interrupt is disabled.

## Bit 2 – ACIC: Analog Comparator Input Capture Enable

When written logic one, this bit enables the input capture function in Timer/Counter1 to be triggered by the Analog Comparator. The comparator output is in this case directly connected to the input capture front-end logic, making the comparator utilize the noise canceler and edge select features of the Timer/Counter1 Input Capture interrupt. When written logic zero, no connection between the Analog Comparator and the input capture function exists. To make the comparator trigger the Timer/Counter1 Input Capture interrupt, the ICIE1 bit in the Timer Interrupt Mask Register (TIMSK1) must be set.

#### 29.7.13. Reading the Calibration Byte

The algorithm for reading the Calibration byte is as follows (Please refer to Programming the Flash on page 289 for details on Command and Address loading):

- 1. Step A: Load Command "0000 1000".

- 2. Step B: Load Address Low byte, (0x00 0x03).

- 3. Set  $\overline{\text{OE}}$  to "0", and BS1 to "1". The Calibration byte can now be read at DATA.

- 4. Set OE to "1".

#### 29.7.14. Parallel Programming Characteristics

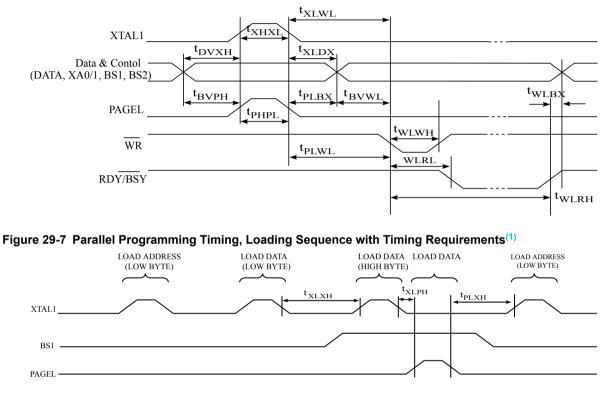

## Figure 29-6 Parallel Programming Timing, Including some General Timing Requirements

**Note:** 1. The timing requirements shown in the first figure in this section (i.e.,  $t_{DVXH}$ ,  $t_{XHXL}$ , and  $t_{XLDX}$ )

DATA (High Byte)

DATA (Low Byte)

also apply to loading operation.

ADDR0 (Low Byte)

DATA

XA0

# Atmel

ADDR1 (Low Byte)

## 30.6. SPI Timing Characteristics

See figures below for details.

## Table 30-7 SPI Timing Parameters

|    | Description                              | Mode   | Min     | Тур                                                                          | Max |    |

|----|------------------------------------------|--------|---------|------------------------------------------------------------------------------|-----|----|

| 1  | SCK period                               | Master |         | See Table 23-5 Relationship between SCK and Oscillator Frequency on page 177 |     |    |

| 2  | SCK high/low                             | Master |         | 50% duty cycle                                                               |     |    |

| 3  | Rise/Fall time                           | Master |         | 3.6                                                                          |     |    |

| 4  | Setup                                    | Master |         | 10                                                                           |     |    |

| 5  | Hold                                     | Master |         | 10                                                                           |     |    |

| 6  | Out to SCK                               | Master |         | 0.5 • t <sub>SCK</sub>                                                       |     |    |

| 7  | SCK to out                               | Master |         | 10                                                                           |     |    |

| 8  | SCK to out high                          | Master |         | 10                                                                           |     |    |

| 9  | $\overline{\text{SS}}$ low to out        | Slave  |         | 15                                                                           |     | ns |

| 10 | SCK period                               | Slave  | 4 • tck |                                                                              |     |    |

| 11 | SCK high/low <sup>(1)</sup>              | Slave  | 2 • tck |                                                                              |     |    |

| 12 | Rise/Fall time                           | Slave  |         |                                                                              | 1.6 |    |

| 13 | Setup                                    | Slave  | 10      |                                                                              |     |    |

| 14 | Hold                                     | Slave  | 10      |                                                                              |     |    |

| 15 | SCK to out                               | Slave  |         | 15                                                                           |     |    |

| 16 | SCK to $\overline{SS}$ high              | Slave  | 20      |                                                                              |     |    |

| 17 | $\overline{\text{SS}}$ high to tri-state | Slave  |         | 10                                                                           |     |    |

| 18 | $\overline{\text{SS}}$ low to SCK        | Salve  | 2 • tck |                                                                              |     |    |

#### Note:

1. In SPI Programming mode the minimum SCK high/low period is:

-  $2t_{CLCL}$  for  $f_{CK}$  < 12MHz

-  $3t_{CLCL}$  for  $f_{CK}$  > 12MHz

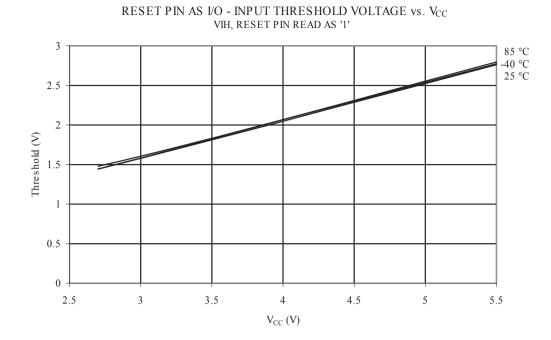

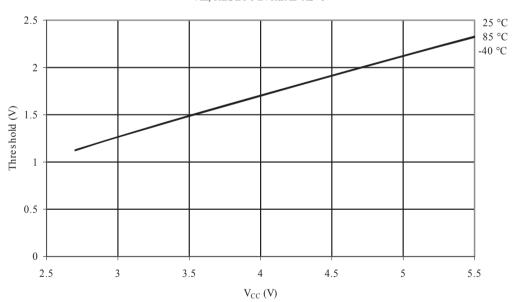

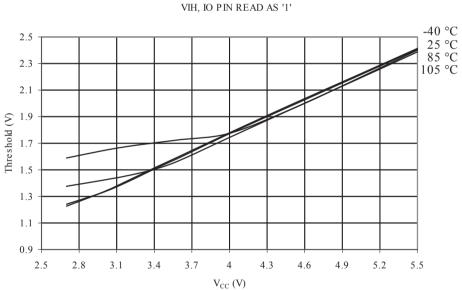

Figure 32-40 Reset Pin as I/O - Input Threshold Voltage vs. V<sub>CC</sub> (V<sub>IL</sub>, Reset Pin Read as "0")

Figure 32-39 Reset Pin as I/O - Input Threshold Voltage vs. V<sub>CC</sub> (V<sub>IH</sub>, Reset Pin Read as "1")

RESET PIN AS I/O - INPUT THRESHOLD VOLTAGE vs.  $V_{\rm CC}$  VIL, reset pin read as '0'

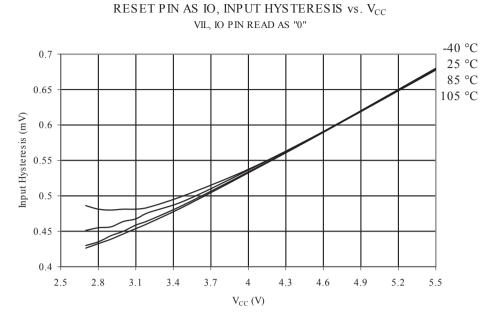

Figure 33-27 Reset Pin as I/O - Pin Hysteresis vs. V<sub>CC</sub>

Figure 33-28 Reset Input Threshold vs. V<sub>CC</sub> (V<sub>IH</sub> , Reset Pin Read as '1')

RESET INPUT THRESHOLD VOLTAGE vs.  $V_{CC}$  vih, 10 pin read as '1'

- Register descriptions are moved to sub section at the end of each chapter.

- New graphics in Typical Characteristics  $-TA = -40^{\circ}C$  to  $85^{\circ}C$ .

- New Ordering Information.