Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detalls                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 28-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj16ga002t-i-so |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

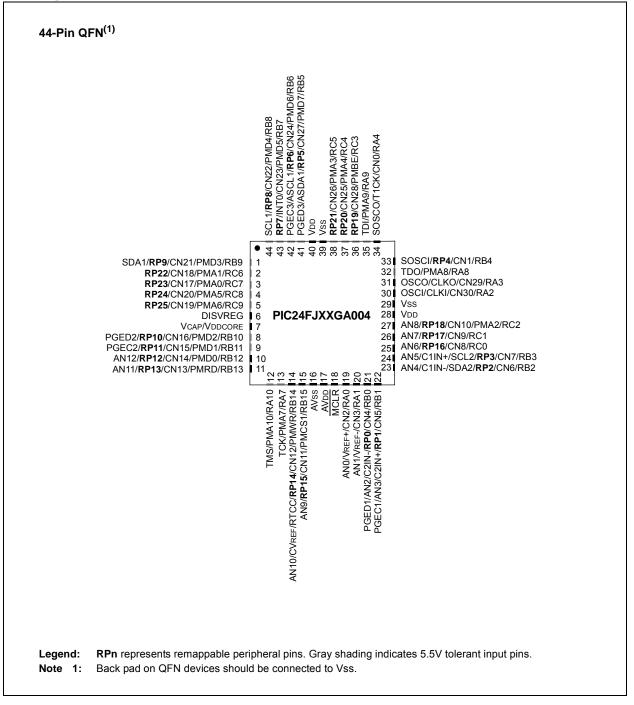

# **Pin Diagrams (Continued)**

# **Table of Contents**

| 1.0   | Device Overview                                                    | 7     |

|-------|--------------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-Bit Microcontrollers        | 17    |

| 3.0   | CPU                                                                | 23    |

| 4.0   | Memory Organization                                                | 29    |

| 5.0   | Flash Program Memory                                               | 47    |

| 6.0   | Resets                                                             | 53    |

| 7.0   | Interrupt Controller                                               | 59    |

| 8.0   | Oscillator Configuration                                           | 95    |

| 9.0   | Power-Saving Features                                              | . 103 |

| 10.0  | I/O Ports                                                          | . 105 |

| 11.0  | Timer1                                                             | . 125 |

| 12.0  | Timer2/3 and Timer4/5                                              | . 127 |

| 13.0  | Input Capture                                                      | . 133 |

| 14.0  | Output Compare                                                     | . 135 |

| 15.0  | Serial Peripheral Interface (SPI)                                  |       |

| 16.0  | Inter-Integrated Circuit (I <sup>2</sup> C <sup>™</sup> )          | . 151 |

| 17.0  | Universal Asynchronous Receiver Transmitter (UART)                 | . 159 |

|       | Parallel Master Port (PMP)                                         |       |

| 19.0  | Real-Time Clock and Calendar (RTCC)                                |       |

| 20.0  | Programmable Cyclic Redundancy Check (CRC) Generator               | . 189 |

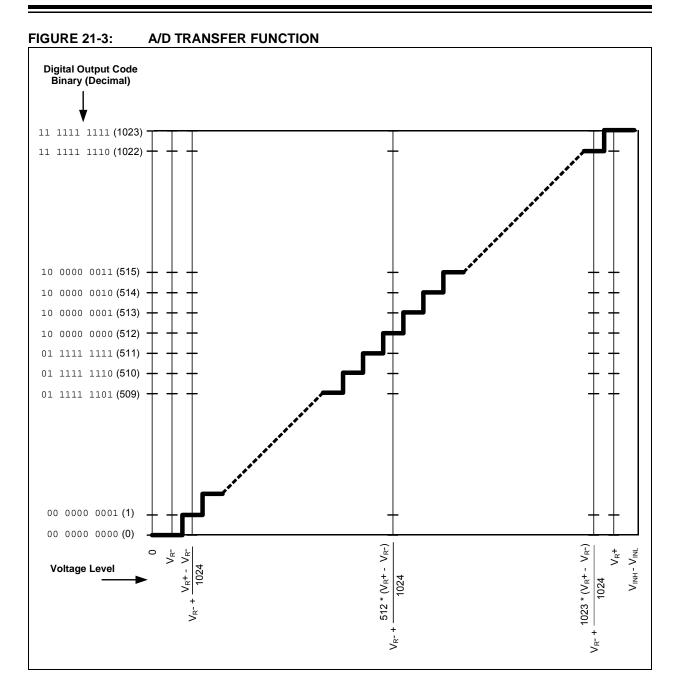

| 21.0  | 10-Bit High-Speed A/D Converter                                    | . 193 |

| 22.0  | Comparator Module                                                  | 203   |

| 23.0  | Comparator Voltage Reference                                       | 207   |

| 24.0  | Special Features                                                   | 209   |

| 25.0  | Development Support                                                | 219   |

| 26.0  | Instruction Set Summary                                            | 223   |

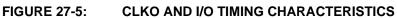

| 27.0  | Electrical Characteristics                                         | . 231 |

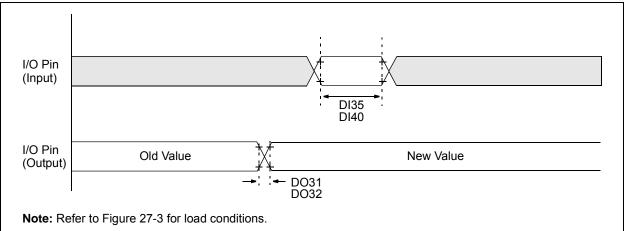

| 28.0  | Packaging Information                                              | 251   |

|       | ndix A: Revision History                                           |       |

| Appe  | ndix B: Additional Guidance for PIC24FJ64GA004 Family Applications | 268   |

| Index |                                                                    | 269   |

| The N | /icrochip Web Site                                                 | . 273 |

| Custo | mer Change Notification Service                                    | 273   |

| Custo | mer Support                                                        | . 273 |

| Read  | er Response                                                        | . 274 |

| Produ | Ict Identification System                                          | 275   |

| Function | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer   | Description                                                                                |  |

|----------|-------------------------------|---------------|--------------------|-----|-------------------|--------------------------------------------------------------------------------------------|--|

| OSCI     | 9                             | 6             | 30                 | Ι   | ANA               | Main Oscillator Input Connection.                                                          |  |

| OSCO     | 10                            | 7             | 31                 | 0   | ANA               | Main Oscillator Output Connection.                                                         |  |

| PGEC1    | 5                             | 2             | 22                 | I/O | ST                | In-Circuit Debugger/Emulator and ICSP™ Programming                                         |  |

| PGEC2    | 22                            | 19            | 9                  | I/O | ST                | Clock.                                                                                     |  |

| PGEC3    | 14                            | 12            | 42                 | I/O | ST                |                                                                                            |  |

| PGED1    | 4                             | 1             | 21                 | I/O | ST                | In-Circuit Debugger/Emulator and ICSP Programming                                          |  |

| PGED2    | 21                            | 18            | 8                  | I/O | ST                | Data.                                                                                      |  |

| PGED3    | 15                            | 11            | 41                 | I/O | ST                |                                                                                            |  |

| PMA0     | 10                            | 7             | 3                  | I/O | ST/TTL            | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |  |

| PMA1     | 12                            | 9             | 2                  | I/O | ST/TTL            | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |  |

| PMA2     | —                             | _             | 27                 | 0   | —                 | Parallel Master Port Address (Demultiplexed Master                                         |  |

| PMA3     | —                             | _             | 38                 | 0   | —                 | modes).                                                                                    |  |

| PMA4     | —                             | _             | 37                 | 0   | —                 |                                                                                            |  |

| PMA5     | —                             | _             | 4                  | 0   | —                 |                                                                                            |  |

| PMA6     | —                             | _             | 5                  | 0   | —                 |                                                                                            |  |

| PMA7     | —                             | _             | 13                 | 0   | —                 |                                                                                            |  |

| PMA8     | —                             | —             | 32                 | 0   | —                 |                                                                                            |  |

| PMA9     | —                             | _             | 35                 | 0   | —                 |                                                                                            |  |

| PMA10    | —                             | _             | 12                 | 0   | —                 |                                                                                            |  |

| PMA11    | —                             | —             | _                  | 0   | —                 |                                                                                            |  |

| PMA12    | —                             | _             | _                  | 0   | —                 |                                                                                            |  |

| PMA13    | —                             | _             | _                  | 0   | —                 |                                                                                            |  |

| PMBE     | 11                            | 8             | 36                 | 0   | —                 | Parallel Master Port Byte Enable Strobe.                                                   |  |

| PMCS1    | 26                            | 23            | 15                 | 0   | —                 | Parallel Master Port Chip Select 1 Strobe/Address Bit 14.                                  |  |

| PMD0     | 23                            | 20            | 10                 | I/O | ST/TTL            | Parallel Master Port Data (Demultiplexed Master mode) o                                    |  |

| PMD1     | 22                            | 19            | 9                  | I/O | ST/TTL            | Address/Data (Multiplexed Master modes).                                                   |  |

| PMD2     | 21                            | 18            | 8                  | I/O | ST/TTL            |                                                                                            |  |

| PMD3     | 18                            | 15            | 1                  | I/O | ST/TTL            |                                                                                            |  |

| PMD4     | 17                            | 14            | 44                 | I/O | ST/TTL            |                                                                                            |  |

| PMD5     | 16                            | 13            | 43                 | I/O | ST/TTL            |                                                                                            |  |

| PMD6     | 15                            | 12            | 42                 | I/O | ST/TTL            |                                                                                            |  |

| PMD7     | 14                            | 11            | 41                 | I/O | ST/TTL            |                                                                                            |  |

| PMRD     | 24                            | 21            | 11                 | 0   | _                 | Parallel Master Port Read Strobe.                                                          |  |

| PMWR     | 25                            | 22            | 14                 | 0   | _                 | Parallel Master Port Write Strobe.                                                         |  |

| Legend:  | TTL = TTL inp<br>ANA = Analog | level input/o | utput              |     | l <sup>2</sup> C™ | Schmitt Trigger input buffer<br>= I <sup>2</sup> C/SMBus input buffer                      |  |

#### TABLE 1-2: PIC24FJ64GA004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Note 1: Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

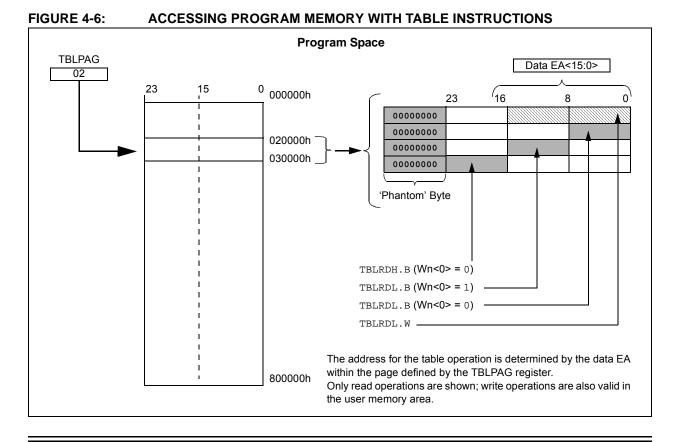

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only table read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 2 IDLE: Wake-up from Idle Flag bit 1 = Device has been in Idle mode

- 0 = Device has not been in Idle mode

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred (note that BOR is also set after a Power-on Reset)

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | —                       |

| POR (RCON<0>)     | POR                                               | —                       |

#### TABLE 6-1: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits may be set or cleared by the user software.

# 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the Oscillator Configuration bits. Refer to **Section 8.0 "Oscillator Configuration"** for further details.

#### TABLE 6-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | FNOSC<2:0> Configuration bits |

| BOR        | (CW2<10:8>)                   |

| MCLR       | COSC<2:0> Control bits        |

| WDTO       | (OSCCON<14:12>)               |

| SWR        |                               |

# 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. Note that the system Master Reset Signal, SYSRST, is released after the POR and PWRT delay times expire.

The time that the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| Reset Type         | Clock Source | SYSRST Delay        | System Clock<br>Delay | Notes         |

|--------------------|--------------|---------------------|-----------------------|---------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT + TRST | _                     | 1, 2, 7       |

|                    | FRC, FRCDIV  | TPOR + TPWRT + TRST | TFRC                  | 1, 2, 3, 7    |

|                    | LPRC         | TPOR + TPWRT + TRST | TLPRC                 | 1, 2, 3, 7    |

|                    | ECPLL        | TPOR + TPWRT + TRST | TLOCK                 | 1, 2, 4, 7    |

|                    | FRCPLL       | TPOR + TPWRT + TRST | TFRC + TLOCK          | 1, 2, 3, 4, 7 |

|                    | XT, HS, SOSC | TPOR + TPWRT + TRST | Tost                  | 1, 2, 5, 7    |

|                    | XTPLL, HSPLL | TPOR + TPWRT + TRST | Tost + Tlock          | 1, 2, 4, 5, 7 |

| BOR                | EC           | TPWRT + TRST        | —                     | 2, 7          |

|                    | FRC, FRCDIV  | TPWRT + TRST        | TFRC                  | 2, 3, 7       |

|                    | LPRC         | TPWRT + TRST        | TLPRC                 | 2, 3, 7       |

|                    | ECPLL        | TPWRT + TRST        | TLOCK                 | 2, 4, 7       |

|                    | FRCPLL       | TPWRT + TRST        | TFRC + TLOCK          | 2, 3, 4, 7    |

|                    | XT, HS, SOSC | TPWRT + TRST        | Tost                  | 2, 5, 7       |

|                    | XTPLL, HSPLL | TPWRT + TRST        | TFRC + TLOCK          | 2, 3, 4, 7    |

| All Others         | Any Clock    | TRST                | —                     | 7             |

## TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

Note 1: TPOR = Power-on Reset delay.

- **2:** TPWRT = 64 ms nominal if regulator is disabled (ENVREG tied to Vss).

- **3:** TFRC and TLPRC = RC Oscillator Start-up Times.

- **4:** TLOCK = PLL Lock Time.

- **5:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing the oscillator clock to the system.

- 6: If Two-Speed Start-up is enabled, regardless of the primary oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

- 7: TRST = Internal State Reset Timer

### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- · The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, will automatically be inserted after the POR and PWRT delay times. The FSCM will not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 100  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay will prevent an oscillator failure trap at a device Reset when the PWRT is disabled.

# 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the PIC24F CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of four registers. The Reset value for the Reset Control register, RCON, will depend on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, will depend on the type of Reset and the programmed values of the FNOSCx bits in the CW2 register (see Table 6-2). The RCFGCAL and NVMCON registers are only affected by a POR.

| U-0                   | R/W-1                                                                   | R/W-0                                                                                                                                                                                                                       | R/W-0                                                                              | U-0                                              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|-----------------|---------|--|--|--|--|--|

| —                     | CNIP2                                                                   | CNIP1                                                                                                                                                                                                                       | CNIP0                                                                              |                                                  | CMIP2           | CMIP1           | CMIP0   |  |  |  |  |  |

| bit 15                |                                                                         |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 | bit     |  |  |  |  |  |

| U-0                   | R/W-1                                                                   | R/W-0                                                                                                                                                                                                                       | R/W-0                                                                              | U-0                                              | R/W-1           | R/W-0           | R/W-0   |  |  |  |  |  |

|                       | MI2C1P2                                                                 | MI2C1P1                                                                                                                                                                                                                     | MI2C1P0                                                                            |                                                  | SI2C1P2         | SI2C1P1         | SI2C1P0 |  |  |  |  |  |

| bit 7                 |                                                                         | 11120111                                                                                                                                                                                                                    | 11120110                                                                           |                                                  | 012011 2        | 0120111         | bit     |  |  |  |  |  |

|                       |                                                                         |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 | _       |  |  |  |  |  |

| Legend:<br>R = Readab | ole bit                                                                 | W = Writable                                                                                                                                                                                                                | bit                                                                                | U = Unimple                                      | mented bit, rea | d as '0'        |         |  |  |  |  |  |

| -n = Value a          |                                                                         | '1' = Bit is set                                                                                                                                                                                                            |                                                                                    | '0' = Bit is cle                                 |                 | x = Bit is unkr | nown    |  |  |  |  |  |

|                       |                                                                         |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 |         |  |  |  |  |  |

| bit 15                | Unimplemen                                                              | ted: Read as '                                                                                                                                                                                                              | 0'                                                                                 |                                                  |                 |                 |         |  |  |  |  |  |

| bit 14-12             | CNIP<2:0>:                                                              | nput Change N                                                                                                                                                                                                               | otification Inte                                                                   | rrupt Priority bi                                | ts              |                 |         |  |  |  |  |  |

|                       | 111 = Interru                                                           | pt is Priority 7 (                                                                                                                                                                                                          | highest priority                                                                   | / interrupt)                                     |                 |                 |         |  |  |  |  |  |

|                       | •                                                                       |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 |         |  |  |  |  |  |

|                       | •                                                                       |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 |         |  |  |  |  |  |

|                       |                                                                         | 001 = Interrupt is Priority 1                                                                                                                                                                                               |                                                                                    |                                                  |                 |                 |         |  |  |  |  |  |

|                       |                                                                         | pt source is dis                                                                                                                                                                                                            |                                                                                    |                                                  |                 |                 |         |  |  |  |  |  |

| bit 11                | -                                                                       | Unimplemented: Read as '0'                                                                                                                                                                                                  |                                                                                    |                                                  |                 |                 |         |  |  |  |  |  |

| bit 10-8              |                                                                         | Comparator Inte                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 |         |  |  |  |  |  |

|                       | 111 = Interrupt is Priority 7 (highest priority interrupt)              |                                                                                                                                                                                                                             |                                                                                    |                                                  |                 |                 |         |  |  |  |  |  |

|                       |                                                                         |                                                                                                                                                                                                                             | rightest priority                                                                  | / interrupt)                                     |                 |                 |         |  |  |  |  |  |

|                       | •                                                                       |                                                                                                                                                                                                                             | nightest phones                                                                    | / interrupt)                                     |                 |                 |         |  |  |  |  |  |

|                       | •                                                                       |                                                                                                                                                                                                                             | night st phone                                                                     | / interrupt)                                     |                 |                 |         |  |  |  |  |  |

|                       | •<br>•<br>001 = Interru                                                 | pt is Priority 1                                                                                                                                                                                                            |                                                                                    | , interrupt)                                     |                 |                 |         |  |  |  |  |  |

| bit 7                 | •<br>•<br>001 = Interru<br>000 = Interru                                | pt is Priority 1<br>pt source is dis                                                                                                                                                                                        | abled                                                                              | , interrupt)                                     |                 |                 |         |  |  |  |  |  |

| bit 7<br>bit 6-4      | •<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen                  | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '                                                                                                                                                               | abled<br>0'                                                                        |                                                  |                 |                 |         |  |  |  |  |  |

| bit 7<br>bit 6-4      | •<br>•<br>• 001 = Interru<br>000 = Interru<br>Unimplemen<br>MI2C1P<2:0> | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1                                                                                                                                             | abled<br>o'<br>Event Interrup                                                      | t Priority bits                                  |                 |                 |         |  |  |  |  |  |

|                       | •<br>•<br>• 001 = Interru<br>000 = Interru<br>Unimplemen<br>MI2C1P<2:0> | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '                                                                                                                                                               | abled<br>o'<br>Event Interrup                                                      | t Priority bits                                  |                 |                 |         |  |  |  |  |  |

|                       | •<br>•<br>• 001 = Interru<br>000 = Interru<br>Unimplemen<br>MI2C1P<2:0> | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1                                                                                                                                             | abled<br>o'<br>Event Interrup                                                      | t Priority bits                                  |                 |                 |         |  |  |  |  |  |

|                       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (                                                                                                                       | abled<br>o'<br>Event Interrup                                                      | t Priority bits                                  |                 |                 |         |  |  |  |  |  |

|                       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1                                                                                                   | abled<br>o'<br>Event Interrup<br>highest priority                                  | t Priority bits                                  |                 |                 |         |  |  |  |  |  |

| bit 6-4               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                                                               | abled<br>o'<br>Event Interrup<br>highest priority<br>abled                         | t Priority bits                                  |                 |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '                                                      | abled<br><sup>0'</sup><br>Event Interrup<br>highest priority<br>abled              | t Priority bits<br>/ interrupt)                  |                 |                 |         |  |  |  |  |  |

|                       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis                                                                               | abled<br>o'<br>Event Interrup<br>highest priority<br>abled<br>o'<br>vent Interrupt | t Priority bits<br>/ interrupt)<br>Priority bits |                 |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Slave I2C1 E                                   | abled<br>o'<br>Event Interrup<br>highest priority<br>abled<br>o'<br>vent Interrupt | t Priority bits<br>/ interrupt)<br>Priority bits |                 |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br>•: Slave I2C1 E                                   | abled<br>o'<br>Event Interrup<br>highest priority<br>abled<br>o'<br>vent Interrupt | t Priority bits<br>/ interrupt)<br>Priority bits |                 |                 |         |  |  |  |  |  |

| bit 6-4<br>bit 3      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•      | pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br><b>:</b> Master I2C1<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ted:</b> Read as '<br><b>:</b> Slave I2C1 E<br>pt is Priority 7 ( | abled<br>o'<br>Event Interrup<br>highest priority<br>abled<br>o'<br>vent Interrupt | t Priority bits<br>/ interrupt)<br>Priority bits |                 |                 |         |  |  |  |  |  |

## REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | —   | T3CKR4 | T3CKR3 | T3CKR2 | T3CKR1 | T3CKR0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | T2CKR4 | T2CKR3 | T2CKR2 | T2CKR1 | T2CKR0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | read as '0'      |                      |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 T3CKR<4:0>: Assign Timer3 External Clock (T3CK) to the Corresponding RPn Pin bits

bit 7-5 Unimplemented: Read as '0'

bit 4-0 T2CKR<4:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn Pin bits

# REGISTER 10-4: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| _      | —   | —   | T5CKR4 | T5CKR3 | T5CKR2 | T5CKR1 | T5CKR0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | T4CKR4 | T4CKR3 | T4CKR2 | T4CKR1 | T4CKR0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 T5CKR<4:0>: Assign Timer5 External Clock (T5CK) to the Corresponding RPn Pin bits

bit 7-5 Unimplemented: Read as '0'

bit 4-0 T4CKR<4:0>: Assign Timer4 External Clock (T4CK) to the Corresponding RPn Pin bits

# REGISTER 10-23: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _      | —   | —   | RP17R4 <sup>(1)</sup> | RP17R3 <sup>(1)</sup> | RP17R2 <sup>(1)</sup> | RP17R1 <sup>(1)</sup> | RP17R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _     | —   | —   | RP16R4 <sup>(1)</sup> | RP16R3 <sup>(1)</sup> | RP16R2 <sup>(1)</sup> | RP16R1 <sup>(1)</sup> | RP16R0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|           |                            |

| bit 12-8 | <b>RP17R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP17 Output Pin bits <sup>(1)</sup> (see Table 10-3 for peripheral function numbers) |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-5  | Unimplemented: Read as '0'                                                                                                                              |

| bit 4-0  | <b>RP16R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP16 Output Pin bits <sup>(1)</sup>                                                  |

(see Table 10-3 for peripheral function numbers)

#### REGISTER 10-24: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | —   | RP19R4 <sup>(1)</sup> | RP19R3 <sup>(1)</sup> | RP19R2 <sup>(1)</sup> | RP19R1 <sup>(1)</sup> | RP19R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | —   | —   | RP18R4 <sup>(1)</sup> | RP18R3 <sup>(1)</sup> | RP18R2 <sup>(1)</sup> | RP18R1 <sup>(1)</sup> | RP18R0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

- bit 12-8 **RP19R<4:0>:** Peripheral Output Function is Assigned to RP19 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP18R<4:0>:** Peripheral Output Function is Assigned to RP18 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

- Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

| R/W-0                | U-0                                | R/W-0                                    | U-0             | U-0                 | R-0              | R-0             | R-0            |

|----------------------|------------------------------------|------------------------------------------|-----------------|---------------------|------------------|-----------------|----------------|

| SPIEN <sup>(1)</sup> | _                                  | SPISIDL                                  | _               | _                   | SPIBEC2          | SPIBEC1         | SPIBEC0        |

| bit 15               |                                    |                                          |                 |                     |                  | •               | bit 8          |

|                      |                                    |                                          |                 |                     |                  |                 |                |

| R-0                  | R/C-0                              | R/W-0                                    | R/W-0           | R/W-0               | R/W-0            | R-0             | R-0            |

| SRMPT                | SPIROV                             | SRXMPT                                   | SISEL2          | SISEL1              | SISEL0           | SPITBF          | SPIRBF         |

| bit 7                | ·                                  |                                          |                 |                     |                  | •               | bit 0          |

|                      |                                    |                                          |                 |                     |                  |                 |                |

| Legend:              |                                    | C = Clearable                            | bit             |                     |                  |                 |                |

| R = Readable         | e bit                              | W = Writable b                           | pit             | U = Unimplen        | nented bit, read | l as '0'        |                |

| -n = Value at        | POR                                | '1' = Bit is set                         |                 | '0' = Bit is clea   | ared             | x = Bit is unkr | iown           |

|                      |                                    |                                          |                 |                     |                  |                 |                |

| bit 15               | SPIEN: SPIX                        | Enable bit <sup>(1)</sup>                |                 |                     |                  |                 |                |

|                      | 1 = Enables n                      | nodule and cont                          | figures SCKx,   | SDOx, SDIx a        | nd SSx as seria  | al port pins    |                |

|                      | 0 = Disables r                     | module                                   |                 |                     |                  |                 |                |

| bit 14               | -                                  | ted: Read as '0                          |                 |                     |                  |                 |                |

| bit 13               |                                    | Ix Stop in Idle M                        |                 |                     |                  |                 |                |

|                      |                                    | ues module ope<br>s module operat        |                 |                     | le mode          |                 |                |

| bit 12-11            | Unimplemented: Read as '0'         |                                          |                 |                     |                  |                 |                |

| bit 10-8             | SPIBEC<2:0>                        | -: SPIx Buffer E                         | lement Count    | bits (valid in E    | nhanced Buffer   | mode)           |                |

|                      | Master mode:<br>Number of SF       | l<br>I transfers pend                    | ding.           |                     |                  |                 |                |

|                      | <u>Slave mode:</u><br>Number of SF | PI transfers unre                        | ad.             |                     |                  |                 |                |

| bit 7                | SRMPT: SPIX                        | Shift Register (                         | SPIxSR) Emp     | oty bit (valid in I | Enhanced Buffe   | er mode)        |                |

|                      | 1 = SPIx Shif                      | ft register is emp<br>ft register is not | oty and ready   | •                   |                  | ,               |                |

| bit 6                |                                    | x Receive Over                           |                 |                     |                  |                 |                |

|                      |                                    | te/word is comp                          | 0               | and discarded       | ; the user softw | are has not rea | d the previous |

|                      |                                    | e SPIxBUF regis<br>ow has occurre        |                 |                     |                  |                 | ·              |

| bit 5                | SRXMPT: SP                         | Ix Receive FIFC                          | ) Empty bit (va | alid in Enhance     | d Buffer mode)   | 1               |                |

|                      | 1 = Receive I                      | FIFO is empty                            |                 |                     |                  |                 |                |

|                      | 0 = Receive I                      | FIFO is not emp                          | oty             |                     |                  |                 |                |

| bit 4-2              |                                    | SPIx Buffer Inte                         | -               |                     |                  | node)           |                |

|                      |                                    | pt when the SP                           |                 |                     |                  |                 | 4.             |

|                      |                                    | pt when the last<br>pt when the last     |                 |                     |                  | •               | ty             |

|                      |                                    | pt when one da                           |                 |                     |                  |                 | one open spot  |

|                      |                                    | pt when the SP                           |                 | •                   | ,                |                 |                |

|                      |                                    | pt when the SP<br>pt when data is        |                 |                     |                  | a aat)          |                |

|                      | 000 = Interru                      | pt when the la<br>IPT bit is set)        |                 |                     | •                | ,               | uffer is empty |

|                      |                                    | se functions mu<br>Select (PPS)" f       |                 |                     | Pn pins before   | use. See Sect   | ion 10.4       |

#### REGISTER 15-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

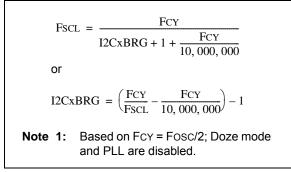

# 16.3 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 16-1.

### EQUATION 16-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

# TABLE 16-1: I<sup>2</sup>C<sup>™</sup> CLOCK RATES<sup>(1)</sup>

# 16.4 Slave Address Masking

The I2CxMSK register (Register 16-3) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '00100000', the slave module will detect both addresses, '00000000' and '00100000'.

To enable address masking, the IPMI (Intelligent Peripheral Management Interface) must be disabled by clearing the IPMIEN bit (I2CxCON<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 16-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Required       | _      | I2CxB     | RG Value      | Actual    |

|----------------|--------|-----------|---------------|-----------|

| System<br>FscL | Fcy    | (Decimal) | (Hexadecimal) | FSCL      |

| 100 kHz        | 16 MHz | 157       | 9D            | 100 kHz   |

| 100 kHz        | 8 MHz  | 78        | 4E            | 100 kHz   |

| 100 kHz        | 4 MHz  | 39        | 27            | 99 kHz    |

| 400 kHz        | 16 MHz | 37        | 25            | 404 kHz   |

| 400 kHz        | 8 MHz  | 18        | 12            | 404 kHz   |

| 400 kHz        | 4 MHz  | 9         | 9             | 385 kHz   |

| 400 kHz        | 2 MHz  | 4         | 4             | 385 kHz   |

| 1 MHz          | 16 MHz | 13        | D             | 1.026 MHz |

| 1 MHz          | 8 MHz  | 6         | 6             | 1.026 MHz |

| 1 MHz          | 4 MHz  | 3         | 3             | 0.909 MHz |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

# TABLE 16-2: $I^2 C^{TM} RESERVED ADDRESSES^{(1)}$

| Slave<br>Address | R/W<br>Bit | Description                            |

|------------------|------------|----------------------------------------|

| 0000 000         | 0          | General Call Address <sup>(2)</sup>    |

| 0000 000         | 1          | Start Byte                             |

| 0000 001         | x          | Cbus Address                           |

| 0000 010         | x          | Reserved                               |

| 0000 011         | x          | Reserved                               |

| 0000 1xx         | x          | HS Mode Master Code                    |

| 1111 1xx         | x          | Reserved                               |

| 1111 0xx         | х          | 10-Bit Slave Upper Byte <sup>(3)</sup> |

Note 1: The address bits listed here will never cause an address match, independent of the address mask settings.

2: The address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

| R-0                   | R/W-0                 | R/W-0            | R/W-0                                | R/W-0             | R/W-0                                                                 | R/W-0                               | R/W-0                 |

|-----------------------|-----------------------|------------------|--------------------------------------|-------------------|-----------------------------------------------------------------------|-------------------------------------|-----------------------|

| BUSY                  | IRQM1                 | IRQM0            | INCM1                                | INCM0             | MODE16                                                                | MODE1                               | MODE0                 |

| bit 15                | 1                     |                  |                                      |                   |                                                                       |                                     | bit 8                 |

|                       |                       |                  |                                      |                   |                                                                       | <b>D</b> 444 A                      | 5444.6                |

| R/W-0                 | R/W-0                 | R/W-0            | R/W-0                                | R/W-0             | R/W-0                                                                 | R/W-0                               | R/W-0                 |

| WAITB1 <sup>(1)</sup> | WAITB0 <sup>(1)</sup> | WAITM3           | WAITM2                               | WAITM1            | WAITM0                                                                | WAITE1 <sup>(1)</sup>               | WAITE0 <sup>(1)</sup> |

| bit 7                 |                       |                  |                                      |                   |                                                                       |                                     | bit (                 |

| Legend:               |                       |                  |                                      |                   |                                                                       |                                     |                       |

| R = Readable          | e bit                 | W = Writable     | bit                                  | U = Unimplen      | nented bit, read                                                      | d as '0'                            |                       |

| -n = Value at         | POR                   | '1' = Bit is set |                                      | '0' = Bit is clea |                                                                       | x = Bit is unkr                     | nown                  |

|                       |                       |                  |                                      |                   |                                                                       |                                     |                       |

| bit 15                | BUSY: Busy b          | bit (Master mod  | de only)                             |                   |                                                                       |                                     |                       |

|                       | 1 = Port is bu        | usy (not useful  | when the proce                       | essor stall is ac | tive)                                                                 |                                     |                       |

|                       | 0 = Port is no        | ot busy          |                                      |                   |                                                                       |                                     |                       |

| bit 14-13             | IRQM<1:0>:            | Interrupt Reque  | est Mode bits                        |                   |                                                                       |                                     |                       |

|                       |                       |                  |                                      |                   |                                                                       | written (Buffer                     |                       |

|                       |                       |                  |                                      |                   |                                                                       | PSP mode onl                        | у)                    |

|                       |                       |                  | ed, processor s<br>at the end of the |                   |                                                                       |                                     |                       |

|                       |                       | rupt is generate |                                      |                   |                                                                       |                                     |                       |

| bit 12-11             |                       | ncrement Mod     |                                      |                   |                                                                       |                                     |                       |

|                       | 11 = PSP rea          | id and write bu  | ffers auto-incre                     | ment (Legacy      | PSP mode only                                                         | /)                                  |                       |

|                       |                       |                  | 0:0> by 1 every                      |                   |                                                                       |                                     |                       |

|                       |                       |                  | 0> by 1 every r                      | •                 | 9                                                                     |                                     |                       |

| hit 10                |                       |                  | ment of addres                       | S                 |                                                                       |                                     |                       |

| bit 10                |                       | 6-Bit Mode bit   | taria 10 hita a                      | read envirite to  | the Deterratio                                                        |                                     |                       |

|                       |                       |                  |                                      |                   |                                                                       | ter invokes two<br>er invokes one 8 |                       |

| bit 9-8               |                       | -                | lode Select bits                     |                   | ne Bata regiote                                                       |                                     |                       |

| bit 0 0               |                       |                  |                                      |                   | MRE PMA <x.< td=""><td>)&gt; and PMD&lt;7:</td><td>·0&gt;)</td></x.<> | )> and PMD<7:                       | ·0>)                  |

|                       |                       |                  |                                      |                   | A <x:0> and P</x:0>                                                   |                                     | .0- )                 |

|                       | 01 = Enhance          | ed PSP, contro   | l signals (PMR                       | D, PMWR, PM       | CS1, PMD<7:0                                                          | > and PMA<1:0                       |                       |

|                       | • •                   |                  | -                                    |                   |                                                                       | 1 and PMD<7:0                       | )>)                   |

| bit 7-6               | WAITB<1:0>:           | : Data Setup to  | Read/Write W                         | ait State Config  | guration bits <sup>(1)</sup>                                          |                                     |                       |

|                       |                       |                  | tiplexed addres                      | •                 |                                                                       |                                     |                       |

|                       |                       |                  | Itiplexed addres                     |                   |                                                                       |                                     |                       |

|                       |                       |                  | Itiplexed addres                     |                   |                                                                       |                                     |                       |

| bit 5-2               |                       |                  | Enable Strobe                        | -                 |                                                                       |                                     |                       |

| 511 0 2               |                       | of additional 15 |                                      | Walt Clate Col    | ingulation bito                                                       |                                     |                       |

|                       |                       |                  |                                      |                   |                                                                       |                                     |                       |

|                       |                       | of additional 1  |                                      |                   |                                                                       |                                     |                       |

|                       |                       | -                | cles (operatior/                     |                   |                                                                       |                                     |                       |

|                       |                       |                  |                                      |                   | - 4 <sup>1</sup> (1)                                                  |                                     |                       |

| bit 1-0               | WAITE<1:0>:           |                  | er Strobe Walt                       | State Configura   | ation dits."                                                          |                                     |                       |

| bit 1-0               | 11 = Wait of          | 4 Tcy            | er Strobe Wait                       | State Configura   | ation dits"                                                           |                                     |                       |

| bit 1-0               |                       | 4 Тсү<br>3 Тсү   | er Strobe Walt                       | State Configura   | ation dits."                                                          |                                     |                       |

## REGISTER 18-2: PMMODE: PARALLEL PORT MODE REGISTER

**Note 1:** WAITBx and WAITEx bits are ignored whenever WAITM<3:0> = 0000.

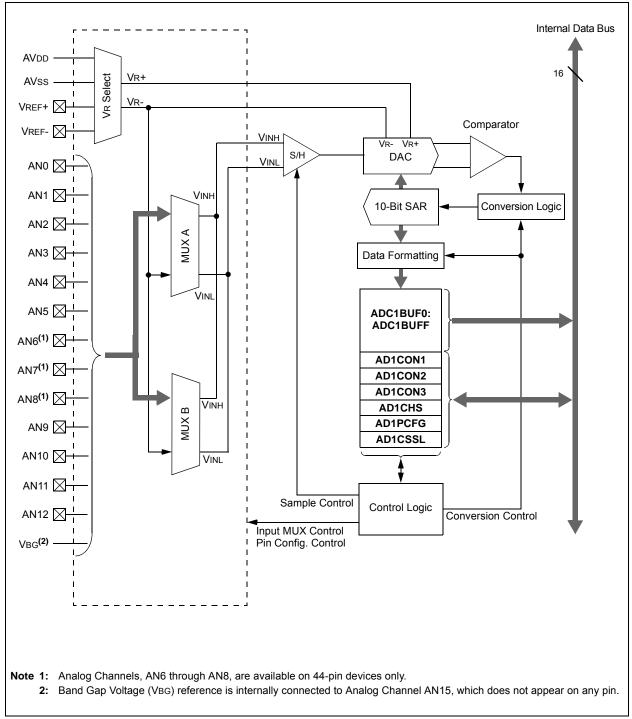

## FIGURE 21-1: 10-BIT HIGH-SPEED A/D CONVERTER BLOCK DIAGRAM

| R/W-0         | U-0                                                          | U-0                                                                              | U-0                                                            | R/W-0                             | R/W-0                   | R/W-0                      | R/W-0                   |

|---------------|--------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------|-------------------------|----------------------------|-------------------------|

| CH0NB         |                                                              |                                                                                  |                                                                | CH0SB3 <sup>(1,2)</sup>           | CH0SB2 <sup>(1,2)</sup> | CH0SB1 <sup>(1,2)</sup>    | CH0SB0 <sup>(1,2)</sup> |

| bit 15        |                                                              |                                                                                  |                                                                |                                   |                         |                            | bit 8                   |

|               |                                                              |                                                                                  |                                                                |                                   |                         |                            |                         |

| R/W-0         | U-0                                                          | U-0                                                                              | U-0                                                            | R/W-0                             | R/W-0                   | R/W-0                      | R/W-0                   |

| CH0NA         | —                                                            |                                                                                  | _                                                              | CH0SA3 <sup>(1,2)</sup>           | CH0SA2 <sup>(1,2)</sup> | CH0SA1 <sup>(1,2)</sup>    | CH0SA0 <sup>(1,2)</sup> |

| bit 7         |                                                              |                                                                                  |                                                                |                                   |                         |                            | bit (                   |