#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 16KB (5.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj16ga004-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

#### 4.1 **Program Address Space**

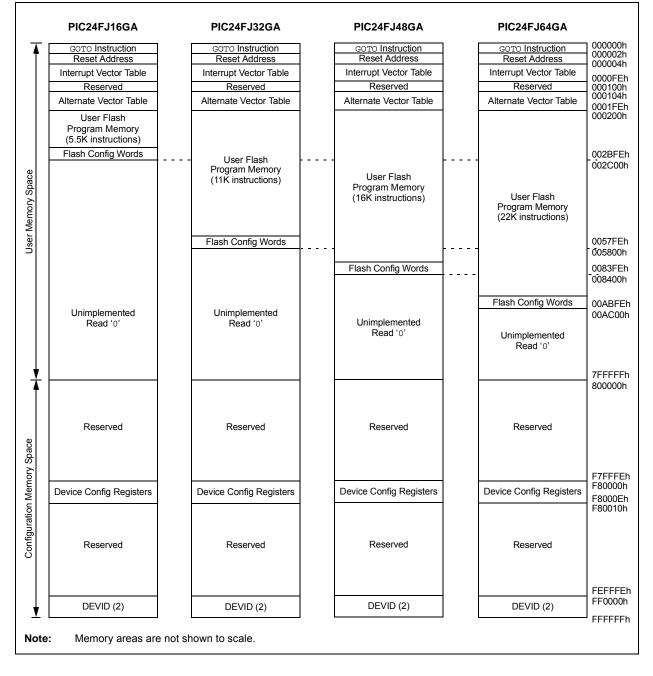

The program address memory space of the PIC24FJ64GA004 family devices is 4M instructions. The space is addressable by a 24-bit value derived

from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping, as described in **Section 4.3** "Interfacing **Program and Data Memory Spaces**".

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of TBLRD/TBLWT operations which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FJ64GA004 family of devices are shown in Figure 4-1.

### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with  $PIC^{\textcircled{s}}$  devices and improve data space memory usage efficiency, the PIC24F instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address (EA) calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word which contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A Sign-Extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions operate only on words.

### 4.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. The remainder of the data space is addressable indirectly. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing with a 16-bit address field.

### 4.2.4 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0000h to 07FFh, are primarily occupied with Special Function Registers (SFRs). These are used by the PIC24F core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A diagram of the SFR space, showing where SFRs are actually implemented, is shown in Table 4-2. Each implemented area indicates a 32-byte region where at least one address is implemented as an SFR. A complete listing of implemented SFRs, including their addresses, is shown in Tables 4-3 through 4-24.

|      |                                    |                | SFR    | Space Add | ress         |     |      |   |

|------|------------------------------------|----------------|--------|-----------|--------------|-----|------|---|

|      | xx00 xx20 xx40 xx60 xx80 xxA0 xxC0 |                |        |           |              |     | xxE0 |   |

| 000h | 000h Core                          |                |        | ICN       | Interrupts – |     |      | _ |

| 100h | Tim                                | Timers Capture |        |           | Compare      | —   | _    | _ |

| 200h | l <sup>2</sup> C™                  | ' UART S       |        | PI        |              |     | I/O  |   |

| 300h | A                                  | /D             | _      | —         | _            | —   | _    | _ |

| 400h | _                                  | —              |        | —         | _            | —   |      | _ |

| 500h | _                                  | _              | _      | —         | _            | —   | _    | _ |

| 600h | PMP                                | RTC/Comp       | CRC    | _         |              | PPS |      |   |

| 700h | —                                  | _              | System | NVM/PMD   | _            | —   | _    | _ |

TABLE 4-2:IMPLEMENTED REGIONS OF SFR DATA SPACE

**Legend:** — = No implemented SFRs in this block

| IABLE        | 4-Z1: | PERI   | PHERA  |        | SELEC                 | I REGIS               |                       | (223)                 |                       |       |       |       |                       |                       |                       |                       |                       |               |

|--------------|-------|--------|--------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------|

| File<br>Name | Addr  | Bit 15 | Bit 14 | Bit 13 | Bit 12                | Bit 11                | Bit 10                | Bit 9                 | Bit 8                 | Bit 7 | Bit 6 | Bit 5 | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 | All<br>Resets |

| RPINR0       | 0680  | —      | _      |        | INT1R4                | INT1R3                | INT1R2                | INT1R1                | INT1R0                | _     | _     | _     | _                     | —                     | _                     | _                     | _                     | 1F00          |

| RPINR1       | 0682  | _      | _      |        | _                     | _                     | _                     | _                     | _                     | _     | _     |       | INT2R4                | INT2R3                | INT2R2                | INT2R1                | INT2R0                | 001F          |

| RPINR3       | 0686  | _      | _      |        | T3CKR4                | T3CKR3                | T3CKR2                | T3CKR1                | T3CKR0                | _     | _     |       | T2CKR4                | T2CKR3                | T2CKR2                | T2CKR1                | T2CKR0                | 1F1F          |

| RPINR4       | 0688  | —      | —      | _      | T5CKR4                | T5CKR3                | T5CKR2                | T5CKR1                | T5CKR0                | —     | —     | -     | T4CKR4                | T4CKR3                | T4CKR2                | T4CKR1                | T4CKR0                | 1F1F          |

| RPINR7       | 068E  | —      | —      | _      | IC2R4                 | IC2R3                 | IC2R2                 | IC2R1                 | IC2R0                 | —     | —     | -     | IC1R4                 | IC1R3                 | IC1R2                 | IC1R1                 | IC1R0                 | 1F1F          |

| RPINR8       | 0690  | —      | —      | _      | IC4R4                 | IC4R3                 | IC4R2                 | IC4R1                 | IC4R0                 | —     | —     | -     | IC3R4                 | IC3R3                 | IC3R2                 | IC3R1                 | IC3R0                 | 1F1F          |

| RPINR9       | 0692  | _      | _      | _      | _                     | —                     | —                     | —                     | —                     | —     | —     | _     | IC5R4                 | IC5R3                 | IC5R2                 | IC5R1                 | IC5R0                 | 001F          |

| RPINR11      | 0696  | _      | _      | _      | OCFBR4                | OCFBR3                | OCFBR2                | OCFBR1                | OCFBR0                | —     | —     | _     | OCFAR4                | OCFAR3                | OCFAR2                | OCFAR1                | OCFAR0                | 1F1F          |

| RPINR18      | 06A4  | —      | —      | _      | U1CTSR4               | U1CTSR3               | U1CTSR2               | U1CTSR1               | U1CTSR0               | —     | —     | _     | U1RXR4                | U1RXR3                | U1RXR2                | U1RXR1                | U1RXR0                | 1F1F          |

| RPINR19      | 06A6  | —      | —      | _      | U2CTSR4               | U2CTSR3               | U2CTSR2               | U2CTSR1               | U2CTSR0               | —     | —     | _     | U2RXR4                | U2RXR3                | U2RXR2                | U2RXR1                | U2RXR0                | 1F1F          |

| RPINR20      | 06A8  | —      | —      | _      | SCK1R4                | SCK1R3                | SCK1R2                | SCK1R1                | SCK1R0                | —     | —     | _     | SDI1R4                | SDI1R3                | SDI1R2                | SDI1R1                | SDI1R0                | 1F1F          |

| RPINR21      | 06AA  | —      | —      | _      | —                     | —                     | —                     | —                     | —                     | —     | —     | _     | SS1R4                 | SS1R3                 | SS1R2                 | SS1R1                 | SS1R0                 | 001F          |

| RPINR22      | 06AC  | —      | _      | _      | SCK2R4                | SCK2R3                | SCK2R2                | SCK2R1                | SCK2R0                | _     | _     | _     | SDI2R4                | SDI2R3                | SDI2R2                | SDI2R1                | SDI2R0                | 1F1F          |

| RPINR23      | 06AE  | —      | —      | _      | _                     | _                     | _                     | _                     | —                     | _     | —     | _     | SS2R4                 | SS2R3                 | SS2R2                 | SS2R1                 | SS2R0                 | 001F          |

| RPOR0        | 06C0  | —      | —      | _      | RP1R4                 | RP1R3                 | RP1R2                 | RP1R1                 | RP1R0                 | —     | —     | _     | RP0R4                 | RP0R3                 | RP0R2                 | RP0R1                 | RP0R0                 | 0000          |

| RPOR1        | 06C2  | —      | —      | _      | RP3R4                 | RP3R3                 | RP3R2                 | RP3R1                 | RP3R0                 | _     | —     | _     | RP2R4                 | RP2R3                 | RP2R2                 | RP2R1                 | RP2R0                 | 0000          |

| RPOR2        | 06C4  | —      | —      | _      | RP5R4                 | RP5R3                 | RP5R2                 | RP5R1                 | RP5R0                 | —     | —     | _     | RP4R4                 | RP4R3                 | RP4R2                 | RP4R1                 | RP4R0                 | 0000          |

| RPOR3        | 06C6  | —      | —      | _      | RP7R4                 | RP7R3                 | RP7R2                 | RP7R1                 | RP7R0                 | —     | —     | _     | RP6R4                 | RP6R3                 | RP6R2                 | RP6R1                 | RP6R0                 | 0000          |

| RPOR4        | 06C8  | —      | —      | _      | RP9R4                 | RP9R3                 | RP9R2                 | RP9R1                 | RP9R0                 | —     | —     | _     | RP8R4                 | RP8R3                 | RP8R2                 | RP8R1                 | RP8R0                 | 0000          |

| RPOR5        | 06CA  | —      | —      | _      | RP11R4                | RP11R3                | RP11R2                | RP11R1                | RP11R0                | —     | _     | _     | RP10R4                | RP10R3                | RP10R2                | RP10R1                | RP10R0                | 0000          |

| RPOR6        | 06CC  | _      |        | _      | RP13R4                | RP13R3                | RP13R2                | RP13R1                | RP13R0                | _     | —     | _     | RP12R4                | RP12R3                | RP12R2                | RP12R1                | RP12R0                | 0000          |

| RPOR7        | 06CE  | _      |        | _      | RP15R4                | RP15R3                | RP15R2                | RP15R1                | RP15R0                | _     | —     | _     | RP14R4                | RP14R3                | RP14R2                | RP14R1                | RP14R0                | 0000          |

| RPOR8        | 06D0  | _      |        | _      |                       | RP17R3 <sup>(1)</sup> | RP17R2 <sup>(1)</sup> |                       |                       | _     | —     | _     | RP16R4 <sup>(1)</sup> |                       |                       | RP16R1 <sup>(1)</sup> |                       | 0000          |

| RPOR9        | 06D2  | —      | —      | —      | RP19R4 <sup>(1)</sup> |                       | RP19R2 <sup>(1)</sup> | RP19R1 <sup>(1)</sup> |                       | —     | —     | _     | RP18R4 <sup>(1)</sup> | RP18R3 <sup>(1)</sup> | RP18R2 <sup>(1)</sup> |                       |                       | 0000          |

| RPOR10       | 06D4  | —      |        |        | RP21R4 <sup>(1)</sup> |                       | RP21R2 <sup>(1)</sup> |                       |                       | —     | _     | _     | RP20R4 <sup>(1)</sup> |                       |                       | RP20R1 <sup>(1)</sup> |                       | 0000          |

| RPOR11       | 06D6  | —      |        |        |                       | RP23R3 <sup>(1)</sup> | RP23R2 <sup>(1)</sup> |                       |                       | _     | _     | _     | RP22R4 <sup>(1)</sup> | RP22R3 <sup>(1)</sup> |                       |                       |                       | 0000          |

| RPOR12       | 06D8  | —      | —      | _      | RP25R4 <sup>(1)</sup> | RP25R3 <sup>(1)</sup> | RP25R2 <sup>(1)</sup> | RP25R1 <sup>(1)</sup> | RP25R0 <sup>(1)</sup> | —     | —     | _     | RP24R4 <sup>(1)</sup> | RP24R3 <sup>(1)</sup> | RP24R2 <sup>(1)</sup> | RP24R1 <sup>(1)</sup> | RP24R0 <sup>(1)</sup> | 0000          |

#### TABLE 4-21: PERIPHERAL PIN SELECT REGISTER MAP (PPS)

Legend:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

These bits are only available on 44-pin devices; otherwise, they read as '0'.

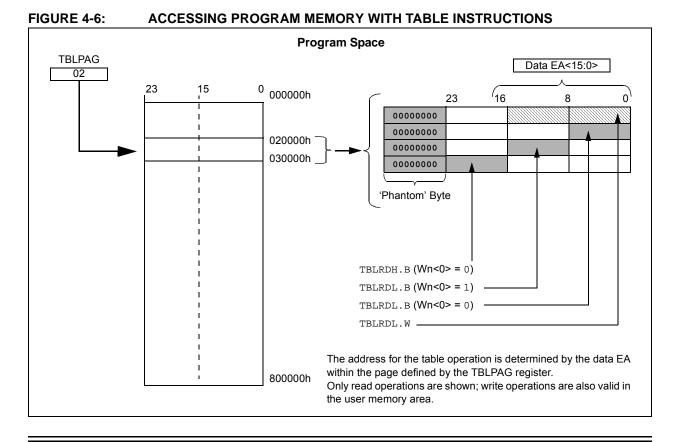

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'. In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

**Note:** Only table read operations will execute in the configuration memory space, and only then, in implemented areas, such as the Device ID. Table write operations are not allowed.

NOTES:

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "PIC24F Family Reference Manual", "Interrupts" (DS39707).

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24F CPU. It has the following features:

- Up to 8 processor exceptions and software traps

- 7 user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of 8 non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

PIC24FJ64GA004 family devices implement non-maskable traps and unique interrupts. These are summarized in Table 7-1 and Table 7-2.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset which forces the PC to zero. The micro-controller then begins program execution at location, 000000h. The user programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

# PIC24FJ64GA004 FAMILY

#### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| U-0          | U-0           | R/W-0                                                                                                                                    | U-0              | U-0               | U-0            | R/W-0           | U-0    |

|--------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|----------------|-----------------|--------|

|              | —             | PMPIF                                                                                                                                    | _                | _                 | _              | OC5IF           |        |

| bit 15       |               |                                                                                                                                          |                  | ·                 |                |                 | bit 8  |

|              |               |                                                                                                                                          |                  |                   |                |                 |        |

| R/W-0        | R/W-0         | R/W-0                                                                                                                                    | U-0              | U-0               | U-0            | R/W-0           | R/W-0  |

| IC5IF        | IC4IF         | IC3IF                                                                                                                                    | —                | —                 | _              | SPI2IF          | SPF2IF |

| bit 7        |               |                                                                                                                                          |                  |                   |                |                 | bit (  |

| Legend:      |               |                                                                                                                                          |                  |                   |                |                 |        |

| R = Readab   | le hit        | W = Writable I                                                                                                                           | hit              | U = Unimplen      | nented hit re: | ad as 'O'       |        |

| -n = Value a |               | '1' = Bit is set                                                                                                                         |                  | '0' = Bit is cle  | -              | x = Bit is unki | nwn    |

|              |               |                                                                                                                                          |                  |                   |                |                 | 101111 |

| bit 15-14    | Unimpleme     | ented: Read as '0                                                                                                                        | )'               |                   |                |                 |        |

| bit 13       | PMPIF: Para   | allel Master Port                                                                                                                        | Interrupt Flag   | g Status bit      |                |                 |        |

|              |               | t request has occ<br>t request has not                                                                                                   |                  |                   |                |                 |        |

| bit 12-10    | Unimpleme     | nted: Read as '0                                                                                                                         | )'               |                   |                |                 |        |

| bit 9        | OC5IF: Outp   | put Compare Cha                                                                                                                          | annel 5 Interr   | upt Flag Status I | bit            |                 |        |

|              |               | t request has occ<br>t request has not                                                                                                   |                  |                   |                |                 |        |

| bit 8        | Unimpleme     | nted: Read as '0                                                                                                                         | )'               |                   |                |                 |        |

| bit 7        |               | Capture Channe<br>t request has occ                                                                                                      |                  | Flag Status bit   |                |                 |        |

|              |               | t request has not                                                                                                                        |                  |                   |                |                 |        |

| bit 6        | IC4IF: Input  | Capture Channe                                                                                                                           | el 4 Interrupt I | Flag Status bit   |                |                 |        |

|              |               | t request has occ<br>t request has not                                                                                                   |                  |                   |                |                 |        |

| bit 5        | •             | •                                                                                                                                        |                  | Flag Status bit   |                |                 |        |

|              | 1 = Interrupt | IC3IF: Input Capture Channel 3 Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |                  |                   |                |                 |        |

| bit 4-2      | -             | ented: Read as '0                                                                                                                        |                  |                   |                |                 |        |

| bit 1        | •             |                                                                                                                                          |                  | oit               |                |                 |        |

|              | 1 = Interrupt | SPI2IF: SPI2 Event Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred             |                  |                   |                |                 |        |

| bit 0        | -             | 12 Fault Interrupt                                                                                                                       |                  | oit               |                |                 |        |

|              | 1 = Interrupt |                                                                                                                                          |                  |                   |                |                 |        |

# PIC24FJ64GA004 FAMILY

| R/W-0        | U-0                                                                              | R/W-0                                                                     | U-0                                                             | U-0              | U-0             | U-0              | U-0   |

|--------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|------------------|-----------------|------------------|-------|

| TON          |                                                                                  | TSIDL                                                                     | _                                                               | _                |                 | _                |       |

| bit 15       |                                                                                  |                                                                           |                                                                 |                  |                 |                  | bit 8 |

|              |                                                                                  |                                                                           |                                                                 |                  |                 |                  |       |

| U-0          | R/W-0                                                                            | R/W-0                                                                     | R/W-0                                                           | U-0              | R/W-0           | R/W-0            | U-0   |

| —            | TGATE                                                                            | TCKPS1                                                                    | TCKPS0                                                          | —                | TSYNC           | TCS              |       |

| bit 7        |                                                                                  |                                                                           |                                                                 |                  |                 |                  | bit ( |

| Legend:      |                                                                                  |                                                                           |                                                                 |                  |                 |                  |       |

| R = Readab   | le bit                                                                           | W = Writable                                                              | bit                                                             | U = Unimpler     | nented bit, rea | d as '0'         |       |

| -n = Value a | t POR                                                                            | '1' = Bit is set                                                          |                                                                 | '0' = Bit is cle |                 | x = Bit is unkno | own   |

|              |                                                                                  |                                                                           |                                                                 |                  |                 |                  |       |

| bit 15       | TON: Timer1                                                                      | On bit                                                                    |                                                                 |                  |                 |                  |       |

|              | 1 = Starts 16                                                                    |                                                                           |                                                                 |                  |                 |                  |       |

|              | 0 = Stops 16                                                                     | 6-bit Timer1                                                              |                                                                 |                  |                 |                  |       |

| bit 14       | Unimplemer                                                                       | nted: Read as '                                                           | )'                                                              |                  |                 |                  |       |

| bit 13       | TSIDL: Time                                                                      | r1 Stop in Idle N                                                         | lode bit                                                        |                  |                 |                  |       |

|              |                                                                                  | ues module op<br>s module opera                                           |                                                                 |                  | le mode         |                  |       |

| bit 12-7     |                                                                                  | nted: Read as '                                                           |                                                                 |                  |                 |                  |       |

| bit 6        | TGATE: Time                                                                      | er1 Gated Time                                                            | Accumulation                                                    | Enable bit       |                 |                  |       |

|              | When TCS =                                                                       | 1:                                                                        |                                                                 |                  |                 |                  |       |

|              | This bit is ign                                                                  | ored.                                                                     |                                                                 |                  |                 |                  |       |

|              | When TCS =                                                                       |                                                                           |                                                                 |                  |                 |                  |       |

|              |                                                                                  | me accumulatio<br>me accumulatio                                          |                                                                 |                  |                 |                  |       |

| bit 5-4      |                                                                                  | -: Timer1 Input                                                           |                                                                 | e Select bits    |                 |                  |       |

|              | 11 <b>= 1:256</b>                                                                | ·                                                                         |                                                                 |                  |                 |                  |       |

|              | 10 <b>= 1:64</b>                                                                 |                                                                           |                                                                 |                  |                 |                  |       |

|              | 01 = 1:8                                                                         |                                                                           |                                                                 |                  |                 |                  |       |

|              | 00 = 1:1                                                                         |                                                                           |                                                                 |                  |                 |                  |       |

| bit 3        | Unimplemented: Read as '0'                                                       |                                                                           |                                                                 |                  |                 |                  |       |

|              | bit 2 TSYNC: Timer1 External Clock Input Synchronization Select bit              |                                                                           |                                                                 |                  |                 |                  |       |

|              |                                                                                  |                                                                           |                                                                 | hronization Sel  | ect bit         |                  |       |

|              | When TCS =                                                                       | 1:                                                                        | ock Input Sync                                                  | hronization Sel  | ect bit         |                  |       |

|              | <u>When TCS =</u><br>1 = Synchro                                                 | <u>1:</u><br>nizes external o                                             | ock Input Sync                                                  |                  | ect bit         |                  |       |

|              | <u>When TCS =</u><br>1 = Synchro<br>0 = Does no                                  | <u>1:</u><br>onizes external o<br>ot synchronize e                        | ock Input Sync                                                  |                  | ect bit         |                  |       |

|              | <u>When TCS =</u><br>1 = Synchro                                                 | <u>1:</u><br>onizes external o<br>ot synchronize e<br><u>0:</u>           | ock Input Sync                                                  |                  | ect bit         |                  |       |

|              | When TCS =<br>1 = Synchro<br>0 = Does no<br>When TCS =<br>This bit is ign        | <u>1:</u><br>onizes external o<br>ot synchronize e<br><u>0:</u>           | ock Input Sync<br>clock input<br>external clock i               |                  | ect bit         |                  |       |

| bit 2        | When TCS =1 = Synchro0 = Does noWhen TCS =This bit is ignTCS: Timer11 = External | <u>1:</u><br>onizes external o<br>ot synchronize e<br><u>0:</u><br>nored. | ock Input Sync<br>clock input<br>external clock i<br>Gelect bit | nput             | ect bit         |                  |       |

# 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Serial Peripheral Interface (SPI)"* (DS39699)

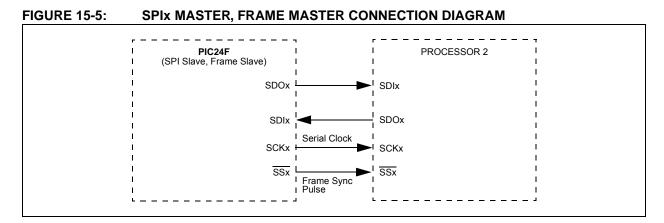

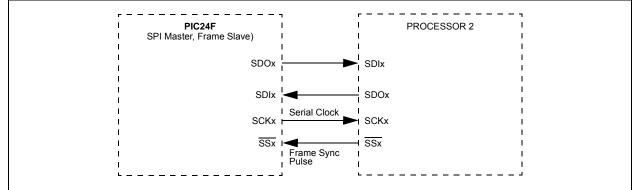

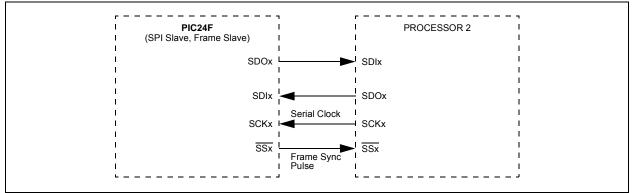

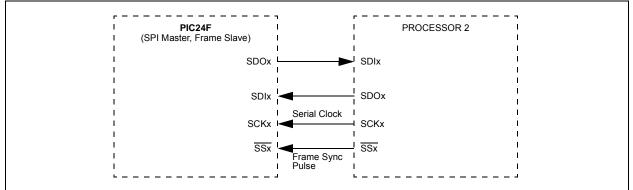

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the SPI and SIOP Motorola<sup>®</sup> interfaces.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

Note: Do not perform read-modify-write operations (such as bit-oriented instructions) on the SPIxBUF register in either Standard or Enhanced Buffer mode.

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The SPI serial interface consists of four pins:

- · SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 15-1 and Figure 15-2.

Depending on the pin count, PIC24FJ64GA004 family devices offer one or two SPI modules on a single device.

Note: In this section, the SPI modules are referred to together as SPIx or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON1 or SPIxCON2 refers to the control register for the SPI1 or SPI2 module. To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

- 5. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit (SPIxCON1<9>).

- 5. If the CKE bit is set, then the SSEN bit (SPIxCON1<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

© 2010-2013 Microchip Technology Inc.

# PIC24FJ64GA004 FAMILY

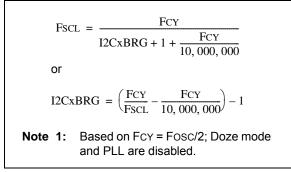

# 16.3 Setting Baud Rate When Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 16-1.

# EQUATION 16-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

# TABLE 16-1: I<sup>2</sup>C<sup>™</sup> CLOCK RATES<sup>(1)</sup>

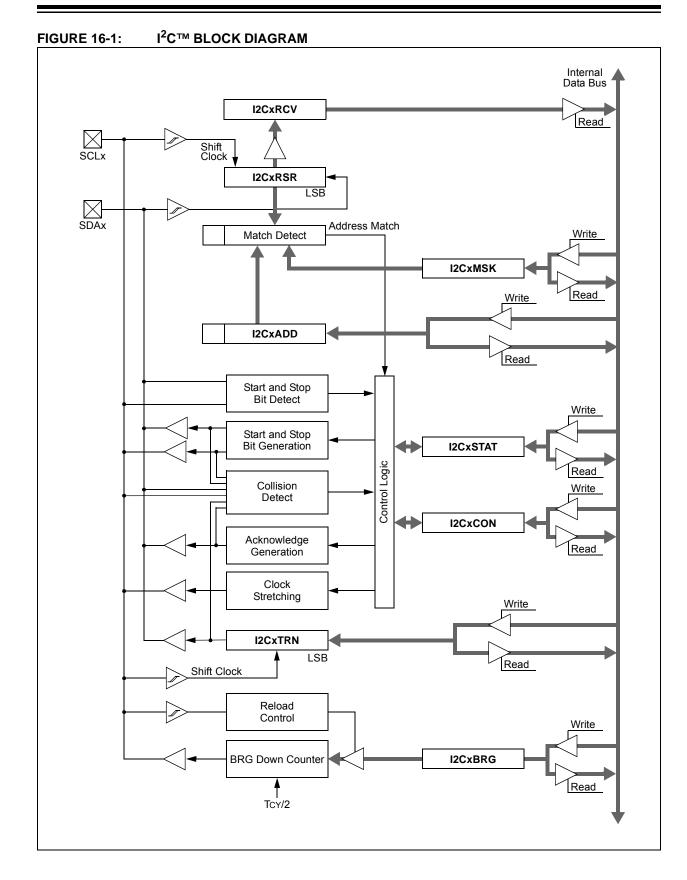

## 16.4 Slave Address Masking

The I2CxMSK register (Register 16-3) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '00100000', the slave module will detect both addresses, '00000000' and '00100000'.

To enable address masking, the IPMI (Intelligent Peripheral Management Interface) must be disabled by clearing the IPMIEN bit (I2CxCON<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 16-2 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Required       | _      | I2CxB     | RG Value      | Actual    |  |

|----------------|--------|-----------|---------------|-----------|--|

| System<br>FscL | Fcy    | (Decimal) | (Hexadecimal) | FSCL      |  |

| 100 kHz        | 16 MHz | 157       | 9D            | 100 kHz   |  |

| 100 kHz        | 8 MHz  | 78        | 4E            | 100 kHz   |  |

| 100 kHz        | 4 MHz  | 39        | 27            | 99 kHz    |  |

| 400 kHz        | 16 MHz | 37        | 25            | 404 kHz   |  |

| 400 kHz        | 8 MHz  | 18        | 12            | 404 kHz   |  |

| 400 kHz        | 4 MHz  | 9         | 9             | 385 kHz   |  |

| 400 kHz        | 2 MHz  | 4         | 4             | 385 kHz   |  |

| 1 MHz          | 16 MHz | 13        | D             | 1.026 MHz |  |

| 1 MHz          | 8 MHz  | 6         | 6             | 1.026 MHz |  |

| 1 MHz          | 4 MHz  | 3         | 3             | 0.909 MHz |  |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

# TABLE 16-2: $I^2 C^{TM} RESERVED ADDRESSES^{(1)}$

| Slave<br>Address | R/W<br>Bit | Description                            |

|------------------|------------|----------------------------------------|

| 0000 000         | 0          | General Call Address <sup>(2)</sup>    |

| 0000 000         | 1          | Start Byte                             |

| 0000 001         | x          | Cbus Address                           |

| 0000 010         | x          | Reserved                               |

| 0000 011         | x          | Reserved                               |

| 0000 1xx         | x          | HS Mode Master Code                    |

| 1111 1xx         | x          | Reserved                               |

| 1111 0xx         | х          | 10-Bit Slave Upper Byte <sup>(3)</sup> |

Note 1: The address bits listed here will never cause an address match, independent of the address mask settings.

2: The address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

# 19.1 RTCC Module Registers

The RTCC module registers are organized into three categories:

- RTCC Control Registers

- RTCC Value Registers

- Alarm Value Registers

# 19.1.1 REGISTER MAPPING

To limit the register interface, the RTCC Timer and Alarm Time registers are accessed through corresponding register pointers. The RTCC Value register window (RTCVALH and RTCVALL) uses the RTCPTR<1:0> bits (RCFGCAL<9:8>) to select the desired Timer register pair (see Table 19-1).

By writing the RTCVALH byte, the RTCC Pointer value (the RTCPTR<1:0> bits) decrements by one until the bits reach '00'. Once they reach '00', the MINUTES and SECONDS value will be accessible through RTCVALH and RTCVALL until the pointer value is manually changed.

TABLE 19-1: RTCVAL REGISTER MAPPING

| RTCPTR | RTCC Value Register Window |             |  |  |  |  |

|--------|----------------------------|-------------|--|--|--|--|

| <1:0>  | RTCVAL<15:8>               | RTCVAL<7:0> |  |  |  |  |

| 00     | MINUTES                    | SECONDS     |  |  |  |  |

| 01     | WEEKDAY                    | HOURS       |  |  |  |  |

| 10     | MONTH                      | DAY         |  |  |  |  |

| 11     | —                          | YEAR        |  |  |  |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTR bits (ALCFGRPT<9:8>) to select the desired Alarm register pair (see Table 19-2).

By writing the ALRMVALH byte, the Alarm Pointer value (the ALRMPTR<1:0> bits) decrements by one until the bits reach '00'. Once they reach '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

# EXAMPLE 19-1: SETTING THE RTCWREN BIT

```

asm volatile("push w7");

asm volatile("push w8");

asm volatile("disi #5");

asm volatile("mov #0x55, w7");

asm volatile("mov w7, _NVMKEY");

asm volatile("mov w8, _NVMKEY");

asm volatile("mov w8, _NVMKEY");

asm volatile("bset _RCFGCAL, #13"); //set the RTCWREN bit

asm volatile("pop w8");

asm volatile("pop w7");

```

### TABLE 19-2: ALRMVAL REGISTER MAPPING

| ALRMPTR | Alarm Value Register Window |              |  |  |  |  |

|---------|-----------------------------|--------------|--|--|--|--|

| <1:0>   | ALRMVAL<15:8>               | ALRMVAL<7:0> |  |  |  |  |

| 00      | ALRMMIN                     | ALRMSEC      |  |  |  |  |

| 01      | ALRMWD                      | ALRMHR       |  |  |  |  |

| 10      | ALRMMNTH                    | ALRMDAY      |  |  |  |  |

| 11      | —                           | —            |  |  |  |  |

Considering that the 16-bit core does not distinguish between 8-bit and 16-bit read operations, the user must be aware that when reading either the ALRMVALH or ALRMVALL, the bytes will decrement the ALRMPTR<1:0> value. The same applies to the RTCVALH or RTCVALL bytes with the RTCPTR<1:0> being decremented.

| Note: | This only applies to read operations and |

|-------|------------------------------------------|

|       | not write operations.                    |

# 19.1.2 WRITE LOCK

In order to perform a write to any of the RTCC Timer registers, the RTCWREN bit (RCFGCAL<13>) must be set (refer to Example 19-1).

Note: To avoid accidental writes to the timer, it is recommended that the RTCWREN bit (RCFGCAL<13>) is kept clear at any other time. For the RTCWREN bit to be set, there is only 1 instruction cycle time window allowed between the 55h/AA sequence and the setting of RTCWREN; therefore, it is recommended that code follow the procedure in Example 19-1.

# PIC24FJ64GA004 FAMILY

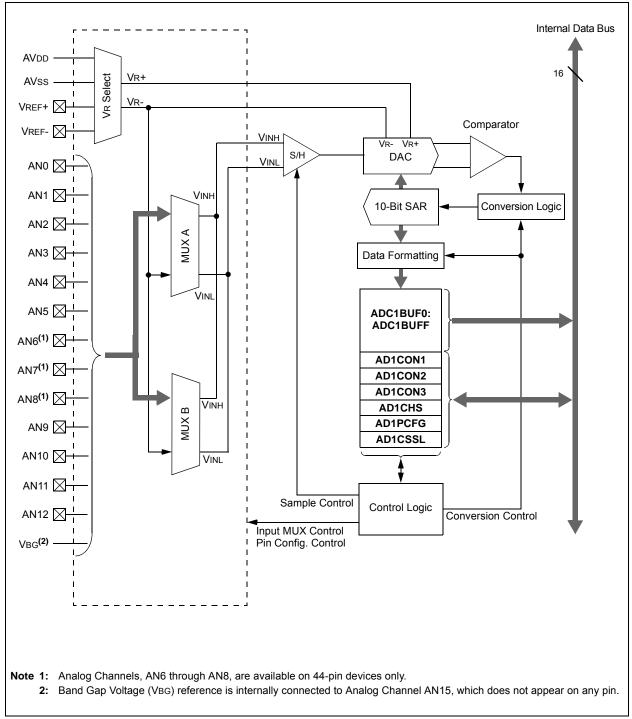

### FIGURE 21-1: 10-BIT HIGH-SPEED A/D CONVERTER BLOCK DIAGRAM

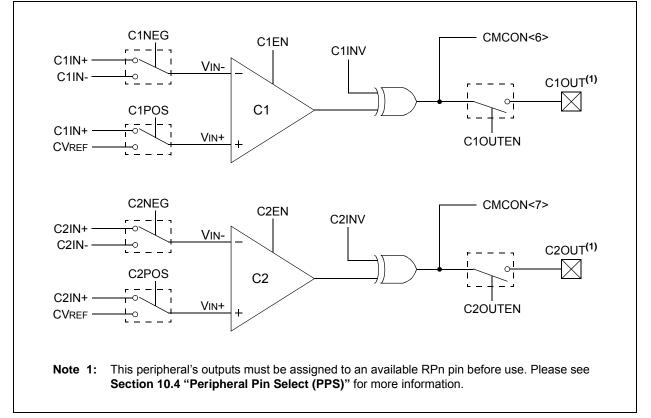

# 22.0 COMPARATOR MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, **"Output Compare"** (DS39706).

## FIGURE 22-1: COMPARATOR I/O OPERATING MODES

# 24.2.3 ON-CHIP REGULATOR AND POR

When the voltage regulator is enabled, it takes approximately 10 µs for it to generate output. During this time, designated as TVREG, code execution is disabled. TVREG is applied every time the device resumes operation after any power-down, including Sleep mode. TVREG is determined by the setting of the PMSLP bit (RCON<8>) and the WUTSELx Configuration bits (CW2<14:13>). For more information on TVREG, see **Section 27.0 "Electrical Characteristics"**.

If the regulator is disabled, a separate Power-up Timer (PWRT) is automatically enabled. The PWRT adds a fixed delay of 64 ms nominal delay at device start-up (POR or BOR only). When waking up from Sleep with the regulator disabled, TVREG is used to determine the wake-up time. To decrease the device wake-up time when operating with the regulator disabled, the PMSLP bit can be set.

# 24.2.4 POWER-UP REQUIREMENTS

The on-chip regulator is designed to meet the power-up requirements for the device. If the application does not use the regulator, then strict power-up conditions must be adhered to. While powering up, VDDCORE must never exceed VDD by 0.3 volts.

| Note: | For more information, see Section 27.0 |

|-------|----------------------------------------|

|       | "Electrical Characteristics".          |

#### 24.2.5 VOLTAGE REGULATOR STANDBY MODE

When enabled, the on-chip regulator always consumes a small incremental amount of current over IDD/IPD, including when the device is in Sleep mode, even though the core digital logic does not require power. To provide additional savings in applications where power resources are critical, the regulator automatically places itself into Standby mode whenever the device goes into Sleep mode. This feature is controlled by the PMSLP bit (RCON<8>). By default, this bit is cleared, which enables Standby mode.

For select PIC24FJ64GA004 family devices, the time required for regulator wake-up from Standby mode is controlled by the WUTSEL<1:0> Configuration bits (CW2<14:13>). The default wake-up time for all devices is 190  $\mu$ s. Where the WUTSELx Configuration bits are implemented, a fast wake-up option is also available. When WUTSEL<1:0> = 01, the regulator wake-up time is 25  $\mu$ s.

Note: This feature is implemented only on PIC24FJ64GA004 family devices with a major silicon revision level of B or later (DEVREV register value is 3042h or greater). When the regulator's Standby mode is turned off (PMSLP = 1), Flash program memory stays powered in Sleep mode and the device can wake-up in less than 10  $\mu$ s. When PMSLP is set, the power consumption while in Sleep mode will be approximately 40  $\mu$ A higher than power consumption when the regulator is allowed to enter Standby mode.

# 24.3 Watchdog Timer (WDT)

For PIC24FJ64GA004 family devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 31 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the FWPSA Configuration bit. With a 31 kHz input, the prescaler yields a nominal WDT Time-out period (TWDT) of 1 ms in 5-bit mode or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPS<3:0> Configuration bits (CW1<3:0>), which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods, ranges from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3:2>) will need to be cleared in software after the device wakes up.

The WDT Flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

# 27.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC24FJ64GA004 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24FJ64GA004 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                      | 40°C to +135°C       |

|-------------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                                 |                      |

| Voltage on VDD with respect to Vss                                                  | 0.3V to +4.0V        |

| Voltage on any combined analog and digital pin and MCLR, with respect to Vss        | 0.3V to (VDD + 0.3V) |

| Voltage on any digital only pin with respect to Vss                                 | -0.3V to +6.0V       |

| Voltage on VDDCORE with respect to Vss                                              | -0.3V to +3.0V       |

| Maximum current out of Vss pin                                                      |                      |

| Maximum current into VDD pin (Note 1)                                               | 250 mA               |

| Maximum output current sunk by any I/O pin                                          |                      |

| Maximum output current sourced by any I/O pin                                       | 25 mA                |

| Maximum current sunk by all ports                                                   | 200 mA               |

| Maximum current sourced by all ports (Note 1)                                       | 200 mA               |

| Note 1: Maximum allowable current is a function of device maximum power dissipation | (see Table 27-1).    |

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| DC CHARACTE                                              | RISTICS                |       | $ \begin{array}{ll} \mbox{Standard Operating Conditions:} & \mbox{2.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \\ \end{array} $ |        |                       |                 |  |  |

|----------------------------------------------------------|------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------|-----------------|--|--|

| Parameter No.                                            | Typical <sup>(1)</sup> | Max   | Units Conditions                                                                                                                                                                                                                                                                           |        |                       |                 |  |  |

| Operating Current (IDD): PMD Bits are Set <sup>(2)</sup> |                        |       |                                                                                                                                                                                                                                                                                            |        |                       |                 |  |  |

| DC20                                                     | 0.650                  | 0.850 | mA                                                                                                                                                                                                                                                                                         | -40°C  |                       |                 |  |  |

| DC20a                                                    | 0.650                  | 0.850 | mA                                                                                                                                                                                                                                                                                         | +25°C  | 2.0V <sup>(3)</sup>   | - 1 MIPS        |  |  |

| DC20b                                                    | 0.650                  | 0.850 | mA                                                                                                                                                                                                                                                                                         | +85°C  |                       |                 |  |  |

| DC20c                                                    | 0.650                  | 0.850 | mA                                                                                                                                                                                                                                                                                         | +125°C |                       |                 |  |  |

| DC20d                                                    | 1.2                    | 1.6   | mA                                                                                                                                                                                                                                                                                         | -40°C  |                       |                 |  |  |

| DC20e                                                    | 1.2                    | 1.6   | mA                                                                                                                                                                                                                                                                                         | +25°C  |                       |                 |  |  |

| DC20f                                                    | 1.2                    | 1.6   | mA                                                                                                                                                                                                                                                                                         | +85°C  | 3.3007                |                 |  |  |

| DC20g                                                    | 1.2                    | 1.6   | mA                                                                                                                                                                                                                                                                                         | +125°C |                       |                 |  |  |

| DC23                                                     | 2.6                    | 3.4   | mA                                                                                                                                                                                                                                                                                         | -40°C  |                       |                 |  |  |

| DC23a                                                    | 2.6                    | 3.4   | mA                                                                                                                                                                                                                                                                                         | +25°C  | -<br>                 |                 |  |  |

| DC23b                                                    | 2.6                    | 3.4   | mA                                                                                                                                                                                                                                                                                         | +85°C  | 2.0V <sup>(3)</sup>   |                 |  |  |

| DC23c                                                    | 2.6                    | 3.4   | mA                                                                                                                                                                                                                                                                                         | +125°C |                       |                 |  |  |

| DC23d                                                    | 4.1                    | 5.4   | mA                                                                                                                                                                                                                                                                                         | -40°C  |                       | 4 MIPS          |  |  |

| DC23e                                                    | 4.1                    | 5.4   | mA                                                                                                                                                                                                                                                                                         | +25°C  | 3.3∨ <sup>(4)</sup>   |                 |  |  |

| DC23f                                                    | 4.1                    | 5.4   | mA                                                                                                                                                                                                                                                                                         | +85°C  |                       |                 |  |  |

| DC23g                                                    | 4.1                    | 5.4   | mA                                                                                                                                                                                                                                                                                         | +125°C |                       |                 |  |  |

| DC24                                                     | 13.5                   | 17.6  | mA                                                                                                                                                                                                                                                                                         | -40°C  |                       | - 16 MIPS       |  |  |

| DC24a                                                    | 13.5                   | 17.6  | mA                                                                                                                                                                                                                                                                                         | +25°C  | -<br>                 |                 |  |  |

| DC24b                                                    | 13.5                   | 17.6  | mA                                                                                                                                                                                                                                                                                         | +85°C  | 2.5V <sup>(3)</sup>   |                 |  |  |

| DC24c                                                    | 13.5                   | 17.6  | mA                                                                                                                                                                                                                                                                                         | +125°C |                       |                 |  |  |

| DC24d                                                    | 15                     | 20    | mA                                                                                                                                                                                                                                                                                         | -40°C  |                       |                 |  |  |

| DC24e                                                    | 15                     | 20    | mA                                                                                                                                                                                                                                                                                         | +25°C  | 3.3√(4)               |                 |  |  |

| DC24f                                                    | 15                     | 20    | mA                                                                                                                                                                                                                                                                                         | +85°C  | 3.3007                |                 |  |  |

| DC24g                                                    | 15                     | 20    | mA                                                                                                                                                                                                                                                                                         | +125°C |                       |                 |  |  |

| DC31                                                     | 13                     | 17    | μA                                                                                                                                                                                                                                                                                         | -40°C  |                       | – LPRC (31 kHz) |  |  |

| DC31a                                                    | 13                     | 17    | μA                                                                                                                                                                                                                                                                                         | +25°C  | 2.0V <sup>(3)</sup>   |                 |  |  |

| DC31b                                                    | 20                     | 26    | μA                                                                                                                                                                                                                                                                                         | +85°C  |                       |                 |  |  |

| DC31c                                                    | 40                     | 50    | μA                                                                                                                                                                                                                                                                                         | +125°C |                       |                 |  |  |

| DC31d                                                    | 54                     | 70    | μA                                                                                                                                                                                                                                                                                         | -40°C  |                       |                 |  |  |

| DC31e                                                    | 54                     | 70    | μA                                                                                                                                                                                                                                                                                         | +25°C  | a av (4)              |                 |  |  |

| DC31f                                                    | 95                     | 124   | μA                                                                                                                                                                                                                                                                                         | +85°C  | - 3.3√ <sup>(4)</sup> |                 |  |  |

| DC31g                                                    | 120                    | 260   | μA                                                                                                                                                                                                                                                                                         | +125°C |                       |                 |  |  |

#### TABLE 27-4: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.