Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

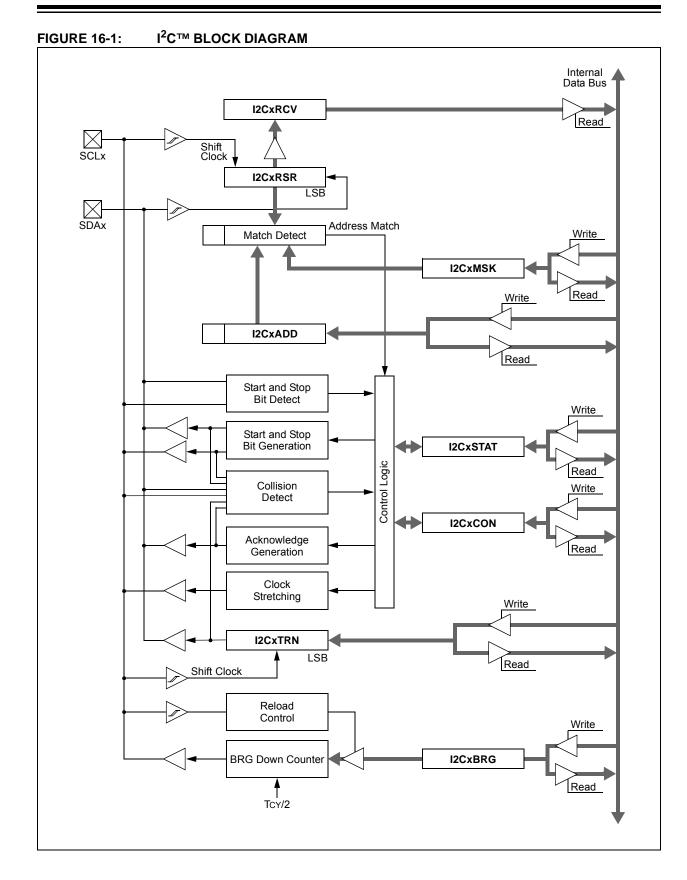

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 16KB (5.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 4K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 44-QFN (8x8)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj16ga004t-i-ml |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

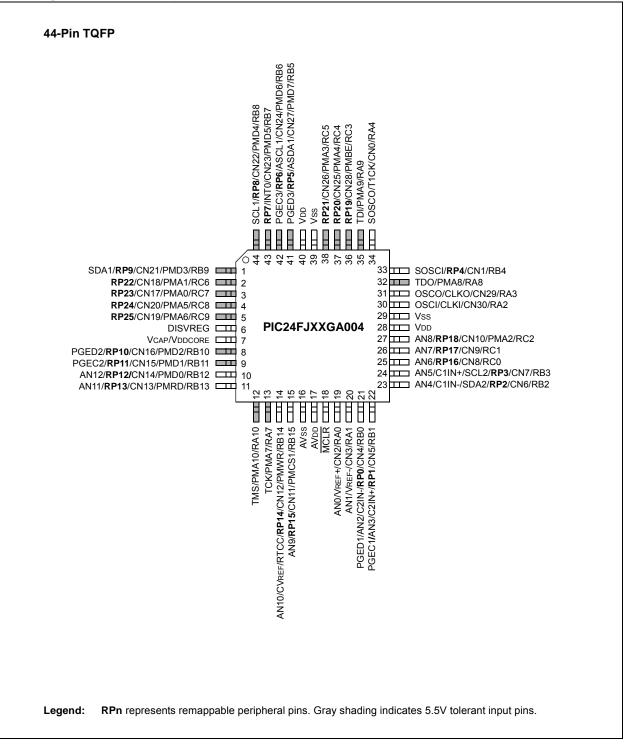

## **Pin Diagrams (Continued)**

|          | 1                             | Pin Number    |                    |     |                   |                                                                                            |

|----------|-------------------------------|---------------|--------------------|-----|-------------------|--------------------------------------------------------------------------------------------|

| Function | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer   | Description                                                                                |

| OSCI     | 9                             | 6             | 30                 | Ι   | ANA               | Main Oscillator Input Connection.                                                          |

| OSCO     | 10                            | 7             | 31                 | 0   | ANA               | Main Oscillator Output Connection.                                                         |

| PGEC1    | 5                             | 2             | 22                 | I/O | ST                | In-Circuit Debugger/Emulator and ICSP™ Programming                                         |

| PGEC2    | 22                            | 19            | 9                  | I/O | ST                | Clock.                                                                                     |

| PGEC3    | 14                            | 12            | 42                 | I/O | ST                |                                                                                            |

| PGED1    | 4                             | 1             | 21                 | I/O | ST                | In-Circuit Debugger/Emulator and ICSP Programming                                          |

| PGED2    | 21                            | 18            | 8                  | I/O | ST                | Data.                                                                                      |

| PGED3    | 15                            | 11            | 41                 | I/O | ST                |                                                                                            |

| PMA0     | 10                            | 7             | 3                  | I/O | ST/TTL            | Parallel Master Port Address Bit 0 Input (Buffered Slave modes) and Output (Master modes). |

| PMA1     | 12                            | 9             | 2                  | I/O | ST/TTL            | Parallel Master Port Address Bit 1 Input (Buffered Slave modes) and Output (Master modes). |

| PMA2     | —                             | _             | 27                 | 0   | —                 | Parallel Master Port Address (Demultiplexed Master                                         |

| PMA3     | —                             | _             | 38                 | 0   | —                 | modes).                                                                                    |

| PMA4     | —                             | _             | 37                 | 0   | —                 |                                                                                            |

| PMA5     | —                             | _             | 4                  | 0   | —                 |                                                                                            |

| PMA6     | —                             | _             | 5                  | 0   | —                 |                                                                                            |

| PMA7     | —                             | _             | 13                 | 0   | —                 |                                                                                            |

| PMA8     | —                             | —             | 32                 | 0   | —                 |                                                                                            |

| PMA9     | —                             | _             | 35                 | 0   | —                 |                                                                                            |

| PMA10    | —                             | _             | 12                 | 0   | —                 |                                                                                            |

| PMA11    | —                             | —             | _                  | 0   | —                 |                                                                                            |

| PMA12    | —                             | _             | _                  | 0   | —                 |                                                                                            |

| PMA13    | —                             | _             | _                  | 0   | —                 |                                                                                            |

| PMBE     | 11                            | 8             | 36                 | 0   | —                 | Parallel Master Port Byte Enable Strobe.                                                   |

| PMCS1    | 26                            | 23            | 15                 | 0   | —                 | Parallel Master Port Chip Select 1 Strobe/Address Bit 14.                                  |

| PMD0     | 23                            | 20            | 10                 | I/O | ST/TTL            | Parallel Master Port Data (Demultiplexed Master mode) o                                    |

| PMD1     | 22                            | 19            | 9                  | I/O | ST/TTL            | Address/Data (Multiplexed Master modes).                                                   |

| PMD2     | 21                            | 18            | 8                  | I/O | ST/TTL            |                                                                                            |

| PMD3     | 18                            | 15            | 1                  | I/O | ST/TTL            |                                                                                            |

| PMD4     | 17                            | 14            | 44                 | I/O | ST/TTL            |                                                                                            |

| PMD5     | 16                            | 13            | 43                 | I/O | ST/TTL            |                                                                                            |

| PMD6     | 15                            | 12            | 42                 | I/O | ST/TTL            |                                                                                            |

| PMD7     | 14                            | 11            | 41                 | I/O | ST/TTL            |                                                                                            |

| PMRD     | 24                            | 21            | 11                 | 0   | _                 | Parallel Master Port Read Strobe.                                                          |

| PMWR     | 25                            | 22            | 14                 | 0   | _                 | Parallel Master Port Write Strobe.                                                         |

| Legend:  | TTL = TTL inp<br>ANA = Analog | level input/o | utput              |     | l <sup>2</sup> C™ | Schmitt Trigger input buffer<br>= I <sup>2</sup> C/SMBus input buffer                      |

#### TABLE 1-2: PIC24FJ64GA004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Note 1: Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

#### 5.5.2 PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

If a Flash location has been erased, it can be programmed using table write instructions to write an instruction word (24-bit) into the write latch. The TBLPAG register is loaded with the 8 Most Significant Bytes of the Flash address. The TBLWTL and TBLWTH instructions write the desired data into the write latches and specify the lower 16 bits of the program memory address to write to. To configure the NVMCON register for a word write, set the NVMOPx bits (NVMCON<3:0>) to '0011'. The write is performed by executing the unlock sequence and setting the WR bit (see Example 5-4).

## EXAMPLE 5-4: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

| ; Setup a p               | pointer to data Program Memory                             |    |                                                      |

|---------------------------|------------------------------------------------------------|----|------------------------------------------------------|

| MOV                       | <pre>#tblpage(PROG_ADDR), W0</pre>                         | ;  |                                                      |

| MOV                       | W0, TBLPAG                                                 | ;1 | Initialize PM Page Boundary SFR                      |

| MOV                       | <pre>#tbloffset(PROG_ADDR), W0</pre>                       | ;1 | initialize a register with program memory address    |

| MOV                       | #LOW_WORD_N, W2                                            | ;  |                                                      |

| MOV                       | #HIGH_BYTE_N, W3                                           | ;  |                                                      |

| TBLWTL                    | W2, [W0]                                                   | ;  | Write PM low word into program latch                 |

| TBLWTH                    | W3, [W0++]                                                 | ;  | Write PM high byte into program latch                |

| ; Setup NVN<br>MOV<br>MOV | 4CON for programming one word<br>#0x4003, W0<br>W0, NVMCON | ;  | data Program Memory<br>Set NVMOP bits to 0011        |

| DISI                      | #5                                                         | ;  | Disable interrupts while the KEY sequence is written |

| MOV                       | #0x55, W0                                                  | ;  | Write the key sequence                               |

| MOV                       | W0, NVMKEY                                                 |    |                                                      |

| MOV                       | #0xAA, W0                                                  |    |                                                      |

| MOV                       | W0, NVMKEY                                                 |    |                                                      |

| BSET                      | NVMCON, #WR                                                | ;  | Start the write cycle                                |

| NOP                       |                                                            | ;  | 2 NOPs required after setting WR                     |

| NOP                       |                                                            | ;  |                                                      |

|                           |                                                            |    |                                                      |

## REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0               | U-0                                           | U-0                                                                                                                         | U-0                           | U-0               | U-0              | U-0                | R/W-0 |  |

|-------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------|------------------|--------------------|-------|--|

|                   |                                               | —                                                                                                                           |                               |                   | _                | —                  | LVDIE |  |

| bit 15            |                                               |                                                                                                                             |                               |                   |                  |                    | bit 8 |  |

|                   |                                               |                                                                                                                             |                               |                   |                  |                    |       |  |

| U-0               | U-0                                           | U-0                                                                                                                         | U-0                           | R/W-0             | R/W-0            | R/W-0              | U-0   |  |

| _                 |                                               |                                                                                                                             | _                             | CRCIE             | U2ERIE           | U1ERIE             | _     |  |

| bit 7             |                                               |                                                                                                                             |                               |                   |                  |                    | bit C |  |

|                   |                                               |                                                                                                                             |                               |                   |                  |                    |       |  |

| Legend:           |                                               |                                                                                                                             |                               |                   |                  |                    |       |  |

| R = Reada         | ble bit                                       | W = Writable b                                                                                                              | oit                           | U = Unimplen      | nented bit, read | d as '0'           |       |  |

| -n = Value        | at POR                                        | '1' = Bit is set                                                                                                            |                               | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |

| bit 15-9<br>bit 8 | LVDIE: Low-<br>1 = Interrupt<br>0 = Interrupt | Noted: Read as 'C<br>Voltage Detect I<br>request is enabl<br>request is not en                                              | nterrupt Enat<br>ed<br>nabled | ble Status bit    |                  |                    |       |  |

| bit 7-4           | •                                             | nted: Read as '0                                                                                                            |                               |                   |                  |                    |       |  |

| bit 3             | 1 = Interrupt                                 | C Generator Inter<br>request is enabl<br>request is not er                                                                  | ed                            | bit               |                  |                    |       |  |

| bit 2             | U2ERIE: UA                                    | RT2 Error Interr                                                                                                            | upt Enable bi                 | t                 |                  |                    |       |  |

|                   |                                               | request is enabl<br>request is not er                                                                                       |                               |                   |                  |                    |       |  |

| bit 1             | 1 = Interrupt                                 | <b>U1ERIE:</b> UART1 Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled |                               |                   |                  |                    |       |  |

| bit 0             | Unimpleme                                     | nted: Read as 'o                                                                                                            | )'                            |                   |                  |                    |       |  |

|                   |                                               |                                                                                                                             |                               |                   |                  |                    |       |  |

| U-0          | U-0                                | U-0                                                        | U-0              | U-0              | U-0              | U-0                | U-0     |  |  |  |

|--------------|------------------------------------|------------------------------------------------------------|------------------|------------------|------------------|--------------------|---------|--|--|--|

|              | —                                  | _                                                          | _                |                  |                  | _                  |         |  |  |  |

| oit 15       |                                    |                                                            |                  |                  |                  |                    | bit 8   |  |  |  |

|              |                                    |                                                            |                  |                  |                  |                    |         |  |  |  |

| U-0          | R/W-1                              | R/W-0                                                      | R/W-0            | U-0              | R/W-1            | R/W-0              | R/W-0   |  |  |  |

|              | SPI2IP2                            | SPI2IP1                                                    | SPI2IP0          | —                | SPF2IP2          | SPF2IP1            | SPF2IP0 |  |  |  |

| oit 7        |                                    |                                                            |                  |                  |                  |                    | bit 0   |  |  |  |

|              |                                    |                                                            |                  |                  |                  |                    |         |  |  |  |

| _egend:      |                                    |                                                            |                  |                  |                  |                    |         |  |  |  |

| R = Readab   | ole bit                            | W = Writable                                               | bit              | U = Unimple      | mented bit, read | d as '0'           |         |  |  |  |

| -n = Value a | it POR                             | '1' = Bit is set                                           |                  | '0' = Bit is cle | eared            | x = Bit is unknown |         |  |  |  |

|              |                                    | (ad. Daad as (                                             | o.'              |                  |                  |                    |         |  |  |  |

| bit 15-7     | -                                  | ted: Read as '                                             |                  |                  |                  |                    |         |  |  |  |

| bit 6-4      |                                    | SPI2 Event In                                              |                  |                  |                  |                    |         |  |  |  |

|              | 111 = Interru                      | ot is Priority 7 (                                         | highest priority | interrupt)       |                  |                    |         |  |  |  |

|              | •                                  |                                                            |                  |                  |                  |                    |         |  |  |  |

|              | •                                  |                                                            |                  |                  |                  |                    |         |  |  |  |

|              | 001 = Interrupt is Priority 1      |                                                            |                  |                  |                  |                    |         |  |  |  |

|              | 000 = Interrupt source is disabled |                                                            |                  |                  |                  |                    |         |  |  |  |

| bit 3        | Unimplemen                         | ted: Read as '                                             | כ'               |                  |                  |                    |         |  |  |  |

| bit 2-0      | SPF2IP<2:0>                        | : SPI2 Fault In                                            | terrupt Priority | bits             |                  |                    |         |  |  |  |

|              | 111 = Interru                      | 111 = Interrupt is Priority 7 (highest priority interrupt) |                  |                  |                  |                    |         |  |  |  |

|              | •                                  |                                                            |                  |                  |                  |                    |         |  |  |  |

|              | •                                  |                                                            |                  |                  |                  |                    |         |  |  |  |

|              |                                    |                                                            |                  |                  |                  |                    |         |  |  |  |

|              | 001 = Interru                      | ot is Priority 1                                           |                  |                  |                  |                    |         |  |  |  |

## REGISTER 7-23: IPC8: INTERRUPT PRIORITY CONTROL REGISTER 8

## REGISTER 7-30: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0           | U-0                                                      | U-0                | U-0              | U-0                                     | U-0    | U-0    | U-0    |  |

|---------------|----------------------------------------------------------|--------------------|------------------|-----------------------------------------|--------|--------|--------|--|

|               | —                                                        | —                  | —                | —                                       | —      | —      | —      |  |

| bit 15        |                                                          |                    |                  |                                         |        |        | bit 8  |  |

|               |                                                          |                    |                  |                                         |        |        |        |  |

| U-0           | U-0                                                      | U-0                | U-0              | U-0                                     | R/W-1  | R/W-0  | R/W-0  |  |

|               | —                                                        | —                  | —                | —                                       | LVDIP2 | LVDIP1 | LVDIP0 |  |

| bit 7         |                                                          |                    |                  |                                         |        |        | bit 0  |  |

|               |                                                          |                    |                  |                                         |        |        |        |  |

| Legend:       |                                                          |                    |                  |                                         |        |        |        |  |

| R = Readabl   | e bit                                                    | W = Writable       | bit              | U = Unimplemented bit, read as '0'      |        |        |        |  |

| -n = Value at | POR                                                      | '1' = Bit is set   |                  | '0' = Bit is cleared x = Bit is unknown |        |        | nown   |  |

|               |                                                          |                    |                  |                                         |        |        |        |  |

| bit 15-3      | Unimplemen                                               | ted: Read as '     | כ'               |                                         |        |        |        |  |

| bit 2-0       | 0 LVDIP<2:0>: Low-Voltage Detect Interrupt Priority bits |                    |                  |                                         |        |        |        |  |

|               | 111 = Interru                                            | ot is Priority 7 ( | highest priority | interrupt)                              |        |        |        |  |

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

| U-0                                | U-0        | U-0                  | R/W-0                 | R/W-0                              | R/W-0                 | R/W-0                 | R/W-0                 |  |

|------------------------------------|------------|----------------------|-----------------------|------------------------------------|-----------------------|-----------------------|-----------------------|--|

| _                                  |            | _                    | RP25R4 <sup>(1)</sup> | RP25R3 <sup>(1)</sup>              | RP25R2 <sup>(1)</sup> | RP25R1 <sup>(1)</sup> | RP25R0 <sup>(1)</sup> |  |

| bit 15                             |            |                      |                       |                                    |                       |                       | bit 8                 |  |

|                                    |            |                      |                       |                                    |                       |                       |                       |  |

| U-0                                | U-0        | U-0                  | R/W-0                 | R/W-0                              | R/W-0                 | R/W-0                 | R/W-0                 |  |

| _                                  |            | —                    | RP24R4 <sup>(1)</sup> | RP24R3 <sup>(1)</sup>              | RP24R2 <sup>(1)</sup> | RP24R1 <sup>(1)</sup> | RP24R0 <sup>(1)</sup> |  |

| bit 7                              |            |                      | •                     | •                                  |                       |                       | bit 0                 |  |

|                                    |            |                      |                       |                                    |                       |                       |                       |  |

| Legend:                            |            |                      |                       |                                    |                       |                       |                       |  |

| R = Readable                       | e bit      | W = Writable         | bit                   | U = Unimplemented bit, read as '0' |                       |                       |                       |  |

| -n = Value at POR '1' = Bit is set |            | '0' = Bit is cleared |                       | ared                               | x = Bit is unknown    |                       |                       |  |

|                                    |            |                      |                       |                                    |                       |                       |                       |  |

| bit 15-13                          | Unimplemen | ted: Read as '@      | י'                    |                                    |                       |                       |                       |  |

### REGISTER 10-27: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

bit 15-13 Unimplemented: Read as '0

RP25R<4:0>: Peripheral Output Function is Assigned to RP25 Output Pin bits<sup>(1)</sup> bit 12-8 (see Table 10-3 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

RP24R<4:0>: Peripheral Output Function is Assigned to RP24 Output Pin bits<sup>(1)</sup> bit 4-0 (see Table 10-3 for peripheral function numbers)

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

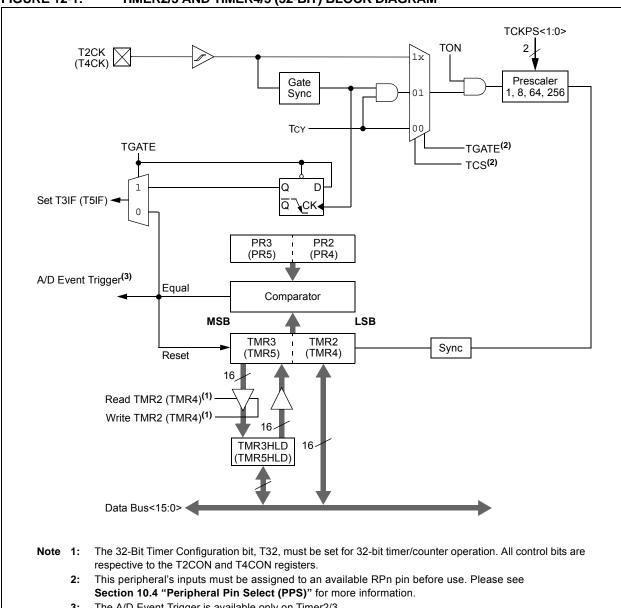

## 12.0 TIMER2/3 AND TIMER4/5

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, **"Timers"** (DS39704).

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent, 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3 and Timer4/5 operate in three modes:

- Two independent, 16-bit timers (Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer

- · Single 32-bit synchronous counter

They also support these features:

- Timer gate operation

- Selectable prescaler settings

- · Timer operation during Idle and Sleep modes

- · Interrupt on a 32-Bit Period register match

- A/D Event Trigger (Timer2/3 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the A/D Event Trigger; this is implemented only with Timer3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 12-1; T3CON and T5CON are shown in generic form in Register 12-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word; Timer3 and Timer4 are the most significant word of the 32-bit timers.

| Note: | For 32-bit operation, T3CON and T5CON      |

|-------|--------------------------------------------|

|       | control bits are ignored. Only T2CON and   |

|       | T4CON control bits are used for setup and  |

|       | control. Timer2 and Timer4 clock and gate  |

|       | inputs are utilized for the 32-bit timer   |

|       | modules, but an interrupt is generated     |

|       | with the Timer3 or Timer5 interrupt flags. |

To configure Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 bit (T2CON<3> or T4CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to the external clock, RPINRx (TxCK) must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- 4. Load the timer period value. PR3 (or PR5) will contain the most significant word of the value while PR2 (or PR4) contains the least significant word.

- 5. If interrupts are required, set the Timer3/5 Interrupt Enable bit, T3IE or T5IE; use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. Note that while Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair, TMR3:TMR2 (or TMR5:TMR4). TMR3 (TMR5) always contains the most significant word of the count, while TMR2 (TMR4) contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- Clear the T32 bit corresponding to that timer (T2CON<3> for Timer2 and Timer3 or T4CON<3> for Timer4 and Timer5).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the Timerx Interrupt Enable bit, TxIE; use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit (TxCON<15> = 1).

#### **FIGURE 12-1:** TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM

3: The A/D Event Trigger is available only on Timer2/3.

NOTES:

## 14.4 Output Compare Register

## REGISTER 14-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER

| U-0 | R/W-0  | U-0      | U-0                           | U-0                 | U-0                 | U-0                                                                                                                                          |

|-----|--------|----------|-------------------------------|---------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| —   | OCSIDL | —        | —                             | _                   | —                   | —                                                                                                                                            |

|     |        |          |                               |                     |                     | bit 8                                                                                                                                        |

|     |        |          |                               |                     |                     |                                                                                                                                              |

| U-0 | U-0    | R-0, HC  | R/W-0                         | R/W-0               | R/W-0               | R/W-0                                                                                                                                        |

|     | —      | OCFLT    | OCTSEL                        | OCM2 <sup>(1)</sup> | OCM1 <sup>(1)</sup> | OCM0 <sup>(1)</sup>                                                                                                                          |

|     |        |          |                               |                     |                     | bit 0                                                                                                                                        |

|     | _      | — OCSIDL | — OCSIDL —<br>U-0 U-0 R-0, HC | - OCSIDL            | - OCSIDL            | −         OCSIDL         −         −         −         −           U-0         U-0         R-0, HC         R/W-0         R/W-0         R/W-0 |

| Legend:           | HC = Hardware Clearable bit |                                    |                    |  |  |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Output Compare x Stop in Idle Mode Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | <ul> <li>1 = Output Compare x halts in CPU Idle mode</li> <li>0 = Output Compare x continues to operate in CPU Idle mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in HW only)</li> <li>0 = No PWM Fault condition has occurred (this bit is only used when OCM&lt;2:0&gt; = 111)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 3     | OCTSEL: Output Compare x Timer Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | <ul> <li>1 = Timer3 is the clock source for Output Compare x</li> <li>0 = Timer2 is the clock source for Output Compare x</li> <li>Refer to the device data sheet for specific time bases available to the output compare module.</li> </ul>                                                                                                                                                                                                                                                                                                                                              |

| bit 2-0   | OCM<2:0>: Output Compare x Mode Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = PWM mode on OCx; Fault pin, OCFx, is enabled<sup>(2)</sup></li> <li>110 = PWM mode on OCx; Fault pin, OCFx, is disabled<sup>(2)</sup></li> <li>101 = Initializes OCx pin low, generates continuous output pulses on OCx pin</li> <li>100 = Initializes OCx pin low, generates single output pulse on OCx pin</li> <li>011 = Compare event toggles OCx pin</li> <li>010 = Initializes OCx pin high, compare event forces OCx pin low</li> <li>001 = Initializes OCx pin low, compare event forces OCx pin high</li> <li>000 = Output compare channel is disabled</li> </ul> |

| Note 1:   | RPORx (OCx) must be configured to an available RPn pin. For more information, see Section 10.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

- "Peripheral Pin Select (PPS)".

- 2: The OCFA pin controls the OC1-OC4 channels. The OCFB pin controls the OC5 channel.

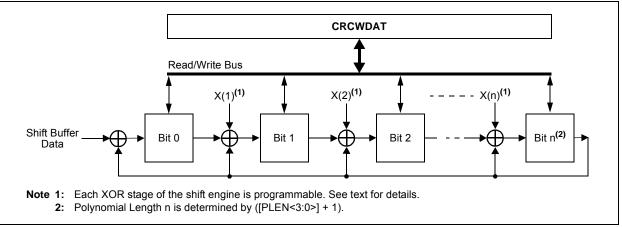

### FIGURE 20-2: CRC SHIFT ENGINE DETAIL

#### 20.1 User Interface

#### 20.1.1 DATA INTERFACE

To start serial shifting, a '1' must be written to the CRCGO bit.

The module incorporates a FIFO that is 8 deep when PLEN<3:0> (CRCCON<3:0>) > 7 and 16 deep, otherwise. The data for which the CRC is to be calculated must first be written into the FIFO. The smallest data element that can be written into the FIFO is one byte. For example, if PLEN<3:0> = 5, then the size of the data is PLEN<3:0> + 1 = 6. When loading data, the two MSbs of the data byte are ignored.

Once data is written into the CRCWDAT MSb (as defined by PLENx), the value of VWORD<4:0> (CRCCON<12:8>) increments by one. When CRCGO = 1 and VWORDx > 0, a word of data to be shifted is moved from the FIFO into the shift engine. When the data word moves from the FIFO to the shift engine, the VWORDx bits decrement by one. The serial shifter continues to receive data from the FIFO, shifting until the VWORDx bits reach 0. The last bit of data will be shifted through the CRC module (PLENx + 1)/2 clock cycles after the VWORDx bits reach 0. This is when the module is completed with the CRC calculation.

Therefore, for a given value of PLENx, it will take (PLENx + 1)/2 \* VWORDx number of clock cycles to complete the CRC calculations.

When the VWORD<4:0> bits reach 8 (or 16), the CRCFUL bit will be set. When the VWORD<4:0> bits reach 0, the CRCMPT bit will be set.

To continually feed data into the CRC engine, the recommended mode of operation is to initially "prime" the FIFO with a sufficient number of words, so no interrupt is generated before the next word can be written. Once that is done, start the CRC by setting the CRCGO bit to '1'. From that point onward, the VWORDx bits should be polled. If they read less than 8 or 16, another word can be written into the FIFO.

To empty words already written into a FIFO, the CRCGO bit must be set to '1' and the CRC shifter allowed to run until the CRCMPT bit is set.

Also, to get the correct CRC reading, it will be necessary to wait for the CRCMPT bit to go high before reading the CRCWDAT register.

If a word is written when the CRCFUL bit is set, the VWORDx Pointer will roll over to 0. The hardware will then behave as if the FIFO is empty. However, the condition to generate an interrupt will not be met; therefore, no interrupt will be generated (See Section 20.1.2 "Interrupt Operation").

At least one instruction cycle must pass after a write to CRCWDAT before a read of the VWORDx bits is done.

### 20.1.2 INTERRUPT OPERATION

When the VWORD<4:0> bits make a transition from a value of '1' to '0', an interrupt will be generated. Note that the CRC calculation is not complete at this point; an additional time of (PLEN + 1)/2 clock cycles is required before the output can be read.

## 20.2 Operation in Power Save Modes

#### 20.2.1 SLEEP MODE

If Sleep mode is entered while the module is operating, the module will be suspended in its current state until clock execution resumes.

### 20.2.2 IDLE MODE

To continue full module operation in Idle mode, the CSIDL bit must be cleared prior to entry into the mode.

If CSIDL = 1, the module will behave the same way as it does in Sleep mode; pending interrupt events will be passed on, even though the module clocks are not available.

## 25.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 25.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| Assembly<br>Mnemonic |         | Assembly Syntax | Description                                                | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|---------|-----------------|------------------------------------------------------------|---------------|----------------|--------------------------|

| BTSS                 | BTSS    | f,#bit4         | Bit Test f, Skip if Set                                    | 1             | 1<br>(2 or 3)  | None                     |

|                      | BTSS    | Ws,#bit4        | Bit Test Ws, Skip if Set                                   | 1             | 1<br>(2 or 3)  | None                     |

| BTST                 | BTST    | f,#bit4         | Bit Test f                                                 | 1             | 1              | Z                        |

|                      | BTST.C  | Ws,#bit4        | Bit Test Ws to C                                           | 1             | 1              | С                        |

|                      | BTST.Z  | Ws,#bit4        | Bit Test Ws to Z                                           | 1             | 1              | Z                        |

|                      | BTST.C  | Ws,Wb           | Bit Test Ws <wb> to C</wb>                                 | 1             | 1              | С                        |

|                      | BTST.Z  | Ws,Wb           | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1              | Z                        |

| BTSTS                | BTSTS   | f,#bit4         | Bit Test then Set f                                        | 1             | 1              | Z                        |

|                      | BTSTS.C | Ws,#bit4        | Bit Test Ws to C, then Set                                 | 1             | 1              | С                        |

|                      | BTSTS.Z | Ws,#bit4        | Bit Test Ws to Z, then Set                                 | 1             | 1              | Z                        |

| CALL                 | CALL    | lit23           | Call Subroutine                                            | 2             | 2              | None                     |

|                      | CALL    | Wn              | Call Indirect Subroutine                                   | 1             | 2              | None                     |

| CLR                  | CLR     | f               | f = 0x0000                                                 | 1             | 1              | None                     |

|                      | CLR     | WREG            | WREG = 0x0000                                              | 1             | 1              | None                     |

|                      | CLR     | Ws              | Ws = 0x0000                                                | 1             | 1              | None                     |

| CLRWDT               | CLRWDT  |                 | Clear Watchdog Timer                                       | 1             | 1              | WDTO, Sleep              |

| COM                  | COM     | f               | $f = \overline{f}$                                         | 1             | 1              | N, Z                     |

|                      | COM     | f,WREG          | WREG = f                                                   | 1             | 1              | N, Z                     |

|                      | COM     | Ws,Wd           | $Wd = \overline{Ws}$                                       | 1             | 1              | N, Z                     |

| CP                   | CP      | f               | Compare f with WREG                                        | 1             | 1              | C, DC, N, OV, Z          |

| -                    | CP      | Wb,#lit5        | Compare Wb with lit5                                       | 1             | 1              | C, DC, N, OV, Z          |

|                      | CP      | Wb,Ws           | Compare Wb with Ws (Wb – Ws)                               | 1             | 1              | C, DC, N, OV, Z          |

| CPO                  | CP0     | f               | Compare f with 0x0000                                      | 1             | 1              | C, DC, N, OV, Z          |

|                      | CP0     | Ws              | Compare Ws with 0x0000                                     | 1             | 1              | C, DC, N, OV, Z          |

| CPB                  | CPB     | f               | Compare f with WREG, with Borrow                           | 1             | 1              | C, DC, N, OV, Z          |

|                      | CPB     | Wb,#lit5        | Compare Wb with lit5, with Borrow                          | 1             | 1              | C, DC, N, OV, Z          |

|                      | CPB     | Wb,Ws           | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1              | C, DC, N, OV, Z          |

| CPSEQ                | CPSEQ   | Wb,Wn           | Compare Wb with Wn, Skip if =                              | 1             | 1<br>(2 or 3)  | None                     |

| CPSGT                | CPSGT   | Wb,Wn           | Compare Wb with Wn, Skip if >                              | 1             | 1<br>(2 or 3)  | None                     |

| CPSLT                | CPSLT   | Wb,Wn           | Compare Wb with Wn, Skip if <                              | 1             | 1<br>(2 or 3)  | None                     |

| CPSNE                | CPSNE   | Wb,Wn           | Compare Wb with Wn, Skip if ≠                              | 1             | 1<br>(2 or 3)  | None                     |

| DAW                  | DAW.B   | Wn              | Wn = Decimal Adjust Wn                                     | 1             | 1              | С                        |

| DEC                  | DEC     | f               | f = f -1                                                   | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC     | f,WREG          | WREG = f –1                                                | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC     | Ws,Wd           | Wd = Ws - 1                                                | 1             | 1              | C, DC, N, OV, Z          |

| DEC2                 | DEC2    | f               | f = f - 2                                                  | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC2    | f,WREG          | WREG = f – 2                                               | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC2    | Ws,Wd           | Wd = Ws - 2                                                | 1             | 1              | C, DC, N, OV, Z          |

| DISI                 | DISI    | #lit14          | Disable Interrupts for k Instruction Cycles                | 1             | 1              | None                     |

| DIV                  | DIV.SW  | Wm,Wn           | Signed 16/16-bit Integer Divide                            | 1             | 18             | N, Z, C, OV              |

|                      | DIV.SD  | Wm,Wn           | Signed 32/16-bit Integer Divide                            | 1             | 18             | N, Z, C, OV              |

|                      | DIV.UW  | Wm,Wn           | Unsigned 16/16-bit Integer Divide                          | 1             | 18             | N, Z, C, OV              |

|                      | DIV.UD  | Wm,Wn           | Unsigned 32/16-bit Integer Divide                          | 1             | 18             | N, Z, C, OV              |

| EXCH                 | EXCH    | Wns,Wnd         | Swap Wns with Wnd                                          | 1             | 1              | None                     |

| FBCL                 | FFBCL   | Ws, Wnd         | Find Bit Change from left (MSb) Side                       | 1             | 1              | None                     |

| FF1L                 | FF1L    | Ws,Wnd          | Find First One from Left (MSb) Side                        | 1             | 1              | С                        |

| FF1R                 | FF1R    | Ws,Wnd          | Find First One from Right (LSb) Side                       | 1             | 1              | С                        |

### TABLE 26-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Assembly<br>Mnemonic |        | Assembly Syntax  | Description                                                                                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|------------------|----------------------------------------------------------------------------------------------|---------------|----------------|--------------------------|

| GOTO                 | GOTO   | Expr             | Go to Address                                                                                | 2             | 2              | None                     |

|                      | GOTO   | Wn               | Go to Indirect                                                                               | 1             | 2              | None                     |

| INC                  | INC    | f                | f = f + 1                                                                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | f,WREG           | WREG = f + 1                                                                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC    | Ws,Wd            | Wd = Ws + 1                                                                                  | 1             | 1              | C, DC, N, OV, Z          |

| INC2                 | INC2   | f                | f = f + 2                                                                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | f,WREG           | WREG = f + 2                                                                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | INC2   | Ws,Wd            | Wd = Ws + 2                                                                                  | 1             | 1              | C, DC, N, OV, Z          |

| IOR                  | IOR    | f                | f = f .IOR. WREG                                                                             | 1             | 1              | N, Z                     |

|                      | IOR    | f,WREG           | WREG = f .IOR. WREG                                                                          | 1             | 1              | N, Z                     |

|                      | IOR    | #lit10,Wn        | Wd = lit10 .IOR. Wd                                                                          | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,Ws,Wd         | Wd = Wb .IOR. Ws                                                                             | 1             | 1              | N, Z                     |

|                      | IOR    | Wb,#lit5,Wd      | Wd = Wb .IOR. lit5                                                                           | 1             | 1              | N, Z                     |

| LNK                  | LNK    | #lit14           | Link Frame Pointer                                                                           | 1             | 1              | None                     |

| LSR                  | LSR    | f                | f = Logical Right Shift f                                                                    | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | f,WREG           | WREG = Logical Right Shift f                                                                 | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Ws,Wd            | Wd = Logical Right Shift Ws                                                                  | 1             | 1              | C, N, OV, Z              |

|                      | LSR    | Wb,Wns,Wnd       | Wnd = Logical Right Shift Wb by Wns                                                          | 1             | 1              | N, Z                     |

|                      | LSR    | Wb,#lit4,Wnd     | Wnd = Logical Right Shift Wb by lit4                                                         | 1             | 1              | N, Z                     |

| MOV                  | MOV    | f,Wn             | Move f to Wn                                                                                 | 1             | 1              | None                     |

|                      | MOV    | [Wns+Slit10],Wnd | Move [Wns+Slit10] to Wnd                                                                     | 1             | 1              | None                     |

|                      | MOV    | f                | Move f to f                                                                                  | 1             | 1              | N, Z                     |

|                      | MOV    | f,WREG           | Move f to WREG                                                                               | 1             | 1              | None                     |

|                      | MOV    | #lit16,Wn        | Move 16-bit Literal to Wn                                                                    | 1             | 1              | None                     |

|                      | MOV.b  | #lit8,Wn         | Move 8-bit Literal to Wn                                                                     | 1             | 1              | None                     |

|                      | MOV    | Wn,f             | Move Wn to f                                                                                 | 1             | 1              | None                     |

|                      | MOV    | Wns,[Wns+Slit10] | Move Wns to [Wns+Slit10]                                                                     | 1             | 1              | None                     |

|                      | MOV    | Wso,Wdo          | Move Ws to Wd                                                                                | 1             | 1              | None                     |

|                      | MOV    | WREG, f          | Move WREG to f                                                                               | 1             | 1              | None                     |

|                      | MOV.D  | Wns,Wd           | Move Double from W(ns):W(ns+1) to Wd                                                         | 1             | 2              | None                     |

|                      | MOV.D  | Wis, Wnd         | Move Double from Ws to W(nd+1):W(nd)                                                         | 1             | 2              | None                     |

| MUL                  | MUL.SS | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Signed(Ws)                                                       | 1             | 1              | None                     |

| MOL                  | MUL.SU | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(Ws) {Wnd+1, Wnd} = Signed(Wb) * Unsigned(Ws)            | 1             | 1              | None                     |

|                      | MUL.US | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Unsigned(Wb) * Signed(Ws)                                                     | 1             | 1              | None                     |

|                      | MUL.UU |                  | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(Ws)<br>{Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(Ws)     | 1             | 1              | None                     |

|                      | MUL.SU | Wb,Ws,Wnd        | {Wnd+1, Wnd} = Signed(Wb) * Unsigned(lit5)                                                   | 1             | 1              | None                     |

|                      | MUL.UU | Wb,#lit5,Wnd     | {Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(lit5)<br>{Wnd+1, Wnd} = Unsigned(Wb) * Unsigned(lit5) | 1             | 1              | None                     |

|                      |        | Wb,#lit5,Wnd     | W3:W2 = f * WREG                                                                             | 1             | 1              | None                     |

|                      | MUL    | f                | $f = \overline{f} + 1$                                                                       |               |                |                          |

| NEG                  | NEG    | f                | _                                                                                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG    | f,WREG           | WREG = f + 1                                                                                 | 1             | 1              | C, DC, N, OV, Z          |

|                      | NEG    | Ws,Wd            | Wd = Ws + 1                                                                                  | 1             | 1              | C, DC, N, OV, Z          |

| NOP                  | NOP    |                  | No Operation                                                                                 | 1             | 1              | None                     |

|                      | NOPR   |                  | No Operation                                                                                 | 1             | 1              | None                     |

| POP                  | POP    | f                | Pop f from Top-of-Stack (TOS)                                                                | 1             | 1              | None                     |

|                      | POP    | Wdo              | Pop from Top-of-Stack (TOS) to Wdo                                                           | 1             | 1              | None                     |

|                      | POP.D  | Wnd              | Pop from Top-of-Stack (TOS) to W(nd):W(nd+1)                                                 | 1             | 2              | None                     |

|                      | POP.S  |                  | Pop Shadow Registers                                                                         | 1             | 1              | All                      |

| PUSH                 | PUSH   | f                | Push f to Top-of-Stack (TOS)                                                                 | 1             | 1              | None                     |

|                      | PUSH   | Wso              | Push Wso to Top-of-Stack (TOS)                                                               | 1             | 1              | None                     |

|                      | PUSH.D | Wns              | Push W(ns):W(ns+1) to Top-of-Stack (TOS)                                                     | 1             | 2              | None                     |

|                      | PUSH.S |                  | Push Shadow Registers                                                                        | 1             | 1              | None                     |

### TABLE 27-16: PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.0V TO 3.6V)

|              |       |                                  | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                    |          |            |                                                                                                                           |

|--------------|-------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|------------|---------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic <sup>(1)</sup>    | Min                                                                                                                                                                                                  | Тур <sup>(2)</sup> | Max      | Units      | Conditions                                                                                                                |

| OS50         | Fplli | PLL Input Frequency<br>Range     | 3<br>3                                                                                                                                                                                               | _                  | 8<br>6   | MHz<br>MHz | ECPLL, HSPLL, XTPLL modes,<br>-40°C $\leq$ TA $\leq$ +85°C<br>ECPLL, HSPLL, XTPLL modes,<br>-40°C $\leq$ TA $\leq$ +125°C |

| OS51         | Fsys  | PLL Output Frequency<br>Range    | 8<br>8                                                                                                                                                                                               | _                  | 32<br>24 | MHz<br>MHz | $\begin{array}{l} -40^\circ C \leq TA \leq +85^\circ C \\ -40^\circ C \leq TA \leq +125^\circ C \end{array}$              |

| OS52         | TLOCK | PLL Start-up Time<br>(Lock Time) | -                                                                                                                                                                                                    | —                  | 2        | ms         |                                                                                                                           |

| OS53         | DCLK  | CLKO Stability (Jitter)          | -2                                                                                                                                                                                                   | 1                  | 2        | %          | Measured over 100 ms period                                                                                               |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 27-17: INTERNAL RC OSCILLATOR SPECIFICATIONS

| AC CHARACTERISTICS |       |                    | Standard Operating Conditions:<br>Operating temperature |     |     | 2.0V to 3.6V (unless otherwise stated) -40°C $\leq$ TA $\leq$ +85°C for Industrial -40°C $\leq$ TA $\leq$ +125°C for Extended |            |

|--------------------|-------|--------------------|---------------------------------------------------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------|------------|

| Param<br>No.       | Sym   | Characteristic     | Min                                                     | Тур | Max | Units                                                                                                                         | Conditions |

|                    | TFRC  | FRC Start-up Time  | _                                                       | 15  | _   | μS                                                                                                                            |            |

|                    | TLPRC | LPRC Start-up Time | _                                                       | 40  | —   | μS                                                                                                                            |            |

#### TABLE 27-18: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| AC CHARACTERISTICS          |                                     | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |     |       |                                       |                                  |  |  |

|-----------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|---------------------------------------|----------------------------------|--|--|