# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32ga002-e-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### TABLE 4-8: OUTPUT COMPARE REGISTER MAP

|              |      |        | •••••  |        | LOIOI  |        |        |          |           |             |          |       |       |        |       |       |       |               |

|--------------|------|--------|--------|--------|--------|--------|--------|----------|-----------|-------------|----------|-------|-------|--------|-------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8     | Bit 7       | Bit 6    | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| OC1RS        | 0180 |        |        |        |        |        |        | Output 0 | Compare 1 | Secondary   | Register |       |       |        |       |       |       | FFFF          |

| OC1R         | 0182 |        |        |        |        |        |        | Οι       | tput Comp | are 1 Regis | ter      |       |       |        |       |       |       | FFFF          |

| OC1CON       | 0184 | _      | —      | OCSIDL | _      | _      | —      | —        | _         | _           | —        | —     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC2RS        | 0186 |        |        |        |        |        |        | Output 0 | Compare 2 | Secondary   | Register |       |       |        |       |       |       | FFFF          |

| OC2R         | 0188 |        |        |        |        |        |        | Οι       | tput Comp | are 2 Regis | ter      |       |       |        |       |       |       | FFFF          |

| OC2CON       | 018A | _      | _      | OCSIDL | _      | _      | _      | _        | _         | _           | _        | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC3RS        | 018C |        |        |        |        |        |        | Output 0 | Compare 3 | Secondary   | Register |       |       |        |       |       |       | FFFF          |

| OC3R         | 018E |        |        |        |        |        |        | Οι       | tput Comp | are 3 Regis | ter      |       |       |        |       |       |       | FFFF          |

| OC3CON       | 0190 | _      | _      | OCSIDL | _      | _      | _      | _        | _         | _           | _        | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC4RS        | 0192 |        |        |        |        |        |        | Output 0 | Compare 4 | Secondary   | Register |       |       |        |       |       |       | FFFF          |

| OC4R         | 0194 |        |        |        |        |        |        | Οι       | tput Comp | are 4 Regis | ter      |       |       |        |       |       |       | FFFF          |

| OC4CON       | 0196 | _      | _      | OCSIDL | _      | _      | _      | _        | _         | _           | _        | _     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

| OC5RS        | 0198 |        |        |        |        |        |        | Output ( | Compare 5 | Secondary   | Register |       |       |        |       |       |       | FFFF          |

| OC5R         | 019A |        |        |        |        |        |        | Οι       | tput Comp | are 5 Regis | ter      |       |       |        |       |       |       | FFFF          |

| OC5CON       | 019C | _      | _      | OCSIDL | _      | _      | —      | —        | —         | _           | —        | —     | OCFLT | OCTSEL | OCM2  | OCM1  | OCM0  | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-9: I<sup>2</sup>C<sup>™</sup> REGISTER MAP

|              | -    |         |        |         |        |        |        |        |       |       |       |            |             |              |       |       |       |               |

|--------------|------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|------------|-------------|--------------|-------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| I2C1RCV      | 0200 | _       |        | —       | _      | _      | _      | —      | —     |       |       |            | I2C1 Recei  | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202 | _       | _      | _       | _      | _      | _      | _      | _     |       |       |            | I2C1 Transr | nit Register | r     |       |       | OOFF          |

| I2C1BRG      | 0204 | _       | _      | _       | _      | _      | _      | _      |       |       |       | Baud Rate  | Generator   | Register 1   |       |       |       | 0000          |

| I2C1CON      | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A        | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A | _       | _      | _       | _      | _      | _      |        |       |       |       | I2C1 Addre | ss Register |              |       |       |       | 0000          |

| I2C1MSK      | 020C | _       | _      | _       | _      | _      | _      | AMSK9  | AMSK8 | AMSK7 | AMSK6 | AMSK5      | AMSK4       | AMSK3        | AMSK2 | AMSK1 | AMSK0 | 0000          |

| I2C2RCV      | 0210 | _       | —      | _       | _      | _      | _      | _      | _     |       |       |            | I2C2 Receiv | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212 | _       | —      | _       | _      | _      | _      | _      | _     |       |       |            | I2C2 Transr | nit Register | r     |       |       | OOFF          |

| I2C2BRG      | 0214 | _       | —      | _       | _      | _      | _      | _      |       |       |       | Baud Rate  | Generator   | Register 2   |       |       |       | 0000          |

| I2C2CON      | 0216 | I2CEN   | —      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218 | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D/A        | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A | _       |        | _       | _      | _      | _      |        | •     |       | •     | I2C2 Addre | ss Register |              | •     | •     | •     | 0000          |

| I2C2MSK      | 021C | _       |        | _       | _      | _      | —      | AMSK9  | AMSK8 | AMSK7 | AMSK6 | AMSK5      | AMSK4       | AMSK3        | AMSK2 | AMSK1 | AMSK0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/SO-0            | R/W-0                                                                                                    | R/W-0                                                                                | U-0                                                                                     | U-0                                                                     | U-0                               | U-0                            | U-0                            |

|-------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------|--------------------------------|--------------------------------|

| WR                | WREN                                                                                                     | WRERR                                                                                | —                                                                                       | —                                                                       | —                                 | —                              | —                              |

| bit 15            |                                                                                                          |                                                                                      |                                                                                         |                                                                         |                                   |                                | bit 8                          |

|                   |                                                                                                          |                                                                                      |                                                                                         | DAALO                                                                   | DAMA                              | DAMA                           | DAMO                           |

| U-0               | R/W-0                                                                                                    | U-0                                                                                  | U-0                                                                                     | R/W-0<br>NVMOP3 <sup>(1)</sup>                                          | R/W-0<br>NVMOP2 <sup>(1)</sup>    | R/W-0<br>NVMOP1 <sup>(1)</sup> | R/W-0<br>NVMOP0 <sup>(1)</sup> |

|                   | ERASE                                                                                                    | —                                                                                    | —                                                                                       | NVMOP3                                                                  | NVMOP207                          | NVMOP1**                       |                                |

| bit 7             |                                                                                                          |                                                                                      |                                                                                         |                                                                         |                                   |                                | bit                            |

| Legend:           |                                                                                                          | SO = Settable                                                                        | Only bit                                                                                |                                                                         |                                   |                                |                                |

| R = Reada         | able bit                                                                                                 | W = Writable                                                                         | bit                                                                                     | U = Unimplem                                                            | nented bit, read                  | as '0'                         |                                |

| -n = Value        | at POR                                                                                                   | '1' = Bit is set                                                                     |                                                                                         | '0' = Bit is clea                                                       | ared                              | x = Bit is unkr                | iown                           |

| bit 14<br>bit 13  | 0 = Program<br>WREN: Write<br>1 = Enables<br>0 = Inhibits F<br>WRERR: Writ<br>1 = An impro-<br>automatic | Flash program/<br>lash program/e<br>te Sequence E<br>oper program<br>cally on any se | tion is complet<br>erase operation<br>rror Flag bit<br>or erase seq<br>t attempt of the | e and inactive<br>ns<br>is<br>uence attempt<br>WR bit)                  | or terminatio                     | n has occurre                  | ed (bit is s                   |

| 1 1 40 7          |                                                                                                          | ram or erase o                                                                       |                                                                                         | leted normally                                                          |                                   |                                |                                |

| bit 12-7<br>bit 6 | =                                                                                                        | ted: Read as '<br>e/Program Ena                                                      |                                                                                         |                                                                         |                                   |                                |                                |

| DIL O             | 1 = Performs                                                                                             | the erase ope                                                                        | ration specified                                                                        | l by the NVMOI<br>fied by the NVM                                       |                                   |                                |                                |

| bit 5-4           | Unimplemen                                                                                               | ted: Read as '                                                                       | )'                                                                                      |                                                                         |                                   |                                |                                |

| bit 3-0           | NVMOP<3:0>                                                                                               | -: NVM Operat                                                                        | ion Select bits <sup>(</sup>                                                            | 1)                                                                      |                                   |                                |                                |

|                   | 0011 = Memo<br>0010 = Memo                                                                               | ory word progra                                                                      | m operation (E<br>operation (ER                                                         | SE = 1) or no o<br>ERASE = 0) or 1<br>ASE = 1) or no<br>RASE = 0) or no | no operation (E<br>operation (ER/ | RASE = 1)<br>ASE = 0)          |                                |

| Note 1:           | All other combina                                                                                        | tions of NVMO                                                                        | P<3:0> are uni                                                                          | implemented.                                                            |                                   |                                |                                |

| 2:                | Available in ICSP                                                                                        |                                                                                      |                                                                                         |                                                                         |                                   |                                |                                |

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 2 IDLE: Wake-up from Idle Flag bit 1 = Device has been in Idle mode

- 0 = Device has not been in Idle mode

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred (note that BOR is also set after a Power-on Reset)

- 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| Flag Bit          | Setting Event                                     | Clearing Event          |

|-------------------|---------------------------------------------------|-------------------------|

| TRAPR (RCON<15>)  | Trap Conflict Event                               | POR                     |

| IOPUWR (RCON<14>) | Illegal Opcode or Uninitialized W Register Access | POR                     |

| CM (RCON<9>)      | Configuration Mismatch Reset                      | POR                     |

| EXTR (RCON<7>)    | MCLR Reset                                        | POR                     |

| SWR (RCON<6>)     | RESET Instruction                                 | POR                     |

| WDTO (RCON<4>)    | WDT Time-out                                      | PWRSAV Instruction, POR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP Instruction                         | POR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE Instruction                          | POR                     |

| BOR (RCON<1>)     | POR, BOR                                          | —                       |

| POR (RCON<0>)     | POR                                               | —                       |

#### TABLE 6-1: RESET FLAG BIT OPERATION

**Note:** All Reset flag bits may be set or cleared by the user software.

NOTES:

| U-0          | U-0           | R/W-0                             | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

|--------------|---------------|-----------------------------------|------------------|-------------------|-----------------|-----------------|--------|

| _            | —             | AD1IF                             | U1TXIF           | U1RXIF            | SPI1IF          | SPF1IF          | T3IF   |

| bit 15       |               |                                   | •                |                   |                 | ·               | bit 8  |

| R/W-0        | R/W-0         | R/W-0                             | U-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

| T2IF         | OC2IF         | IC2IF                             | _                | T1IF              | OC1IF           | IC1IF           | INTOIF |

| bit 7        | 002li         | 10211                             |                  |                   | 00111           | 10111           | bit    |

| Legend:      |               |                                   |                  |                   |                 |                 |        |

| R = Readab   | le bit        | W = Writable                      | bit              | U = Unimplem      | nented bit. rea | d as '0'        |        |

| -n = Value a | t POR         | '1' = Bit is set                  |                  | '0' = Bit is clea |                 | x = Bit is unkn | iown   |

|              |               |                                   |                  |                   |                 |                 |        |

| bit 15-14    | Unimpleme     | nted: Read as '                   | 0'               |                   |                 |                 |        |

| bit 13       | AD1IF: A/D    | Conversion Cor                    | nplete Interrup  | t Flag Status bit |                 |                 |        |

|              | 1 = Interrupt | request has oc<br>request has no  | curred           | U                 |                 |                 |        |

| bit 12       | •             | RT1 Transmitte                    |                  | Status bit        |                 |                 |        |

|              | 1 = Interrupt | request has oc                    | curred           |                   |                 |                 |        |

| L:1 4 4      | •             | request has no                    |                  |                   |                 |                 |        |

| oit 11       |               | RT1 Receiver li<br>request has oc |                  |                   |                 |                 |        |

|              |               | request has no                    |                  |                   |                 |                 |        |

| bit 10       | -             | 1 Event Interrup                  |                  | it                |                 |                 |        |

|              | 1 = Interrupt | request has oc<br>request has no  | curred           |                   |                 |                 |        |

| bit 9        |               | 1 Fault Interrup                  |                  | it                |                 |                 |        |

| bit 0        |               | request has oc                    | •                | it i              |                 |                 |        |

|              | •             | request has no                    |                  |                   |                 |                 |        |

| bit 8        | T3IF: Timer3  | B Interrupt Flag                  | Status bit       |                   |                 |                 |        |

|              |               | request has oc<br>request has no  |                  |                   |                 |                 |        |

| bit 7        | T2IF: Timer2  | 2 Interrupt Flag                  | Status bit       |                   |                 |                 |        |

|              | •             | request has oc                    |                  |                   |                 |                 |        |

| hit C        | •             | request has no                    |                  | nt Flag Status k  | .:+             |                 |        |

| bit 6        | -             | out Compare Ch<br>request has oc  |                  | pi riag Status i  | JIL             |                 |        |

|              | •             | request has no                    |                  |                   |                 |                 |        |

| bit 5        | IC2IF: Input  | Capture Chann                     | el 2 Interrupt F | lag Status bit    |                 |                 |        |

|              | •             | request has oc<br>request has no  |                  |                   |                 |                 |        |

| bit 4        | -             | nted: Read as '                   |                  |                   |                 |                 |        |

| bit 3        | -             | Interrupt Flag                    |                  |                   |                 |                 |        |

|              |               | request has oc                    |                  |                   |                 |                 |        |

|              |               | request has no                    |                  |                   |                 |                 |        |

| bit 2        | -             | out Compare Ch                    |                  | pt Flag Status b  | pit             |                 |        |

|              |               | request has oc                    |                  |                   |                 |                 |        |

|              |               | request has no                    |                  |                   |                 |                 |        |

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0            | U-0              | R/W-0                             | R/W-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0                 |

|----------------|------------------|-----------------------------------|-------------------|-------------------|-----------------|-----------------|-----------------------|

| _              | _                | AD1IE                             | U1TXIE            | U1RXIE            | SPI1IE          | SPF1IE          | T3IE                  |

| bit 15         |                  |                                   |                   | •                 |                 |                 | bit                   |

|                |                  |                                   |                   |                   |                 |                 |                       |

| R/W-0          | R/W-0            | R/W-0                             | U-0               | R/W-0             | R/W-0           | R/W-0           | R/W-0                 |

| T2IE           | OC2IE            | IC2IE                             | —                 | T1IE              | OC1IE           | IC1IE           | INT0IE <sup>(1)</sup> |

| bit 7          |                  |                                   |                   |                   |                 |                 | bit                   |

| Legend:        |                  |                                   |                   |                   |                 |                 |                       |

| R = Readable   | e bit            | W = Writable                      | bit               | U = Unimplem      | ented bit, read | l as '0'        |                       |

| -n = Value at  | POR              | '1' = Bit is set                  |                   | '0' = Bit is clea | red             | x = Bit is unkn | iown                  |

|                |                  |                                   |                   |                   |                 |                 |                       |

| bit 15-14      | -                | ted: Read as '                    |                   |                   |                 |                 |                       |

| bit 13         |                  |                                   | nplete Interrup   | t Enable bit      |                 |                 |                       |

|                | •                | equest is enab<br>equest is not e |                   |                   |                 |                 |                       |

| bit 12         | -                | -                                 | r Interrupt Enal  | hle hit           |                 |                 |                       |

|                |                  | equest is enab                    | •                 |                   |                 |                 |                       |

|                |                  | equest is not e                   |                   |                   |                 |                 |                       |

| bit 11         | U1RXIE: UAR      | RT1 Receiver In                   | nterrupt Enable   | e bit             |                 |                 |                       |

|                |                  | equest is enab<br>equest is not e |                   |                   |                 |                 |                       |

| bit 10         | -                | -                                 | olete Interrupt I | Enable bit        |                 |                 |                       |

|                |                  | equest is enab                    | •                 |                   |                 |                 |                       |

|                | •                | equest is not e                   |                   |                   |                 |                 |                       |

| bit 9          |                  | Fault Interrup                    |                   |                   |                 |                 |                       |

|                |                  | equest is enab<br>equest is not e |                   |                   |                 |                 |                       |

| bit 8          | -                | Interrupt Enab                    |                   |                   |                 |                 |                       |

|                |                  | equest is enab                    |                   |                   |                 |                 |                       |

|                | 0 = Interrupt r  | equest is not e                   | nabled            |                   |                 |                 |                       |

| bit 7          |                  | Interrupt Enab                    |                   |                   |                 |                 |                       |

|                | •                | equest is enab                    |                   |                   |                 |                 |                       |

| bit 6          | •                | equest is not e                   | annel 2 Interru   | unt Enable bit    |                 |                 |                       |

|                | -                | equest is enab                    |                   |                   |                 |                 |                       |

|                |                  | equest is not e                   |                   |                   |                 |                 |                       |

| bit 5          | IC2IE: Input C   | Capture Chann                     | el 2 Interrupt E  | nable bit         |                 |                 |                       |

|                | •                | equest is enab                    |                   |                   |                 |                 |                       |

| L:1 1          | -                | equest is not e                   |                   |                   |                 |                 |                       |

| bit 4<br>bit 3 | -                | ted: Read as '                    |                   |                   |                 |                 |                       |

| UIL J          | I IIE. IIIIief I | Interrupt Enab                    |                   |                   |                 |                 |                       |

|                | 1 = Interrupt r  | equest is enab                    | led               |                   |                 |                 |                       |

#### REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

**Note 1:** If INTxIE = 1, this external interrupt input must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

|                    | R/W-1                                                                                                                                                                | R/W-0                                                                                                                                                                    | R/W-0                                                                                                  | U-0                                | R/W-1            | R/W-0           | R/W-0  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------|------------------|-----------------|--------|

|                    | T4IP2                                                                                                                                                                | T4IP1                                                                                                                                                                    | T4IP0                                                                                                  | _                                  | OC4IP2           | OC4IP1          | OC4IP0 |

| bit 15             |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 | bit 8  |

|                    |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| U-0                | R/W-1                                                                                                                                                                | R/W-0                                                                                                                                                                    | R/W-0                                                                                                  | U-0                                | U-0              | U-0             | U-0    |

| <br>bit 7          | OC3IP2                                                                                                                                                               | OC3IP1                                                                                                                                                                   | OC3IP0                                                                                                 | _                                  | _                | _               | bit (  |

|                    |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 | Ditt   |

| Legend:            |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| R = Readab         | ole bit                                                                                                                                                              | W = Writable                                                                                                                                                             | bit                                                                                                    | U = Unimplen                       | nented bit, read | d as '0'        |        |

| -n = Value a       | at POR                                                                                                                                                               | '1' = Bit is set                                                                                                                                                         |                                                                                                        | '0' = Bit is clea                  | ared             | x = Bit is unkr | nown   |

|                    |                                                                                                                                                                      |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| bit 15             | Unimplemen                                                                                                                                                           | ted: Read as '                                                                                                                                                           | 0'                                                                                                     |                                    |                  |                 |        |

| bit 14-12          | <b>T4IP&lt;2:0&gt;:</b> ⊺i                                                                                                                                           | imer4 Interrupt                                                                                                                                                          | Priority bits                                                                                          |                                    |                  |                 |        |

|                    | 111 = Interrup                                                                                                                                                       | pt is Priority 7 (                                                                                                                                                       | highest priority                                                                                       | / interrupt)                       |                  |                 |        |

|                    | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

|                    | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

|                    | •                                                                                                                                                                    |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

|                    | •<br>001 = Interrup                                                                                                                                                  | pt is Priority 1                                                                                                                                                         |                                                                                                        |                                    |                  |                 |        |

|                    |                                                                                                                                                                      | pt is Priority 1<br>pt source is dis                                                                                                                                     | abled                                                                                                  |                                    |                  |                 |        |

| bit 11             | 000 = Interru                                                                                                                                                        |                                                                                                                                                                          |                                                                                                        |                                    |                  |                 |        |

| bit 11<br>bit 10-8 | 000 = Interrup<br>Unimplemen                                                                                                                                         | pt source is dis<br>ted: Read as '                                                                                                                                       | 0'                                                                                                     | Interrupt Priorit                  | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br>ted: Read as '                                                                                                                                       | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br><b>ted:</b> Read as '<br>Output Compa                                                                                                                | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br><b>ted:</b> Read as '<br>Output Compa                                                                                                                | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | / bits           |                 |        |

|                    | 000 = Interru<br>Unimplemen<br>OC4IP<2:0>:                                                                                                                           | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (                                                                                                 | <sup>0'</sup><br>are Channel 4                                                                         | • •                                | y bits           |                 |        |

|                    | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                       | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (                                                                                                 | <sup>0'</sup><br>are Channel 4<br>highest priority                                                     | • •                                | / bits           |                 |        |

|                    | 000 = Interrup<br>Unimplemen<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                        | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1                                                                             | <sub>0</sub> '<br>are Channel 4<br>highest priority<br>abled                                           | • •                                | / bits           |                 |        |

| bit 10-8           | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup                                                                                                       | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '                                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br>0'                                      | • •                                |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '                                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa                       | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:                                     | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 ( | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br><sup>0'</sup><br>are Channel 3          | y interrupt)<br>Interrupt Priority |                  |                 |        |

| bit 10-8<br>bit 7  | 000 = Interrup<br>Unimplement<br>OC4IP<2:0>:<br>111 = Interrup<br>001 = Interrup<br>000 = Interrup<br>Unimplement<br>OC3IP<2:0>:<br>111 = Interrup<br>001 = Interrup | pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br>ted: Read as '<br>Output Compa<br>pt is Priority 7 ( | <sup>0'</sup><br>are Channel 4<br>highest priority<br>abled<br>0'<br>are Channel 3<br>highest priority | y interrupt)<br>Interrupt Priority |                  |                 |        |

#### REGISTER 7-21: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

REGISTER 7-25: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0           | U-0           | U-0                | U-0              | U-0                | U-0              | U-0             | U-0   |

|---------------|---------------|--------------------|------------------|--------------------|------------------|-----------------|-------|

| _             | —             |                    |                  | —                  | —                | —               | _     |

| bit 15        |               |                    |                  |                    |                  |                 | bit 8 |

|               |               |                    |                  |                    |                  |                 |       |

| U-0           | R/W-1         | R/W-0              | R/W-0            | U-0                | U-0              | U-0             | U-0   |

| _             | OC5IP2        | OC5IP1             | OC5IP0           | —                  | —                | —               | —     |

| bit 7         |               |                    |                  | ·                  |                  |                 | bit 0 |

|               |               |                    |                  |                    |                  |                 |       |

| Legend:       |               |                    |                  |                    |                  |                 |       |

| R = Readable  | e bit         | W = Writable       | bit              | U = Unimplen       | nented bit, read | l as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set   |                  | '0' = Bit is clea  | ared             | x = Bit is unkr | iown  |

|               |               |                    |                  |                    |                  |                 |       |

| bit 15-7      | Unimplemen    | ted: Read as '     | 0'               |                    |                  |                 |       |

| bit 6-4       | OC5IP<2:0>:   | Output Compa       | are Channel 5 I  | Interrupt Priority | y bits           |                 |       |

|               | 111 = Interru | pt is Priority 7 ( | highest priority | / interrupt)       |                  |                 |       |

|               | •             |                    |                  |                    |                  |                 |       |

|               | •             |                    |                  |                    |                  |                 |       |

|               | •             |                    |                  |                    |                  |                 |       |

|               | 001 = Interru |                    |                  |                    |                  |                 |       |

|               | 000 = Interru | pt source is dis   | abled            |                    |                  |                 |       |

|               |               |                    |                  |                    |                  |                 |       |

bit 3-0 Unimplemented: Read as '0'

#### REGISTER 7-26: IPC11: INTERRUPT PRIORITY CONTROL REGISTER 11

| U-0          | U-0           | U-0                | U-0              | U-0               | U-0              | U-0                | U-0   |  |

|--------------|---------------|--------------------|------------------|-------------------|------------------|--------------------|-------|--|

| _            | —             | —                  | —                | —                 | —                | —                  | —     |  |

| bit 15       |               |                    |                  |                   |                  |                    | bit 8 |  |

|              |               |                    |                  |                   |                  |                    |       |  |

| U-0          | R/W-1         | R/W-0              | R/W-0            | U-0               | U-0              | U-0                | U-0   |  |

| _            | PMPIP2        | PMPIP1             | PMPIP0           | —                 | —                | —                  |       |  |

| bit 7        |               |                    |                  |                   |                  |                    | bit 0 |  |

|              |               |                    |                  |                   |                  |                    |       |  |

| Legend:      |               |                    |                  |                   |                  |                    |       |  |

| R = Readab   | le bit        | W = Writable       | bit              | U = Unimplem      | nented bit, read | l as '0'           |       |  |

| -n = Value a | t POR         | '1' = Bit is set   |                  | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |

|              |               |                    |                  |                   |                  |                    |       |  |

| bit 15-7     | Unimplemen    | ted: Read as '0    | )'               |                   |                  |                    |       |  |

| bit 6-4      | PMPIP<2:0>    | : Parallel Maste   | r Port Interrupt | t Priority bits   |                  |                    |       |  |

|              | 111 = Interru | pt is Priority 7 ( | highest priority | interrupt)        |                  |                    |       |  |

|              | •             |                    |                  |                   |                  |                    |       |  |

|              | •             |                    |                  |                   |                  |                    |       |  |

|              | •             |                    |                  |                   |                  |                    |       |  |

|              | 001 = Interru | pt is Priority 1   |                  |                   |                  |                    |       |  |

|              | 000 = Interru | pt source is dis   | abled            |                   |                  |                    |       |  |

| bit 3-0      | Unimplemen    | ted: Read as '     | )'               |                   |                  |                    |       |  |

|              |               |                    |                  |                   |                  |                    |       |  |

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7                   | CLKLOCK: Clock Selection Lock Enable bit                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | <u>If FSCM is enabled (FCKSM1 = 1):</u>                                                                                                                                                                                                                                                                                                                                           |

|                         | 1 = Clock and PLL selections are locked                                                                                                                                                                                                                                                                                                                                           |

|                         | 0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit                                                                                                                                                                                                                                                                                          |

|                         | <u>If FSCM is disabled (FCKSM1 = 0):</u>                                                                                                                                                                                                                                                                                                                                          |

|                         | Clock and PLL selections are never locked and may be modified by setting the OSWEN bit.                                                                                                                                                                                                                                                                                           |

| bit 6                   | IOLOCK: I/O Lock Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                        |

|                         | 1 = I/O lock is active                                                                                                                                                                                                                                                                                                                                                            |

|                         | 0 = I/O lock is not active                                                                                                                                                                                                                                                                                                                                                        |

| bit 5                   | LOCK: PLL Lock Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                          |

|                         | 1 = PLL module is in lock or PLL module start-up timer is satisfied                                                                                                                                                                                                                                                                                                               |

|                         | 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled                                                                                                                                                                                                                                                                                                   |

|                         |                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 4                   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                        |

| bit 4<br>bit 3          | <b>CF:</b> Clock Fail Detect bit                                                                                                                                                                                                                                                                                                                                                  |

|                         | •                                                                                                                                                                                                                                                                                                                                                                                 |

|                         | CF: Clock Fail Detect bit                                                                                                                                                                                                                                                                                                                                                         |

|                         | <b>CF:</b> Clock Fail Detect bit<br>1 = FSCM has detected a clock failure                                                                                                                                                                                                                                                                                                         |

| bit 3                   | <ul> <li>CF: Clock Fail Detect bit</li> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> </ul>                                                                                                                                                                                                                                      |

| bit 3<br>bit 2          | <ul> <li>CF: Clock Fail Detect bit</li> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                  |

| bit 3<br>bit 2          | CF: Clock Fail Detect bit<br>1 = FSCM has detected a clock failure<br>0 = No clock failure has been detected<br>Unimplemented: Read as '0'<br>SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                                                                                                                                                               |

| bit 3<br>bit 2          | <ul> <li>CF: Clock Fail Detect bit</li> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> <li>Unimplemented: Read as '0'</li> <li>SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit</li> <li>1 = Enables Secondary Oscillator</li> </ul>                                                                                         |

| bit 3<br>bit 2<br>bit 1 | <ul> <li>CF: Clock Fail Detect bit</li> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> <li>Unimplemented: Read as '0'</li> <li>SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit</li> <li>1 = Enables Secondary Oscillator</li> <li>0 = Disables Secondary Oscillator</li> </ul>                                              |

| bit 3<br>bit 2<br>bit 1 | <ul> <li>CF: Clock Fail Detect bit</li> <li>1 = FSCM has detected a clock failure</li> <li>0 = No clock failure has been detected</li> <li>Unimplemented: Read as '0'</li> <li>SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit</li> <li>1 = Enables Secondary Oscillator</li> <li>0 = Disables Secondary Oscillator</li> <li>OSWEN: Oscillator Switch Enable bit</li> </ul> |

Note 1: Reset values for these bits are determined by the FNOSCx Configuration bits.

- 2: The state of the IOLOCK bit can only be changed once an unlocking sequence has been executed. In addition, if the IOL1WAY Configuration bit is '1' once the IOLOCK bit is set, it cannot be cleared.

- 3: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

### 10.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"I/O* Ports with Peripheral Pin Select (PPS)" (DS39711).

All of the device pins (except VDD, VSS, MCLR and OSCI/CLKI) are shared between the peripherals and the Parallel I/O (PIO) ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 10.1 Parallel I/O (PIO) Ports

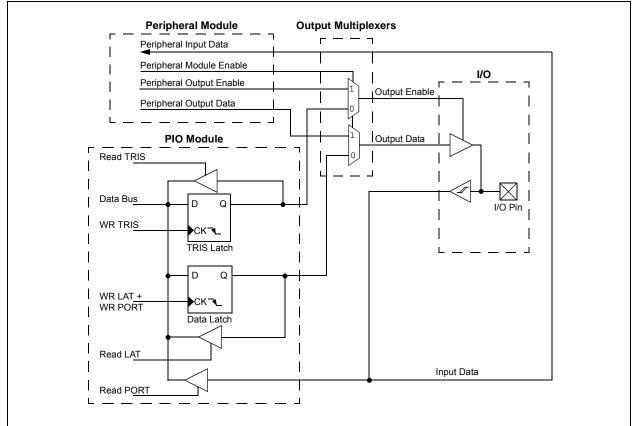

A Parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Output Latch register (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless, regarded as a dedicated port because there is no other competing source of outputs.

#### FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

| U-0                 | U-0                                    | U-0              | R/W-0                                  | R/W-0                 | R/W-0                  | R/W-0            | R/W-0              |

|---------------------|----------------------------------------|------------------|----------------------------------------|-----------------------|------------------------|------------------|--------------------|

| _                   | _                                      | _                | DISSCK <sup>(1)</sup>                  | DISSDO <sup>(2)</sup> | MODE16                 | SMP              | CKE <sup>(3)</sup> |

| bit 15              |                                        |                  |                                        |                       |                        |                  | bit                |

|                     |                                        |                  |                                        |                       |                        |                  |                    |

| R/W-0               |                                        | R/W-0            | R/W-0                                  | R/W-0                 | R/W-0                  | R/W-0            | R/W-0              |

| SSEN <sup>(4)</sup> | ) CKP                                  | MSTEN            | SPRE2                                  | SPRE1                 | SPRE0                  | PPRE1            | PPRE0              |

| bit 7               |                                        |                  |                                        |                       |                        |                  | bit                |

| Legend:             |                                        |                  |                                        |                       |                        |                  |                    |

| R = Reada           | able bit                               | W = Writable     | bit                                    | U = Unimplem          | nented bit, read       | as '0'           |                    |

| -n = Value          | at POR                                 | '1' = Bit is set |                                        | '0' = Bit is clea     |                        | x = Bit is unkn  | iown               |

|                     |                                        |                  | -                                      |                       |                        |                  | -                  |

| bit 15-13           | Unimplemen                             | ted: Read as '   | 0'                                     |                       |                        |                  |                    |