Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detalls                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

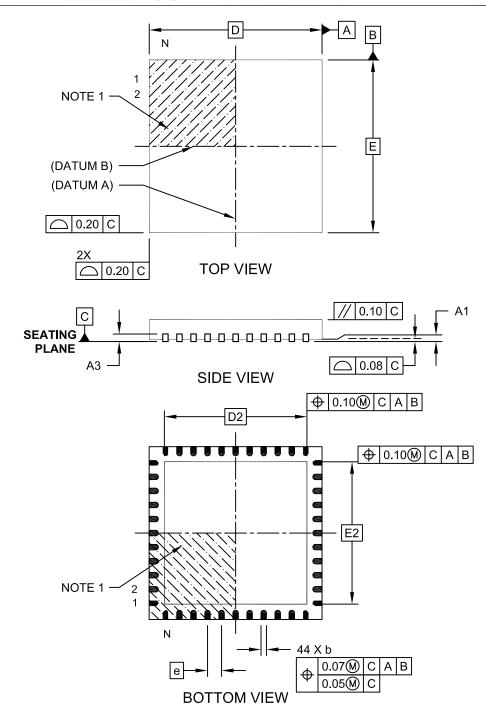

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32ga002-i-so |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                  | U-0                  | U-0                                    | U-0             | U-0                                      | U-0                | U-0               | R/W-0           |

|----------------------|----------------------|----------------------------------------|-----------------|------------------------------------------|--------------------|-------------------|-----------------|

| —                    | _                    | _                                      | —               | _                                        |                    | _                 | DC              |

| bit 15               |                      |                                        |                 |                                          |                    |                   | bit 8           |

|                      |                      |                                        |                 |                                          |                    |                   |                 |

| R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                   | R-0             | R/W-0                                    | R/W-0              | R/W-0             | R/W-0           |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>                    | RA              | N                                        | OV                 | Z                 | С               |

| bit 7                |                      |                                        |                 |                                          |                    |                   | bit (           |

| Legend:              |                      |                                        |                 |                                          |                    |                   |                 |

| R = Readat           | ole bit              | W = Writable                           | oit             | U = Unimplem                             | nented bit, read   | d as '0'          |                 |

| -n = Value a         | at POR               | '1' = Bit is set                       |                 | '0' = Bit is clea                        |                    | x = Bit is unki   | nown            |

|                      |                      |                                        |                 |                                          |                    |                   |                 |

| bit 15-9             | -                    | ted: Read as '0                        |                 |                                          |                    |                   |                 |

| bit 8                |                      | f Carry/Borrow I                       |                 |                                          |                    |                   |                 |

|                      |                      | out from the 4th sult occurred         | low-order bit ( | for byte-sized da                        | ata) or 8th low-   | order bit (for we | ord-sized data  |

|                      |                      |                                        | h or 8th low-o  | rder bit of the re                       | sult has occurr    | red               |                 |

| bit 7-5              | IPL<2:0>: CF         | PU Interrupt Price                     | ority Level Sta | itus bits <sup>(1,2)</sup>               |                    |                   |                 |

|                      |                      |                                        |                 | i); user interrupts                      | s are disabled     |                   |                 |

|                      |                      | nterrupt Priority                      |                 |                                          |                    |                   |                 |

|                      |                      | nterrupt Priority<br>nterrupt Priority |                 |                                          |                    |                   |                 |

|                      |                      | nterrupt Priority                      |                 |                                          |                    |                   |                 |

|                      | 010 = CPU Ir         | nterrupt Priority                      | Level is 2 (10  | )                                        |                    |                   |                 |

|                      |                      | nterrupt Priority<br>nterrupt Priority |                 |                                          |                    |                   |                 |

| bit 4                |                      | Loop Active bit                        |                 |                                          |                    |                   |                 |

|                      |                      | oop in progress                        |                 |                                          |                    |                   |                 |

|                      |                      | oop not in prog                        |                 |                                          |                    |                   |                 |

| bit 3                | N: ALU Nega          | itive bit                              |                 |                                          |                    |                   |                 |

|                      | 1 = Result wa        |                                        | , .             | <i></i> 、                                |                    |                   |                 |

| 1.11.0               |                      | as non-negative                        | (zero or posi   | tive)                                    |                    |                   |                 |

| bit 2                | OV: ALU Ove          |                                        | uned (O'e eero  | nlanaant) arithma                        | atia in this avith | motio operatio    | -               |

|                      |                      | occurred for sig                       |                 | plement) arithm                          | etic in this anth  | imetic operatio   | n               |

| bit 1                | Z: ALU Zero          | bit                                    |                 |                                          |                    |                   |                 |

|                      |                      |                                        |                 | as set it at some<br>ets the Z bit has o |                    |                   | sult)           |

| bit 0                | C: ALU Carry         | //Borrow bit                           |                 |                                          |                    |                   |                 |

|                      |                      |                                        |                 | bit of the result o<br>bit of the result |                    |                   |                 |

| Note 1: 7            | The IPL Status bi    | its are read-only                      | when NSTD       | IS (INTCON1<1                            | <b>5&gt;) =</b> 1. |                   |                 |

|                      | The IPL Status bi    | -                                      |                 |                                          |                    | n the CPU Inte    | errupt Priority |

| 1                    | aval (IDL) Thay      | value in parenth                       | oooo indiaata   | a tha IDI when                           |                    |                   | -               |

2: The IPL Status bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

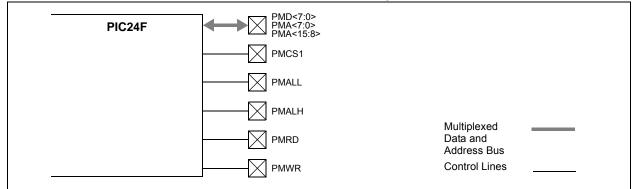

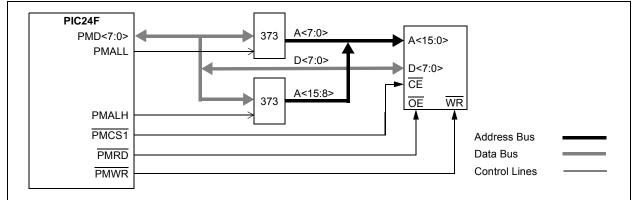

#### TABLE 4-17: PARALLEL MASTER/SLAVE PORT REGISTER MAP

|              |      |        |                                                                                                                                                                        |        |         | -       |        |                |              |                |              |        |        |        |        |        |        |               |

|--------------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|---------|--------|----------------|--------------|----------------|--------------|--------|--------|--------|--------|--------|--------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14                                                                                                                                                                 | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9          | Bit 8        | Bit 7          | Bit 6        | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| PMCON        | 0600 | PMPEN  |                                                                                                                                                                        | PSIDL  | ADRMUX1 | ADRMUX0 | PTBEEN | PTWREN         | PTRDEN       | CSF1           | CSF0         | ALP    |        | CS1P   | BEP    | WRSP   | RDSP   | 0000          |

| PMMODE       | 0602 | BUSY   | IRQM1                                                                                                                                                                  | IRQM0  | INCM1   | INCM0   | MODE16 | MODE1          | MODE0        | WAITB1         | WAITB0       | WAITM3 | WAITM2 | WAITM1 | WAITM0 | WAITE1 | WAITE0 | 0000          |

| PMADDR       | 0604 |        | CS1                                                                                                                                                                    | _      | _       | _       | ADDR10 | ADDR9          | ADDR8        | ADDR7          | ADDR6        | ADDR5  | ADDR4  | ADDR3  | ADDR2  | ADDR1  | ADDR0  | 0000          |

| PMDOUT1      |      |        |                                                                                                                                                                        |        |         |         | Pa     | rallel Port D  | ata Out Reg  | jister 1 (Buff | fers 0 and 1 | )      |        |        |        |        |        | 0000          |

| PMDOUT2      | 0606 |        |                                                                                                                                                                        |        |         |         | Pa     | rallel Port D  | ata Out Reg  | jister 2 (Buff | fers 2 and 3 | )      |        |        |        |        |        | 0000          |

| PMDIN1       | 0608 |        |                                                                                                                                                                        |        |         |         | Pa     | arallel Port [ | Data In Regi | ster 1 (Buffe  | ers 0 and 1) |        |        |        |        |        |        | 0000          |

| PMDIN2       | 060A |        |                                                                                                                                                                        |        |         |         | Pa     | arallel Port [ | Data In Regi | ster 2 (Buffe  | ers 2 and 3) |        |        |        |        |        |        | 0000          |

| PMAEN        | 060C |        | PTEN14         —         —         PTEN10         PTEN9         PTEN8         PTEN6         PTEN5         PTEN3         PTEN2         PTEN1         PTEN0         0000 |        |         |         |        |                |              |                |              |        |        |        |        |        |        |               |

| PMSTAT       | 060E | IBF    | IBOV                                                                                                                                                                   | —      | _       | IB3F    | IB2F   | IB1F           | IB0F         | OBE            | OBUF         | _      | _      | OB3E   | OB2E   | OB1E   | OB0E   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-18: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File<br>Name | Addr                                                        | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9         | Bit 8         | Bit 7     | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------------------------------------------------------------|--------|--------|---------|---------|---------|--------|---------------|---------------|-----------|-----------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL      | MVAL 0620 Alarm Value Register Window Based on ALRMPTR<1:0> |        |        |         |         |         |        |               |               |           |           |       |       | xxxx  |       |       |       |               |

| ALCFGRPT     | 0622                                                        | ALRMEN | CHIME  | AMASK3  | AMASK2  | AMASK1  | AMASK0 | ALRMPTR1      | ALRMPTR0      | ARPT7     | ARPT6     | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | 0000          |

| RTCVAL       | 0624                                                        |        |        |         |         |         | RTCC   | Value Registe | er Window Bas | sed on RT | CPTR<1:0> | >     |       |       |       |       |       | xxxx          |

| RCFGCAL      | 0626                                                        | RTCEN  |        | RTCWREN | RTCSYNC | HALFSEC | RTCOE  | RTCPTR1       | RTCPTR0       | CAL7      | CAL6      | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-19: DUAL COMPARATOR REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|---------|---------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| CMCON        | 0630 | CMIDL  | _      | C2EVT  | C1EVT  | C2EN   | C1EN   | C2OUTEN | C1OUTEN | C2OUT | C10UT | C2INV | C1INV | C2NEG | C2POS | C1NEG | C1POS | 0000          |

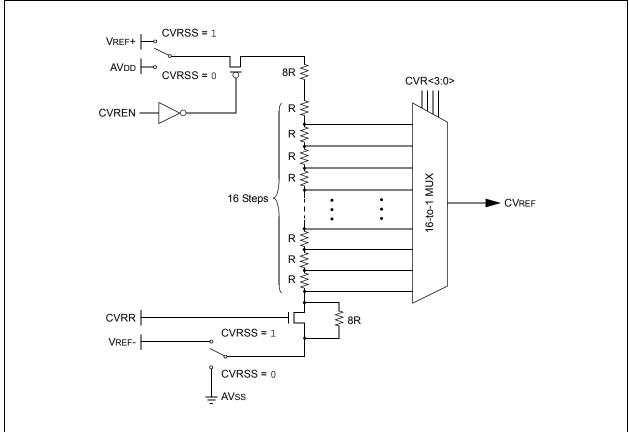

| CVRCON       | 0632 | —      | _      | _      | —      | _      |        | _       | _       | CVREN | CVROE | CVRR  | CVRSS | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: CRC REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7        | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|---------------------|--------|--------|--------|--------|--------|-------------|--------------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CRCCON       | 0640 | _      | _                   | CSIDL  | VWORD4 | VWORD3 | VWORD2 | VWORD1 | VWORD0      | CRCFUL       | CRCMPT | _     | CRCGO | PLEN3 | PLEN2 | PLEN1 | PLEN0 | 0040          |

| CRCXOR       | 0642 | X15    | X14                 | X13    | X12    | X11    | X10    | X9     | X8          | X7           | X6     | X5    | X4    | X3    | X2    | X1    | _     | 0000          |

| CRCDAT       | 0644 |        |                     |        |        |        |        | (      | CRC Data Ir | nput Registe | er     |       |       |       |       |       |       | 0000          |

| CRCWDAT      | 0646 |        | CRC Result Register |        |        |        |        |        |             |              |        |       |       |       | 0000  |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 7-30: IPC18: INTERRUPT PRIORITY CONTROL REGISTER 18

| U-0           | U-0           | U-0                | U-0              | U-0               | U-0              | U-0             | U-0    |

|---------------|---------------|--------------------|------------------|-------------------|------------------|-----------------|--------|

|               | —             | —                  | —                | —                 | —                | —               | —      |

| bit 15        |               |                    |                  |                   |                  |                 | bit 8  |

|               |               |                    |                  |                   |                  |                 |        |

| U-0           | U-0           | U-0                | U-0              | U-0               | R/W-1            | R/W-0           | R/W-0  |

|               | —             | —                  | —                | —                 | LVDIP2           | LVDIP1          | LVDIP0 |

| bit 7         |               |                    |                  |                   |                  |                 | bit 0  |

|               |               |                    |                  |                   |                  |                 |        |

| Legend:       |               |                    |                  |                   |                  |                 |        |

| R = Readabl   | e bit         | W = Writable       | bit              | U = Unimplem      | nented bit, read | l as '0'        |        |

| -n = Value at | POR           | '1' = Bit is set   |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown   |

|               |               |                    |                  |                   |                  |                 |        |

| bit 15-3      | Unimplemen    | ted: Read as '     | כ'               |                   |                  |                 |        |

| bit 2-0       | LVDIP<2:0>:   | Low-Voltage D      | etect Interrupt  | Priority bits     |                  |                 |        |

|               | 111 = Interru | ot is Priority 7 ( | highest priority | interrupt)        |                  |                 |        |

•

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

#### REGISTER 10-19: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0      | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------|-----|-----|-------|-------|-------|-------|-------|

| —        | —   | —   | RP9R4 | RP9R3 | RP9R2 | RP9R1 | RP9R0 |

| bit 15   |     |     |       |       |       |       | bit 8 |

|          |     |     |       |       |       |       |       |

| U-0      | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —        | —   | —   | RP8R4 | RP8R3 | RP8R2 | RP8R1 | RP8R0 |

| bit 7    |     |     |       | •     |       |       | bit 0 |

|          |     |     |       |       |       |       |       |

| l egend. |     |     |       |       |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

| bit 12-8 | <b>RP9R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP9 Output Pin bits |

|----------|---------------------------------------------------------------------------------------|

|          | (see Table 10-3 for peripheral function numbers)                                      |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin bits (see Table 10-3 for peripheral function numbers)

#### REGISTER 10-20: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | —   | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           |                                                        |                      |                    |  |  |

|-------------------|--------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | it W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                       | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 10-3 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 10-3 for peripheral function numbers)

#### REGISTER 10-25: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | —   | RP21R4 <sup>(1)</sup> | RP21R3 <sup>(1)</sup> | RP21R2 <sup>(1)</sup> | RP21R1 <sup>(1)</sup> | RP21R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|       | —   | —   | RP20R4 <sup>(1)</sup> | RP20R3 <sup>(1)</sup> | RP20R2 <sup>(1)</sup> | RP20R1 <sup>(1)</sup> | RP20R0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 12-8  | <b>RP21R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP21 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-3 for peripheral function numbers)                                                       |

| bit 7-5 | Unimplemented: Read as '0' |  |

|---------|----------------------------|--|

| bit 7-5 | Unimplemented: Read as '0' |  |

bit 4-0 **RP20R<4:0>:** Peripheral Output Function is Assigned to RP20 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|        | —   | _   | RP23R4 <sup>(1)</sup> | RP23R3 <sup>(1)</sup> | RP23R2 <sup>(1)</sup> | RP23R1 <sup>(1)</sup> | RP23R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

|        |     |     |                       |                       |                       |                       |                       |

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|        | —   | —   | RP22R4 <sup>(1)</sup> | RP22R3 <sup>(1)</sup> | RP22R2 <sup>(1)</sup> | RP22R1 <sup>(1)</sup> | RP22R0 <sup>(1)</sup> |

| bit 7  |     |     |                       |                       |                       |                       | bit 0                 |

#### REGISTER 10-26: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP23R<4:0>:** Peripheral Output Function is Assigned to RP23 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP22R<4:0>:** Peripheral Output Function is Assigned to RP22 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

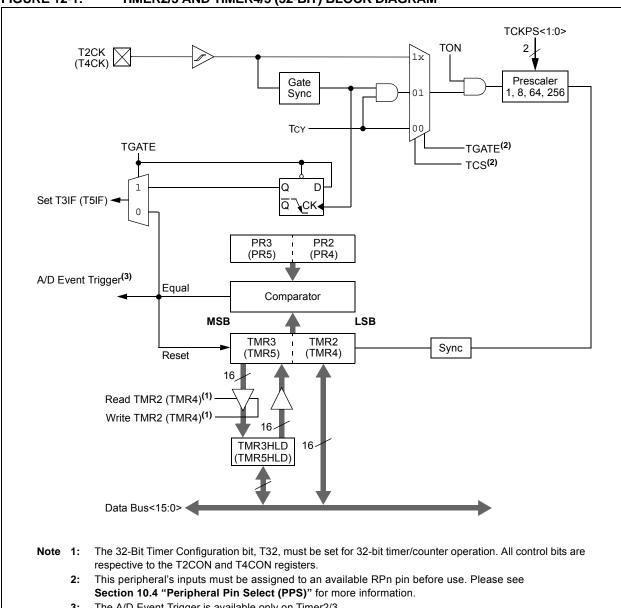

#### **FIGURE 12-1:** TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM

3: The A/D Event Trigger is available only on Timer2/3.

#### 14.4 Output Compare Register

#### REGISTER 14-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER

| U-0 | R/W-0  | U-0      | U-0                           | U-0                 | U-0                 | U-0                                                                                                                                          |

|-----|--------|----------|-------------------------------|---------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| —   | OCSIDL | —        | —                             | _                   | —                   | —                                                                                                                                            |

|     |        |          |                               |                     |                     | bit 8                                                                                                                                        |

|     |        |          |                               |                     |                     |                                                                                                                                              |

| U-0 | U-0    | R-0, HC  | R/W-0                         | R/W-0               | R/W-0               | R/W-0                                                                                                                                        |

|     | —      | OCFLT    | OCTSEL                        | OCM2 <sup>(1)</sup> | OCM1 <sup>(1)</sup> | OCM0 <sup>(1)</sup>                                                                                                                          |

|     |        |          |                               |                     |                     | bit 0                                                                                                                                        |

|     | _      | — OCSIDL | — OCSIDL —<br>U-0 U-0 R-0, HC | - OCSIDL            | - OCSIDL            | −         OCSIDL         −         −         −         −           U-0         U-0         R-0, HC         R/W-0         R/W-0         R/W-0 |

| Legend:           | HC = Hardware Clearable bit |                                    |                    |  |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Output Compare x Stop in Idle Mode Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           | <ul> <li>1 = Output Compare x halts in CPU Idle mode</li> <li>0 = Output Compare x continues to operate in CPU Idle mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in HW only)</li> <li>0 = No PWM Fault condition has occurred (this bit is only used when OCM&lt;2:0&gt; = 111)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 3     | OCTSEL: Output Compare x Timer Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | <ul> <li>1 = Timer3 is the clock source for Output Compare x</li> <li>0 = Timer2 is the clock source for Output Compare x</li> <li>Refer to the device data sheet for specific time bases available to the output compare module.</li> </ul>                                                                                                                                                                                                                                                                                                                                              |

| bit 2-0   | OCM<2:0>: Output Compare x Mode Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>111 = PWM mode on OCx; Fault pin, OCFx, is enabled<sup>(2)</sup></li> <li>110 = PWM mode on OCx; Fault pin, OCFx, is disabled<sup>(2)</sup></li> <li>101 = Initializes OCx pin low, generates continuous output pulses on OCx pin</li> <li>100 = Initializes OCx pin low, generates single output pulse on OCx pin</li> <li>011 = Compare event toggles OCx pin</li> <li>010 = Initializes OCx pin high, compare event forces OCx pin low</li> <li>001 = Initializes OCx pin low, compare event forces OCx pin high</li> <li>000 = Output compare channel is disabled</li> </ul> |

| Note 1:   | RPORx (OCx) must be configured to an available RPn pin. For more information, see Section 10.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

- "Peripheral Pin Select (PPS)".

- 2: The OCFA pin controls the OC1-OC4 channels. The OCFB pin controls the OC5 channel.

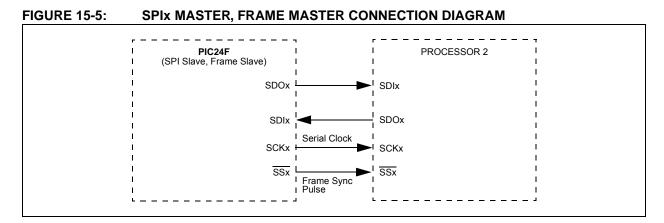

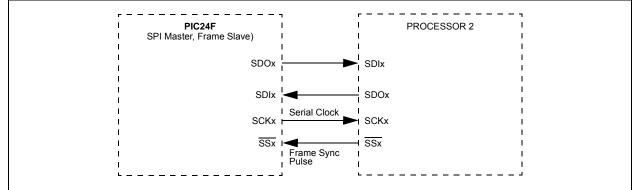

### 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Serial Peripheral Interface (SPI)"* (DS39699)

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the SPI and SIOP Motorola<sup>®</sup> interfaces.

The module supports operation in two buffer modes. In Standard mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through an 8-level FIFO buffer.

Note: Do not perform read-modify-write operations (such as bit-oriented instructions) on the SPIxBUF register in either Standard or Enhanced Buffer mode.

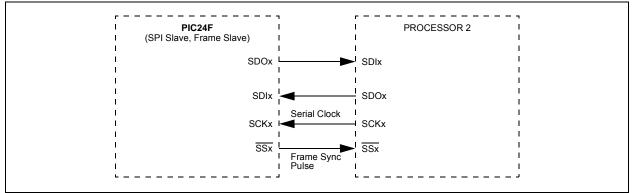

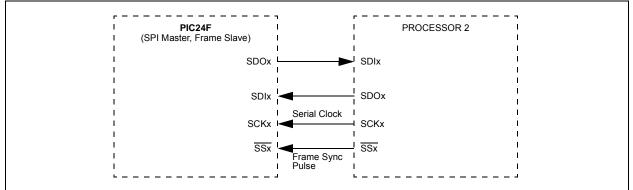

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The SPI serial interface consists of four pins:

- · SDIx: Serial Data Input

- SDOx: Serial Data Output

- · SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 15-1 and Figure 15-2.

Depending on the pin count, PIC24FJ64GA004 family devices offer one or two SPI modules on a single device.

Note: In this section, the SPI modules are referred to together as SPIx or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON1 or SPIxCON2 refers to the control register for the SPI1 or SPI2 module. To set up the SPIx module for the Standard Master mode of operation:

- 1. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

- 5. Write the data to be transmitted to the SPIxBUF register. Transmission (and reception) will start as soon as data is written to the SPIxBUF register.

To set up the SPIx module for the Standard Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- a) Clear the SPIxIF bit in the respective IFSx register.

- b) Set the SPIxIE bit in the respective IECx register.

- c) Write the SPIxIP bits in the respective IPCx register to set the interrupt priority.

- Write the desired settings to the SPIxCON1 and SPIxCON2 registers with the MSTEN bit (SPIxCON1<5>) = 0.

- 4. Clear the SMP bit (SPIxCON1<9>).

- 5. If the CKE bit is set, then the SSEN bit (SPIxCON1<7>) must be set to enable the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>).

- 7. Enable SPIx operation by setting the SPIEN bit (SPIxSTAT<15>).

© 2010-2013 Microchip Technology Inc.

#### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0, HSC             | R-0, HSC                                 | U-0                                  | U-0                     | U-0                          | R/C-0, HS                    | R-0, HSC           | R-0, HSC        |

|----------------------|------------------------------------------|--------------------------------------|-------------------------|------------------------------|------------------------------|--------------------|-----------------|

| ACKSTAT <sup>(</sup> | <sup>1)</sup> TRSTAT                     | —                                    | —                       | —                            | BCL                          | GCSTAT             | ADD10           |

| bit 15               |                                          |                                      |                         |                              |                              |                    | bit 8           |

|                      |                                          |                                      |                         |                              |                              |                    |                 |

| R/C-0, HS            | 8 R/C-0, HS                              | R-0, HSC                             | R/C-0, HSC              | R/C-0, HSC                   | R-0, HSC                     | R-0, HSC           | R-0, HSC        |

| IWCOL                | I2COV                                    | D/A                                  | Р                       | S                            | R/W                          | RBF                | TBF             |

| bit 7                |                                          |                                      | 1                       |                              |                              | •                  | bit 0           |

|                      |                                          |                                      |                         |                              |                              |                    |                 |

| Legend:              |                                          | C = Clearabl                         | e bit                   | HS = Hardware                | e Settable bit               |                    |                 |

| R = Readal           | ole bit                                  | W = Writable                         | bit                     | U = Unimpleme                | ented bit, read a            | s '0'              |                 |

| -n = Value a         | at POR                                   | '1' = Bit is se                      | t                       | '0' = Bit is clear           | red                          | x = Bit is unkr    | nown            |

| HSC = Har            | dware Settable/C                         | learable bit                         |                         |                              |                              |                    |                 |

|                      |                                          |                                      |                         |                              |                              |                    |                 |

| bit 15               | ACKSTAT: Ad                              | cknowledge St                        | atus bit <sup>(1)</sup> |                              |                              |                    |                 |

|                      |                                          | s detected las                       |                         |                              |                              |                    |                 |

|                      | 0 = ACK was                              |                                      |                         |                              |                              |                    |                 |

|                      | Hardware is s                            |                                      |                         | -                            |                              |                    |                 |

| bit 14               |                                          |                                      |                         | ting as l <sup>2</sup> C™ ma | ister, applicable            | to master trans    | smit operation) |

|                      |                                          | ansmit is in pro                     | <b>U</b>                | + ACK)                       |                              |                    |                 |

|                      |                                          | ansmit is not ir<br>et at the beginn |                         | ansmission. Har              | dware is clear at            | the end of slave   | Acknowledge     |

| bit 13-11            | Unimplemen                               | -                                    | -                       |                              |                              |                    | ger             |

| bit 10               | BCL: Master                              |                                      |                         |                              |                              |                    |                 |

|                      |                                          |                                      |                         | ing a master op              | eration                      |                    |                 |

|                      | 0 = No collisio                          | on                                   |                         |                              |                              |                    |                 |

|                      | Hardware is s                            | et at the dete                       | ction of bus co         | ollision.                    |                              |                    |                 |

| bit 9                | GCSTAT: Ger                              |                                      |                         |                              |                              |                    |                 |

|                      |                                          | all address wa                       |                         | 4                            |                              |                    |                 |

|                      |                                          | all address wa<br>et when an ad      |                         | u<br>s the general call      | address. Hardw               | vare is clear at s | Stop detection. |

| bit 8                | ADD10: 10-B                              |                                      |                         | stre general eau             |                              |                    |                 |

|                      |                                          | lress was mat                        |                         |                              |                              |                    |                 |

|                      |                                          | lress was not                        |                         |                              |                              |                    |                 |

|                      | Hardware is se                           | et at the match                      | of the 2nd byte         | e of matched 10-b            | oit address. Hard            | ware is clear at   | Stop detection. |

| bit 7                | IWCOL: I2Cx                              |                                      |                         |                              | 2                            |                    |                 |

|                      |                                          |                                      | e I2CxTRN re            | egister failed beo           | cause the I <sup>2</sup> C m | odule is busy      |                 |

|                      | 0 = No collisio<br>Hardware is s         |                                      | rrence of a wr          | ite to I2CxTRN               | while busy (clea             | red by software    | e)              |

| bit 6                | 12COV: 12Cx 1                            |                                      |                         |                              |                              | . ca sy convar     |                 |

| 211.0                |                                          |                                      | -                       | CV register is sti           | Il holdina the pro           | evious bvte        |                 |

|                      | 0 = No overflo                           |                                      |                         | - <u></u>                    | 3 P.                         |                    |                 |

|                      | Hardware is s                            | et at an attem                       | pt to transfer          | 2CxRSR to 12C                | xRCV (cleared                | by software).      |                 |

| Note 1:              | n both Master an                         | d Slave mode                         | s, the ACKST            | AT bit is only up            | dated when tran              | ismitting data r   | esultina in the |

| r                    | reception of an A<br>data, either as a s | CK or NACK f                         | rom another d           | evice. Do not ch             | neck the state of            | ACKSTAT who        | en receiving    |

#### 17.1 UARTx Baud Rate Generator (BRG)

The UARTx module includes a dedicated 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 17-1 shows the formula for computation of the baud rate with BRGH = 0.

### EQUATION 17-1: UARTx BAUD RATE WITH BRGH = $0^{(1)}$

Baud Rate =  $\frac{FCY}{16 \cdot (UxBRG + 1)}$ UxBRG =  $\frac{FCY}{16 \cdot Baud Rate} - 1$

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

Example 17-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 17-2 shows the formula for computation of the baud rate with BRGH = 1.

## EQUATION 17-2: UARTx BAUD RATE WITH BRGH = $1^{(1)}$

Baud Rate =

$$\frac{FCY}{4 \cdot (UxBRG + 1)}$$

$UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$

Note 1: Based on FCY = FOSC/2; Doze mode

and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FCY/4 (for UxBRG = 0) and the minimum baud rate possible is FCY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

#### EXAMPLE 17-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

```

Desired Baud Rate = FCY/(16 (UxBRG + 1))

Solving for UxBRG value:

UxBRG = ((FCY/Desired Baud Rate)/16) - 1

UxBRG = ((4000000/9600)/16) - 1

UxBRG = 25

Calculated Baud Rate = 4000000/(16 (25 + 1))

= 9615

Error = (Calculated Baud Rate - Desired Baud Rate)

Desired Baud Rate = (9615 - 9600)/9600

= 0.16%

```

Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

| R/W-0                | U-0                                 | R/W-0                                                                | R/W-0                         | R/W-0                             | U-0                         | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> |

|----------------------|-------------------------------------|----------------------------------------------------------------------|-------------------------------|-----------------------------------|-----------------------------|----------------------|----------------------|

| UARTEN <sup>(1</sup> | ) _                                 | USIDL                                                                | IREN <sup>(2)</sup>           | RTSMD                             | —                           | UEN1                 | UEN0                 |

| bit 15               | ·                                   |                                                                      |                               | ·                                 |                             | •                    | bit 8                |

|                      | <b>D</b> 444 0                      |                                                                      | <b>D</b> 444 A                | <b>D</b> 444 0                    | <b>D</b> 444 0              | <b>D</b> 444 A       | <b>D</b> 444 0       |

| R/C-0, HC            |                                     | R/W-0, HC                                                            | R/W-0                         | R/W-0                             | R/W-0                       | R/W-0                | R/W-0                |

| WAKE                 | LPBACK                              | ABAUD                                                                | RXINV                         | BRGH                              | PDSEL1                      | PDSEL0               | STSEL                |

| bit 7                |                                     |                                                                      |                               |                                   |                             |                      | bit 0                |

| Legend:              |                                     | C = Clearable                                                        | bit                           | HC = Hardwa                       | are Clearable bi            | t                    |                      |

| R = Readab           | ole bit                             | W = Writable b                                                       |                               |                                   | mented bit, read            |                      |                      |

| -n = Value a         |                                     | '1' = Bit is set                                                     |                               | '0' = Bit is cle                  |                             | x = Bit is unkn      | own                  |

|                      |                                     |                                                                      |                               |                                   |                             |                      | lowin                |

| bit 15               | UARTEN: UA                          | ARTx Enable bit <sup>(</sup>                                         | 1)                            |                                   |                             |                      |                      |

|                      |                                     | s enabled; all UA                                                    |                               | e controlled by                   | UARTx as defin              | ed by UEN<1:0        | )>                   |

|                      |                                     | s disabled; all UA                                                   |                               |                                   |                             |                      |                      |

| bit 14               |                                     | nted: Read as '0                                                     | ,                             |                                   |                             |                      |                      |

| bit 13               | USIDL: UAR                          | Tx Stop in Idle M                                                    | lode bit                      |                                   |                             |                      |                      |

|                      |                                     | nues module ope                                                      |                               |                                   | dle mode                    |                      |                      |

|                      |                                     | es module opera                                                      |                               |                                   |                             |                      |                      |

| bit 12               |                                     | Encoder and De                                                       |                               |                                   |                             |                      |                      |

|                      |                                     | oder and decode                                                      |                               |                                   |                             |                      |                      |

| bit 11               |                                     | de Selection for I                                                   |                               |                                   |                             |                      |                      |

|                      | $1 = \overline{\text{UxRTS}} p$     | oin in Simplex mo<br>oin in Flow Contr                               | ode                           |                                   |                             |                      |                      |

| bit 10               | •                                   | nted: Read as '0                                                     |                               |                                   |                             |                      |                      |

| bit 9-8              | UEN<1:0>: L                         | JARTx Enable bi                                                      | ts <sup>(3)</sup>             |                                   |                             |                      |                      |

|                      | 10 = UxTX, l<br>01 = UxTX, l        | JxRX and BCLK<br>JxRX, UxCTS ar<br>JxRX and UxRT<br>nd UxRX pins are | nd UxRTS pin<br>S pins are er | ns are enabled<br>habled and used | and used<br>d; UxCTS pin is | controlled by F      | ORT latches          |

| bit 7                | WAKE: Wake                          | e-up on Start Bit                                                    | Detect Durin                  | g Sleep Mode I                    | Enable bit                  |                      |                      |

|                      | hardware                            | vill continue to sa<br>e on following ris<br>e-up is enabled         |                               | RX pin; interrup                  | t is generated or           | n falling edge, b    | it is cleared in     |

| bit 6                |                                     | •                                                                    | Mada Salaat                   | hit                               |                             |                      |                      |

|                      |                                     | ARTx Loopback  <br>Loopback mode                                     |                               | DIL                               |                             |                      |                      |

|                      |                                     | k mode is disabl                                                     |                               |                                   |                             |                      |                      |

| bit 5                | •                                   | o-Baud Enable b                                                      |                               |                                   |                             |                      |                      |

|                      | cleared i                           | baud rate meas<br>n hardware upor                                    | n completion                  |                                   | er – requires re            | ception of a Sy      | nc field (55h);      |

|                      | 0 = Baud rat                        | e measurement                                                        | is disabled o                 | r completed                       |                             |                      |                      |

|                      | f UARTEN = 1, t<br>Section 10.4 "Pe |                                                                      |                               |                                   |                             | vailable RPn p       | in. See              |

|                      | This feature is or                  | -                                                                    |                               |                                   |                             |                      |                      |

| <b>3:</b> E          | Bit availability de                 | pends on pin ava                                                     | ailability.                   |                                   |                             |                      |                      |

#### REGISTER 17-1: UXMODE: UARTX MODE REGISTER

**3:** Bit availability depends on pin availability.

| REGISTER 17-2: | UxSTA: UARTx STATUS AND CONTROL REGISTER |

|----------------|------------------------------------------|

|----------------|------------------------------------------|

| REGISTER 1          | 17-2: UxST                                                                                                                                                                                                                                                                                                                                                               | A: UARTx ST                                                                         | ATUS AND                                                                                 |                                                                                    | EGISTER                                  |                    |                   |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------|--------------------|-------------------|

| R/W-0               | R/W-0                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                               | U-0                                                                                      | R/W-0, HC                                                                          | R/W-0                                    | R-0                | R-1               |

| UTXISEL1            | UTXINV                                                                                                                                                                                                                                                                                                                                                                   | UTXISEL0                                                                            | _                                                                                        | UTXBRK                                                                             | UTXEN <sup>(1)</sup>                     | UTXBF              | TRMT              |

| bit 15              |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     |                                                                                          |                                                                                    |                                          |                    | bit 8             |

|                     |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     | D 4                                                                                      |                                                                                    |                                          | D/C 0              | <b>D</b> 0        |

| R/W-0               | R/W-0                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                               | R-1                                                                                      | R-0                                                                                | R-0                                      | R/C-0              | R-0               |

| URXISEL1<br>bit 7   | URXISEL0                                                                                                                                                                                                                                                                                                                                                                 | ADDEN                                                                               | RIDLE                                                                                    | PERR                                                                               | FERR                                     | OERR               | URXDA<br>bit C    |

|                     |                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     |                                                                                          |                                                                                    |                                          |                    |                   |

| Legend:             |                                                                                                                                                                                                                                                                                                                                                                          | C = Clearable                                                                       | bit                                                                                      | HC = Hardwa                                                                        | re Clearable bit                         | t                  |                   |

| R = Readable        | e bit                                                                                                                                                                                                                                                                                                                                                                    | W = Writable b                                                                      | bit                                                                                      | U = Unimplem                                                                       | nented bit, read                         | as '0'             |                   |

| -n = Value at       | POR                                                                                                                                                                                                                                                                                                                                                                      | '1' = Bit is set                                                                    |                                                                                          | '0' = Bit is clea                                                                  | ared                                     | x = Bit is unkr    | nown              |

| bit 15,13<br>bit 14 | 11 = Reserve<br>10 = Interrupt<br>transmit<br>01 = Interrupt<br>operatio<br>00 = Interrupt<br>one char                                                                                                                                                                                                                                                                   | d; do not use<br>when a charac<br>buffer becomes<br>when the las<br>ns are complete | ter is transfer<br>s empty<br>t character is<br>ed<br>ter is transferm<br>ne transmit bu |                                                                                    | mit Shift Regist                         | Shift Registe      | er; all transmi   |

|                     | If IREN = 0:<br>1 = UxTX Idle<br>0 = UxTX Idle<br>If IREN = 1:<br>1 = UxTX Idle<br>0 = UxTX Idle                                                                                                                                                                                                                                                                         | state is '0'<br>state is '1'<br>state is '1'                                        |                                                                                          |                                                                                    |                                          |                    |                   |

| bit 12              | Unimplement                                                                                                                                                                                                                                                                                                                                                              | ted: Read as 'o                                                                     | 3                                                                                        |                                                                                    |                                          |                    |                   |

| bit 11              | UTXBRK: UA                                                                                                                                                                                                                                                                                                                                                               | RTx Transmit E                                                                      | Break bit                                                                                |                                                                                    |                                          |                    |                   |