#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32ga002-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                                                                                | Pin Number |             |     |                  |                                             |  |  |  |

|----------|--------------------------------------------------------------------------------|------------|-------------|-----|------------------|---------------------------------------------|--|--|--|

| Function | tion 28-Pin<br>SPDIP/<br>SSOP/SOIC 28-Pin<br>QFN 44-Pin<br>QFN/TQFP //O Buffer |            | Description |     |                  |                                             |  |  |  |

| RP0      | 4                                                                              | 1          | 21          | I/O | ST               | Remappable Peripheral.                      |  |  |  |

| RP1      | 5                                                                              | 2          | 22          | I/O | ST               | ]                                           |  |  |  |

| RP2      | 6                                                                              | 3          | 23          | I/O | ST               |                                             |  |  |  |

| RP3      | 7                                                                              | 4          | 24          | I/O | ST               |                                             |  |  |  |

| RP4      | 11                                                                             | 8          | 33          | I/O | ST               |                                             |  |  |  |

| RP5      | 14                                                                             | 11         | 41          | I/O | ST               |                                             |  |  |  |

| RP6      | 15                                                                             | 12         | 42          | I/O | ST               |                                             |  |  |  |

| RP7      | 16                                                                             | 13         | 43          | I/O | ST               |                                             |  |  |  |

| RP8      | 17                                                                             | 14         | 44          | I/O | ST               |                                             |  |  |  |

| RP9      | 18                                                                             | 15         | 1           | I/O | ST               |                                             |  |  |  |

| RP10     | 21                                                                             | 18         | 8           | I/O | ST               |                                             |  |  |  |

| RP11     | 22                                                                             | 19         | 9           | I/O | ST               |                                             |  |  |  |

| RP12     | 23                                                                             | 20         | 10          | I/O | ST               |                                             |  |  |  |

| RP13     | 24                                                                             | 21         | 11          | I/O | ST               |                                             |  |  |  |

| RP14     | 25                                                                             | 22         | 14          | I/O | ST               |                                             |  |  |  |

| RP15     | 26                                                                             | 23         | 15          | I/O | ST               |                                             |  |  |  |

| RP16     | _                                                                              |            | 25          | I/O | ST               |                                             |  |  |  |

| RP17     | _                                                                              |            | 26          | I/O | ST               |                                             |  |  |  |

| RP18     | _                                                                              | _          | 27          | I/O | ST               |                                             |  |  |  |

| RP19     | _                                                                              | _          | 36          | I/O | ST               |                                             |  |  |  |

| RP20     | _                                                                              |            | 37          | I/O | ST               |                                             |  |  |  |

| RP21     | _                                                                              | _          | 38          | I/O | ST               |                                             |  |  |  |

| RP22     | —                                                                              |            | 2           | I/O | ST               |                                             |  |  |  |

| RP23     | —                                                                              |            | 3           | I/O | ST               |                                             |  |  |  |

| RP24     | —                                                                              | _          | 4           | I/O | ST               |                                             |  |  |  |

| RP25     | —                                                                              |            | 5           | I/O | ST               |                                             |  |  |  |

| RTCC     | 25                                                                             | 22         | 14          | 0   |                  | Real-Time Clock Alarm Output.               |  |  |  |

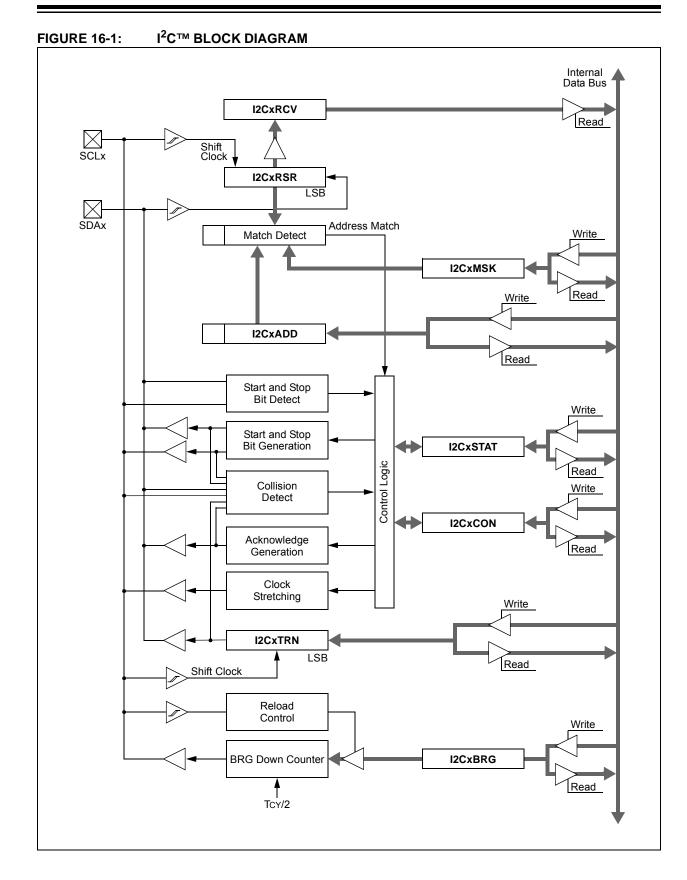

| SCL1     | 17                                                                             | 14         | 44          | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock Input/Output. |  |  |  |

| SCL2     | 7                                                                              | 4          | 24          | I/O | l <sup>2</sup> C | I2C2 Synchronous Serial Clock Input/Output. |  |  |  |

| SDA1     | 18                                                                             | 15         | 1           | I/O | l <sup>2</sup> C | I2C1 Data Input/Output.                     |  |  |  |

| SDA2     | 6                                                                              | 3          | 23          | I/O | l <sup>2</sup> C | I2C2 Data Input/Output.                     |  |  |  |

| SOSCI    | 11                                                                             | 8          | 33          | I   | ANA              | Secondary Oscillator/Timer1 Clock Input.    |  |  |  |

| SOSCO    | 12                                                                             | 9          | 34          | 0   | ANA              | Secondary Oscillator/Timer1 Clock Output.   |  |  |  |

| Legend:  | TTL = TTL inp                                                                  | ut buffer  | •           | •   | ST = 5           | Schmitt Trigger input buffer                |  |  |  |

**Legend:** TTL = TTL input buffer

ST = Schmitt Trigger input buffer  $I^2C^{TM} = I^2C/SMBus$  input buffer

ANA = Analog level input/output  $I^2 C^{TM} = I^2 C/SMBu$ **Note 1:** Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

| IABLE        | 4-Z1: | PERI   | PHERA  |        | SELEC                 | I REGIS               |                       | (223)                 |                       |       |       |       |                       |                       |                       |                       |                       |               |

|--------------|-------|--------|--------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------|

| File<br>Name | Addr  | Bit 15 | Bit 14 | Bit 13 | Bit 12                | Bit 11                | Bit 10                | Bit 9                 | Bit 8                 | Bit 7 | Bit 6 | Bit 5 | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 | All<br>Resets |

| RPINR0       | 0680  | —      | _      |        | INT1R4                | INT1R3                | INT1R2                | INT1R1                | INT1R0                | _     | _     | _     | _                     | —                     | _                     | _                     | _                     | 1F00          |

| RPINR1       | 0682  | _      | _      |        | _                     | _                     | _                     | _                     | _                     | _     | _     |       | INT2R4                | INT2R3                | INT2R2                | INT2R1                | INT2R0                | 001F          |

| RPINR3       | 0686  | _      | _      |        | T3CKR4                | T3CKR3                | T3CKR2                | T3CKR1                | T3CKR0                | _     | _     |       | T2CKR4                | T2CKR3                | T2CKR2                | T2CKR1                | T2CKR0                | 1F1F          |

| RPINR4       | 0688  | —      | —      | _      | T5CKR4                | T5CKR3                | T5CKR2                | T5CKR1                | T5CKR0                | —     | —     | -     | T4CKR4                | T4CKR3                | T4CKR2                | T4CKR1                | T4CKR0                | 1F1F          |

| RPINR7       | 068E  | —      | —      | _      | IC2R4                 | IC2R3                 | IC2R2                 | IC2R1                 | IC2R0                 | —     | —     | -     | IC1R4                 | IC1R3                 | IC1R2                 | IC1R1                 | IC1R0                 | 1F1F          |

| RPINR8       | 0690  | —      | —      | _      | IC4R4                 | IC4R3                 | IC4R2                 | IC4R1                 | IC4R0                 | —     | —     | -     | IC3R4                 | IC3R3                 | IC3R2                 | IC3R1                 | IC3R0                 | 1F1F          |

| RPINR9       | 0692  | _      | _      | _      | _                     | —                     | —                     | —                     | —                     | —     | —     | _     | IC5R4                 | IC5R3                 | IC5R2                 | IC5R1                 | IC5R0                 | 001F          |

| RPINR11      | 0696  | _      | _      | _      | OCFBR4                | OCFBR3                | OCFBR2                | OCFBR1                | OCFBR0                | —     | —     | _     | OCFAR4                | OCFAR3                | OCFAR2                | OCFAR1                | OCFAR0                | 1F1F          |

| RPINR18      | 06A4  | —      | —      | _      | U1CTSR4               | U1CTSR3               | U1CTSR2               | U1CTSR1               | U1CTSR0               | —     | —     | _     | U1RXR4                | U1RXR3                | U1RXR2                | U1RXR1                | U1RXR0                | 1F1F          |

| RPINR19      | 06A6  | —      | —      | _      | U2CTSR4               | U2CTSR3               | U2CTSR2               | U2CTSR1               | U2CTSR0               | —     | —     | _     | U2RXR4                | U2RXR3                | U2RXR2                | U2RXR1                | U2RXR0                | 1F1F          |

| RPINR20      | 06A8  | —      | —      | _      | SCK1R4                | SCK1R3                | SCK1R2                | SCK1R1                | SCK1R0                | —     | —     | _     | SDI1R4                | SDI1R3                | SDI1R2                | SDI1R1                | SDI1R0                | 1F1F          |

| RPINR21      | 06AA  | —      | —      | _      | —                     | —                     | —                     | —                     | —                     | —     | —     | _     | SS1R4                 | SS1R3                 | SS1R2                 | SS1R1                 | SS1R0                 | 001F          |

| RPINR22      | 06AC  | —      | _      | _      | SCK2R4                | SCK2R3                | SCK2R2                | SCK2R1                | SCK2R0                | _     | _     | _     | SDI2R4                | SDI2R3                | SDI2R2                | SDI2R1                | SDI2R0                | 1F1F          |

| RPINR23      | 06AE  | —      | —      | _      | _                     | _                     | _                     | _                     | —                     | _     | —     | _     | SS2R4                 | SS2R3                 | SS2R2                 | SS2R1                 | SS2R0                 | 001F          |

| RPOR0        | 06C0  | —      | —      | _      | RP1R4                 | RP1R3                 | RP1R2                 | RP1R1                 | RP1R0                 | —     | —     | _     | RP0R4                 | RP0R3                 | RP0R2                 | RP0R1                 | RP0R0                 | 0000          |

| RPOR1        | 06C2  | —      | —      | _      | RP3R4                 | RP3R3                 | RP3R2                 | RP3R1                 | RP3R0                 | _     | —     | _     | RP2R4                 | RP2R3                 | RP2R2                 | RP2R1                 | RP2R0                 | 0000          |

| RPOR2        | 06C4  | —      | —      | _      | RP5R4                 | RP5R3                 | RP5R2                 | RP5R1                 | RP5R0                 | —     | —     | _     | RP4R4                 | RP4R3                 | RP4R2                 | RP4R1                 | RP4R0                 | 0000          |

| RPOR3        | 06C6  | —      | —      | _      | RP7R4                 | RP7R3                 | RP7R2                 | RP7R1                 | RP7R0                 | —     | —     | _     | RP6R4                 | RP6R3                 | RP6R2                 | RP6R1                 | RP6R0                 | 0000          |

| RPOR4        | 06C8  | —      | —      | _      | RP9R4                 | RP9R3                 | RP9R2                 | RP9R1                 | RP9R0                 | —     | —     | _     | RP8R4                 | RP8R3                 | RP8R2                 | RP8R1                 | RP8R0                 | 0000          |

| RPOR5        | 06CA  | —      | —      | _      | RP11R4                | RP11R3                | RP11R2                | RP11R1                | RP11R0                | —     | _     | _     | RP10R4                | RP10R3                | RP10R2                | RP10R1                | RP10R0                | 0000          |

| RPOR6        | 06CC  | _      |        | _      | RP13R4                | RP13R3                | RP13R2                | RP13R1                | RP13R0                | _     | —     | _     | RP12R4                | RP12R3                | RP12R2                | RP12R1                | RP12R0                | 0000          |

| RPOR7        | 06CE  | _      |        | _      | RP15R4                | RP15R3                | RP15R2                | RP15R1                | RP15R0                | _     | —     | _     | RP14R4                | RP14R3                | RP14R2                | RP14R1                | RP14R0                | 0000          |

| RPOR8        | 06D0  | _      |        | _      |                       | RP17R3 <sup>(1)</sup> | RP17R2 <sup>(1)</sup> |                       |                       | _     | —     | _     | RP16R4 <sup>(1)</sup> |                       |                       | RP16R1 <sup>(1)</sup> |                       | 0000          |

| RPOR9        | 06D2  | —      | —      | —      | RP19R4 <sup>(1)</sup> |                       | RP19R2 <sup>(1)</sup> | RP19R1 <sup>(1)</sup> |                       | —     | —     | _     | RP18R4 <sup>(1)</sup> | RP18R3 <sup>(1)</sup> | RP18R2 <sup>(1)</sup> |                       |                       | 0000          |

| RPOR10       | 06D4  | _      |        |        | RP21R4 <sup>(1)</sup> |                       | RP21R2 <sup>(1)</sup> |                       |                       | —     | _     | _     | RP20R4 <sup>(1)</sup> |                       |                       | RP20R1 <sup>(1)</sup> |                       | 0000          |

| RPOR11       | 06D6  | _      |        |        |                       | RP23R3 <sup>(1)</sup> | RP23R2 <sup>(1)</sup> |                       |                       | _     | _     | _     | RP22R4 <sup>(1)</sup> | RP22R3 <sup>(1)</sup> |                       |                       |                       | 0000          |

| RPOR12       | 06D8  | —      | —      | _      | RP25R4 <sup>(1)</sup> | RP25R3 <sup>(1)</sup> | RP25R2 <sup>(1)</sup> | RP25R1 <sup>(1)</sup> | RP25R0 <sup>(1)</sup> | —     | —     | _     | RP24R4 <sup>(1)</sup> | RP24R3 <sup>(1)</sup> | RP24R2 <sup>(1)</sup> | RP24R1 <sup>(1)</sup> | RP24R0 <sup>(1)</sup> | 0000          |

### TABLE 4-21: PERIPHERAL PIN SELECT REGISTER MAP (PPS)

Legend:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

These bits are only available on 44-pin devices; otherwise, they read as '0'.

### 5.0 FLASH PROGRAM MEMORY

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | "PIC24F Family Reference Manual",          |

|       | "Program Memory" (DS39715).                |

The PIC24FJ64GA004 family of devices contains internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable when operating with VDD over 2.25V.

Flash memory can be programmed in three ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- Run-Time Self-Programming (RTSP)

- Enhanced In-Circuit Serial Programming (Enhanced ICSP)

ICSP allows a PIC24FJ64GA004 family device to be serially programmed while in the end application circuit. This is simply done with two lines for the programming clock and programming data (which are named PGCx and PGDx, respectively), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed. RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user may write program memory data in blocks of 64 instructions (192 bytes) at a time and erase program memory in blocks of 512 instructions (1536 bytes) at a time.

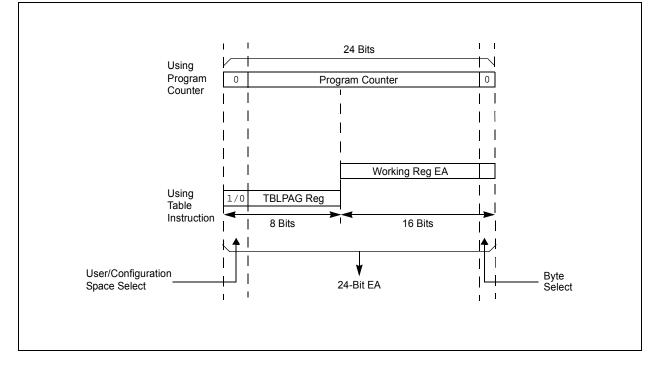

### 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using the TBLPAG<7:0> bits and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

© 2010-2013 Microchip Technology Inc.

### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| -                   | row programming operations      |     |                                       |

|---------------------|---------------------------------|-----|---------------------------------------|

|                     | 0x4001, W0                      | ;   |                                       |

|                     | ), NVMCON                       |     | Initialize NVMCON                     |

| ; Set up a pointer  | to the first program memory lo  | C   | ation to be written                   |

| ; program memory se | elected, and writes enabled     |     |                                       |

|                     | )x0000, W0                      | ;   |                                       |

| MOV WO              | ), TBLPAG                       | ;   | Initialize PM Page Boundary SFR       |

|                     | )x6000, W0                      |     | An example program memory address     |

|                     | ' instructions to write the lat | tcl | hes                                   |

| ; 0th_program_word  |                                 |     |                                       |

| MOV #I              | LOW_WORD_0, W2                  | ;   |                                       |

|                     | HIGH_BYTE_0, W3                 | ;   |                                       |

| TBLWTL W2           | 2, [WO]                         |     | Write PM low word into program latch  |

| TBLWTH W3           | 3, [WO++]                       | ;   | Write PM high byte into program latch |

| ; 1st_program_word  |                                 |     |                                       |

|                     | LOW_WORD_1, W2                  | ;   |                                       |

|                     | HIGH_BYTE_1, W3                 | ;   |                                       |

|                     | 2, [WO]                         |     | Write PM low word into program latch  |

|                     | 3, [WO++]                       | ;   | Write PM high byte into program latch |

| ; 2nd_program_word  |                                 |     |                                       |

|                     | LOW_WORD_2, W2                  | ;   |                                       |

|                     | HIGH_BYTE_2, W3                 | ;   |                                       |

| TBLWTL W2           |                                 |     | Write PM low word into program latch  |

| TBLWTH W3           | 3, [WO++]                       | ;   | Write PM high byte into program latch |

| •                   |                                 |     |                                       |

| •                   |                                 |     |                                       |

| •                   |                                 |     |                                       |

| ; 63rd_program_word |                                 |     |                                       |

|                     | LOW_WORD_31, W2                 | ;   |                                       |

|                     | HIGH_BYTE_31, W3                | ;   |                                       |

| TBLWTL W2           |                                 |     | Write PM low word into program latch  |

| TBLWTH W3           | 3, [WO]                         | ;   | Write PM high byte into program latch |

### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI |             | ; Block all interrupts with priority <7 |

|------|-------------|-----------------------------------------|

|      |             | ; for next 5 instructions               |

| MOV  | #0x55, W0   |                                         |

| MOV  | W0, NVMKEY  | ; Write the 55 key                      |

| MOV  | #0xAA, W1   | ;                                       |

| MOV  | W1, NVMKEY  | ; Write the AA key                      |

| BSET | NVMCON, #WR | ; Start the erase sequence              |

| NOP  |             | ; 2 NOPs required after setting WR      |

| NOP  |             | ;                                       |

| BTSC | NVMCON, #15 | ; Wait for the sequence to be completed |

| BRA  | \$-2        | ;                                       |

|      |             |                                         |

### REGISTER 7-24: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

| U-0                   | R/W-1                                                  | R/W-0                                   | R/W-0            | U-0                 | R/W-1                                                                          | R/W-0           | R/W-0  |  |  |  |  |  |  |  |  |

|-----------------------|--------------------------------------------------------|-----------------------------------------|------------------|---------------------|--------------------------------------------------------------------------------|-----------------|--------|--|--|--|--|--|--|--|--|

| _                     | IC5IP2                                                 | IC5IP1                                  | IC5IP0           |                     | IC4IP2                                                                         | IC4IP1          | IC4IP0 |  |  |  |  |  |  |  |  |

| bit 15                |                                                        |                                         |                  |                     |                                                                                |                 | bit    |  |  |  |  |  |  |  |  |

| U-0                   | R/W-1                                                  | R/W-0                                   | R/W-0            | U-0                 | U-0                                                                            | U-0             | U-0    |  |  |  |  |  |  |  |  |

|                       | IC3IP2                                                 | IC3IP1                                  | IC3IP0           | _                   | _                                                                              | _               | _      |  |  |  |  |  |  |  |  |

| bit 7                 |                                                        |                                         |                  |                     |                                                                                |                 | bit    |  |  |  |  |  |  |  |  |

| Lonondi               |                                                        |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

| Legend:<br>R = Readat | ala hit                                                | W = Writable                            | h:t              |                     | aantad hit raa                                                                 | 1 00'           |        |  |  |  |  |  |  |  |  |

| -n = Value a          |                                                        | '1' = Bit is set                        |                  | '0' = Bit is clea   | nented bit, read                                                               | x = Bit is unkr | 0000   |  |  |  |  |  |  |  |  |

|                       |                                                        |                                         |                  |                     | areu                                                                           |                 | IOWII  |  |  |  |  |  |  |  |  |

| bit 15                | Unimpleme                                              | nted: Read as '                         | o'               |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

| bit 14-12             | -                                                      | Input Capture C                         |                  | rrupt Priority bits | 3                                                                              |                 |        |  |  |  |  |  |  |  |  |

| 511 112               |                                                        | upt is Priority 7 (                     |                  |                     | 5                                                                              |                 |        |  |  |  |  |  |  |  |  |

|                       | •                                                      | артю:е., у . (                          |                  | y                   |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       | •                                                      |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       | •                                                      | untin Drianity (                        |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       |                                                        | upt is Priority 1<br>upt source is dis  | abled            |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

| bit 11                |                                                        | nted: Read as '                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

| bit 10-8              | •                                                      | Input Capture C                         |                  | rrupt Drigrity bit  | -                                                                              |                 |        |  |  |  |  |  |  |  |  |

|                       |                                                        | upt is Priority 7 (                     |                  |                     | 5                                                                              |                 |        |  |  |  |  |  |  |  |  |

|                       | •                                                      |                                         | nightest phone   | y menupt)           |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       | •                                                      |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       | •                                                      |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       |                                                        | upt is Priority 1                       | ablad            |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

| 🗕                     |                                                        | upt source is dis<br>nted: Read as '(   |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       | -                                                      |                                         |                  | rrupt Drigrity bits | _                                                                              |                 |        |  |  |  |  |  |  |  |  |

| bit 7                 |                                                        |                                         |                  |                     |                                                                                |                 |        |  |  |  |  |  |  |  |  |

| bit 7<br>bit 6-4      |                                                        | • •                                     | hish a stariarit | (intermunt)         | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul> |                 |        |  |  |  |  |  |  |  |  |

|                       |                                                        | • •                                     | highest priorit  | y interrupt)        |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       |                                                        | • •                                     | highest priorit  | y interrupt)        |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       | 111 = Interr<br>•<br>•                                 | upt is Priority 7 (                     | highest priorit  | y interrupt)        |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       | 111 = Interr<br>•<br>•<br>001 = Interr                 | upt is Priority 7(<br>upt is Priority 1 |                  | y interrupt)        |                                                                                |                 |        |  |  |  |  |  |  |  |  |

|                       | 111 = Interr<br>•<br>•<br>001 = Interr<br>000 = Interr | upt is Priority 7 (                     | abled            | y interrupt)        |                                                                                |                 |        |  |  |  |  |  |  |  |  |

### REGISTER 10-23: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _      | —   | —   | RP17R4 <sup>(1)</sup> | RP17R3 <sup>(1)</sup> | RP17R2 <sup>(1)</sup> | RP17R1 <sup>(1)</sup> | RP17R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _     | —   | —   | RP16R4 <sup>(1)</sup> | RP16R3 <sup>(1)</sup> | RP16R2 <sup>(1)</sup> | RP16R1 <sup>(1)</sup> | RP16R0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|           |                            |

| bit 12-8 | <b>RP17R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP17 Output Pin bits <sup>(1)</sup> (see Table 10-3 for peripheral function numbers) |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-5  | Unimplemented: Read as '0'                                                                                                                              |

| bit 4-0  | <b>RP16R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP16 Output Pin bits <sup>(1)</sup>                                                  |

(see Table 10-3 for peripheral function numbers)

### REGISTER 10-24: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | —   | RP19R4 <sup>(1)</sup> | RP19R3 <sup>(1)</sup> | RP19R2 <sup>(1)</sup> | RP19R1 <sup>(1)</sup> | RP19R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| U-0   | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —     | —   | —   | RP18R4 <sup>(1)</sup> | RP18R3 <sup>(1)</sup> | RP18R2 <sup>(1)</sup> | RP18R1 <sup>(1)</sup> | RP18R0 <sup>(1)</sup> |

| bit 7 |     |     |                       |                       |                       |                       | bit 0                 |

| Legend:           |                                                                      |                      |                    |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-13 Unimplemented: Read as '0'

- bit 12-8 **RP19R<4:0>:** Peripheral Output Function is Assigned to RP19 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP18R<4:0>:** Peripheral Output Function is Assigned to RP18 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

- Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

### REGISTER 10-25: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| —      | —   | —   | RP21R4 <sup>(1)</sup> | RP21R3 <sup>(1)</sup> | RP21R2 <sup>(1)</sup> | RP21R1 <sup>(1)</sup> | RP21R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| U-0         | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|-------------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|             | —   | —   | RP20R4 <sup>(1)</sup> | RP20R3 <sup>(1)</sup> | RP20R2 <sup>(1)</sup> | RP20R1 <sup>(1)</sup> | RP20R0 <sup>(1)</sup> |

| bit 7 bit 0 |     |     |                       |                       |                       |                       |                       |

| Legend:           |                  |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 12-8  | <b>RP21R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP21 Output Pin bits <sup>(1)</sup> |

|           | (see Table 10-3 for peripheral function numbers)                                                       |

| bit 7-5 | Unimplemented: Read as '0' |  |

|---------|----------------------------|--|

| bit 7-5 | Unimplemented: Read as '0' |  |

bit 4-0 **RP20R<4:0>:** Peripheral Output Function is Assigned to RP20 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|        | _   | _   | RP23R4 <sup>(1)</sup> | RP23R3 <sup>(1)</sup> | RP23R2 <sup>(1)</sup> | RP23R1 <sup>(1)</sup> | RP23R0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

|        |     |     |                       |                       |                       |                       |                       |

| U-0    | U-0 | U-0 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|        | —   | —   | RP22R4 <sup>(1)</sup> | RP22R3 <sup>(1)</sup> | RP22R2 <sup>(1)</sup> | RP22R1 <sup>(1)</sup> | RP22R0 <sup>(1)</sup> |

| bit 7  |     |     |                       |                       |                       |                       | bit 0                 |

### REGISTER 10-26: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| Legend:           |                                                                  |                      |                    |  |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP23R<4:0>:** Peripheral Output Function is Assigned to RP23 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP22R<4:0>:** Peripheral Output Function is Assigned to RP22 Output Pin bits<sup>(1)</sup> (see Table 10-3 for peripheral function numbers)

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

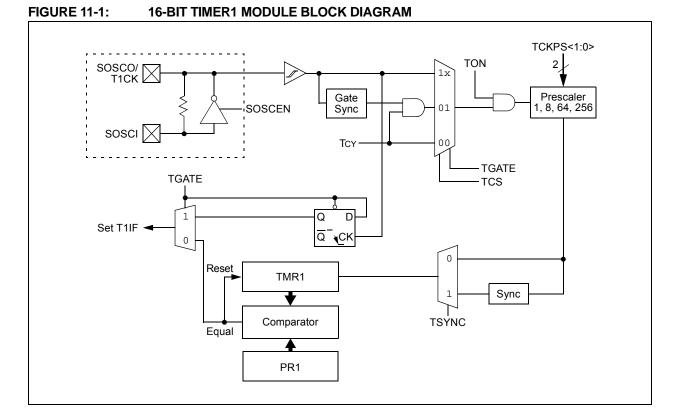

### 11.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, **"Timers"** (DS39704).

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-Time Clock (RTC), or operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Timer1 also supports these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation During CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 11-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the Timer1 Interrupt Enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

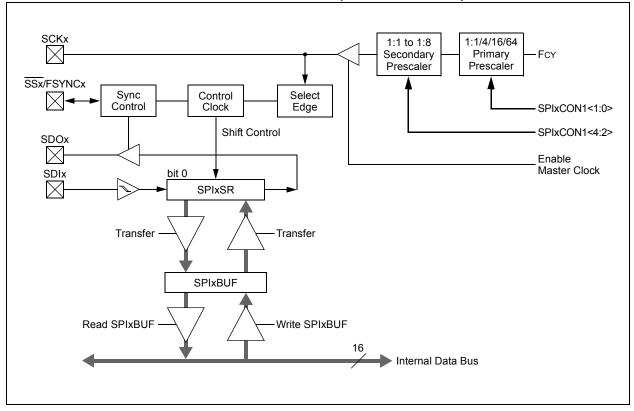

### FIGURE 15-1: SPIX MODULE BLOCK DIAGRAM (STANDARD MODE)

### EQUATION 15-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED<sup>(1)</sup>

FCY

FSCK = Primary Prescaler \* Secondary Prescaler

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### TABLE 15-1: SAMPLE SCKx FREQUENCIES<sup>(1,2)</sup>

| Fcy = 16 MHz               |      | Secondary Prescaler Settings |      |      |      |      |  |

|----------------------------|------|------------------------------|------|------|------|------|--|

|                            |      | 1:1                          | 2:1  | 4:1  | 6:1  | 8:1  |  |

| Primary Prescaler Settings | 1:1  | Invalid                      | 8000 | 4000 | 2667 | 2000 |  |

|                            | 4:1  | 4000                         | 2000 | 1000 | 667  | 500  |  |

|                            | 16:1 | 1000                         | 500  | 250  | 167  | 125  |  |

|                            | 64:1 | 250                          | 125  | 63   | 42   | 31   |  |

| FCY = 5 MHz                |      |                              |      |      |      |      |  |

| Primary Prescaler Settings | 1:1  | 5000                         | 2500 | 1250 | 833  | 625  |  |

|                            | 4:1  | 1250                         | 625  | 313  | 208  | 156  |  |

|                            | 16:1 | 313                          | 156  | 78   | 52   | 39   |  |

|                            | 64:1 | 78                           | 39   | 20   | 13   | 10   |  |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

2: SCKx frequencies are shown in kHz.

### REGISTER 17-3: UXTXREG: UARTX TRANSMIT REGISTER

| U-x          | U-x | U-x | U-x | U-x | U-x | U-x | W-x  |

|--------------|-----|-----|-----|-----|-----|-----|------|

| —            | —   | —   | —   | —   | —   | —   | UTX8 |

| bit 15 bit 8 |     |     |     |     |     |     |      |

| W-x         | W-x  | W-x  | W-x  | W-x  | W-x  | W-x  | W-x  |

|-------------|------|------|------|------|------|------|------|

| UTX7        | UTX6 | UTX5 | UTX4 | UTX3 | UTX2 | UTX1 | UTX0 |

| bit 7 bit 0 |      |      |      |      |      |      |      |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-9 Unimplemented: Read as '0'

bit 8 **UTX8:** UARTx Data of the Transmitted Character bit (in 9-bit mode)

bit 7-0 UTX<7:0>: UARTx Data of the Transmitted Character bits

### REGISTER 17-4: UXRXREG: UARTX RECEIVE REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

|        | —   | —   | —   | —   | —   | —   | URX8  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R-0         | R-0  | R-0  | R-0  | R-0  | R-0  | R-0  | R-0   |

|-------------|------|------|------|------|------|------|-------|

| URX7        | URX6 | URX5 | URX4 | URX3 | URX2 | URX1 | URX0  |

| bit 7 bit 0 |      |      |      |      |      |      | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-9 Unimplemented: Read as '0'

bit 8 URX8: UARTx Data of the Received Character bit (in 9-bit mode)

bit 7-0 URX<7:0>: UARTx Data of the Received Character bits

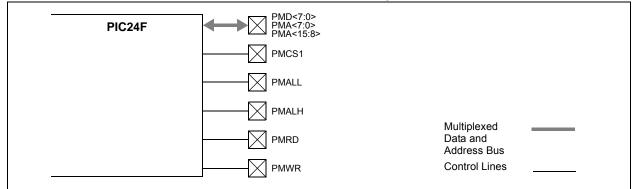

### FIGURE 18-5: MASTER MODE, PARTIALLY MULTIPLEXED ADDRESSING (SEPARATE READ AND WRITE STROBES, SINGLE CHIP SELECT)

| PIC24F | PMA<10:8>            |                         |

|--------|----------------------|-------------------------|

|        | PMD<7:0><br>PMA<7:0> |                         |

|        | PMCS1                |                         |

|        |                      | Address Bus             |

|        |                      | Multiplexed             |

|        |                      | Data and<br>Address Bus |

|        |                      | Control Lines           |

|        |                      |                         |

### FIGURE 18-6: MASTER MODE, FULLY MULTIPLEXED ADDRESSING (SEPARATE READ AND WRITE STROBES, SINGLE CHIP SELECT)

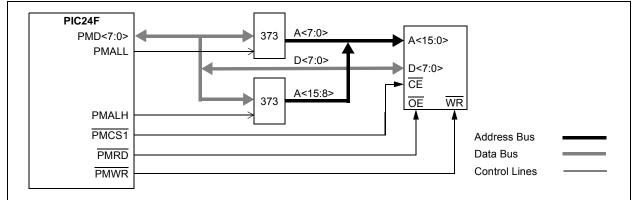

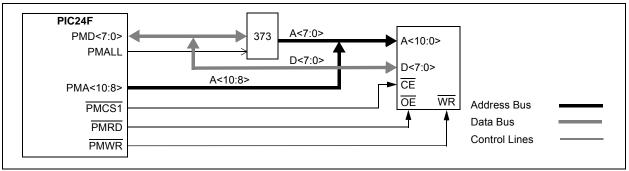

### FIGURE 18-8: EXAMPLE OF A PARTIALLY MULTIPLEXED ADDRESSING APPLICATION

© 2010-2013 Microchip Technology Inc.

### 21.0 10-BIT HIGH-SPEED A/D CONVERTER

| Note:                             | This data sheet summarizes the features of |  |  |  |  |  |

|-----------------------------------|--------------------------------------------|--|--|--|--|--|

|                                   | this group of PIC24F devices. It is not    |  |  |  |  |  |

|                                   | intended to be a comprehensive reference   |  |  |  |  |  |

|                                   | source. For more information, refer to the |  |  |  |  |  |

|                                   | "PIC24F Family Reference Manual",          |  |  |  |  |  |

| "10-Bit A/D Converter" (DS39705). |                                            |  |  |  |  |  |

The 10-bit A/D Converter has the following key features:

- · Successive Approximation (SAR) conversion

- Conversion speeds of up to 500 ksps

- Up to 13 analog input pins

- External voltage reference input pins

- · Automatic Channel Scan mode

- · Selectable conversion trigger source

- 16-word conversion result buffer

- · Selectable Buffer Fill modes

- · Four result alignment options

- Operation during CPU Sleep and Idle modes

Depending on the particular device pinout, the 10-bit A/D Converter can have up to three analog input pins, designated AN0 through AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins. The actual number of analog input pins and the external voltage reference input configuration will depend on the specific device.

A block diagram of the A/D Converter is shown in Figure 21-1.

To perform an A/D conversion:

- 1. Configure the A/D module:

- a) Select the port pins as analog inputs (AD1PCFG<15:0>).

- b) Select the voltage reference source to match the expected range on the analog inputs (AD1CON2<15:13>).

- c) Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- d) Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- e) Select how conversion results are presented in the buffer (AD1CON1<9:8>).

- f) Select the interrupt rate (AD1CON2<5:2>).

- g) Turn on the A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select the A/D interrupt priority.

### TABLE 26-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                           |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| #text           | Means literal defined by "text"                                                       |  |  |  |  |  |

| (text)          | Means "content of text"                                                               |  |  |  |  |  |

| [text]          | Means "the location addressed by text"                                                |  |  |  |  |  |

| { }             | Optional field or operation                                                           |  |  |  |  |  |

| <n:m></n:m>     | Register bit field                                                                    |  |  |  |  |  |

| .b              | Byte mode selection                                                                   |  |  |  |  |  |

| .d              | Double-Word mode selection                                                            |  |  |  |  |  |

| .S              | Shadow register select                                                                |  |  |  |  |  |

| .W              | Word mode selection (default)                                                         |  |  |  |  |  |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$         |  |  |  |  |  |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                  |  |  |  |  |  |

| Expr            | Absolute address, label or expression (resolved by the linker)                        |  |  |  |  |  |

| f               | File register address ∈ {0000h1FFFh}                                                  |  |  |  |  |  |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                        |  |  |  |  |  |

| lit4            | 4-bit unsigned literal ∈ {015}                                                        |  |  |  |  |  |

| lit5            | 5-bit unsigned literal ∈ {031}                                                        |  |  |  |  |  |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                       |  |  |  |  |  |

| lit10           | 10-bit unsigned literal $\in$ {0255} for Byte mode, {0:1023} for Word mode            |  |  |  |  |  |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                    |  |  |  |  |  |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                    |  |  |  |  |  |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be '0'                                 |  |  |  |  |  |

| None            | Field does not require an entry, may be blank                                         |  |  |  |  |  |

| PC              | Program Counter                                                                       |  |  |  |  |  |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                     |  |  |  |  |  |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                 |  |  |  |  |  |

| Slit6           | 6-bit signed literal $\in$ {-1616}                                                    |  |  |  |  |  |

| Wb              | Base W register $\in$ {W0W15}                                                         |  |  |  |  |  |

| Wd              | Destination W register $\in$ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                 |  |  |  |  |  |

| Wdo             | Destination W register $\in$ { Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |  |  |  |  |  |

| Wm,Wn           | Dividend, Divisor working register pair (direct addressing)                           |  |  |  |  |  |

| Wn              | One of 16 working registers ∈ {W0W15}                                                 |  |  |  |  |  |

| Wnd             | One of 16 destination working registers ∈ {W0W15}                                     |  |  |  |  |  |

| Wns             | One of 16 source working registers ∈ {W0W15}                                          |  |  |  |  |  |

| WREG            | W0 (working register used in file register instructions)                              |  |  |  |  |  |

| Ws              | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                          |  |  |  |  |  |

| Wso             | Source W register ∈ { Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }          |  |  |  |  |  |

| DC CHARACTERISTICS |       |                                                                          |        | Standard Operating Conditions:2.0V to 3.6V (unless other<br>-40°C $\leq$ TA $\leq$ +85°C for Ind<br>-40°C $\leq$ TA $\leq$ +125°C for E |                       |          | $\leq$ +85°C for Industrial                                                                                                                                |

|--------------------|-------|--------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym   | Characteristic                                                           | Min    | Typ <sup>(1)</sup>                                                                                                                      | Мах                   | Units    | Conditions                                                                                                                                                 |

| DI31               | IPU   | Maximum Load Current<br>for Digital High Detection                       |        |                                                                                                                                         | 30<br>100             | μA<br>μA | VDD = 2.0V<br>VDD = 3.3V                                                                                                                                   |

|                    | 1     | with Internal Pull-up<br>Input Leakage Current <sup>(2,3)</sup>          |        |                                                                                                                                         |                       | •        |                                                                                                                                                            |

| DI50               | lı∟   | I/O Ports                                                                | _      | _                                                                                                                                       | <u>+</u> 1            | μA       | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance                                                                                                                 |

| DI51               |       | Analog Input Pins                                                        | —      | —                                                                                                                                       | <u>+</u> 1            | μA       | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                                                                                                           |

| DI55               |       | MCLR                                                                     | —      |                                                                                                                                         | <u>+</u> 1            | μA       | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                                   |

| DI56               |       | OSCI                                                                     | —      | —                                                                                                                                       | <u>+</u> 1            | μA       | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                                                  |

| DI60a              | licl  | Input Low Injection<br>Current                                           | 0      |                                                                                                                                         | _5 <sup>(5,8)</sup>   | mA       | All pins exce <u>pt VDD</u> , VSS,<br>AVDD, AVSS, MCLR, VCAP,<br>RB11, SOSCI, SOSCO,<br>D+, D-, VUSB, and VBUS                                             |

| DI60b              | Іісн  | Input High Injection<br>Current                                          | 0      | _                                                                                                                                       | +5 <sup>(6,7,8)</sup> | mA       | All pins exce <u>pt VDD</u> , VSS,<br>AVDD, AVSS, MCLR, VCAP,<br>RB11, SOSCI, SOSCO,<br>D+, D-, VUSB, and VBUS,<br>and all 5V tolerant pins <sup>(7)</sup> |

| DI60c              | ∑lict | Total Input Injection<br>Current<br>(sum of all I/O and control<br>pins) | -20(9) | _                                                                                                                                       | +20 <b>(9)</b>        | mA       | Absolute instantaneous<br>sum of all $\pm$ input injection<br>currents from all I/O pins<br>(  IICL +   IICH  ) $\leq \sum$ IICT)                          |

### TABLE 27-7: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- **4:** Refer to Table 1-2 for I/O pin buffer types.

- 5: Parameter is characterized but not tested.

- **6:** Non-5V tolerant pins, VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- **7:** Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources greater than 5.5V.

- 8: Injection currents > | 0 | can affect the performance of all analog peripherals (e.g., A/D, comparators, internal band gap reference, etc.)

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

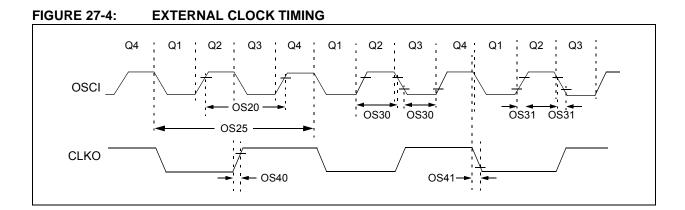

### TABLE 27-15: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |       |                                       | Standard Operating ter | -                  | <b>3.6V (unless otherwise stated)</b><br>$\leq$ TA $\leq$ +85°C for Industrial<br>$\leq$ TA $\leq$ +125°C for Extended |       |                                                |

|--------------------|-------|---------------------------------------|------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------|

| Param<br>No.       | Sym   | Characteristic                        | Min                    | Typ <sup>(1)</sup> | Max                                                                                                                    | Units | Conditions                                     |

| OS10               | Fosc  | External CLKI Frequency               | DC                     | _                  | 32                                                                                                                     | MHz   | EC, $-40^{\circ}C \le TA \le +85^{\circ}C$     |

|                    |       | (External clocks allowed              | 4                      | —                  | 8                                                                                                                      | MHz   | ECPLL, $-40^{\circ}C \le TA \le +85^{\circ}C$  |

|                    |       | only in EC mode)                      | DC                     | —                  | 24                                                                                                                     | MHz   | EC, $-40^{\circ}C \le TA \le +125^{\circ}C$    |

|                    |       |                                       | 4                      | —                  | 6                                                                                                                      | MHz   | ECPLL, -40°C $\leq$ TA $\leq$ +125°C           |

|                    |       | Oscillator Frequency                  | 3                      | _                  | 10                                                                                                                     | MHz   | ХТ                                             |

|                    |       |                                       | 3                      | —                  | 8                                                                                                                      | MHz   | XTPLL, $-40^{\circ}C \le TA \le +85^{\circ}C$  |

|                    |       |                                       | 10                     | —                  | 32                                                                                                                     | MHz   | HS, $-40^{\circ}C \le TA \le +85^{\circ}C$     |

|                    |       |                                       | 31                     | —                  | 33                                                                                                                     | kHz   | SOSC                                           |

|                    |       |                                       | 3                      | —                  | 6                                                                                                                      | MHz   | XTPLL, $-40^{\circ}C \le TA \le +125^{\circ}C$ |

|                    |       |                                       | 10                     | —                  | 24                                                                                                                     | MHz   | HS, $-40^{\circ}C \le TA \le +125^{\circ}C$    |

| OS20               | Tosc  | Tosc = 1/Fosc                         | _                      | _                  | _                                                                                                                      | _     | See Parameter OS10 for                         |

|                    |       |                                       |                        |                    |                                                                                                                        |       | Fosc value                                     |

| OS25               | Тсү   | Instruction Cycle Time <sup>(2)</sup> | 62.5                   | _                  | DC                                                                                                                     | ns    |                                                |

| OS30               | TosL, | External Clock In (OSCI)              | 0.45 x Tosc            | _                  | _                                                                                                                      | ns    | EC                                             |

|                    | TosH  | High or Low Time                      |                        |                    |                                                                                                                        |       |                                                |

| OS31               | TosR, | External Clock In (OSCI)              | _                      |                    | 20                                                                                                                     | ns    | EC                                             |

|                    | TosF  | Rise or Fall Time                     |                        |                    |                                                                                                                        |       |                                                |

| OS40               | TckR  | CLKO Rise Time <sup>(3)</sup>         |                        | 6                  | 10                                                                                                                     | ns    |                                                |

| OS41               | TckF  | CLKO Fall Time <sup>(3)</sup>         | _                      | 6                  | 10                                                                                                                     | ns    |                                                |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: Instruction cycle period (Tcr) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

- **3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 TcY) and high for the Q3-Q4 period (1/2 TcY).

### APPENDIX B: ADDITIONAL GUIDANCE FOR PIC24FJ64GA004 FAMILY APPLICATIONS

### B.1 Additional Methods for Power Reduction

Devices in the PIC24FJ64GA004 family include a number of core features to significantly reduce the application's power requirements. For truly power-sensitive applications, it is possible to further reduce the application's power demands by taking advantage of the device's regulator architecture. These methods help decrease power in two ways: by disabling the internal voltage regulator to eliminate its power consumption, and by reducing the voltage on VDDCORE to lower the device's dynamic current requirements. Using these methods, it is possible to reduce Sleep currents (IPD) from 3.5 µA to 250 nA (typical values, refer to Parameters DC60d and DC60g in Table 27-6). For dynamic power consumption, the reduction in VDDCORE from 2.5V provided by the regulator, to 2.0V, can provide a power reduction of about 30%.

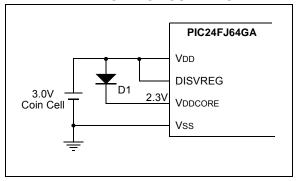

When using a regulated power source or a battery with a constant output voltage, it is possible to decrease power consumption by disabling the regulator. In this case (Figure B-1), a simple diode can be used to reduce the voltage from 3V or greater to the 2V-2.5V required for VDDCORE. This method is only advised on power supplies, such as Lithium Coin cells, which maintain a constant voltage over the life of the battery.

#### FIGURE B-1: POWER REDUCTION EXAMPLE FOR CONSTANT VOLTAGE SUPPLIES

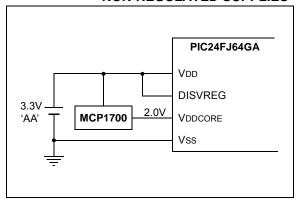

A similar method can be used for non-regulated sources (Figure B-2). In this case, it can be beneficial to use a low quiescent current, external voltage regulator. Devices, such as the MCP1700, consume only 1  $\mu$ A to regulate to 2V or 2.5V, which is lower than the current required to power the internal voltage regulator.

### FIGURE B-2: POWER REDUCTION EXAMPLE FOR NON-REGULATED SUPPLIES

### Ρ

| Packaging                            |         |

|--------------------------------------|---------|

| Details                              | 253     |

| Marking                              | 251     |

| Parallel Master Port. See PMP.       |         |

| Peripheral Enable Bits               | 104     |

| Peripheral Module Disable (PMD) Bits | 104     |

| Peripheral Pin Select (PPS)          | 107     |

| Available Peripherals and Pins       | 107     |

| Configuration Control                | 109     |

| Considerations for Use               | 110     |