Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Detuils                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32ga002t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10                 | Bit 9                 | Bit 8                 | Bit 7                 | Bit 6 | Bit 5 | Bit 4  | Bit 3                 | Bit 2                 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|------------------------|-----------------------|-----------------------|-----------------------|-------|-------|--------|-----------------------|-----------------------|--------|--------|---------------|

| TRISA        | 02C0 |        | _      | _      | —      | _      | TRISA10 <sup>(1)</sup> | TRISA9 <sup>(1)</sup> | TRISA8 <sup>(1)</sup> | TRISA7 <sup>(1)</sup> | _     | _     | TRISA4 | TRISA3 <sup>(2)</sup> | TRISA2 <sup>(3)</sup> | TRISA1 | TRISA0 | 079F          |

| PORTA        | 02C2 | _      | _      | _      | —      |        | RA10 <sup>(1)</sup>    | RA9 <sup>(1)</sup>    | RA8 <sup>(1)</sup>    | RA7 <sup>(1)</sup>    | _     |       | RA4    | RA3 <sup>(2)</sup>    | RA2 <sup>(3)</sup>    | RA1    | RA0    | 0000          |

| LATA         | 02C4 | _      | _      | _      | —      |        | LATA10 <sup>(1)</sup>  | LATA9 <sup>(1)</sup>  | LATA8 <sup>(1)</sup>  | LATA7 <sup>(1)</sup>  | _     |       | LATA4  | LATA3 <sup>(2)</sup>  | LATA2 <sup>(3)</sup>  | LATA1  | LATA0  | 0000          |

| ODCA         | 02C6 | _      | _      | _      | _      | _      | ODA10 <sup>(1)</sup>   | ODA9 <sup>(1)</sup>   | ODA8 <sup>(1)</sup>   | ODA7 <sup>(1)</sup>   | _     | _     | ODA4   | ODA3 <sup>(2)</sup>   | ODA2 <sup>(3)</sup>   | ODA1   | ODA0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are not available on 28-pin devices; read as '0'.

2: These bits are only available when the primary oscillator is disabled (POSCMD<1:0> = 00); otherwise, read as '0'.

3: These bits are only available when the primary oscillator is disabled or EC mode is selected (POSCMD<1:0> = 00 or 11) and CLKO is disabled (OSCIOFNC = 0); otherwise, read as '0'.

#### TABLE 4-13: PORTB REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 02CA | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 0000          |

| LATB         | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000          |

| ODCB         | 02CE | ODB15   | ODB14   | ODB13   | ODB12   | ODB11   | ODB10   | ODB9   | ODB8   | ODB7   | ODB6   | ODB5   | ODB4   | ODB3   | ODB2   | ODB1   | ODB0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-14: PORTC REGISTER MAP

| File<br>Name         | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|----------------------|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC <sup>(1)</sup> | 02D0 | _      | —      | _      |        | _      | -      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC <sup>(1)</sup> | 02D2 | _      | _      | _      | _      | _      | _      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | 0000          |

| LATC <sup>(1)</sup>  | 02D4 | _      | _      | _      | _      | _      | _      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | 0000          |

| ODCC <sup>(1)</sup>  | 02D6 | —      | _      | _      | —      | _      |        | ODC9   | OSC8   | ODC7   | ODC6   | ODC5   | ODC4   | ODC3   | ODC2   | ODC1   | ODC0   | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.Bits are not available on 28-pin devices; read as '0'.

#### TABLE 4-15: PAD CONFIGURATION REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------|--------|---------------|

| PADCFG1      | 02FC |        |        |        |        |        |        |       |       | _     | _     |       |       |       |       | RTSECSEL | PMPTTL | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE        | 4-Z1: | PERI   | PHERA  |        | SELEC                 | I REGIS               |                       | (223)                 |                       |       |       |       |                       |                       |                       |                       |                       |               |

|--------------|-------|--------|--------|--------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------|-------|-------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------|

| File<br>Name | Addr  | Bit 15 | Bit 14 | Bit 13 | Bit 12                | Bit 11                | Bit 10                | Bit 9                 | Bit 8                 | Bit 7 | Bit 6 | Bit 5 | Bit 4                 | Bit 3                 | Bit 2                 | Bit 1                 | Bit 0                 | All<br>Resets |

| RPINR0       | 0680  | —      | _      |        | INT1R4                | INT1R3                | INT1R2                | INT1R1                | INT1R0                | _     | _     | _     | _                     | —                     | _                     | _                     | _                     | 1F00          |

| RPINR1       | 0682  | _      | _      |        | _                     | _                     | _                     | _                     | _                     | _     | _     |       | INT2R4                | INT2R3                | INT2R2                | INT2R1                | INT2R0                | 001F          |

| RPINR3       | 0686  | _      | _      |        | T3CKR4                | T3CKR3                | T3CKR2                | T3CKR1                | T3CKR0                | _     | _     |       | T2CKR4                | T2CKR3                | T2CKR2                | T2CKR1                | T2CKR0                | 1F1F          |

| RPINR4       | 0688  | —      | —      | _      | T5CKR4                | T5CKR3                | T5CKR2                | T5CKR1                | T5CKR0                | —     | —     | -     | T4CKR4                | T4CKR3                | T4CKR2                | T4CKR1                | T4CKR0                | 1F1F          |

| RPINR7       | 068E  | —      | —      | _      | IC2R4                 | IC2R3                 | IC2R2                 | IC2R1                 | IC2R0                 | —     | —     | -     | IC1R4                 | IC1R3                 | IC1R2                 | IC1R1                 | IC1R0                 | 1F1F          |

| RPINR8       | 0690  | —      | —      | _      | IC4R4                 | IC4R3                 | IC4R2                 | IC4R1                 | IC4R0                 | —     | —     | -     | IC3R4                 | IC3R3                 | IC3R2                 | IC3R1                 | IC3R0                 | 1F1F          |

| RPINR9       | 0692  | _      | _      | _      | _                     | —                     | —                     | —                     | —                     | —     | —     | _     | IC5R4                 | IC5R3                 | IC5R2                 | IC5R1                 | IC5R0                 | 001F          |

| RPINR11      | 0696  | _      | _      | _      | OCFBR4                | OCFBR3                | OCFBR2                | OCFBR1                | OCFBR0                | —     | —     | _     | OCFAR4                | OCFAR3                | OCFAR2                | OCFAR1                | OCFAR0                | 1F1F          |

| RPINR18      | 06A4  | —      | —      | _      | U1CTSR4               | U1CTSR3               | U1CTSR2               | U1CTSR1               | U1CTSR0               | —     | —     | _     | U1RXR4                | U1RXR3                | U1RXR2                | U1RXR1                | U1RXR0                | 1F1F          |

| RPINR19      | 06A6  | —      | —      | _      | U2CTSR4               | U2CTSR3               | U2CTSR2               | U2CTSR1               | U2CTSR0               | —     | —     | _     | U2RXR4                | U2RXR3                | U2RXR2                | U2RXR1                | U2RXR0                | 1F1F          |

| RPINR20      | 06A8  | —      | —      | _      | SCK1R4                | SCK1R3                | SCK1R2                | SCK1R1                | SCK1R0                | —     | —     | _     | SDI1R4                | SDI1R3                | SDI1R2                | SDI1R1                | SDI1R0                | 1F1F          |

| RPINR21      | 06AA  | —      | —      | _      | —                     | —                     | —                     | —                     | —                     | —     | —     | _     | SS1R4                 | SS1R3                 | SS1R2                 | SS1R1                 | SS1R0                 | 001F          |

| RPINR22      | 06AC  | —      | _      | _      | SCK2R4                | SCK2R3                | SCK2R2                | SCK2R1                | SCK2R0                | _     | _     | _     | SDI2R4                | SDI2R3                | SDI2R2                | SDI2R1                | SDI2R0                | 1F1F          |

| RPINR23      | 06AE  | —      | —      | _      | _                     | _                     | _                     | _                     | —                     | _     | —     | _     | SS2R4                 | SS2R3                 | SS2R2                 | SS2R1                 | SS2R0                 | 001F          |

| RPOR0        | 06C0  | —      | —      | _      | RP1R4                 | RP1R3                 | RP1R2                 | RP1R1                 | RP1R0                 | —     | —     | _     | RP0R4                 | RP0R3                 | RP0R2                 | RP0R1                 | RP0R0                 | 0000          |

| RPOR1        | 06C2  | —      | —      | _      | RP3R4                 | RP3R3                 | RP3R2                 | RP3R1                 | RP3R0                 | _     | —     | _     | RP2R4                 | RP2R3                 | RP2R2                 | RP2R1                 | RP2R0                 | 0000          |

| RPOR2        | 06C4  | —      | —      | _      | RP5R4                 | RP5R3                 | RP5R2                 | RP5R1                 | RP5R0                 | —     | —     | _     | RP4R4                 | RP4R3                 | RP4R2                 | RP4R1                 | RP4R0                 | 0000          |

| RPOR3        | 06C6  | —      | —      | _      | RP7R4                 | RP7R3                 | RP7R2                 | RP7R1                 | RP7R0                 | —     | —     | _     | RP6R4                 | RP6R3                 | RP6R2                 | RP6R1                 | RP6R0                 | 0000          |

| RPOR4        | 06C8  | —      | —      | _      | RP9R4                 | RP9R3                 | RP9R2                 | RP9R1                 | RP9R0                 | —     | —     | _     | RP8R4                 | RP8R3                 | RP8R2                 | RP8R1                 | RP8R0                 | 0000          |

| RPOR5        | 06CA  | —      | —      | _      | RP11R4                | RP11R3                | RP11R2                | RP11R1                | RP11R0                | —     | _     | _     | RP10R4                | RP10R3                | RP10R2                | RP10R1                | RP10R0                | 0000          |

| RPOR6        | 06CC  | _      |        | _      | RP13R4                | RP13R3                | RP13R2                | RP13R1                | RP13R0                | _     | —     | _     | RP12R4                | RP12R3                | RP12R2                | RP12R1                | RP12R0                | 0000          |

| RPOR7        | 06CE  | _      |        | _      | RP15R4                | RP15R3                | RP15R2                | RP15R1                | RP15R0                | _     | —     | _     | RP14R4                | RP14R3                | RP14R2                | RP14R1                | RP14R0                | 0000          |

| RPOR8        | 06D0  | _      |        | _      |                       | RP17R3 <sup>(1)</sup> | RP17R2 <sup>(1)</sup> |                       |                       | _     | —     | _     | RP16R4 <sup>(1)</sup> |                       |                       | RP16R1 <sup>(1)</sup> |                       | 0000          |

| RPOR9        | 06D2  | —      | —      | —      | RP19R4 <sup>(1)</sup> |                       | RP19R2 <sup>(1)</sup> | RP19R1 <sup>(1)</sup> |                       | —     | —     | _     | RP18R4 <sup>(1)</sup> | RP18R3 <sup>(1)</sup> | RP18R2 <sup>(1)</sup> |                       |                       | 0000          |

| RPOR10       | 06D4  | —      |        |        | RP21R4 <sup>(1)</sup> |                       | RP21R2 <sup>(1)</sup> |                       |                       | —     | _     | _     | RP20R4 <sup>(1)</sup> |                       |                       | RP20R1 <sup>(1)</sup> |                       | 0000          |

| RPOR11       | 06D6  | —      |        |        |                       | RP23R3 <sup>(1)</sup> | RP23R2 <sup>(1)</sup> |                       |                       | _     | _     | _     | RP22R4 <sup>(1)</sup> | RP22R3 <sup>(1)</sup> |                       |                       |                       | 0000          |

| RPOR12       | 06D8  | —      | —      | _      | RP25R4 <sup>(1)</sup> | RP25R3 <sup>(1)</sup> | RP25R2 <sup>(1)</sup> | RP25R1 <sup>(1)</sup> | RP25R0 <sup>(1)</sup> | —     | —     | _     | RP24R4 <sup>(1)</sup> | RP24R3 <sup>(1)</sup> | RP24R2 <sup>(1)</sup> | RP24R1 <sup>(1)</sup> | RP24R0 <sup>(1)</sup> | 0000          |

#### TABLE 4-21: PERIPHERAL PIN SELECT REGISTER MAP (PPS)

Legend:

— = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1:

These bits are only available on 44-pin devices; otherwise, they read as '0'.

#### 5.5.2 PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

If a Flash location has been erased, it can be programmed using table write instructions to write an instruction word (24-bit) into the write latch. The TBLPAG register is loaded with the 8 Most Significant Bytes of the Flash address. The TBLWTL and TBLWTH instructions write the desired data into the write latches and specify the lower 16 bits of the program memory address to write to. To configure the NVMCON register for a word write, set the NVMOPx bits (NVMCON<3:0>) to '0011'. The write is performed by executing the unlock sequence and setting the WR bit (see Example 5-4).

#### EXAMPLE 5-4: PROGRAMMING A SINGLE WORD OF FLASH PROGRAM MEMORY

| ; Setup a p               | pointer to data Program Memory                             |    |                                                      |

|---------------------------|------------------------------------------------------------|----|------------------------------------------------------|

| MOV                       | <pre>#tblpage(PROG_ADDR), W0</pre>                         | ;  |                                                      |

| MOV                       | W0, TBLPAG                                                 | ;1 | Initialize PM Page Boundary SFR                      |

| MOV                       | <pre>#tbloffset(PROG_ADDR), W0</pre>                       | ;1 | initialize a register with program memory address    |

| MOV                       | #LOW_WORD_N, W2                                            | ;  |                                                      |

| MOV                       | #HIGH_BYTE_N, W3                                           | ;  |                                                      |

| TBLWTL                    | W2, [W0]                                                   | ;  | Write PM low word into program latch                 |

| TBLWTH                    | W3, [W0++]                                                 | ;  | Write PM high byte into program latch                |

| ; Setup NVN<br>MOV<br>MOV | 4CON for programming one word<br>#0x4003, W0<br>W0, NVMCON | ;  | data Program Memory<br>Set NVMOP bits to 0011        |

| DISI                      | #5                                                         | ;  | Disable interrupts while the KEY sequence is written |

| MOV                       | #0x55, W0                                                  | ;  | Write the key sequence                               |

| MOV                       | W0, NVMKEY                                                 |    |                                                      |

| MOV                       | #0xAA, W0                                                  |    |                                                      |

| MOV                       | W0, NVMKEY                                                 |    |                                                      |

| BSET                      | NVMCON, #WR                                                | ;  | Start the write cycle                                |

| NOP                       |                                                            | ;  | 2 NOPs required after setting WR                     |

| NOP                       |                                                            | ;  |                                                      |

|                           |                                                            |    |                                                      |

### 9.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Power-Saving Features"* (DS39698). Additional power-saving tips can also be found in Appendix B: "Additional Guidance for PIC24FJ64GA004 Family Applications" of this document.

The PIC24FJ64GA004 family of devices provides the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. All PIC24F devices manage power consumption in four different ways:

- Clock Frequency

- Instruction-Based Sleep and Idle modes

- Software Controlled Doze mode

- · Selective Peripheral Control in Software

Combinations of these methods can be used to selectively tailor an application's power consumption, while still maintaining critical application features, such as timing-sensitive communications.

#### 9.1 Clock Frequency and Clock Switching

PIC24F devices allow for a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSCx bits. The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 8.0** "Oscillator Configuration".

#### 9.2 Instruction-Based Power-Saving Modes

PIC24F devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution; Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 9-1. Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

#### 9.2.1 SLEEP MODE

Sleep mode includes these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the Input Change Notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation will be disabled in Sleep mode.

Additional power reductions can be achieved by disabling the on-chip voltage regulator whenever Sleep mode is invoked. This is done by clearing the PMSLP bit (RCON<8>). Disabling the regulator adds an additional delay of about 190  $\mu$ s to the device wake-up time. It is recommended that applications not using the voltage regulator leave the PMSLP bit set. For additional details on the regulator and Sleep mode, see **Section 24.2.5 "Voltage Regulator Standby Mode"**.

The device will wake-up from Sleep mode on any of these events:

- On any interrupt source that is individually enabled.

- · On any form of device Reset.

- On a WDT time-out.

On wake-up from Sleep, the processor will restart with the same clock source that was active when Sleep mode was entered.

#### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

| PWRSAV | #SLEEP_MODE | ; Put the device into SLEEP mode |

|--------|-------------|----------------------------------|

| PWRSAV | #IDLE_MODE  | ; Put the device into IDLE mode  |

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|-----|--------|--------|--------|--------|--------|

| —      | —   | —   | SCK1R4 | SCK1R3 | SCK1R2 | SCK1R1 | SCK1R0 |

| bit 15 |     |     |        |        |        |        | bit 8  |

|        |     |     |        |        |        |        |        |

| U-0    | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

| —      | —   | —   | SDI1R4 | SDI1R3 | SDI1R2 | SDI1R1 | SDI1R0 |

| bit 7  |     |     |        |        |        |        | bit 0  |

|        |     |     |        |        |        |        |        |

|        |     |     |        |        |        |        |        |

#### REGISTER 10-11: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                     |

|-----------|--------------------------------------------------------------------------------|

| bit 12-8  | SCK1R<4:0>: Assign SPI1 Clock Input (SCK1IN) to the Corresponding RPn Pin bits |

| bit 7-5   | Unimplemented: Read as '0'                                                     |

| bit 4-0   | SDI1R<4:0>: Assign SPI1 Data Input (SDI1) to the Corresponding RPn Pin bits    |

#### REGISTER 10-12: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0 | U-0              | U-0   | U-0                                                                                                      | U-0                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------------------|-------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _   | —                | —     | —                                                                                                        | —                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                  |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |                  |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| U-0 | U-0              | R/W-1 | R/W-1                                                                                                    | R/W-1                                                                                                                                                                                                         | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| _   | —                | SS1R4 | SS1R3                                                                                                    | SS1R2                                                                                                                                                                                                         | SS1R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SS1R0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |                  |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |                  |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |                  |       |                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit | W = Writable     | bit   | U = Unimplem                                                                                             | nented bit, read                                                                                                                                                                                              | l as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| POR | '1' = Bit is set |       | '0' = Bit is clea                                                                                        | ared                                                                                                                                                                                                          | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                  |       | U-0         U-0         R/W-1           —         —         SS1R4           bit         W = Writable bit | —         —         —         —           U-0         U-0         R/W-1         R/W-1           —         —         —         SS1R4         SS1R3           bit         W = Writable bit         U = Unimplem | —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         Image: Marce of the field of th | —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         — |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 SS1R<4:0>: Assign SPI1 Slave Select Input (SS1IN) to the Corresponding RPn Pin bits

#### REGISTER 10-15: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-------|-------|-------|

| —      | —   | —   | RP1R4 | RP1R3 | RP1R2 | RP1R1 | RP1R0 |

| bit 15 |     |     |       |       |       |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP0R4 | RP0R3 | RP0R2 | RP0R1 | RP0R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                                                                      |                      |                    |  |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-13 Unimplemented: Read as '0'

| bit 12-8 | <b>RP1R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP1 Output Pin bits |

|----------|---------------------------------------------------------------------------------------|

|          | (see Table 10-3 for peripheral function numbers)                                      |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 10-3 for peripheral function numbers)

#### REGISTER 10-16: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-------|-------|-------|

| —      | —   | —   | RP3R4 | RP3R3 | RP3R2 | RP3R1 | RP3R0 |

| bit 15 | -   |     |       |       |       |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP2R4 | RP2R3 | RP2R2 | RP2R1 | RP2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                                                                      |                      |                    |  |  |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 10-3 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-3 for peripheral function numbers)

### REGISTER 15-1: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 1 | SPITBF: SPIx Transmit Buffer Full Status bit<br>1 = Transmit has not yet started, SPIxTXB is full<br>0 = Transmit has started, SPIxTXB is empty                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | In Standard Buffer mode:<br>Automatically set in hardware when CPU writes the SPIxBUF location, loading SPIxTXB. Automatically<br>cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.                                              |

|       | In Enhanced Buffer mode:<br>Automatically set in hardware when CPU writes the SPIxBUF location, loading the last available buffer<br>location. Automatically cleared in hardware when a buffer location is available for a CPU write.                          |

| bit 0 | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                                                                    |

|       | 1 = Receive is complete, SPIxRXB is full<br>0 = Receive is not complete, SPIxRXB is empty                                                                                                                                                                      |

|       | In Standard Buffer mode:<br>Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.                                                        |

|       | In Enhanced Buffer mode:<br>Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread<br>buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from<br>SPIxSR. |

**Note 1:** If SPIEN = 1, these functions must be assigned to available RPn pins before use. See **Section 10.4** "**Peripheral Pin Select (PPS)**" for more information.

### REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends a NACK during Acknowledge<br>0 = Sends an ACK during Acknowledge                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | <ul> <li>ACKEN: Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits the ACKDT data bit.<br/>Hardware is clear at the end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)<br>1 = Enables Receive mode for I <sup>2</sup> C. Hardware is clear at the end of eighth bit of master receive data byte.<br>0 = Receive sequence is not in progress                                                                                                                 |

| bit 2 | <ul> <li>PEN: Stop Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of master Stop sequence.</li> <li>0 = Stop condition is not in progress</li> </ul>                                                                                                   |

| bit 1 | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                                                          |

| bit 0 | <ul> <li>SEN: Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                                                               |

Note 1: In Slave mode, the module will not automatically clock stretch after receiving the address byte.

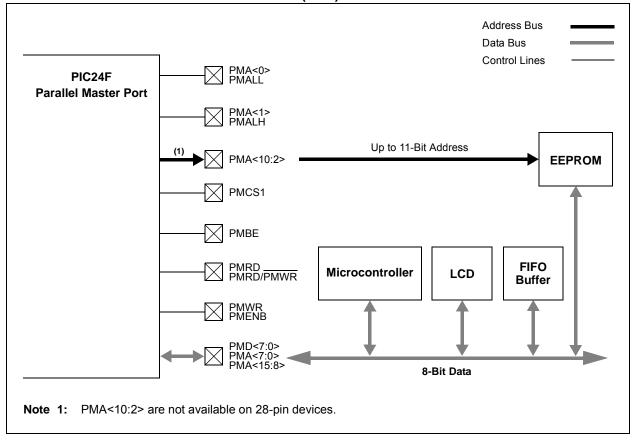

### 18.0 PARALLEL MASTER PORT (PMP)

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | "PIC24F Family Reference Manual",          |

|       | "Parallel Master Port (PMP)" (DS39713).    |

The Parallel Master Port (PMP) module is a parallel 8-bit I/O module, specifically designed to communicate with a wide variety of parallel devices, such as communication peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP is highly configurable.

**Note:** A number of the pins for the PMP are not present on PIC24FJ64GA004 devices. Refer to the specific device's pinout to determine which pins are available.

Key features of the PMP module include:

- Up to 16 Programmable Address Lines

- One Chip Select Line

- Programmable Strobe Options:

- Individual Read and Write Strobes or;

- Read/Write Strobe with Enable Strobe

- Address Auto-Increment/Auto-Decrement

- Programmable Address/Data Multiplexing

- · Programmable Polarity on Control Signals

- Legacy Parallel Slave Port Support

- Enhanced Parallel Slave Support:

- Address Support

- 4-Byte Deep Auto-Incrementing Buffer

- Programmable Wait States

- · Selectable Input Voltage Levels

#### FIGURE 18-1: PARALLEL MASTER PORT (PMP) MODULE OVERVIEW

#### **REGISTER 19-3:** ALCFGRPT: ALARM CONFIGURATION REGISTER R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ALRMEN CHIME AMASK3 AMASK2 AMASK1 AMASK0 ALRMPTR1 ALRMPTR0 bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ARPT6 ARPT5 ARPT4 ARPT3 ARPT2 ARPT1 ARPT0 ARPT7 bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared '1' = Bit is set x = Bit is unknown bit 15 ALRMEN: Alarm Enable bit 1 = Alarm is enabled (cleared automatically after an alarm event whenever ARPT<7:0> = 00h and CHIME = 0) 0 = Alarm is disabled bit 14 CHIME: Chime Enable bit 1 = Chime is enabled; ARPT<7:0> bits are allowed to roll over from 00h to FFh 0 = Chime is disabled; ARPT<7:0> bits stop once they reach 00h bit 13-10 AMASK<3:0>: Alarm Mask Configuration bits 0000 = Every half second 0001 = Every second 0010 = Every 10 seconds 0011 = Every minute 0100 = Every 10 minutes 0101 = Every hour 0110 = Once a day 0111 = Once a week 1000 = Once a month 1001 = Once a year (except when configured for February 29th, once every 4 years) 101x = Reserved; do not use 11xx = Reserved: do not use bit 9-8 ALRMPTR<1:0>: Alarm Value Register Window Pointer bits Points to the corresponding Alarm Value registers when reading ALRMVALH and ALRMVALL registers; the ALRMPTR<1:0> value decrements on every read or write of ALRMVALH until it reaches '00'. ALRMVAL<15:8>: 00 = ALRMMIN 01 = ALRMWD 10 = ALRMMNTH 11 = Unimplemented ALRMVAL<7:0>: 00 = ALRMSEC 01 = ALRMHR 10 = ALRMDAY 11 = Unimplemented bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits 11111111 = Alarm will repeat 255 more times 00000000 = Alarm will not repeat The counter decrements on any alarm event. The counter is prevented from rolling over from 00h to FFh unless CHIME = 1.

#### 19.2 Calibration

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than 3 seconds per month. This is accomplished by finding the number of error clock pulses and storing the value into the lower half of the RCFGCAL register. The 8-bit signed value, loaded into the lower half of RCFGCAL, is multiplied by four and will be either added or subtracted from the RTCC timer, once every minute. Refer to the steps below for RTCC calibration:

- 1. Using another timer resource on the device, the user must find the error of the 32.768 kHz crystal.

- 2. Once the error is known, it must be converted to the number of error clock pulses per minute.

#### EQUATION 19-1:

(Ideal Frequency<sup>†</sup> – Measured Frequency) \* 60 = Clocks per Minute

† Ideal frequency = 32,768 Hz

3. a) If the oscillator is faster then ideal (negative result form Step 2), the RCFGCAL register value needs to be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

b) If the oscillator is slower then ideal (positive result from Step 2), the RCFGCAL register value needs to be positive. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

Divide the number of error clocks per minute by 4 to get the correct CAL<7:0> bits value and load the RCFGCAL register with the correct value.

(Each 1-bit increment in the CALx bits value adds or subtracts 4 pulses).

Writes to the lower half of the RCFGCAL register should only occur when the timer is turned off or immediately after the rising edge of the seconds pulse.

| Note: | It is up to the user to include in the error  |

|-------|-----------------------------------------------|

|       | value the initial error of the crystal, drift |

|       | due to temperature and drift due to crystal   |

|       | aging.                                        |

#### 19.3 Alarm

- Configurable from half second to one year

- Enabled using the ALRMEN bit (ALCFGRPT<15>, Register 19-3)

- One-time alarm and repeat alarm options are available

#### 19.3.1 CONFIGURING THE ALARM

The alarm feature is enabled using the ALRMEN bit. This bit is cleared when an alarm is issued. Writes to ALRMVAL should only take place when ALRMEN = 0.

As shown in Figure 19-2, the interval selection of the alarm is configured through the AMASK<3:0> bits (ALCFGRPT<13:10>). These bits determine which and how many digits of the alarm must match the clock value for the alarm to occur.

The alarm can also be configured to repeat based on a preconfigured interval. The amount of times this occurs, once the alarm is enabled, is stored in the ARPT<7:0> bits (ALCFGRPT<7:0>). When the value of the ARPTx bits equals 00h and the CHIME bit (ALCFGRPT<14>) is cleared, the repeat function is disabled and only a single alarm will occur. The alarm can be repeated up to 255 times by loading ARPT<7:0> with FFh.