Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

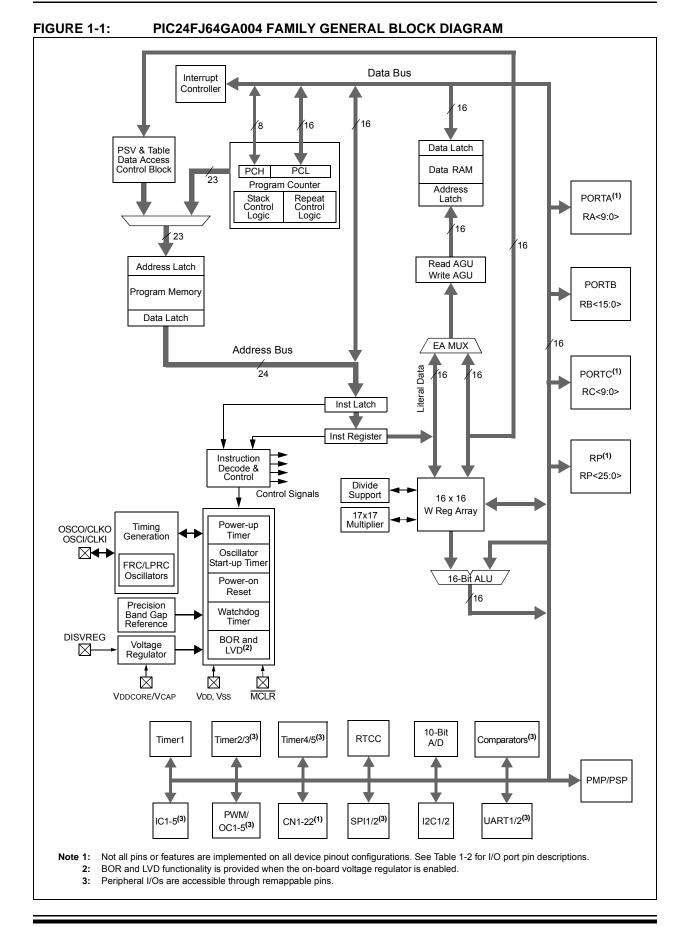

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj32ga004-i-ml |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          | I                             | Pin Number    |                    |     |                             |                                                                                            |

|----------|-------------------------------|---------------|--------------------|-----|-----------------------------|--------------------------------------------------------------------------------------------|

| Function | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/TQFP | I/O | Input<br>Buffer             | Description                                                                                |

| CN0      | 12                            | 9             | 34                 | I   | ST                          | Interrupt-on-Change Inputs.                                                                |

| CN1      | 11                            | 8             | 33                 | Ι   | ST                          |                                                                                            |

| CN2      | 2                             | 27            | 19                 | Ι   | ST                          |                                                                                            |

| CN3      | 3                             | 28            | 20                 | I   | ST                          |                                                                                            |

| CN4      | 4                             | 1             | 21                 | I   | ST                          |                                                                                            |

| CN5      | 5                             | 2             | 22                 | Ι   | ST                          |                                                                                            |

| CN6      | 6                             | 3             | 23                 | I   | ST                          |                                                                                            |

| CN7      | 7                             | 4             | 24                 | I   | ST                          |                                                                                            |

| CN8      | _                             | _             | 25                 | Ι   | ST                          |                                                                                            |

| CN9      | —                             | _             | 26                 | I   | ST                          |                                                                                            |

| CN10     | _                             | _             | 27                 | Ι   | ST                          |                                                                                            |

| CN11     | 26                            | 23            | 15                 | Ι   | ST                          |                                                                                            |

| CN12     | 25                            | 22            | 14                 | Ι   | ST                          |                                                                                            |

| CN13     | 24                            | 21            | 11                 | Ι   | ST                          |                                                                                            |

| CN14     | 23                            | 20            | 10                 | Ι   | ST                          |                                                                                            |

| CN15     | 22                            | 19            | 9                  | Ι   | ST                          |                                                                                            |

| CN16     | 21                            | 18            | 8                  | Ι   | ST                          |                                                                                            |

| CN17     | _                             | _             | 3                  | Ι   | ST                          |                                                                                            |

| CN18     | _                             | _             | 2                  | Ι   | ST                          |                                                                                            |

| CN19     | _                             | _             | 5                  | Ι   | ST                          |                                                                                            |

| CN20     | _                             | _             | 4                  | Ι   | ST                          |                                                                                            |

| CN21     | 18                            | 15            | 1                  | Ι   | ST                          |                                                                                            |

| CN22     | 17                            | 14            | 44                 | Ι   | ST                          |                                                                                            |

| CN23     | 16                            | 13            | 43                 | Ι   | ST                          |                                                                                            |

| CN24     | 15                            | 12            | 42                 | Ι   | ST                          |                                                                                            |

| CN25     | —                             | —             | 37                 | I   | ST                          | ]                                                                                          |

| CN26     | _                             | _             | 38                 | I   | ST                          | 1                                                                                          |

| CN27     | 14                            | 11            | 41                 | I   | ST                          | ]                                                                                          |

| CN28     | _                             | _             | 36                 | I   | ST                          | 1                                                                                          |

| CN29     | 10                            | 7             | 31                 | I   | ST                          | 1                                                                                          |

| CN30     | 9                             | 6             | 30                 | I   | ST                          | 1                                                                                          |

| CVREF    | 25                            | 22            | 14                 | 0   | ANA                         | Comparator Voltage Reference Output.                                                       |

| DISVREG  | 19                            | 16            | 6                  | Ι   | ST                          | Voltage Regulator Disable.                                                                 |

| INT0     | 16                            | 13            | 43                 | I   | ST                          | External Interrupt Input.                                                                  |

| MCLR     | 1                             | 26            | 18                 | I   | ST                          | Master Clear (device Reset) Input. This line is brought lov to cause a Reset.              |

| Legend:  | TTL = TTL inp<br>ANA = Analog |               | utput              |     | ST = S<br>I <sup>2</sup> C™ | to cause a Reset.<br>Schmitt Trigger input buffer<br>= I <sup>2</sup> C/SMBus input buffer |

# TABLE 1-2: PIC24FJ64GA004 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

Note 1: Alternative multiplexing when the I2C1SEL Configuration bit is cleared.

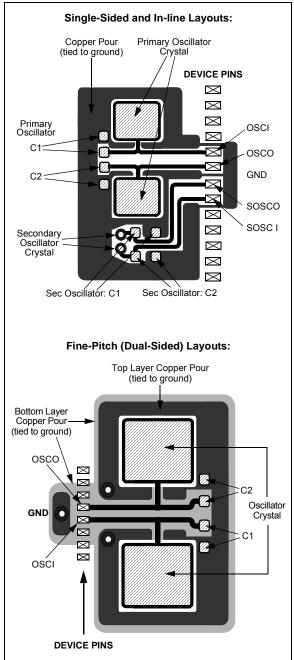

# 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

# FIGURE 2-5:

# PLACEMENT OF THE OSCILLATOR CIRCUIT

SUGGESTED

| U-0            | U-0              | R/W-0                             | R/W-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0                 |

|----------------|------------------|-----------------------------------|-------------------|-------------------|-----------------|-----------------|-----------------------|

| _              | _                | AD1IE                             | U1TXIE            | U1RXIE            | SPI1IE          | SPF1IE          | T3IE                  |

| bit 15         |                  |                                   |                   | •                 |                 |                 | bit                   |

|                |                  |                                   |                   |                   |                 |                 |                       |

| R/W-0          | R/W-0            | R/W-0                             | U-0               | R/W-0             | R/W-0           | R/W-0           | R/W-0                 |

| T2IE           | OC2IE            | IC2IE                             | —                 | T1IE              | OC1IE           | IC1IE           | INT0IE <sup>(1)</sup> |

| bit 7          |                  |                                   |                   |                   |                 |                 | bit                   |

| Legend:        |                  |                                   |                   |                   |                 |                 |                       |

| R = Readable   | e bit            | W = Writable                      | bit               | U = Unimplem      | ented bit, read | l as '0'        |                       |

| -n = Value at  | POR              | '1' = Bit is set                  |                   | '0' = Bit is clea | red             | x = Bit is unkn | iown                  |

|                |                  |                                   |                   |                   |                 |                 |                       |

| bit 15-14      | -                | ted: Read as '                    |                   |                   |                 |                 |                       |

| bit 13         |                  |                                   | nplete Interrup   | t Enable bit      |                 |                 |                       |

|                | •                | equest is enab<br>equest is not e |                   |                   |                 |                 |                       |

| bit 12         | -                | -                                 | r Interrupt Enal  | hle hit           |                 |                 |                       |

|                |                  | equest is enab                    | •                 |                   |                 |                 |                       |

|                |                  | equest is not e                   |                   |                   |                 |                 |                       |

| bit 11         | U1RXIE: UAR      | RT1 Receiver In                   | nterrupt Enable   | e bit             |                 |                 |                       |

|                |                  | equest is enab<br>equest is not e |                   |                   |                 |                 |                       |

| bit 10         | -                | -                                 | olete Interrupt I | Enable bit        |                 |                 |                       |

|                |                  | equest is enab                    | •                 |                   |                 |                 |                       |

|                | •                | equest is not e                   |                   |                   |                 |                 |                       |

| bit 9          |                  | Fault Interrup                    |                   |                   |                 |                 |                       |

|                |                  | equest is enab<br>equest is not e |                   |                   |                 |                 |                       |

| bit 8          | -                | Interrupt Enab                    |                   |                   |                 |                 |                       |

|                |                  | equest is enab                    |                   |                   |                 |                 |                       |

|                | 0 = Interrupt r  | equest is not e                   | nabled            |                   |                 |                 |                       |

| bit 7          |                  | Interrupt Enab                    |                   |                   |                 |                 |                       |

|                | •                | equest is enab                    |                   |                   |                 |                 |                       |

| bit 6          | •                | equest is not e                   | annel 2 Interru   | unt Enable bit    |                 |                 |                       |

|                | -                | equest is enab                    |                   |                   |                 |                 |                       |

|                |                  | equest is not e                   |                   |                   |                 |                 |                       |

| bit 5          | IC2IE: Input C   | Capture Chann                     | el 2 Interrupt E  | nable bit         |                 |                 |                       |

|                |                  | equest is enab                    |                   |                   |                 |                 |                       |

| L:1 1          | -                | equest is not e                   |                   |                   |                 |                 |                       |

| bit 4<br>bit 3 | -                | ted: Read as '                    |                   |                   |                 |                 |                       |

| UIL J          | I IIE. IIIIief I | Interrupt Enab                    |                   |                   |                 |                 |                       |

|                | 1 = Interrupt r  | equest is enab                    | led               |                   |                 |                 |                       |

# REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

**Note 1:** If INTxIE = 1, this external interrupt input must be configured to an available RPn pin. See Section 10.4 "Peripheral Pin Select (PPS)" for more information.

# REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0              | R/W-1                                                            | R/W-0                                                     | R/W-0                                                        | U-0                 | R/W-1            | R/W-0           | R/W-0  |

|------------------|------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------|---------------------|------------------|-----------------|--------|

| —                | T2IP2                                                            | T2IP1                                                     | T2IP0                                                        | —                   | OC2IP2           | OC2IP1          | OC2IP0 |

| bit 15           |                                                                  |                                                           |                                                              |                     |                  |                 | bit 8  |

| U-0              | R/W-1                                                            | R/W-0                                                     | R/W-0                                                        | U-0                 | U-0              | U-0             | U-0    |

| 0-0              | IC2IP2                                                           | IC2IP1                                                    | IC2IP0                                                       | 0-0                 | 0-0              | 0-0             | 0-0    |

| bit 7            | 10211 2                                                          | 10211 1                                                   | 10211 0                                                      |                     |                  |                 | bit C  |

|                  |                                                                  |                                                           |                                                              |                     |                  |                 |        |

| Legend:          |                                                                  |                                                           |                                                              |                     |                  |                 |        |

| R = Readab       | le bit                                                           | W = Writable                                              | bit                                                          | U = Unimplem        | nented bit, read | l as '0'        |        |

| -n = Value a     | t POR                                                            | '1' = Bit is set                                          |                                                              | '0' = Bit is clea   | ared             | x = Bit is unkr | nown   |

|                  |                                                                  |                                                           |                                                              |                     |                  |                 |        |

| bit 15           | -                                                                | nted: Read as '                                           |                                                              |                     |                  |                 |        |

| bit 14-12        |                                                                  | Timer2 Interrupt                                          | •                                                            |                     |                  |                 |        |

|                  | 111 = Interru                                                    | pt is Priority 7 (                                        | highest priority                                             | (interrupt)         |                  |                 |        |

|                  | •                                                                |                                                           |                                                              |                     |                  |                 |        |

|                  | •                                                                |                                                           |                                                              |                     |                  |                 |        |

|                  |                                                                  | ipt is Priority 1<br>ipt source is dis                    | abled                                                        |                     |                  |                 |        |

| bit 11           | Unimplemer                                                       | nted: Read as '                                           | 0'                                                           |                     |                  |                 |        |

| bit 10-8         | OC2IP<2:0>                                                       | : Output Compa                                            | are Channel 2                                                | Interrupt Priority  | / bits           |                 |        |

|                  | 111 = Interru                                                    | pt is Priority 7 (                                        | highest priority                                             | / interrupt)        |                  |                 |        |

|                  | •                                                                |                                                           |                                                              |                     |                  |                 |        |

|                  | •                                                                |                                                           |                                                              |                     |                  |                 |        |

|                  | •                                                                |                                                           |                                                              |                     |                  |                 |        |

|                  | •<br>001 = Interru                                               | ipt is Priority 1                                         |                                                              |                     |                  |                 |        |

|                  |                                                                  | ipt is Priority 1<br>ipt source is dis                    | abled                                                        |                     |                  |                 |        |

| bit 7            | 000 = Interru                                                    |                                                           |                                                              |                     |                  |                 |        |

|                  | 000 = Interru<br>Unimplemer                                      | ipt source is dis<br>nted: Read as '                      | 0'                                                           | rrupt Priority bits | 6                |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                       | ipt source is dis<br>nted: Read as '                      | <sup>0'</sup><br>Channel 2 Inte                              |                     | 3                |                 |        |

|                  | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                       | ipt source is dis<br>nted: Read as fi<br>Input Capture C  | <sup>0'</sup><br>Channel 2 Inte                              |                     | 3                |                 |        |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemer<br>IC2IP<2:0>:                       | ipt source is dis<br>nted: Read as fi<br>Input Capture C  | <sup>0'</sup><br>Channel 2 Inte                              |                     | 5                |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru<br>• | nted: Read as f<br>Input Capture C<br>Input Spriority 7 ( | <sup>0'</sup><br>Channel 2 Inte                              |                     | 3                |                 |        |

|                  | 000 = Interru<br>Unimplemen<br>IC2IP<2:0>:<br>111 = Interru      | ipt source is dis<br>nted: Read as fi<br>Input Capture C  | <sup>0'</sup><br>Channel 2 Inter<br>highest priorit <u>y</u> |                     | 5                |                 |        |

# 7.4 Interrupt Setup Procedures

### 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS Control bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

Note: At a device Reset, the IPCx registers are initialized, such that all user interrupt sources are assigned to Priority Level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

### 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, OEh, with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

# 9.2.2 IDLE MODE

Idle mode includes these features:

- · The CPU will stop executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 9.4 "Selective Peripheral Module Control").

- If the WDT or FSCM is enabled, the LPRC will also remain active.

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled.

- · Any device Reset.

- A WDT time-out.

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction or the first instruction in the ISR.

### 9.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction will be held off until entry into Sleep or Idle mode has completed. The device will then wake-up from Sleep or Idle mode.

# 9.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:256, with 1:1 being the default.

It is also possible to use Doze mode to selectively reduce power consumption in event driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

# 9.4 Selective Peripheral Module Control

Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked and thus, consume power. There may be cases where the application needs what these modes do not provide: the allocation of power resources to CPU processing with minimal power consumption from the peripherals.

PIC24F devices address this requirement by allowing peripheral modules to be selectively disabled, reducing or eliminating their power consumption. This can be done with two control bits:

- The Peripheral Enable bit, generically named, "XXXEN", located in the module's main control SFR.

- The Peripheral Module Disable (PMD) bit, generically named, "XXXMD", located in one of the PMD control registers.

Both bits have similar functions in enabling or disabling its associated module. Setting the PMD bit for a module disables all clock sources to that module, reducing its power consumption to an absolute minimum. In this state, the control and status registers associated with the peripheral will also be disabled, so writes to those registers will have no effect and read values will be invalid. Many peripheral modules have a corresponding PMD bit.

In contrast, disabling a module by clearing its XXXEN bit disables its functionality, but leaves its registers available to be read and written to. Power consumption is reduced, but not by as much as the PMD bit does. Most peripheral modules have an enable bit; exceptions include capture, compare and RTCC.

To achieve more selective power savings, peripheral modules can also be selectively disabled when the device enters Idle mode. This is done through the control bit of the generic name format, "XXXIDL". By default, all modules that can operate during Idle mode will do so. Using the disable on Idle feature allows further reduction of power consumption during Idle mode, enhancing power savings for extremely critical power applications.

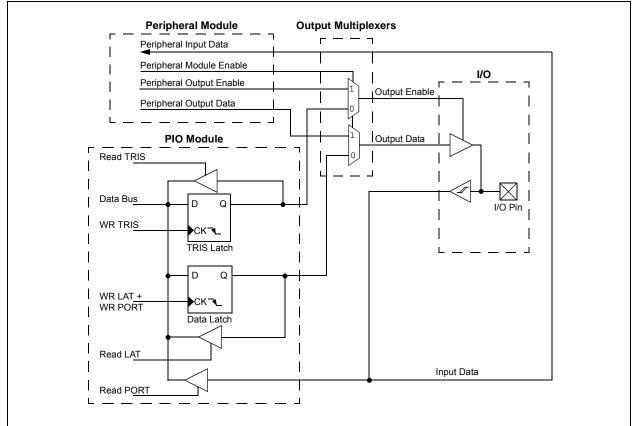

# 10.0 I/O PORTS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"I/O* Ports with Peripheral Pin Select (PPS)" (DS39711).

All of the device pins (except VDD, VSS, MCLR and OSCI/CLKI) are shared between the peripherals and the Parallel I/O (PIO) ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

# 10.1 Parallel I/O (PIO) Ports

A Parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Output Latch register (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless, regarded as a dedicated port because there is no other competing source of outputs.

### FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

| U-0           | U-0        | U-0              | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|---------------|------------|------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _             |            | _                | RP25R4 <sup>(1)</sup> | RP25R3 <sup>(1)</sup> | RP25R2 <sup>(1)</sup> | RP25R1 <sup>(1)</sup> | RP25R0 <sup>(1)</sup> |

| bit 15        |            |                  |                       |                       |                       |                       | bit 8                 |

|               |            |                  |                       |                       |                       |                       |                       |

| U-0           | U-0        | U-0              | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

| _             |            | —                | RP24R4 <sup>(1)</sup> | RP24R3 <sup>(1)</sup> | RP24R2 <sup>(1)</sup> | RP24R1 <sup>(1)</sup> | RP24R0 <sup>(1)</sup> |

| bit 7         |            |                  | •                     | •                     |                       |                       | bit 0                 |

|               |            |                  |                       |                       |                       |                       |                       |

| Legend:       |            |                  |                       |                       |                       |                       |                       |

| R = Readable  | e bit      | W = Writable     | bit                   | U = Unimplem          | nented bit, read      | l as '0'              |                       |

| -n = Value at | POR        | '1' = Bit is set |                       | '0' = Bit is clea     | ared                  | x = Bit is unkn       | iown                  |

|               |            |                  |                       |                       |                       |                       |                       |

| bit 15-13     | Unimplemen | ted: Read as '@  | י'                    |                       |                       |                       |                       |

### REGISTER 10-27: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

bit 15-13 Unimplemented: Read as '0

RP25R<4:0>: Peripheral Output Function is Assigned to RP25 Output Pin bits<sup>(1)</sup> bit 12-8 (see Table 10-3 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

RP24R<4:0>: Peripheral Output Function is Assigned to RP24 Output Pin bits<sup>(1)</sup> bit 4-0 (see Table 10-3 for peripheral function numbers)

Note 1: These bits are only available on the 44-pin devices; otherwise, they read as '0'.

| R/W-0         | U-0                         | R/W-0                              | U-0                       | U-0                | U-0              | U-0                | U-0    |

|---------------|-----------------------------|------------------------------------|---------------------------|--------------------|------------------|--------------------|--------|

| TON           |                             | TSIDL                              |                           |                    |                  | _                  | _      |

| bit 15        |                             |                                    |                           |                    |                  |                    | bit 8  |

|               |                             |                                    |                           |                    |                  |                    |        |

| U-0           | R/W-0                       | R/W-0                              | R/W-0                     | R/W-0              | U-0              | R/W-0              | U-0    |

| _             | TGATE                       | TCKPS1                             | TCKPS0                    | T32 <sup>(1)</sup> |                  | TCS <sup>(2)</sup> | _      |

| bit 7         |                             |                                    |                           |                    |                  |                    | bit (  |

|               |                             |                                    |                           |                    |                  |                    |        |

| Legend:       |                             |                                    |                           |                    |                  |                    |        |

| R = Readabl   | le bit                      | W = Writable                       | bit                       | U = Unimplem       | nented bit, rea  | d as '0'           |        |

| -n = Value at | t POR                       | '1' = Bit is set                   |                           | '0' = Bit is clea  | ared             | x = Bit is unkno   | own    |

|               |                             |                                    |                           |                    |                  |                    |        |

| bit 15        | TON: Timerx                 |                                    |                           |                    |                  |                    |        |

|               | When TxCOM<br>1 = Starts 32 |                                    |                           |                    |                  |                    |        |

|               | 0 =  Stops 32               | •                                  |                           |                    |                  |                    |        |

|               | When TxCO                   | -                                  |                           |                    |                  |                    |        |

|               | 1 = Starts 16               |                                    |                           |                    |                  |                    |        |

|               | 0 = Stops 16                |                                    | - 1                       |                    |                  |                    |        |

| bit 14        | •                           | ted: Read as '                     |                           |                    |                  |                    |        |

| bit 13        |                             | rx Stop in Idle N                  |                           |                    |                  |                    |        |

|               |                             | ues module op<br>s module opera    |                           |                    | e mode           |                    |        |

| bit 12-7      |                             | ted: Read as '                     |                           |                    |                  |                    |        |

| bit 6         | -                           | erx Gated Time                     |                           | Enable bit         |                  |                    |        |

|               | When TCS =                  |                                    |                           |                    |                  |                    |        |

|               | This bit is ign             |                                    |                           |                    |                  |                    |        |

|               | When TCS =                  |                                    |                           |                    |                  |                    |        |

|               |                             | ne accumulatio<br>ne accumulatio   |                           |                    |                  |                    |        |

| bit 5-4       |                             | : Timerx Input                     |                           | Select bits        |                  |                    |        |

|               | 11 = 1:256                  | i mont mpat                        |                           |                    |                  |                    |        |

|               | 10 = 1:64                   |                                    |                           |                    |                  |                    |        |

|               | 01 = 1:8                    |                                    |                           |                    |                  |                    |        |

| hit 2         | 00 = 1:1                    | imer Mode Sele                     | not hit(1)                |                    |                  |                    |        |

| bit 3         |                             | nd Timery form                     |                           | timer              |                  |                    |        |

|               |                             | nd Timery act a                    |                           |                    |                  |                    |        |

|               |                             | e, T3CON cont                      |                           |                    | er operation.    |                    |        |

| bit 2         | Unimplemer                  | ted: Read as '                     | 0'                        |                    |                  |                    |        |

| bit 1         | TCS: Timerx                 | Clock Source S                     | Select bit <sup>(2)</sup> |                    |                  |                    |        |

|               |                             | l clock from pin<br>clock (Fosc/2) | , TxCK (on the            | rising edge)       |                  |                    |        |

| bit 0         | Unimplemer                  | ted: Read as '                     | 0'                        |                    |                  |                    |        |

| Note 1: In    | n 32-bit mode, th           | ne T3CON or T                      | 5CON control h            | its do not affec   | t 32-hit timer o | neration           |        |

|               |                             |                                    |                           |                    |                  | more informatio    | n, see |

|               | ection 10.4 "Pe             |                                    |                           |                    |                  |                    | ,      |

#### REGISTER 12-1: TxCON: TIMER2 AND TIMER4 CONTROL REGISTER

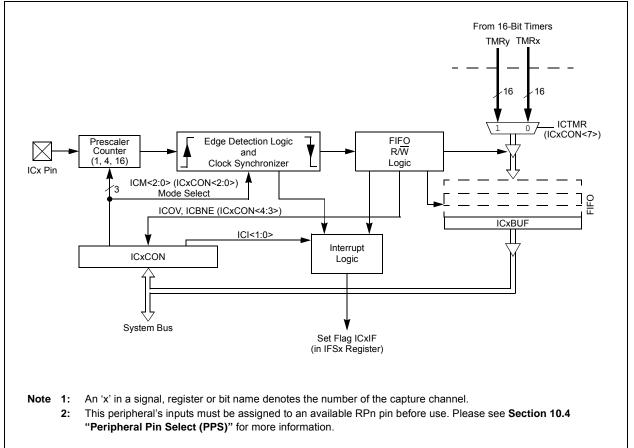

# **13.0 INPUT CAPTURE**

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"PIC24F Family Reference Manual"*, *"Input Capture"* (DS39701).

| U-0                 | U-0                                    | U-0              | R/W-0                                  | R/W-0                 | R/W-0                  | R/W-0            | R/W-0              |

|---------------------|----------------------------------------|------------------|----------------------------------------|-----------------------|------------------------|------------------|--------------------|

| _                   | _                                      | _                | DISSCK <sup>(1)</sup>                  | DISSDO <sup>(2)</sup> | MODE16                 | SMP              | CKE <sup>(3)</sup> |

| bit 15              |                                        |                  |                                        |                       |                        |                  | bit                |

|                     |                                        |                  |                                        |                       |                        |                  |                    |

| R/W-0               |                                        | R/W-0            | R/W-0                                  | R/W-0                 | R/W-0                  | R/W-0            | R/W-0              |

| SSEN <sup>(4)</sup> | ) CKP                                  | MSTEN            | SPRE2                                  | SPRE1                 | SPRE0                  | PPRE1            | PPRE0              |

| bit 7               |                                        |                  |                                        |                       |                        |                  | bit                |

| Legend:             |                                        |                  |                                        |                       |                        |                  |                    |

| R = Reada           | able bit                               | W = Writable     | bit                                    | U = Unimplem          | nented bit, read       | as '0'           |                    |

| -n = Value          | at POR                                 | '1' = Bit is set |                                        | '0' = Bit is clea     |                        | x = Bit is unkn  | iown               |

|                     |                                        |                  | -                                      |                       |                        |                  | -                  |

| bit 15-13           | Unimplemen                             | ted: Read as '   | 0'                                     |                       |                        |                  |                    |

| bit 12              | DISSCK: Disa                           | ables SCKx Pi    | n bit (SPI Maste                       | er modes only)        | (1)                    |                  |                    |

|                     |                                        |                  | abled; pin funct                       | ions as I/O           |                        |                  |                    |

|                     |                                        | SPI clock is en  |                                        |                       |                        |                  |                    |

| bit 11              |                                        | ables SDOx Pi    |                                        |                       |                        |                  |                    |

|                     |                                        |                  | y the module; p                        | in functions as       | I/O                    |                  |                    |

| bit 10              |                                        | n is controlled  | •                                      | at hit                |                        |                  |                    |

|                     |                                        | -                | unication Seleo                        |                       |                        |                  |                    |

|                     |                                        | ication is byte- | , ,                                    |                       |                        |                  |                    |

| bit 9               |                                        | ata Input Sam    |                                        |                       |                        |                  |                    |

|                     | Master mode:                           |                  |                                        |                       |                        |                  |                    |

|                     |                                        |                  | t end of data ou                       |                       |                        |                  |                    |

|                     | -                                      | a is sampled a   | t middle of data                       | output time           |                        |                  |                    |

|                     | <u>Slave mode:</u>                     | cleared when     | SPIx is used in                        | Slave mode            |                        |                  |                    |

| bit 8               |                                        | lock Edge Sele   |                                        |                       |                        |                  |                    |

| bit 0               |                                        | •                |                                        | n from active c       | lock state to Idl      | e clock state (s | see bit 6)         |

|                     |                                        |                  |                                        |                       | ck state to active     |                  |                    |

| bit 7               | SSEN: Slave                            | Select Enable    | bit (Slave mode                        | ∋) <sup>(4)</sup>     |                        |                  |                    |

|                     |                                        | s used for Slav  |                                        |                       |                        |                  |                    |

|                     | 0 = SSx pin i                          | s not used by    | he module; pin                         | is controlled by      | y port function        |                  |                    |

| bit 6               |                                        | olarity Select   |                                        |                       |                        |                  |                    |

|                     |                                        |                  | s a high level; a<br>s a low level; ac |                       |                        |                  |                    |

| bit 5               |                                        | ter Mode Enat    | -                                      |                       | lignievei              |                  |                    |

| DIUD                | 1 = Master m                           |                  | ne bit                                 |                       |                        |                  |                    |

|                     | 0 = Slave mo                           |                  |                                        |                       |                        |                  |                    |

| Note 1:             | If DISSCK = 0, So<br>Select (PPS)" for |                  |                                        | available RPn         | pin. See <b>Sectio</b> | on 10.4 "Perip   | heral Pin          |

| 2:                  | If DISSDO = 0, S<br>Select (PPS)" for  | DOx must be o    | configured to an                       | available RPn         | pin. See <b>Secti</b>  | on 10.4 "Perip   | oheral Pin         |

| 3:                  | The CKE bit is no SPI modes (FRM       | EN = 1).         |                                        |                       |                        |                  |                    |

| 4:                  | If SSEN = 1, SSx<br>(PPS)" for more i  |                  | gured to an ava                        | ilable RPn pin.       | See Section 1          | 0.4 "Peripher    | al Pin Selec       |

### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 5 | D/A: Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that the last byte received was data</li> <li>0 = Indicates that the last byte received was a device address</li> <li>Hardware is clear at a device address match. Hardware is set by a write to I2CxTRN or by reception of a slave byte.</li> </ul> |

| bit 4 | P: Stop bit                                                                                                                                                                                                                                                                 |

|       | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> <li>Hardware is set or clear when Start, Repeated Start or Stop is detected.</li> </ul>                                                                      |

| bit 3 | S: Start bit                                                                                                                                                                                                                                                                |

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware is set or clear when Start, Repeated Start or Stop is detected.</li> </ul>                                                |

| bit 2 | <b>R/W</b> : Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                          |

|       | <ul> <li>1 = Read – Indicates data transfer is output from slave</li> <li>0 = Write – Indicates data transfer is input to slave</li> <li>Hardware is set or clear after reception of an I<sup>2</sup>C device address byte.</li> </ul>                                      |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                                                                         |

|       | <ul> <li>1 = Receive is complete, I2CxRCV is full</li> <li>0 = Receive is not complete, I2CxRCV is empty</li> <li>Hardware is set when I2CxRCV is written with received byte. Hardware is clear when software reads</li> <li>I2CxRCV.</li> </ul>                            |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit<br>1 = Transmit is in progress, I2CxTRN is full<br>0 = Transmit is complete, I2CxTRN is empty<br>Hardware is set when software writes I2CxTRN. Hardware is clear at completion of data transmission.                            |

**Note 1:** In both Master and Slave modes, the ACKSTAT bit is only updated when transmitting data resulting in the reception of an ACK or NACK from another device. Do not check the state of ACKSTAT when receiving data, either as a slave or a master. Reading ACKSTAT after receiving address or data bytes returns an invalid result.

### REGISTER 16-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------|-------|

| —      | —   | —   | —   | —   | _   | AMSK9 | AMSK8 |

| bit 15 |     |     |     |     |     |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| AMSK7 | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

AMSK<9:0>: Mask for Address Bit x Select bits

- 1 = Enables masking for bit x of incoming message address; bit match is not required in this position

- 0 = Disables masking for bit x; bit match is required in this position

bit 9-0

### REGISTER 18-6: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| <br>bit 7 | —   | —   | —   | —   | —   | RTSECSEL <sup>(1)</sup> | PMPTTL<br>bit 0 |

|-----------|-----|-----|-----|-----|-----|-------------------------|-----------------|

| U-0       | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                   | R/W-0           |

| bit 15    |     |     |     |     |     |                         | bit 8           |

| _         | —   | —   | —   | —   | —   | —                       |                 |

| U-0       | U-0 | U-0 | U-0 | U-0 | U-0 | U-0                     | U-0             |

bit 15-2 Unimplemented: Read as '0'

- bit 1RTSECSEL: RTCC Seconds Clock Output Select bit(1)1 = RTCC seconds clock is selected for the RTCC pin0 = RTCC alarm pulse is selected for the RTCC pinbit 0PMPTTL: PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffers

Note 1: To enable the actual RTCC output, the RTCOE (RCFGCAL) bit needs to be set.

# 19.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

| Note: | This data sheet summarizes the features of |

|-------|--------------------------------------------|

|       | this group of PIC24F devices. It is not    |

|       | intended to be a comprehensive reference   |

|       | source. For more information, refer to the |

|       | "PIC24F Family Reference Manual",          |

|       | "Real-Time Clock and Calendar              |

|       | (RTCC)" (DS39696).                         |

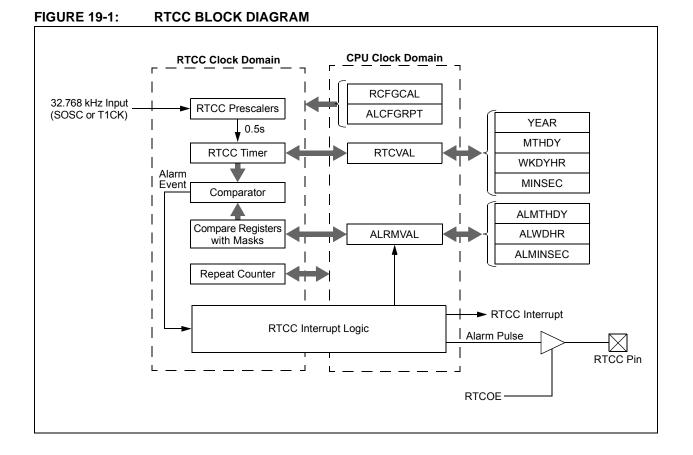

The Real-Time Clock and Calendar (RTCC) provides on-chip, hardware-based clock and calendar functionality with little or no CPU overhead. It is intended for applications where accurate time must be maintained for extended periods, with minimal CPU activity and with limited power resources, such as battery-powered applications. Key features include:

- Time data in hours, minutes and seconds, with a granularity of one-half second

- 24-hour format (military time) display option

- · Calendar data as date, month and year

- Automatic, hardware-based day of week and leap year calculations for dates from 2000 through 2099

- Time and calendar data in BCD format for compact firmware

- Highly configurable alarm function

- External output pin with selectable alarm signal or seconds "tick" signal output

- Time base input from Secondary Oscillator (SOSC) or the T1CK digital clock input (32.768 kHz)

- · User calibration feature with auto-adjust

A simplified block diagram of the module is shown in Figure 19-1.The SOSC and RTCC will both remain running while the device is held in Reset with MCLR, and will continue running after MCLR is released.

### © 2010-2013 Microchip Technology Inc.

### REGISTER 21-5: AD1PCFG: A/D PORT CONFIGURATION REGISTER

| R/W-0  | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0                |

|--------|-----|-----|--------|--------|--------|-------|----------------------|

| PCFG15 | —   | —   | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 <sup>(1)</sup> |

| bit 15 |     |     |        |        |        |       | bit 8                |

| R/W-0                | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|----------------------|----------------------|-------|-------|-------|-------|-------|-------|--|

| PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 | PCFG4 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |  |

| bit 7 bit 0          |                      |       |       |       |       |       |       |  |

# Legend

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 **PCFG15:** Analog Input Pin Configuration Control bit

1 = Band gap voltage reference is disabled

0 = Band gap voltage reference is enabled

bit 14-13 Unimplemented: Read as '0'

bit 12-0 PCFG<12:0>: Analog Input Pin Configuration Control bits<sup>(1)</sup>

1 = Pin for corresponding analog channel is configured in Digital mode; I/O port read is enabled

0 = Pin is configured in Analog mode; I/O port read is disabled, A/D samples pin voltage

Note 1: Analog Channels, AN6, AN7 and AN8, are unavailable on 28-pin devices; leave these corresponding bits set.

| R/W-0                | U-0                  | U-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0                |  |

|----------------------|----------------------|-------|--------|--------|--------|-------|----------------------|--|

| CSSL15               | —                    | —     | CSSL12 | CSSL11 | CSSL10 | CSSL9 | CSSL8 <sup>(1)</sup> |  |

| bit 15               |                      |       |        |        |        |       | bit 8                |  |

|                      |                      |       |        |        |        |       |                      |  |

| R/W-0                | R/W-0                | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0                |  |

| CSSL7 <sup>(1)</sup> | CSSL6 <sup>(1)</sup> | CSSL5 | CSSL4  | CSSL3  | CSSL2  | CSSL1 | CSSL0                |  |

| bit 7                |                      |       |        |        |        |       | bit 0                |  |

|                      |                      |       |        |        |        |       |                      |  |

### REGISTER 21-6: AD1CSSL: A/D INPUT SCAN SELECT REGISTER

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 CSSL15: Band Gap Reference Input Pin Scan Selection bit

1 = Band gap voltage reference channel is selected for input scan

0 = Band gap voltage reference channel is omitted from input scan

bit 14-13 Unimplemented: Read as '0'

bit 12-0 CSSL<12:0>: A/D Input Pin Scan Selection bits<sup>(1)</sup>

1 = Corresponding analog channel is selected for input scan

0 = Analog channel is omitted from input scan

**Note 1:** Analog Channels, AN6, AN7 and AN8, are unavailable on 28-pin devices; leave these corresponding bits cleared.

# REGISTER 24-4: DEVREV: DEVICE REVISION REGISTER

| U      | U      | U | U | U | U    | U    | U      |

|--------|--------|---|---|---|------|------|--------|

|        | —      | — | — | — | —    | —    | —      |

| bit 23 |        |   |   |   |      |      | bit 16 |

|        |        |   |   |   |      |      |        |

| U      | U      | U | U | U | U    | U    | R      |

| —      | —      | — | — | — |      | —    | MAJRV2 |

| bit 15 |        |   |   |   |      |      | bit 8  |

|        |        |   |   |   |      |      |        |

| R      | R      | U | U | U | R    | R    | R      |

| MAJRV1 | MAJRV0 | — | — | — | DOT2 | DOT1 | DOT0   |

| bit 7  |        |   |   |   |      |      | bit 0  |

|        |        |   |   |   |      |      |        |

| Legend: R = Read-only bit | U = Unimplemented bit |  |

|---------------------------|-----------------------|--|

|---------------------------|-----------------------|--|

- bit 23-9 Unimplemented: Read as '0'

- bit 8-6 MAJRV<2:0>: Major Revision Identifier bits

- bit 5-3 Unimplemented: Read as '0'

- bit 2-0 DOT<2:0>: Minor Revision Identifier bits

# TABLE 26-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                           |

|-----------------|---------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                       |

| (text)          | Means "content of text"                                                               |

| [text]          | Means "the location addressed by text"                                                |

| { }             | Optional field or operation                                                           |

| <n:m></n:m>     | Register bit field                                                                    |

| .b              | Byte mode selection                                                                   |

| .d              | Double-Word mode selection                                                            |

| .S              | Shadow register select                                                                |

| .W              | Word mode selection (default)                                                         |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$         |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                  |

| Expr            | Absolute address, label or expression (resolved by the linker)                        |

| f               | File register address ∈ {0000h1FFFh}                                                  |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                        |

| lit4            | 4-bit unsigned literal ∈ {015}                                                        |

| lit5            | 5-bit unsigned literal ∈ {031}                                                        |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                       |

| lit10           | 10-bit unsigned literal $\in$ {0255} for Byte mode, {0:1023} for Word mode            |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                    |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                    |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be '0'                                 |

| None            | Field does not require an entry, may be blank                                         |

| PC              | Program Counter                                                                       |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                     |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                 |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                        |

| Wb              | Base W register ∈ {W0W15}                                                             |

| Wd              | Destination W register $\in$ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                 |

| Wdo             | Destination W register $\in$ { Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm,Wn           | Dividend, Divisor working register pair (direct addressing)                           |

| Wn              | One of 16 working registers ∈ {W0W15}                                                 |

| Wnd             | One of 16 destination working registers ∈ {W0W15}                                     |

| Wns             | One of 16 source working registers ∈ {W0W15}                                          |

| WREG            | W0 (working register used in file register instructions)                              |

| Ws              | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                          |

| Wso             | Source W register ∈ { Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }          |

### TABLE 27-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                | Symbol | Min | Тур         | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| PIC24FJ64GA004 Family:                                                                                                                                                                |        |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                  | TJ     | -40 | —           | +140 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                   | TA     | -40 | —           | +125 | °C   |